VLSI設計-MOSインバーター

インバーターは本当にすべてのデジタル設計の中核です。その動作と特性が明確に理解されると、NANDゲート、加算器、乗算器、マイクロプロセッサなどのより複雑な構造の設計が大幅に簡素化されます。これらの複雑な回路の電気的動作は、インバーターで得られた結果を外挿することでほぼ完全に導き出すことができます。

インバーターの分析を拡張して、NAND、NOR、XORなどのより複雑なゲートの動作を説明できます。これらのゲートは、乗算器やプロセッサーなどのモジュールの構成要素を形成します。この章では、静的CMOSインバーター、つまりCMOSインバーターであるインバーターゲートの単一の化身に焦点を当てます。これは確かに現在最も人気があり、したがって私たちの特別な注意に値します。

動作原理

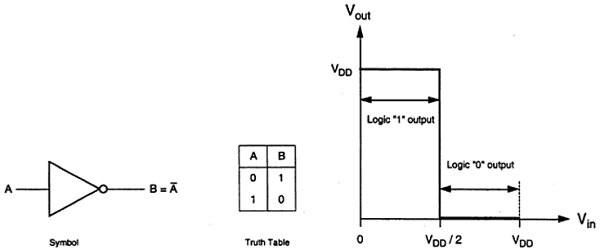

理想的なインバータの論理記号と真理値表を下図に示します。ここで、Aは入力であり、Bはノード電圧で表される反転出力です。Vにより正論理を使用して、論理1のブール値が示されているddは論理0が0 Vで表される第Vインバータ閾値電圧であり、DDのV / 2、DDは出力電圧です。

出力はV 0から切り替えられddは、入力がV未満である場合番目。だから、0 <Vために<V番目の出力は、論理0入力及びVに等しい番目<Vで<VのDDはインバータのロジック1入力に等しいです。

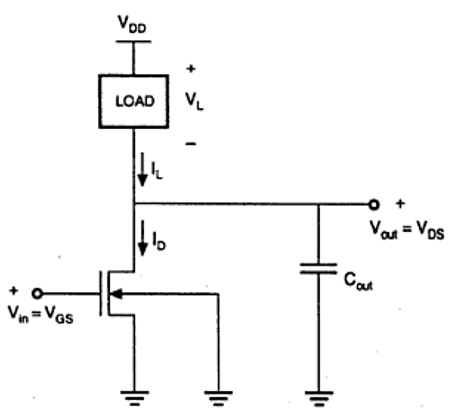

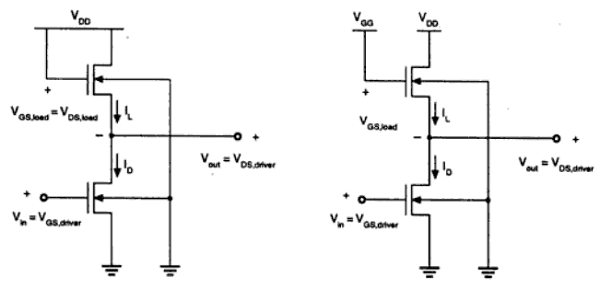

図に示す特性は理想的です。nMOSインバータの一般的な回路構造を下図に示します。

与えられた図から、インバータの入力電圧はnMOSトランジスタのゲート-ソース間電圧に等しく、インバータの出力電圧はnMOSトランジスタのドレイン-ソース間電圧に等しいことがわかります。nMOSのソース間電圧は、接地されたトランジスタのドライバとも呼ばれます。したがって、V SS = 0です。出力ノードは、VTCに使用される集中容量に接続されています。

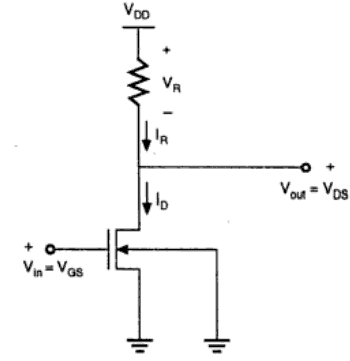

抵抗負荷インバータ

抵抗負荷インバータの基本構造を下図に示します。ここでは、エンハンスメント型nMOSがドライバトランジスタとして機能します。負荷は、単純な線形抵抗Rから成るL。回路の電源はVであるDDとドレイン電流I Dは、負荷電流Iに等しいR。

回路動作

ドライバトランジスタの入力がスレッショルド電圧VTH(V in <V TH)未満の場合、ドライバトランジスタはカットオフ領域にあり、電流は流れません。したがって、負荷抵抗の両端の電圧降下はゼロであり、出力電圧はVDDに等しくなります。ここで、入力電圧がさらに上昇すると、ドライバトランジスタがゼロ以外の電流を流し始め、nMOSが飽和領域に入ります。

数学的には、

$$ I_ {D} = \ frac {K_ {n}} {2} \ left [V_ {GS} -V_ {TO} \ right] ^ {2} $$

入力電圧をさらに上げると、ドライバトランジスタは線形領域に入り、ドライバトランジスタの出力は減少します。

$$ I_ {D} = \ frac {K_ {n}} {2} 2 \ left [V_ {GS} -V_ {TO} \ right] V_ {DS} -V_ {DS} ^ {2} $$

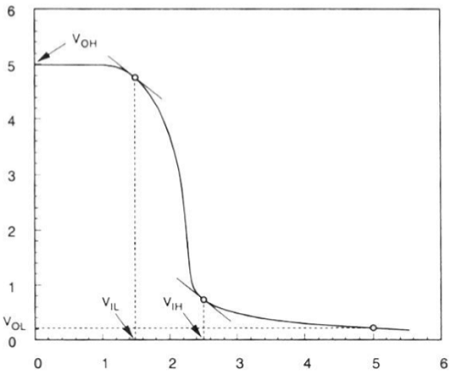

以下に示す抵抗負荷インバータのVTCは、ドライバトランジスタの動作モードと電圧ポイントを示します。

N型MOSFET負荷のインバータ

MOSFETを負荷デバイスとして使用する主な利点は、トランジスタが占めるシリコンの面積が、抵抗性負荷が占める面積よりも小さいことです。ここで、MOSFETはアクティブ負荷であり、アクティブ負荷のあるインバーターは、抵抗性負荷のあるインバーターよりも優れた性能を発揮します。

エンハンスメントロードNMOS

エンハンスメント型負荷装置を備えた2台のインバータを図に示します。負荷トランジスタは、ゲート端子に印加されるバイアス電圧に応じて、飽和領域または線形領域のいずれかで動作できます。飽和エンハンスメント負荷インバータを図1に示します。(a)。これは、単一の電圧源と、単純な製造工程を必要とし、VようOH Vに制限されているDD - V T。

線形増強負荷インバータを図1に示します。(b)。常に線形領域で動作します。したがって、VOHレベルはVDDに等しくなります。

線形負荷インバーターは、飽和エンハンスメントインバーターと比較して高いノイズマージンを持っています。ただし、リニアエンハンスメントインバータの欠点は、2つの別個の電源が必要であり、両方の回路で高い電力損失が発生することです。したがって、エンハンスメントインバータは大規模なデジタルアプリケーションでは使用されません。

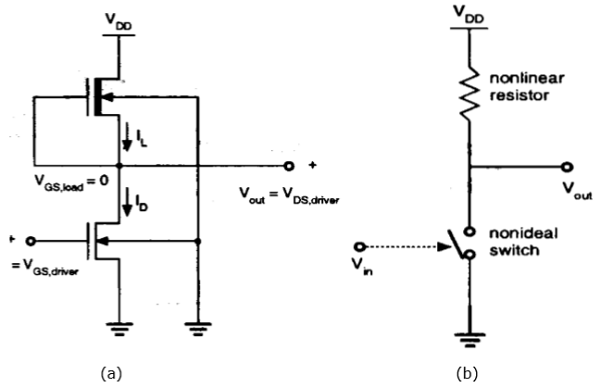

枯渇負荷NMOS

エンハンスメントロードインバーターの欠点は、デプレッションロードインバーターを使用することで克服できます。エンハンスメント負荷インバーターと比較して、空乏負荷インバーターは、負荷のしきい値電圧を調整するためにチャネル注入のためのいくつかのより多くの製造ステップを必要とします。

枯渇負荷インバーターの利点は、シャープなVTC遷移、優れたノイズマージン、単一電源、および全体的なレイアウト領域の縮小です。

図に示すように、負荷のゲート端子とソース端子が接続されています。したがって、V GS = 0です。したがって、負荷のしきい値電圧は負です。したがって、

$$ V_ {GS、load}> V_ {T、load} $$が満たされている

したがって、負荷デバイスには、入力および出力電圧レベルに関係なく、常に導通チャネルがあります。

負荷トランジスタが飽和領域にあるとき、負荷電流は次の式で与えられます。

$$ I_ {D、load} = \ frac {K_ {n、load}} {2} \ left [-V_ {T、load} \ left(V_ {out} \ right)\ right] ^ {2} $ $

負荷トランジスタが線形領域にある場合、負荷電流は次の式で与えられます。

$$ I_ {D、load} = \ frac {K_ {n、load}} {2} \ left [2 \ left | V_ {T、load} \ left(V_ {out} \ right)\ right |。\ left(V_ {DD} -V_ {out} \ right)-\ left(V_ {DD} -V_ {out} \ right )^ {2} \ right] $$

空乏負荷インバータの電圧伝達特性を下図に示します。

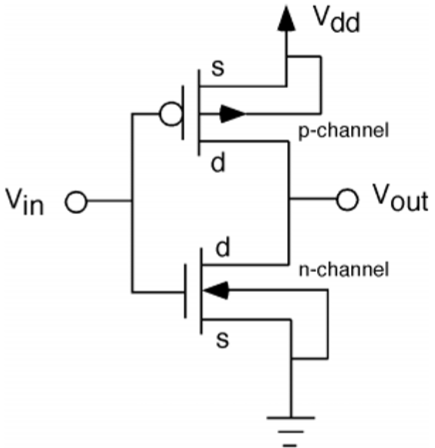

CMOSインバーター–回路、操作および説明

図にCMOSインバータ回路を示します。ここでは、nMOSおよびpMOSトランジスタがドライバトランジスタとして機能します。一方のトランジスタがオンのとき、もう一方はオフです。

この構成はと呼ばれます complementary MOS (CMOS)。入力は両方のトランジスタのゲート端子に接続されているため、両方を入力電圧で直接駆動できます。nMOSトランジスタの基板は、グランドに接続され、pMOSの基板は電源、Vに接続されているDD。

したがって、両方のトランジスタでV SB = 0です。

$$ V_ {GS、n} = V_ {in} $$

$$ V_ {DS、n} = V_ {out} $$

そして、

$$ V_ {GS、p} = V_ {in} -V_ {DD} $$

$$ V_ {DS、p} = V_ {out} -V_ {DD} $$

nMOSの入力がスレッショルド電圧よりも小さい場合(V in <V TO、n)、nMOSはカットオフされ、pMOSは線形領域にあります。したがって、両方のトランジスタのドレイン電流はゼロです。

$$ I_ {D、n} = I_ {D、p} = 0 $$

したがって、出力電圧VOHは供給電圧に等しくなります。

$$ V_ {out} = V_ {OH} = V_ {DD} $$

入力電圧がVDD + V TO、pより大きい場合、pMOSトランジスタはカットオフ領域にあり、nMOSは線形領域にあるため、両方のトランジスタのドレイン電流はゼロです。

$$ I_ {D、n} = I_ {D、p} = 0 $$

したがって、出力電圧VOLはゼロに等しくなります。

$$ V_ {out} = V_ {OL} = 0 $$

V in > V TOの場合、および以下の条件が満たされる場合、nMOSは飽和領域で動作します。

$$ V_ {DS、n} \ geq V_ {GS、n} -V_ {TO、n} $$

$$ V_ {out} \ geq V_ {in} -V_ {TO、n} $$

V in <V DD + V TO、pの場合、および以下の条件が満たされる場合、 pMOSは飽和領域で動作します。

$$ V_ {DS、p} \ leq V_ {GS、p} -V_ {TO、p} $$

$$ V_ {out} \ leq V_ {in} -V_ {TO、p} $$

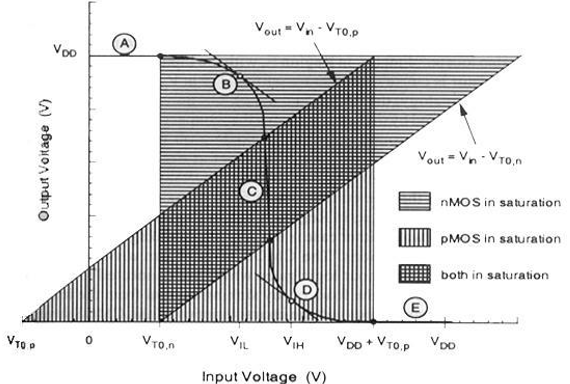

入力電圧の値が異なる場合、両方のトランジスタの動作領域を以下に示します。

| 領域 | V in | Vアウト | nMOS | pMOS |

|---|---|---|---|---|

| A | <V TO、n | V OH | を中断する | 線形 |

| B | V IL | 高≈V OH | 飽和 | 線形 |

| C | V番目 | V番目 | 飽和 | 飽和 |

| D | V IH | 低≈V OL | 線形 | 飽和 |

| E | >(V DD + V TO、p) | V OL | 線形 | を中断する |

CMOSのVTCを下図に示します-