디지털 카운터

카운터는 순차 회로입니다. 카운트 펄스에 사용되는 디지털 회로는 알려진 카운터입니다. 카운터는 플립 플롭의 가장 광범위한 응용 프로그램입니다. 클럭 신호가 적용된 플립 플롭 그룹입니다. 카운터는 두 가지 유형이 있습니다.

- 비동기 또는 리플 카운터.

- 동기식 카운터.

비동기 또는 리플 카운터

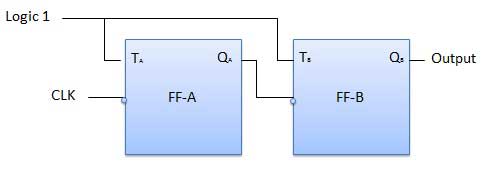

2 비트 리플 업 카운터의 논리 다이어그램이 그림에 나와 있습니다. 토글 (T) 플립 플롭이 사용되고 있습니다. 그러나 J와 K가 로직 1에 영구적으로 연결된 상태에서도 JK 플립 플롭을 사용할 수 있습니다. 외부 클럭은 플립 플롭 A 의 클럭 입력에 적용 되고 Q A 출력은 다음 플립 플롭의 클럭 입력에 적용됩니다. FF-B.

논리 다이어그램

조작

| SN | 질환 | 조작 |

|---|---|---|

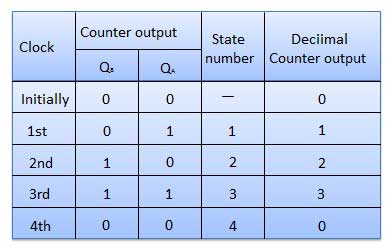

| 1 | Initially let both the FFs be in the reset state | Q B Q A = 처음에는 00 |

| 2 | After 1st negative clock edge | 첫 번째 네거티브 클럭 에지가 적용되 자마자 FF-A가 토글되고 Q A 는 1이됩니다. Q A 는 FF-B의 클럭 입력에 연결됩니다. Q A 가 0에서 1로 변경되었으므로 FF-B에 의해 양의 클럭 에지로 처리됩니다. FF-B는 네거티브 에지 트리거 FF이기 때문에 Q B 에는 변화가 없습니다 . Q B Q A = 첫 번째 클록 펄스 이후 01. |

| 삼 | After 2nd negative clock edge | 두 번째 네거티브 클럭 에지에 도달하면 FF-A가 다시 토글되고 Q A = 0입니다. Q A 의 변화는 FF-B의 음의 클록 에지 역할을합니다. 그래서 그것은 토글되고 Q B 는 1이 될 것입니다. Q B Q A = 두 번째 클럭 펄스 이후 10. |

| 4 | After 3rd negative clock edge | 세 번째 음의 클럭 에지가 도착하면 FF-A가 다시 토글되고 Q A 는 0에서 1이됩니다. 이것은 긍정적 인 변화이기 때문에 FF-B는 이에 응답하지 않고 비활성 상태로 유지됩니다. 따라서 Q B 는 변하지 않고 계속 1과 같습니다. 세 번째 클럭 펄스 후 Q B Q A = 11. |

| 5 | After 4th negative clock edge | 네 번째 네거티브 클럭 에지에 도달하면 FF-A가 다시 토글되고 Q A 는 0에서 1이됩니다. Q A의 이러한 음의 변화는 FF-B의 클럭 펄스 역할을합니다. 따라서 Q B 를 1에서 0 으로 변경하도록 전환됩니다 . 네 번째 클럭 펄스 이후 Q B Q A = 00. |

진실 테이블

동기식 카운터

"클록"펄스가 카운터의 모든 플립 플롭에 동시에 적용되는 경우 이러한 카운터를 동기식 카운터라고합니다.

2 비트 동기식 업 카운터

FF-A 의 J A 및 K A 입력은 논리 1에 연결됩니다. 따라서 FF-A는 토글 플립 플롭으로 작동합니다. J B 및 K B 입력은 Q A에 연결됩니다 .

논리 다이어그램

조작

| SN | 질환 | 조작 |

|---|---|---|

| 1 | Initially let both the FFs be in the reset state | Q B Q A = 처음에는 00. |

| 2 | After 1st negative clock edge | 첫 번째 네거티브 클럭 에지가 적용되 자마자 FF-A가 토글되고 Q A 가 0에서 1로 변경됩니다. 그러나 네거티브 클럭 에지를 적용하는 순간 Q A , J B = K B = 0. 따라서 FF-B는 상태를 변경하지 않습니다. 따라서 Q B 는 0으로 유지됩니다. Q B Q A = 첫 번째 클록 펄스 이후 01. |

| 삼 | After 2nd negative clock edge | 두 번째 네거티브 클럭 에지에 도달하면 FF-A가 다시 토글되고 Q A 가 1에서 0으로 변경됩니다. 그러나이 순간 Q A 는 1이었습니다. 따라서 J B = K B = 1이고 FF-B가 전환됩니다. 따라서 Q B 는 0에서 1로 변경됩니다. Q B Q A = 두 번째 클럭 펄스 이후 10. |

| 4 | After 3rd negative clock edge | 세 번째 하강 클럭 에지를 적용하면 FF-A가 0에서 1로 전환되지만 FF-B에 대한 상태 변경은 없습니다. 세 번째 클럭 펄스 후 Q B Q A = 11. |

| 5 | After 4th negative clock edge | 다음 클럭 펄스 를 적용하면 Q B 도 1에서 0으로 변경되므로 Q A 는 1에서 0으로 변경됩니다. 네 번째 클럭 펄스 이후 Q B Q A = 00. |

카운터 분류

계산이 진행되는 방식에 따라 동기식 또는 비동기식 카운터는 다음과 같이 분류됩니다.

- 업 카운터

- 다운 카운터

- 업 / 다운 카운터

UP / DOWN 카운터

업 카운터와 다운 카운터를 결합하여 UP / DOWN 카운터를 얻습니다. 모드 제어 (M) 입력도 제공되어 업 또는 다운 모드를 선택합니다. 업 / 다운 작동을 위해서는 각 플립 플롭 쌍 사이에 조합 회로를 설계하고 사용해야합니다.

- 업 / 다운 카운터 유형

- 위 / 아래 리플 카운터

- UP / DOWN 동기 카운터

위 / 아래 리플 카운터

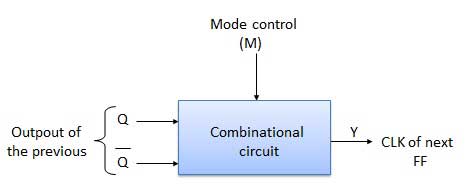

UP / DOWN 리플 카운터에서 모든 FF는 토글 모드에서 작동합니다. 따라서 T 플립 플롭 또는 JK 플립 플롭이 사용됩니다. LSB 플립 플롭은 클럭을 직접 수신합니다. 그러나 다른 모든 FF에 대한 클럭은 이전 FF의 (Q = Q bar) 출력에서 얻습니다.

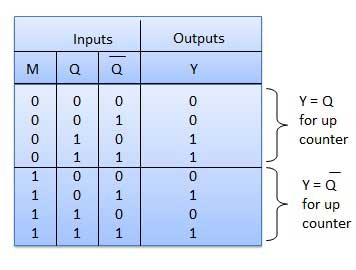

UP counting mode (M=0)− 업 카운팅을 달성하려면 선행 FF의 Q 출력이 다음 단계의 클록에 연결됩니다. 이 모드의 경우 모드 선택 입력 M은 논리 0 (M = 0)에 있습니다.

DOWN counting mode (M=1)− M = 1이면 이전 FF의 Q bar 출력이 다음 FF에 연결됩니다. 이것은 계수 모드에서 카운터를 작동합니다.

예

3 비트 바이너리 업 / 다운 리플 카운터.

3 비트-따라서 3 개의 FF가 필요합니다.

UP / DOWN-따라서 모드 제어 입력이 필수적입니다.

리플 업 카운터의 경우 이전 FF의 Q 출력은 다음 FF의 클록 입력에 연결됩니다.

리플 업 카운터의 경우 이전 FF의 Q 출력은 다음 FF의 클록 입력에 연결됩니다.

리플 다운 카운터의 경우 이전 FF의 Q 바 출력은 다음 FF의 클록 입력에 연결됩니다.

이전 FF의 Q 및 Q bar 출력의 선택이 모드 제어 입력 M에 의해 제어되도록하여 M = 0이면 UP 카운팅을 수행합니다. 따라서 Q를 CLK에 연결하십시오. M = 1이면 DOWN 카운팅. 따라서 Q bar를 CLK에 연결하십시오.

블록 다이어그램

진실 테이블

조작

| SN | 질환 | 조작 |

|---|---|---|

| 1 | Case 1 − With M = 0 (Up counting mode) | M = 0이고 M bar = 1이면 그림의 AND 게이트 1과 3입니다. AND 게이트 2와 4는 비활성화됩니다. 따라서 Q A 는 FF-B 의 클록 입력에 연결 되고 Q B 는 FF-C의 클록 입력에 연결됩니다. 이러한 연결은 일반 업 카운터의 연결과 동일합니다. 따라서 M = 0이면 회로가 업 카운터로 작동합니다. |

| 2 | Case 2: With M = 1 (Down counting mode) | M = 1이면 그림의 AND 게이트 2와 4. AND 게이트 1과 3은 비활성화되어 있습니다. 따라서 Q A 바는 FF-B 의 클럭 입력에 연결 되고 Q B 바는 FF-C의 클럭 입력에 연결됩니다. 이러한 연결은 다운 카운터를 생성합니다. 따라서 M = 1이면 회로가 다운 카운터로 작동합니다. |

모듈러스 카운터 (MOD-N 카운터)

2 비트 리플 카운터를 MOD-4 카운터라고하고 3 비트 리플 카운터를 MOD-8 카운터라고합니다. 따라서 일반적으로 n 비트 리플 카운터를 모듈로 N 카운터라고합니다. 여기서 MOD 번호 = 2n .

계수 유형

- 2 비트 업 또는 다운 (MOD-4)

- 3 비트 위로 또는 아래로 (MOD-8)

- 4 비트 업 또는 다운 (MOD-16)

카운터 적용

- 주파수 카운터

- 디지털 시계

- 시간 측정

- A to D 변환기

- 주파수 분배기 회로

- 디지털 삼각파 발생기.