디지털 레지스터

플립 플롭은 디지털 데이터를 저장하는 데 사용할 수있는 1 비트 메모리 셀입니다. 비트 수 측면에서 저장 용량을 늘리려면 플립 플롭 그룹을 사용해야합니다. 이러한 플립 플롭 그룹은Register. 그만큼n-bit register 구성됩니다 n 플립 플롭의 수와 그것은 저장할 수 있습니다 n-bit 워드.

레지스터의 이진 데이터는 한 플립 플롭에서 다른 플립 플롭으로 레지스터 내에서 이동할 수 있습니다. 이러한 데이터 전송을 허용하는 레지스터를 다음과 같이 호출합니다.shift registers. 시프트 레지스터에는 네 가지 작동 모드가 있습니다.

- 직렬 입력 직렬 출력

- 직렬 입력 병렬 출력

- 병렬 입력 직렬 출력

- 병렬 입력 병렬 출력

직렬 입력 직렬 출력

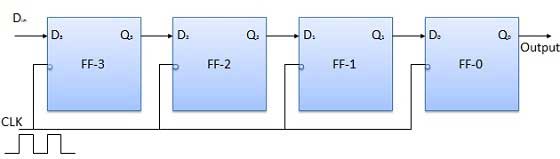

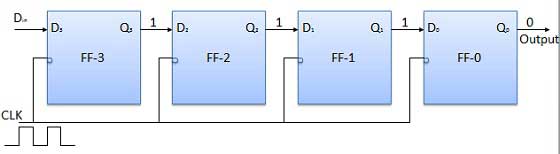

모든 플립 플롭이 초기에 리셋 조건에 있도록합니다. 즉 Q 3 = Q 2 = Q 1 = Q 0 = 0입니다. 레지스터에 4 비트 이진 숫자 1 1 1 1이 입력되면이 숫자는 다음과 같아야합니다. 적용DinLSB 비트가 먼저 적용된 비트. FF-3 즉 D 3 의 D 입력은 직렬 데이터 입력에 연결됩니다.Din. FF-3의 출력, 즉 Q 3 은 다음 플립 플롭, 즉 D 2 의 입력에 연결됩니다 .

블록 다이어그램

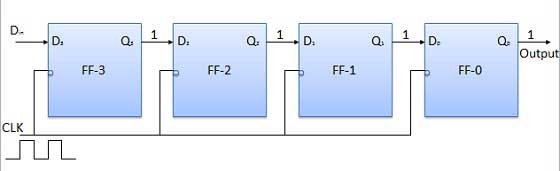

조작

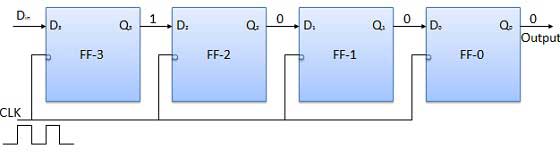

클럭 신호를 적용하기 전에 Q 3 Q 2 Q 1 Q 0 = 0000으로하고 D 에 입력 할 숫자의 LSB 비트 를 . 따라서 D in = D 3 = 1. 시계를 적용합니다. 클록의 첫 번째 하강 에지에서 FF-3이 설정되고 레지스터에 저장된 워드는 Q 3 Q 2 Q 1 Q 0 = 1000입니다.

에서 D 에 다음 비트를 적용합니다 . 따라서 D in = 1입니다. 클럭의 다음 네거티브 에지에 도달하자마자 FF-2가 설정되고 저장된 워드가 Q 3 Q 2 Q 1 Q 0 = 1100으로 변경됩니다.

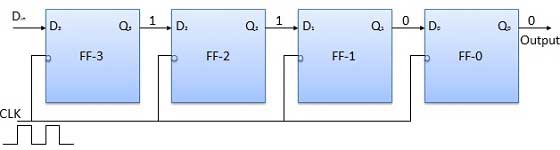

저장 될 다음 비트를 적용합니다 . 즉 1에서 D in . 클럭 펄스를 적용합니다. 세 번째 네거티브 클럭 에지에 도달하자마자 FF-1이 설정되고 출력이 Q 3 Q 2 Q 1 Q 0 = 1110 으로 수정됩니다 .

마찬가지로 D in = 1이고 네 번째 음의 클럭 에지가 도착하면 레지스터에 저장된 워드는 Q 3 Q 2 Q 1 Q 0 = 1111입니다.

진실 테이블

파형

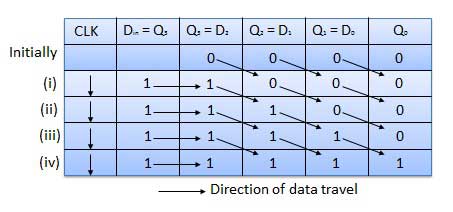

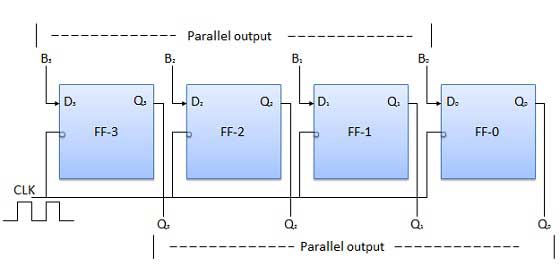

직렬 입력 병렬 출력

이러한 유형의 작업에서 데이터는 직렬로 입력되고 병렬 방식으로 추출됩니다.

데이터는 비트 단위로로드됩니다. 데이터가로드되는 동안에는 출력이 비활성화됩니다.

데이터로드가 완료 되 자마자 모든 플립 플롭에는 필요한 데이터가 포함되며,로드 된 모든 데이터가 동시에 모든 출력 라인에서 사용 가능하도록 출력이 활성화됩니다.

4 비트 워드를로드하려면 4 클럭 사이클이 필요합니다. 따라서 SIPO 모드의 작동 속도는 SISO 모드의 속도와 동일합니다.

블록 다이어그램

병렬 입력 직렬 출력 (PISO)

데이터 비트는 병렬 방식으로 입력됩니다.

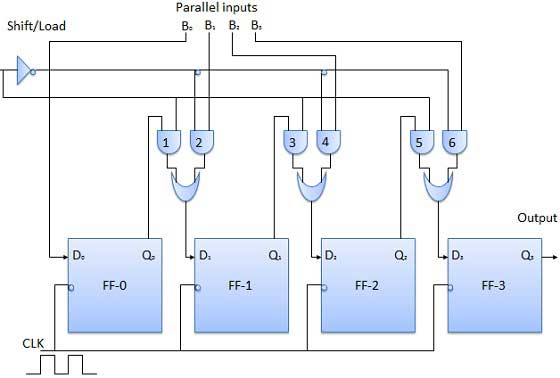

아래에 표시된 회로는 4 비트 병렬 입력 직렬 출력 레지스터입니다.

이전 플립 플롭의 출력은 조합 회로를 통해 다음 플립 플롭의 입력에 연결됩니다.

바이너리 입력 워드 B 0 , B 1 , B 2 , B 3 은 동일한 조합 회로를 통해 적용됩니다.

이 회로가 작동 할 수있는 두 가지 모드, 즉 시프트 모드 또는로드 모드가 있습니다.

로드 모드

시프트 /로드 바 라인이 낮 으면 (0) AND 게이트 2, 4 및 6이 활성화되어 B 1 , B 2 , B 3 비트를 해당 플립 플롭에 전달합니다. 클럭의 낮은 에지에서 이진 입력 B 0 , B 1 , B 2 , B 3 은 해당 플립 플롭에로드됩니다. 따라서 병렬 로딩이 발생합니다.

시프트 모드

변속 / 부하 막대 라인이 낮 으면 (1) AND 게이트 2, 4 및 6이 비활성화됩니다. 따라서 데이터의 병렬로드가 불가능합니다. 그러나 AND 게이트 1,3 및 5가 활성화됩니다. 따라서 클럭 펄스를 적용 할 때 데이터가 왼쪽에서 오른쪽으로 조금씩 이동합니다. 따라서 직렬 출력 작업에서 병렬이 발생합니다.

블록 다이어그램

병렬 입력 병렬 출력 (PIPO)

이 모드에서 4 비트 이진 입력 B 0 , B 1 , B 2 , B 3 은 4 개의 플립 플롭 의 데이터 입력 D 0 , D 1 , D 2 , D 3 각각에 적용됩니다. 네거티브 클럭 에지가 적용되는 즉시 입력 이진 비트가 플립 플롭에 동시에로드됩니다. 로드 된 비트는 출력 측에 동시에 나타납니다. 모든 비트를로드하려면 클럭 펄스 만 필요합니다.

블록 다이어그램

양방향 시프트 레지스터

이진수가 한 자리 왼쪽으로 이동하면 원래 숫자에 2를 곱하는 것과 같습니다. 마찬가지로 이진수가 오른쪽으로 한 자리 이동하면 원래 숫자를 2로 나눈 것과 같습니다.

따라서 시프트 레지스터를 사용하여 주어진 이진수를 곱하고 나누려면 데이터를 왼쪽 또는 오른쪽 방향으로 이동할 수 있어야합니다.

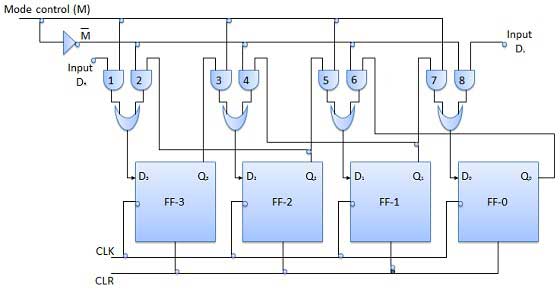

이러한 레지스터를 양방향 레지스터라고합니다. 4 비트 양방향 시프트 레지스터가 그림에 나와 있습니다.

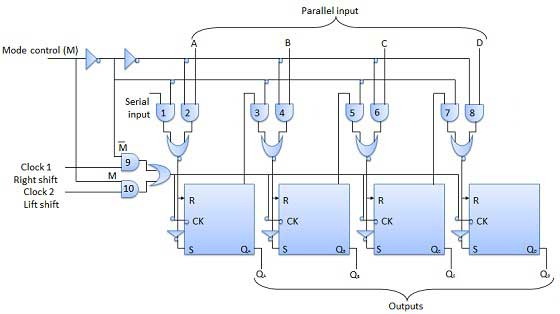

직렬 오른쪽 시프트 데이터 입력 DR과 모드 선택 입력 (M)과 함께 직렬 왼쪽 시프트 데이터 입력 DL의 두 개의 직렬 입력이 있습니다.

블록 다이어그램

조작

| SN | 질환 | 조작 |

|---|---|---|

| 1 | With M = 1 − Shift right operation | M = 1이면 AND 게이트 1, 3, 5 및 7이 활성화되고 나머지 AND 게이트 2, 4, 6 및 8은 비활성화됩니다. D R 의 데이터 는 클럭 펄스를 적용 할 때 FF-3에서 FF-0으로 비트 단위로 오른쪽으로 이동합니다. 따라서 M = 1이면 직렬 오른쪽 시프트 연산이 수행됩니다. |

| 2 | With M = 0 − Shift left operation | 모드 제어 M이 0에 연결되면 AND 게이트 2, 4, 6 및 8이 활성화되고 1, 3, 5 및 7은 비활성화됩니다. D L 의 데이터 는 클럭 펄스를 적용 할 때 FF-0에서 FF-3으로 비트 씩 왼쪽으로 이동합니다. 따라서 M = 0으로 직렬 오른쪽 시프트 연산을 얻습니다. |

범용 시프트 레지스터

데이터를 한 방향으로 만 시프트 할 수있는 시프트 레지스터를 단방향 시프트 레지스터라고합니다. 데이터를 양방향으로 시프트 할 수있는 시프트 레지스터를 양방향 시프트 레지스터라고합니다. 동일한 논리를 적용하여 데이터를 양방향으로 이동하고 병렬로로드 할 수있는 시프트 레지스터를 범용 시프트 레지스터라고합니다. 시프트 레지스터는 다음 작업을 수행 할 수 있습니다.

- 병렬 로딩

- 왼쪽 이동

- 오른쪽 이동

모드 제어 입력은 병렬 로딩 작동을 위해 로직 1에 연결되고 직렬 시프 팅을 위해 0에 연결됩니다. 모드 제어 핀이 접지에 연결된 상태에서 범용 시프트 레지스터는 양방향 레지스터로 작동합니다. 직렬 왼쪽 작동의 경우 입력은 그림과 같이 AND gate-1로가는 직렬 입력에 적용됩니다. 오른쪽 시프트 작동의 경우 직렬 입력이 D 입력에 적용됩니다.

블록 다이어그램