Rejestry cyfrowe

Flip-flop to 1-bitowa komórka pamięci, która może być używana do przechowywania danych cyfrowych. Aby zwiększyć pojemność pamięci pod względem liczby bitów, musimy użyć grupy przerzutników. Taka grupa przerzutników jest znana jakoRegister. Plikn-bit register będzie składać się z n liczba przerzutników i jest w stanie przechowywać plik n-bit słowo.

Dane binarne w rejestrze mogą być przenoszone w obrębie rejestru z jednego przerzutnika do drugiego. Rejestry, które umożliwiają takie przesyłanie danych, nazywane są jakoshift registers. Istnieją cztery tryby działania rejestru przesuwnego.

- Wejście szeregowe Wyjście szeregowe

- Szeregowe wyjście równoległe

- Szeregowe wyjście równoległe

- Wejście równoległe Wyjście równoległe

Wejście szeregowe Wyjście szeregowe

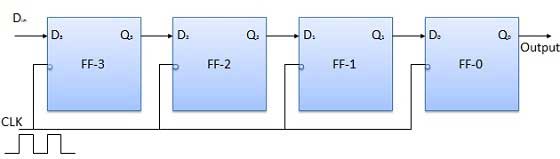

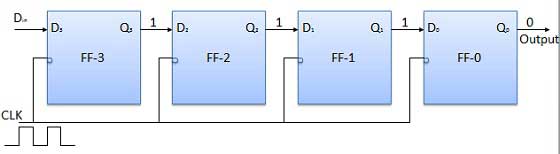

Niech wszystkie przerzutniki będą początkowo w stanie resetowania, tj. Q 3 = Q 2 = Q 1 = Q 0 = 0. Jeżeli do rejestru zostanie wprowadzona czterobitowa liczba binarna 1 1 1 1, liczba ta powinna być zastosowany doDinbit z bitem LSB zastosowanym jako pierwszy. Wejście D FF-3 tj. D 3 jest połączone z wejściem danych szeregowychDin. Wyjście FF-3 czyli Q 3 jest podłączone do wejścia kolejnego przerzutnika tj. D 2 i tak dalej.

Schemat blokowy

Operacja

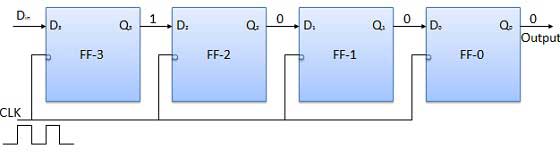

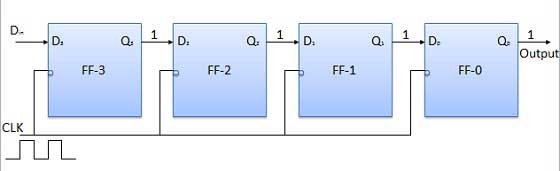

Przed przyłożeniem sygnału zegarowego niech Q 3 Q 2 Q 1 Q 0 = 0000 i zastosuj bit LSB numeru, który ma być wprowadzony do D in . Więc D in = D 3 = 1. Zastosuj zegar. Na pierwszym zboczu opadającym zegara ustawiany jest FF-3, a słowo przechowywane w rejestrze to Q 3 Q 2 Q 1 Q 0 = 1000.

Zastosuj następny bit do D in . Więc D in = 1. Gdy tylko trafi następny ujemny zbocze zegara, FF-2 ustawi się, a zapisane słowo zmieni się na Q 3 Q 2 Q 1 Q 0 = 1100.

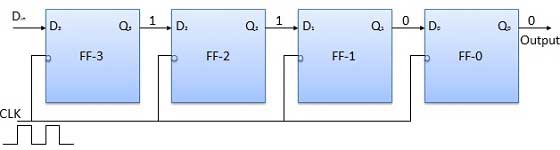

Zastosuj następny bit do zapisania, tj. Od 1 do D w . Zastosuj impuls zegarowy. Gdy tylko dojdzie do trzeciego ujemnego zbocza zegara, FF-1 zostanie ustawiony, a wyjście zostanie zmienione na Q 3 Q 2 Q 1 Q 0 = 1110.

Podobnie z D in = 1 i przy czwartym ujemnym zboczu zegara, przechowywane słowo w rejestrze to Q 3 Q 2 Q 1 Q 0 = 1111.

Tabela prawdy

Przebiegi

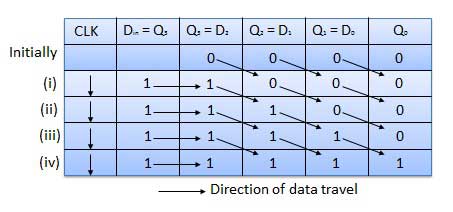

Szeregowe wyjście równoległe

W tego typu operacjach dane są wprowadzane szeregowo i równolegle pobierane.

Dane są ładowane bit po bicie. Wyjścia są wyłączone, dopóki dane są ładowane.

Gdy tylko ładowanie danych zostanie zakończone, wszystkie przerzutniki zawierają wymagane dane, wyjścia są włączone, aby wszystkie załadowane dane były dostępne na wszystkich liniach wyjściowych w tym samym czasie.

Do załadowania czterobitowego słowa potrzebne są 4 cykle zegara. Stąd szybkość działania trybu SIPO jest taka sama jak w trybie SISO.

Schemat blokowy

Wyjście szeregowe z wejściem równoległym (PISO)

Bity danych są wprowadzane równolegle.

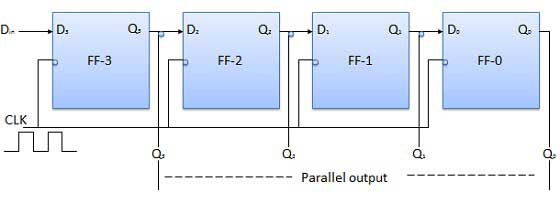

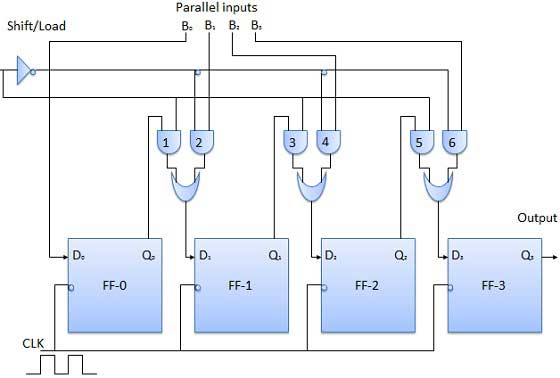

Obwód pokazany poniżej to czterobitowy szeregowy rejestr wejściowy.

Wyjście poprzedniego Flip Flopa jest podłączone do wejścia następnego poprzez obwód kombinacyjny.

Binarne słowo wejściowe B 0 , B 1 , B 2 , B 3 jest stosowane przez ten sam obwód kombinacyjny.

Istnieją dwa tryby, w których ten obwód może pracować, a mianowicie - tryb przesunięcia lub tryb obciążenia.

Tryb ładowania

Gdy linia paska przesunięcia / obciążenia jest niska (0), bramki AND 2, 4 i 6 stają się aktywne i przekazują bity B 1 , B 2 , B 3 do odpowiednich przerzutników. Przy niskim zboczu zegara, wejście binarne B 0 , B 1 , B 2 , B 3 zostanie załadowane do odpowiednich przerzutników. W ten sposób odbywa się równoległe ładowanie.

Tryb zmiany

Kiedy linia paska zmiany / obciążenia jest niska (1), bramki AND 2, 4 i 6 stają się nieaktywne. Stąd równoległe ładowanie danych staje się niemożliwe. Ale bramki AND 1, 3 i 5 stają się aktywne. Dlatego przesuwanie danych z lewej strony na prawą bit po bicie przy zastosowaniu impulsów zegara. W ten sposób ma miejsce równoległe działanie szeregowe.

Schemat blokowy

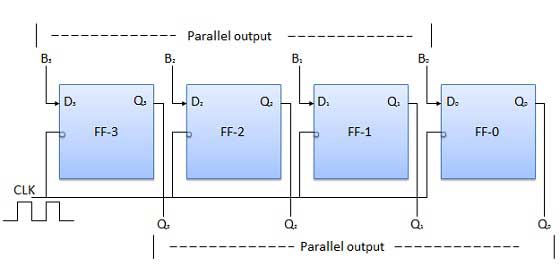

Wejście równoległe Wyjście równoległe (PIPO)

W tym trybie 4-bitowe wejście binarne B 0 , B 1 , B 2 , B 3 jest stosowane odpowiednio do wejść danych D 0 , D 1 , D 2 , D 3 czterech przerzutników. Gdy tylko zostanie przyłożone ujemne zbocze zegara, wejściowe bity binarne zostaną jednocześnie załadowane do przerzutników. Załadowane bity pojawią się jednocześnie na stronie wyjściowej. Do załadowania wszystkich bitów niezbędny jest tylko impuls zegarowy.

Schemat blokowy

Dwukierunkowy rejestr przesuwny

Jeśli liczba binarna zostanie przesunięta w lewo o jedną pozycję, jest to równoważne pomnożeniu liczby pierwotnej przez 2. Podobnie, jeśli liczba binarna zostanie przesunięta w prawo o jedną pozycję, to jest to równoważne podzieleniu liczby pierwotnej przez 2.

Dlatego jeśli chcemy użyć rejestru przesuwnego do pomnożenia i podzielenia podanej liczby binarnej, powinniśmy być w stanie przesunąć dane w lewo lub w prawo.

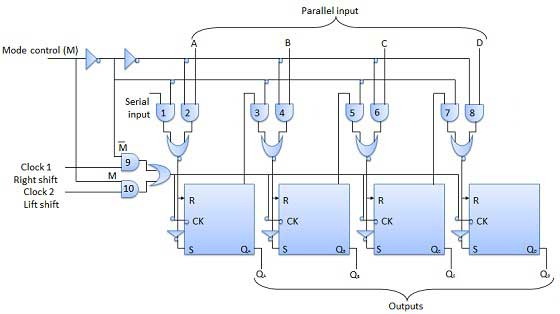

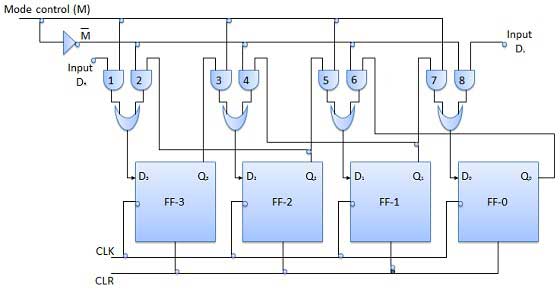

Taki rejestr nazywany jest rejestrem dwukierunkowym. Czterobitowy dwukierunkowy rejestr przesuwny pokazano na rys.

Istnieją dwa wejścia szeregowe, a mianowicie wejście danych szeregowego przesunięcia w prawo DR i wejście danych szeregowego przesunięcia w lewo DL wraz z wejściem wyboru trybu (M).

Schemat blokowy

Operacja

| SN | Stan: schorzenie | Operacja |

|---|---|---|

| 1 | With M = 1 − Shift right operation | Jeśli M = 1, wtedy bramki AND 1, 3, 5 i 7 są włączone, podczas gdy pozostałe bramki AND 2, 4, 6 i 8 będą wyłączone. Dane w D R są przesuwane w prawo bit po bicie z FF-3 do FF-0 przy zastosowaniu impulsów zegara. Zatem przy M = 1 otrzymujemy szeregową operację przesunięcia w prawo. |

| 2 | With M = 0 − Shift left operation | Gdy regulator trybu M jest podłączony do 0, wtedy bramki AND 2, 4, 6 i 8 są włączone, a 1, 3, 5 i 7 są wyłączone. Dane w DL są przesuwane w lewo bit po bicie od FF-0 do FF-3 przy zastosowaniu impulsów zegara. Zatem przy M = 0 otrzymujemy szeregową operację przesunięcia w prawo. |

Universal Shift Register

Rejestr przesuwny, który może przesuwać dane tylko w jednym kierunku, nazywany jest jednokierunkowym rejestrem przesuwnym. Rejestr przesuwny, który może przesuwać dane w obu kierunkach, nazywany jest dwukierunkowym rejestrem przesuwnym. Stosując tę samą logikę, rejestr przesuwny, który może przesuwać dane w obu kierunkach, a także ładować je równolegle, jest znany jako uniwersalny rejestr przesuwny. Rejestr przesuwny jest w stanie wykonać następujące operacje -

- Ładowanie równoległe

- Przesunięcie w lewo

- Właściwa zmiana biegów

Wejście sterujące trybem jest podłączone do logiki 1 dla operacji ładowania równoległego, a do 0 dla przesunięcia szeregowego. Gdy pin sterujący trybem jest podłączony do masy, uniwersalny rejestr przesuwny działa jako rejestr dwukierunkowy. W przypadku pracy szeregowej lewostronnej wejście jest podawane na wejście szeregowe, które przechodzi do bramki AND-1 pokazanej na rysunku. Podczas gdy dla operacji zmiany biegów w prawo wejście szeregowe jest przykładane do wejścia D.

Schemat blokowy