Projeto VLSI - Tecnologia FPGA

FPGA - Introdução

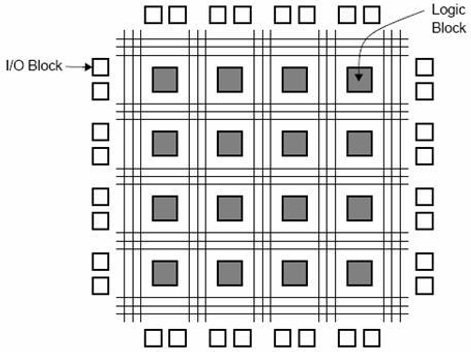

A forma completa de FPGA é "Field Programmable Gate Array”. Ele contém de dez mil a mais de um milhão de portas lógicas com interconexão programável. As interconexões programáveis estão disponíveis para usuários ou projetistas executarem determinadas funções facilmente. Um chip FPGA de modelo típico é mostrado na figura fornecida. Existem blocos de E / S, que são projetados e numerados de acordo com a função. Para cada módulo de composição de nível lógico, existemCLB’s (Configurable Logic Blocks).

CLB executa a operação lógica dada ao módulo. A interconexão entre CLB e blocos de E / S é feita com a ajuda de canais de roteamento horizontal, canais de roteamento vertical e PSM (Multiplexadores Programáveis).

O número de CLB que ele contém decide apenas a complexidade do FPGA. As funcionalidades dos CLBs e PSMs são projetadas por VHDL ou qualquer outra linguagem descritiva de hardware. Após a programação, CLB e PSM são colocados no chip e conectados entre si com canais de roteamento.

Vantagens

- Requer muito pouco tempo; começando do processo de design ao chip funcional.

- Nenhuma etapa de fabricação física está envolvida nisso.

- A única desvantagem é que é caro do que outros estilos.

Projeto de matriz de portão

o gate array (GA)ocupa o segundo lugar depois do FPGA, em termos de capacidade de prototipagem rápida. Embora a programação do usuário seja importante para a implementação do design do chip FPGA, o design e o processamento da máscara de metal são usados para GA. A implementação da matriz de portas requer um processo de fabricação de duas etapas.

A primeira fase resulta em uma série de transistores não comprometidos em cada chip GA. Esses chips não confirmados podem ser armazenados para personalização posterior, que é concluída definindo as interconexões de metal entre os transistores do array. A padronização das interconexões metálicas é feita no final do processo de fabricação do chip, de forma que o tempo de retorno ainda possa ser curto, de alguns dias a algumas semanas. A figura abaixo mostra as etapas básicas de processamento para a implementação do array de portas.

Plataformas de gate array típicas usam áreas dedicadas chamadas canais, para roteamento entre células entre linhas ou colunas de transistores MOS. Eles simplificam as interconexões. Os padrões de interconexão que executam portas lógicas básicas são armazenados em uma biblioteca, que pode então ser usada para personalizar linhas de transistores não confirmados de acordo com a netlist.

Na maioria dos GAs modernos, várias camadas de metal são usadas para o roteamento do canal. Com o uso de várias camadas interconectadas, o roteamento pode ser realizado nas áreas de células ativas; para que os canais de roteamento possam ser removidos como nos chips Sea-of-Gates (SOG). Aqui, toda a superfície do chip é coberta com transistores nMOS e pMOS não comprometidos. Os transistores vizinhos podem ser personalizados usando uma máscara de metal para formar portas lógicas básicas.

Para roteamento entre células, alguns dos transistores não comprometidos devem ser sacrificados. Este estilo de projeto resulta em mais flexibilidade para interconexões e geralmente em uma densidade mais alta. O fator de utilização do chip GA é medido pela área do chip usada dividida pela área total do chip. É maior que o FPGA e também a velocidade do chip.

Design baseado em células padrão

Um design baseado em célula padrão requer o desenvolvimento de um conjunto de máscara totalmente personalizado. A célula padrão também é conhecida como polycell. Nesta abordagem, todas as células lógicas comumente usadas são desenvolvidas, caracterizadas e armazenadas em uma biblioteca de células padrão.

Uma biblioteca pode conter algumas centenas de células, incluindo inversores, portas NAND, portas NOR, AOI complexo, portas OAI, travas D e flip-flops. Cada tipo de portão pode ser implementado em várias versões para fornecer capacidade de acionamento adequada para diferentes fan-outs. A porta do inversor pode ter tamanho padrão, tamanho duplo e tamanho quádruplo para que o projetista do chip possa selecionar o tamanho adequado para obter alta velocidade de circuito e densidade de layout.

Cada célula é caracterizada de acordo com várias categorias de caracterização diferentes, como,

- Tempo de atraso versus capacitância de carga

- Modelo de simulação de circuito

- Modelo de simulação de tempo

- Modelo de simulação de falha

- Dados de celular para local e rota

- Dados de máscara

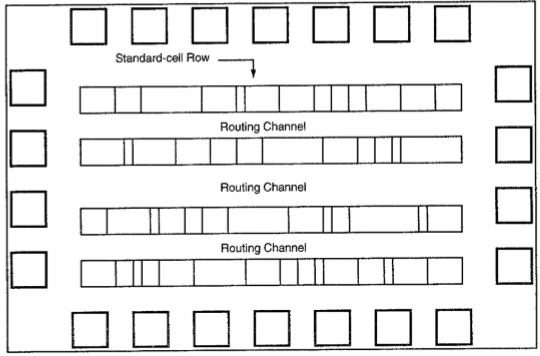

Para posicionamento automatizado das células e roteamento, cada layout de célula é projetado com uma altura fixa, de modo que várias células possam ser delimitadas lado a lado para formar linhas. Os trilhos de alimentação e de aterramento correm paralelos aos limites superior e inferior da célula. Assim, as células vizinhas compartilham um barramento de força comum e um barramento de aterramento comum. A figura mostrada abaixo é uma planta baixa para design baseado em células padrão.

Design totalmente personalizado

Em um design totalmente personalizado, todo o design da máscara é feito novo, sem o uso de qualquer biblioteca. O custo de desenvolvimento deste estilo de design está aumentando. Assim, o conceito de reutilização de design está se tornando famoso para reduzir o tempo do ciclo de design e o custo de desenvolvimento.

O design personalizado completo mais difícil pode ser o design de uma célula de memória, seja ela estática ou dinâmica. Para design de chip lógico, uma boa negociação pode ser obtida usando uma combinação de diferentes estilos de design no mesmo chip, ou seja, células padrão, células de caminho de dados eprogrammable logic arrays (PLAs).

Na prática, o designer faz o layout personalizado completo, ou seja, a geometria, orientação e colocação de cada transistor. A produtividade do projeto geralmente é muito baixa; normalmente algumas dezenas de transistores por dia, por designer. No CMOS VLSI digital, o design totalmente personalizado dificilmente é usado devido ao alto custo de mão de obra. Esses estilos de design incluem o design de produtos de alto volume, como chips de memória, microprocessadores de alto desempenho e FPGA.