Projeto VLSI - Introdução ao VHDL

VHDL significa linguagem de descrição de hardware de circuito integrado de altíssima velocidade. É uma linguagem de programação usada para modelar um sistema digital por fluxo de dados, estilo comportamental e estrutural de modelagem. Esta linguagem foi introduzida pela primeira vez em 1981 para o departamento de defesa (DoD) sob o programa VHSIC.

Descrevendo um Design

Em VHDL, uma entidade é usada para descrever um módulo de hardware. Uma entidade pode ser descrita usando,

- Declaração de entidade

- Architecture

- Configuration

- Declaração do pacote

- Corpo da embalagem

Vamos ver o que é isso?

Declaração de Entidade

Ele define os nomes, sinais de entrada e saída e modos de um módulo de hardware.

Syntax -

entity entity_name is

Port declaration;

end entity_name;Uma declaração de entidade deve começar com 'entidade' e terminar com palavras-chave 'fim'. A direção será entrada, saída ou entrada.

| Dentro | A porta pode ser lida |

| Fora | A porta pode ser escrita |

| Inout | A porta pode ser lida e escrita |

| Amortecedor | A porta pode ser lida e escrita, pode ter apenas uma fonte. |

Architecture -

A arquitetura pode ser descrita usando um estilo estrutural, de fluxo de dados, comportamental ou misto.

Syntax -

architecture architecture_name of entity_name

architecture_declarative_part;

begin

Statements;

end architecture_name;Aqui, devemos especificar o nome da entidade para a qual estamos escrevendo o corpo da arquitetura. As instruções de arquitetura devem estar dentro das palavras-chave 'begin' e 'énd'. A parte declarativa da arquitetura pode conter variáveis, constantes ou declaração de componente.

Modelagem de Fluxo de Dados

Neste estilo de modelagem, o fluxo de dados através da entidade é expresso usando sinal simultâneo (paralelo). As instruções simultâneas em VHDL são WHEN e GENERATE.

Além deles, atribuições usando apenas operadores (AND, NOT, +, *, sll, etc.) também podem ser usadas para construir código.

Finalmente, um tipo especial de atribuição, chamado BLOCK, também pode ser empregado nesse tipo de código.

No código simultâneo, o seguinte pode ser usado -

- Operators

- A instrução WHEN (WHEN / ELSE ou WITH / SELECT / WHEN);

- A instrução GENERATE;

- A declaração BLOCK

Modelagem Comportamental

Nesse estilo de modelagem, o comportamento de uma entidade como conjunto de instruções é executado sequencialmente na ordem especificada. Apenas as instruções colocadas dentro de um PROCESS, FUNCTION ou PROCEDURE são sequenciais.

PROCESSOS, FUNCTIONS e PROCEDURES são as únicas seções de código que são executadas sequencialmente.

No entanto, como um todo, qualquer um desses blocos ainda é concorrente com quaisquer outras instruções colocadas fora dele.

Um aspecto importante do código de comportamento é que ele não se limita à lógica sequencial. Na verdade, com ele, podemos construir circuitos sequenciais, bem como circuitos combinacionais.

As declarações de comportamento são IF, WAIT, CASE e LOOP. VARIÁVEIS também são restritas e devem ser usadas apenas em código sequencial. VARIABLE nunca pode ser global, portanto, seu valor não pode ser transmitido diretamente.

Modelagem Estrutural

Nesta modelagem, uma entidade é descrita como um conjunto de componentes interconectados. Uma instrução de instanciação de componente é uma instrução simultânea. Portanto, a ordem dessas declarações não é importante. O estilo estrutural de modelagem descreve apenas uma interconexão de componentes (vistos como caixas pretas), sem implicar em qualquer comportamento dos próprios componentes nem da entidade que eles representam coletivamente.

Na modelagem estrutural, o corpo da arquitetura é composto de duas partes - a parte declarativa (antes do início da palavra-chave) e a parte da instrução (após o início da palavra-chave).

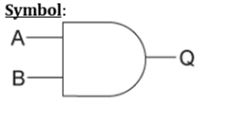

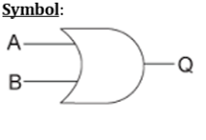

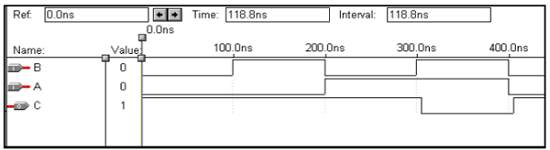

Operação lógica - E GATE

| X | Y | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity and1 is

port(x,y:in bit ; z:out bit);

end and1;

architecture virat of and1 is

begin

z<=x and y;

end virat;Formas de onda

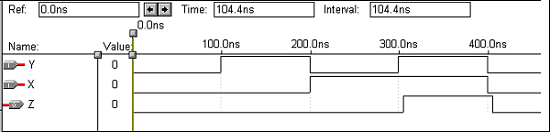

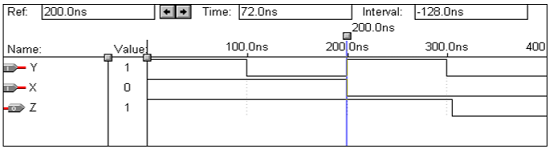

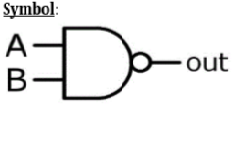

Operação lógica - OR Gate

| X | Y | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity or1 is

port(x,y:in bit ; z:out bit);

end or1;

architecture virat of or1 is

begin

z<=x or y;

end virat;Formas de onda

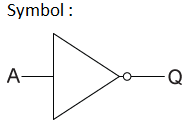

Operação lógica - NÃO Gate

| X | Y |

|---|---|

| 0 | 1 |

| 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity not1 is

port(x:in bit ; y:out bit);

end not1;

architecture virat of not1 is

begin

y<=not x;

end virat;Formas de onda

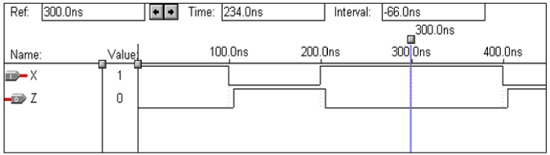

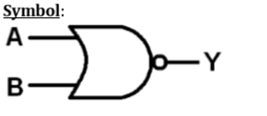

Operação lógica - NAND Gate

| X | Y | z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity nand1 is

port(a,b:in bit ; c:out bit);

end nand1;

architecture virat of nand1 is

begin

c<=a nand b;

end virat;Formas de onda

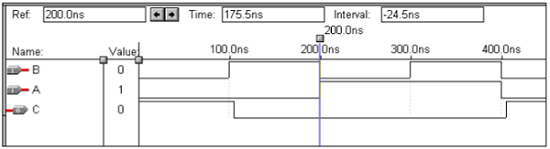

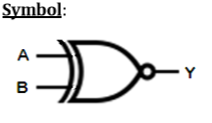

Operação lógica - Porta NOR

| X | Y | z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity nor1 is

port(a,b:in bit ; c:out bit);

end nor1;

architecture virat of nor1 is

begin

c<=a nor b;

end virat;Formas de onda

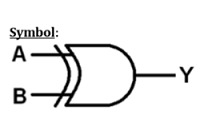

Operação lógica - XOR Gate

| X | Y | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity xor1 is

port(a,b:in bit ; c:out bit);

end xor1;

architecture virat of xor1 is

begin

c<=a xor b;

end virat;Formas de onda

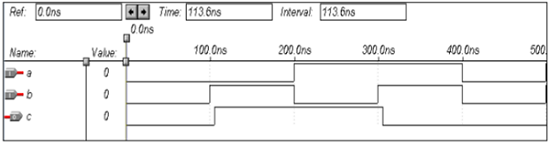

Operação lógica - X-NOR Gate

| X | Y | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity xnor1 is

port(a,b:in bit ; c:out bit);

end xnor1;

architecture virat of xnor1 is

begin

c<=not(a xor b);

end virat;Formas de onda