Projeto VLSI - Inversor MOS

O inversor é verdadeiramente o núcleo de todos os designs digitais. Uma vez que sua operação e propriedades são claramente compreendidas, o projeto de estruturas mais complexas, como portas NAND, somadores, multiplicadores e microprocessadores, é bastante simplificado. O comportamento elétrico desses circuitos complexos pode ser quase completamente derivado extrapolando os resultados obtidos para inversores.

A análise de inversores pode ser estendida para explicar o comportamento de portas mais complexas como NAND, NOR ou XOR, que por sua vez formam os blocos de construção para módulos como multiplicadores e processadores. Neste capítulo, nos concentramos em uma única encarnação da porta do inversor, sendo o inversor CMOS estático - ou, em resumo, o inversor CMOS. Este é certamente o mais popular atualmente e, portanto, merece nossa atenção especial.

Princípio da Operação

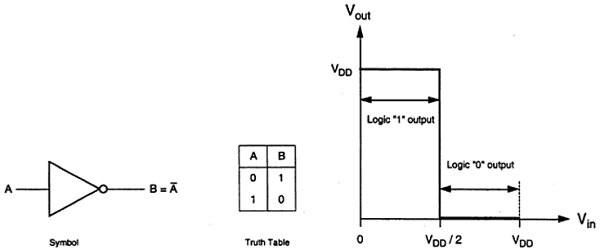

O símbolo lógico e a tabela verdade do inversor ideal são mostrados na figura abaixo. Aqui, A é a entrada e B é a saída invertida representada por suas tensões de nó. Usando a lógica positiva, o valor booleano da lógica 1 é representado por V dd e a lógica 0 é representada por 0. V th é a tensão limite do inversor, que é V dd / 2, onde V dd é a tensão de saída.

A saída é comutada de 0 para V dd quando a entrada é menor que Vth . Portanto, para 0 <V em <V, a saída é igual à entrada lógica 0 e Vth <V em <V dd é igual à entrada lógica 1 do inversor.

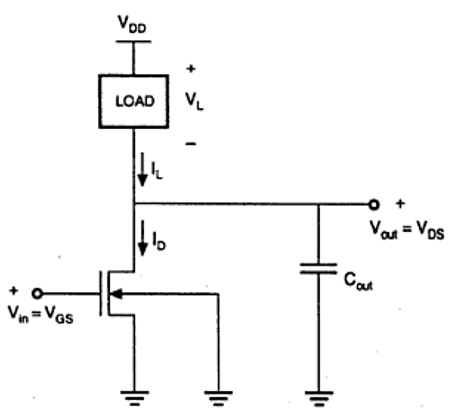

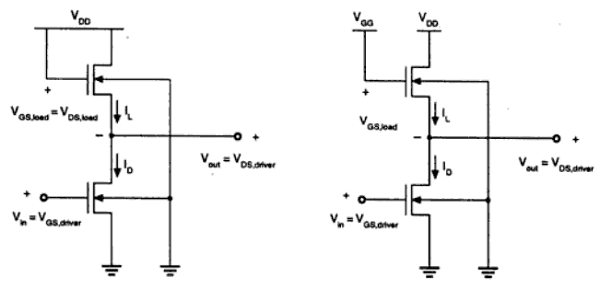

As características mostradas na figura são ideais. A estrutura generalizada do circuito de um inversor nMOS é mostrada na figura abaixo.

A partir da figura dada, podemos ver que a tensão de entrada do inversor é igual à tensão de porta para fonte do transistor nMOS e a tensão de saída do inversor é igual à tensão de dreno para fonte do transistor nMOS. A tensão da fonte para o substrato do nMOS também é chamada de driver para transistor que é aterrado; então V SS = 0. O nó de saída é conectado com uma capacitância concentrada usada para VTC.

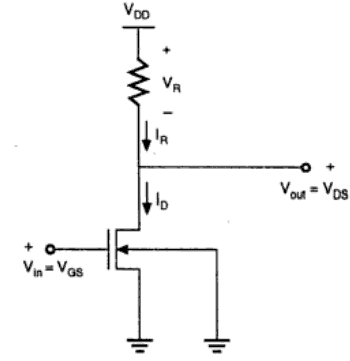

Inversor de carga resistiva

A estrutura básica de um inversor de carga resistiva é mostrada na figura abaixo. Aqui, o tipo de aprimoramento nMOS atua como o transistor de driver. A carga é constituída por uma simples resistência R linear L . A fonte de alimentação do circuito é V DD e a corrente de dreno que D é igual à corrente de carga I R .

Operação de Circuito

Quando a entrada do transistor driver é menor do que a tensão limite V TH (V in <V TH ), o transistor driver está na região de corte e não conduz nenhuma corrente. Portanto, a queda de tensão no resistor de carga é ZERO e a tensão de saída é igual a V DD . Agora, quando a tensão de entrada aumenta ainda mais, o transistor do driver começará a conduzir a corrente diferente de zero e o nMOS vai para a região de saturação.

Matematicamente,

$$ I_ {D} = \ frac {K_ {n}} {2} \ esquerda [V_ {GS} -V_ {TO} \ direita] ^ {2} $$

Aumentando ainda mais a tensão de entrada, o transistor driver entrará na região linear e a saída do transistor driver diminui.

$$ I_ {D} = \ frac {K_ {n}} {2} 2 \ esquerda [V_ {GS} -V_ {TO} \ direita] V_ {DS} -V_ {DS} ^ {2} $$

O VTC do inversor de carga resistiva, mostrado abaixo, indica o modo de operação do transistor do driver e pontos de tensão.

Inversor com Carga MOSFET tipo N

A principal vantagem de usar o MOSFET como dispositivo de carga é que a área de silício ocupada pelo transistor é menor do que a área ocupada pela carga resistiva. Aqui, o MOSFET é carga ativa e o inversor com carga ativa oferece um melhor desempenho do que o inversor com carga resistiva.

Enhancement Load NMOS

Dois inversores com dispositivo de carga do tipo aprimoramento são mostrados na figura. O transistor de carga pode ser operado tanto na região de saturação quanto na região linear, dependendo da tensão de polarização aplicada ao seu terminal de porta. O inversor de carga de reforço saturado é mostrado na fig. (uma). Ela exige uma única alimentação de tensão e processo de fabricação simples e de modo V OH está limitado ao V DD - V T .

O inversor de carga de realce linear é mostrado na fig. (b). Sempre opera em região linear; então o nível V OH é igual a V DD .

O inversor de carga linear tem maior margem de ruído em comparação com o inversor de aprimoramento saturado. Mas, a desvantagem do inversor de realce linear é que ele requer duas fontes de alimentação separadas e ambos os circuitos sofrem de alta dissipação de energia. Portanto, os inversores de aprimoramento não são usados em nenhuma aplicação digital de grande escala.

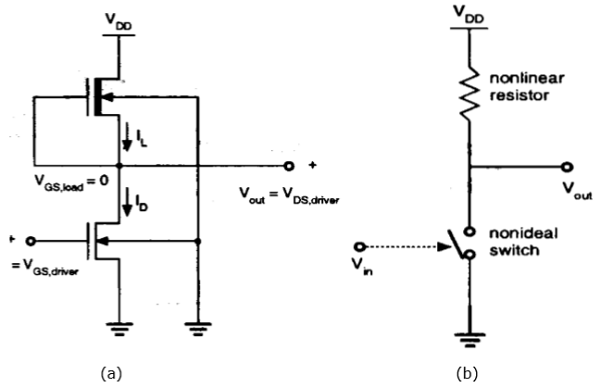

NMOS de carga de esgotamento

As desvantagens do inversor de carga de aprimoramento podem ser superadas usando o inversor de carga de depleção. Comparado com o inversor de carga de reforço, o inversor de carga de depleção requer mais algumas etapas de fabricação para que o implante de canal ajuste a tensão limite de carga.

As vantagens do inversor de carga de depleção são - transição VTC nítida, melhor margem de ruído, fonte de alimentação única e área de layout geral menor.

Conforme mostrado na figura, o portão e o terminal de origem da carga estão conectados; Portanto, V GS = 0. Assim, a tensão limite da carga é negativa. Conseqüentemente,

$$ V_ {GS, carga}> V_ {T, carga} $$ está satisfeito

Portanto, o dispositivo de carga sempre tem um canal de condução independente do nível de tensão de entrada e saída.

Quando o transistor de carga está na região de saturação, a corrente de carga é dada por

$$ I_ {D, carga} = \ frac {K_ {n, carga}} {2} \ esquerda [-V_ {T, carga} \ esquerda (V_ {saída} \ direita) \ direita] ^ {2} $ $

Quando o transistor de carga está na região linear, a corrente de carga é dada por

$$ I_ {D, carregar} = \ frac {K_ {n, carregar}} {2} \ left [2 \ left | V_ {T, carregar} \ left (V_ {out} \ right) \ right |. \ Left (V_ {DD} -V_ {out} \ right) - \ left (V_ {DD} -V_ {out} \ right) ) ^ {2} \ right] $$

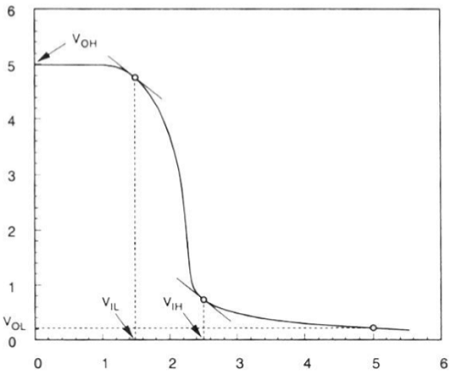

As características de transferência de tensão do inversor de carga de exaustão são mostradas na figura abaixo -

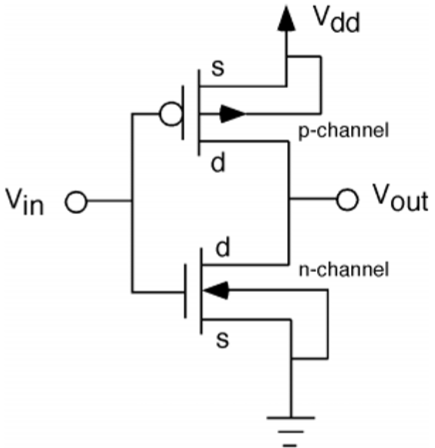

Inversor CMOS - Circuito, Operação e Descrição

O circuito do inversor CMOS é mostrado na figura. Aqui, os transistores nMOS e pMOS funcionam como transistores de driver; quando um transistor está LIGADO, o outro está DESLIGADO.

Esta configuração é chamada complementary MOS (CMOS). A entrada é conectada ao terminal da porta de ambos os transistores de forma que ambos possam ser acionados diretamente com tensões de entrada. O substrato do nMOS é conectado ao aterramento e o substrato do pMOS é conectado à fonte de alimentação, V DD .

Portanto, V SB = 0 para ambos os transistores.

$$ V_ {GS, n} = V_ {em} $$

$$ V_ {DS, n} = V_ {out} $$

E,

$$ V_ {GS, p} = V_ {em} -V_ {DD} $$

$$ V_ {DS, p} = V_ {saída} -V_ {DD} $$

Quando a entrada de nMOS é menor que a tensão de limiar (V in <V TO, n ), o nMOS é cortado e o pMOS está na região linear. Portanto, a corrente de dreno de ambos os transistores é zero.

$$ I_ {D, n} = I_ {D, p} = 0 $$

Portanto, a tensão de saída V OH é igual à tensão de alimentação.

$$ V_ {out} = V_ {OH} = V_ {DD} $$

Quando a tensão de entrada é maior que V DD + V TO, p , o transistor pMOS está na região de corte e o nMOS está na região linear, então a corrente de drenagem de ambos os transistores é zero.

$$ I_ {D, n} = I_ {D, p} = 0 $$

Portanto, a tensão de saída V OL é igual a zero.

$$ V_ {out} = V_ {OL} = 0 $$

O nMOS opera na região de saturação se V em > V TO e se as seguintes condições forem satisfeitas.

$$ V_ {DS, n} \ geq V_ {GS, n} -V_ {TO, n} $$

$$ V_ {out} \ geq V_ {in} -V_ {TO, n} $$

O pMOS opera na região de saturação se V em <V DD + V TO, p e se as seguintes condições forem satisfeitas.

$$ V_ {DS, p} \ leq V_ {GS, p} -V_ {TO, p} $$

$$ V_ {out} \ leq V_ {in} -V_ {TO, p} $$

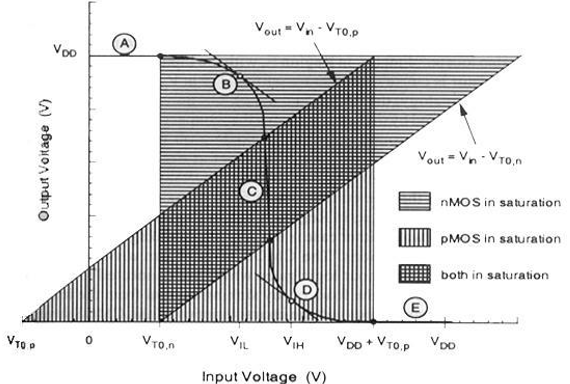

Para valores diferentes de tensões de entrada, as regiões de operação estão listadas abaixo para ambos os transistores.

| Região | V em | V fora | nMOS | pMOS |

|---|---|---|---|---|

| UMA | <V TO, n | V OH | Corte fora | Linear |

| B | V IL | Alto ≈ V OH | Saturação | Linear |

| C | V th | V th | Saturação | Saturação |

| D | V IH | Baixo ≈ V OL | Linear | Saturação |

| E | > (V DD + V TO, p ) | V OL | Linear | Corte fora |

O VTC do CMOS é mostrado na figura abaixo -