Цифро-аналоговые преобразователи

А Digital to Analog Converter (DAC)преобразует цифровой входной сигнал в аналоговый выходной сигнал. Цифровой сигнал представлен двоичным кодом, который представляет собой комбинацию битов 0 и 1. В этой главе подробно рассматриваются цифро-аналоговые преобразователи.

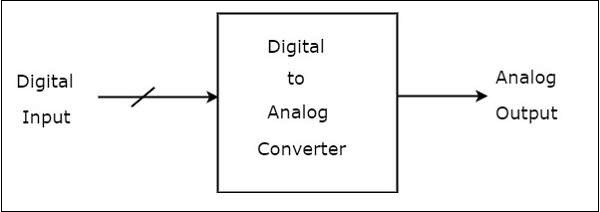

В block diagram ЦАП показан на следующем рисунке -

Цифро-аналоговый преобразователь (ЦАП) состоит из нескольких двоичных входов и одного выхода. В целомnumber of binary inputs ЦАП будет степенью двойки.

Типы ЦАП

Есть two types ЦАПов

- Взвешенный резисторный ЦАП

- Лестничный ЦАП R-2R

В этом разделе подробно обсуждаются эти два типа ЦАП -

Взвешенный резисторный ЦАП

ЦАП с взвешенным резистором создает аналоговый выход, который почти равен цифровому (двоичному) входу при использовании binary weighted resistorsв цепи инвертирующего сумматора. Короче говоря, ЦАП с двоичным взвешенным резистором называется ЦАП с взвешенным резистором.

В circuit diagram 3-битного двоично-взвешенного резисторного ЦАП показан на следующем рисунке -

Напомним, что биты двоичного числа могут иметь только одно из двух значений. т.е. либо 0, либо 1. Пусть3-bit binary inputэто $ b_ {2} b_ {1} b_ {0} $. Здесь биты $ b_ {2} $ и $ b_ {0} $ обозначаютMost Significant Bit (MSB) and Least Significant Bit (LSB) соответственно.

В digital switchesпоказанный на приведенном выше рисунке будет подключен к земле, когда соответствующие входные биты будут равны «0». Аналогичным образом, цифровые переключатели, показанные на рисунке выше будут соединены с отрицательным опорным напряжением, $ -V_ {R} $, когда соответствующие входные биты равны «1».

В приведенной выше схеме неинвертирующий входной терминал операционного усилителя подключен к земле. Это означает, что на неинвертирующую входную клемму операционного усилителя подается нулевое напряжение.

Согласно virtual short concept, напряжение на инвертирующем входном выводе операционного усилителя такое же, как напряжение на его неинвертирующем входном выводе. Таким образом, напряжение в узле инвертирующей входной клеммы будет равно нулю вольт.

В nodal equation в узле инвертирующего входного терминала:

$$ \ frac {0 + V_ {R} b_ {2}} {2 ^ {0} R} + \ frac {0 + V_ {R} b_ {1}} {2 ^ {1} R} + \ frac {0 + V_ {R} b_ {0}} {2 ^ {2} R} + \ frac {0-V_ {0}} {R_ {f}} = 0 $$

$$ => \ frac {V_ {0}} {R_ {f}} = \ frac {V_ {R} b_ {2}} {2 ^ {0} R} + \ frac {V_ {R} b_ {1 }} {2 ^ {1} R} + \ frac {V_ {R} b_ {0}} {2 ^ {2} R} $$

$$ => V_ {0} = \ frac {V_ {R} R_ {f}} {R} \ left \ {\ frac {b_ {2}} {2 ^ {0}} + \ frac {b_ {1 }} {2 ^ {1}} + \ frac {b_ {0}} {2 ^ {2}} \ right \} $$

Подставив, $ R = 2R_ {f} $ в приведенном выше уравнении.

$$ => V_ {0} = \ frac {V_ {R} R_ {f}} {2R_ {f}} \ left \ {\ frac {b_ {2}} {2 ^ {0}} + \ frac { b_ {1}} {2 ^ {1}} + \ frac {b_ {0}} {2 ^ {2}} \ right \} $$

$$ => V_ {0} = \ frac {V_ {R}} {2} \ left \ {\ frac {b_ {2}} {2 ^ {0}} + \ frac {b_ {1}} {2 ^ {1}} + \ frac {b_ {0}} {2 ^ {2}} \ right \} $$

Вышеприведенное уравнение представляет output voltage equation3-битного двоично-взвешенного резисторного ЦАП. Так как число битов три в двоичной (цифровой) вход, мы получим семь возможных значений выходного напряжения путем изменения двоичного входа от 000 до 111 для фиксированного опорного напряжения, $ V_ {R} $.

Мы можем написать generalized output voltage equation N-разрядного двоично-взвешенного резисторного ЦАП, как показано ниже, на основе уравнения выходного напряжения 3-разрядного двоично-взвешенного резисторного ЦАП.

$$ => V_ {0} = \ frac {V_ {R}} {2} \ left \ {\ frac {b_ {N-1}} {2 ^ {0}} + \ frac {b_ {N-2 }} {2 ^ {1}} + .... + \ frac {b_ {0}} {2 ^ {N-1}} \ right \} $$

В disadvantages ЦАП с двоичным взвешенным резистором выглядят следующим образом -

Разница между значениями сопротивления, соответствующими LSB и MSB, будет увеличиваться по мере увеличения количества бит, присутствующих на цифровом входе.

Трудно разработать более точные резисторы, поскольку количество битов, присутствующих на цифровом входе, увеличивается.

Лестничный ЦАП R-2R

Релейный ЦАП R-2R преодолевает недостатки ЦАП с дискретным взвешенным резистором. Как следует из названия, лестничный ЦАП R-2R выдает аналоговый выход, который почти равен цифровому (двоичному) входу при использованииR-2R ladder network в цепи инвертирующего сумматора.

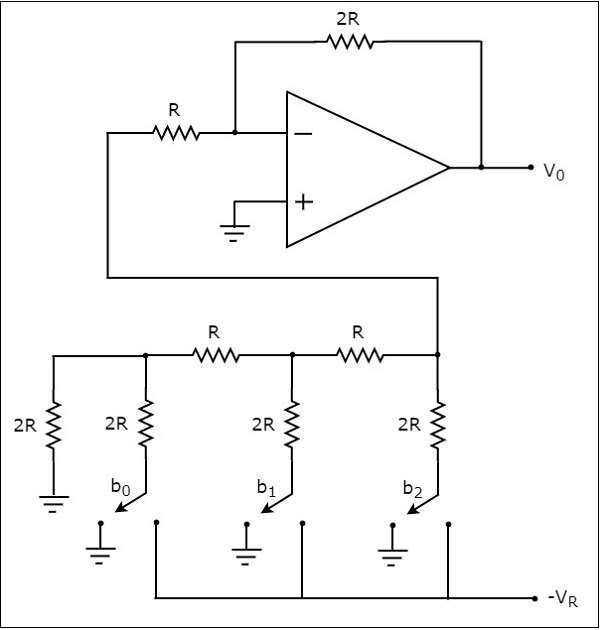

Вcircuit diagram3-битного лестничного ЦАП R-2R показан на следующем рисунке -

Напомним, что биты двоичного числа могут иметь только одно из двух значений. т.е. либо 0, либо 1. Пусть3-bit binary inputэто $ b_ {2} b_ {1} b_ {0} $. Здесь биты $ b_ {2} $ и $ b_ {0} $ обозначают старший значащий бит (MSB) и младший значащий бит (LSB) соответственно.

Цифровые переключатели, показанные на рисунке выше, будут подключены к земле, когда соответствующие входные биты будут равны «0». Аналогичным образом, цифровые переключатели, показанные на рисунке выше будут соединены с отрицательным опорным напряжением, $ -V_ {R} $, когда соответствующие входные биты равны «1».

Получить обобщенное уравнение выходного напряжения для лестничного ЦАП R-2R сложно. Но мы можем легко найти значения аналогового выходного напряжения R-2R Ladder DAC для отдельных комбинаций двоичных входов.

В advantages лестничного ЦАП R-2R следующие:

R-2R Ladder DAC содержит только два значения резистора: R и 2R. Таким образом, легко выбрать и спроектировать более точные резисторы.

Если на цифровом входе присутствует большее количество битов, то необходимо дополнительно включить необходимое количество секций R-2R.

Из-за вышеуказанных преимуществ лестничный ЦАП R-2R предпочтительнее ЦАП с двоично-взвешенным резистором.