АЦП прямого типа

Аналого-цифровой преобразователь (ADC)преобразует аналоговый сигнал в цифровой. Цифровой сигнал представлен двоичным кодом, который представляет собой комбинацию битов 0 и 1.

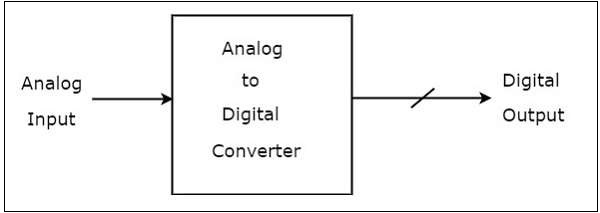

В block diagram АЦП показан на следующем рисунке -

Обратите внимание, что на приведенном выше рисунке аналого-цифровой преобразователь (ADC)состоит из одного аналогового входа и множества двоичных выходов. В общем, количество двоичных выходов АЦП будет степенью двух.

Есть two typesиз АЦП: АЦП прямого типа и АЦП косвенного типа. В этой главе подробно рассматриваются АЦП прямого типа.

Если АЦП выполняет аналого-цифровое преобразование напрямую, используя сгенерированный внутри эквивалентный цифровой (двоичный) код для сравнения с аналоговым входом, то он называется Direct type ADC.

Ниже приведены examples АЦП прямого типа -

- Тип счетчика АЦП

- АЦП последовательного приближения

- АЦП типа вспышки

В этом разделе подробно рассматриваются эти АЦП прямого типа.

Тип счетчика АЦП

А counter type ADC формирует цифровой выход, который приблизительно равен аналоговому входу за счет использования внутреннего счетчика.

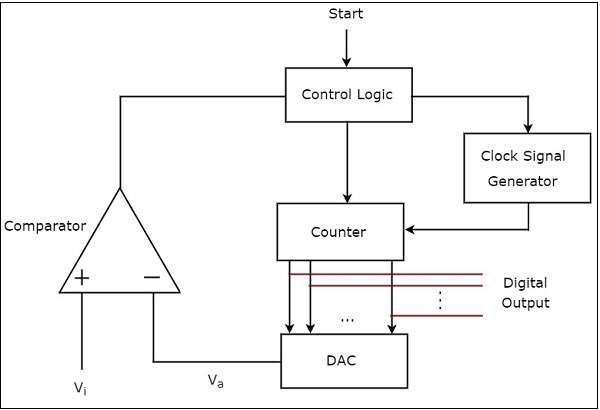

В block diagram АЦП счетного типа показан на следующем рисунке -

АЦП счетного типа в основном состоит из 5 блоков: генератора тактовых сигналов, счетчика, ЦАП, компаратора и управляющей логики.

В working АЦП счетного типа выглядит следующим образом -

В control logic сбрасывает счетчик и включает генератор тактовых сигналов для отправки тактовых импульсов на счетчик, когда он получил командный сигнал пуска.

В counterувеличивается на единицу для каждого тактового импульса, и его значение будет в двоичном (цифровом) формате. Этот выход счетчика применяется как вход ЦАП.

DACпреобразует полученный двоичный (цифровой) вход, который является выходом счетчика, в аналоговый выход. Компаратор сравнивает это аналоговое значение $ V_ {a} $ со значением внешнего аналогового входа $ V_ {i} $.

В output of comparator будет ‘1’пока больше чем. Операции, упомянутые в двух вышеупомянутых шагах, будут продолжаться до тех пор, пока управляющая логика получит «1» с выхода компаратора.

В output of comparator будет ‘0’когда $ V_ {i} $ меньше или равно $ V_ {a} $. Таким образом, логика управления получает «0» с выхода компаратора. Затем управляющая логика отключает генератор тактовых сигналов, чтобы он не отправлял тактовые импульсы на счетчик.

В этот момент выходные данные счетчика будут отображаться как digital output. Это почти эквивалентно соответствующему значению внешнего аналогового входа $ V_ {i} $.

АЦП последовательного приближения

А successive approximation type ADC формирует цифровой выход, который приблизительно равен аналоговому входу, используя метод последовательного приближения внутри.

В block diagram АЦП последовательного приближения показан на следующем рисунке

АЦП последовательного приближения в основном состоит из 5 блоков - генератора тактовых сигналов, регистра последовательного приближения (SAR), ЦАП, компаратора и логики управления.

В working АЦП последовательного приближения выглядит следующим образом -

В control logic сбрасывает все биты SAR и включает генератор тактовых сигналов для отправки тактовых импульсов в SAR, когда он получил командный сигнал запуска.

Двоичные (цифровые) данные, представленные в SARбудет обновляться для каждого тактового импульса в зависимости от выхода компаратора. Выход SAR используется как вход DAC.

DAC преобразует полученный цифровой вход, который является выходом SAR, в аналоговый выход. Компаратор сравнивает это аналоговое значение $ V_ {a} $ со значением внешнего аналогового входа $ V_ {i} $.

В output of a comparatorбудет '1', пока $ V_ {i} $ больше, чем $ V_ {a} $. Точно так же выход компаратора будет '0', когда $ V_ {i} $ меньше или равно $ V_ {a} $.

Операции, упомянутые в шагах выше, будут продолжаться до тех пор, пока цифровой выход не станет действующим.

Цифровой выход будет действительным, когда он почти эквивалентен соответствующему внешнему аналоговому входному значению $ V_ {i} $.

АЦП типа вспышки

А flash type ADCпроизводит эквивалентный цифровой выход для соответствующего аналогового входа в кратчайшие сроки. Следовательно, АЦП флэш-памяти - это самый быстрый АЦП.

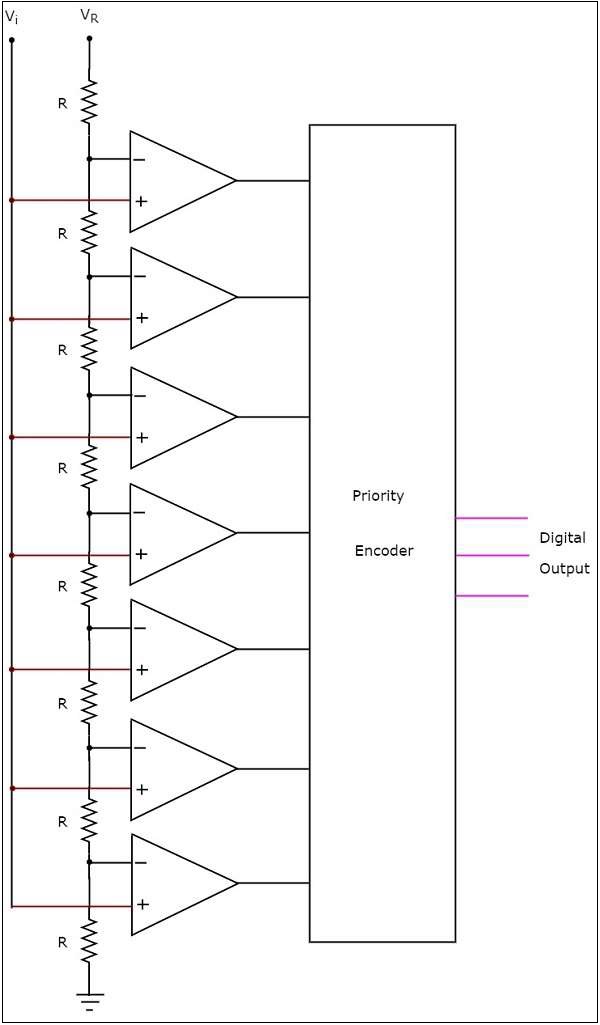

В circuit diagram 3-битного АЦП флэш-памяти показан на следующем рисунке -

3-битный АЦП флэш-памяти состоит из цепи делителя напряжения, 7 компараторов и кодировщика приоритета.

В working 3-битного АЦП флэш-памяти выглядит следующим образом.

В voltage divider networkсодержит 8 одинаковых резисторов. Опорное напряжение $ V_ {R} $ прикладываются через эту всю сеть по отношению к земле. Падение напряжения на каждом резисторе снизу вверх по отношению к земле будет кратным (от 1 до 8) $ \ frac {V_ {R}} {8} $.

Внешний input voltage$ V_ {i} $ применяется к неинвертирующему терминалу всех компараторов. Падение напряжения на каждом резисторе снизу вверх по отношению к земле подается на инвертирующий вывод компараторов снизу вверх.

Одновременно все компараторы сравнивают внешнее входное напряжение с падениями напряжения на соответствующей другой входной клемме. Это означает, что операции сравнения выполняются каждым компаратором.parallelly.

В output of the comparatorбудет '1', пока $ V_ {i} $ больше, чем падение напряжения на соответствующей другой входной клемме. Точно так же на выходе компаратора будет «0», когда $ V_ {i} $ меньше или равно падению напряжения на соответствующем другом входном выводе.

Все выходы компараторов подключены как входы priority encoder.Этот кодировщик приоритета выдает двоичный код (цифровой выход), который соответствует входу с высоким приоритетом, имеющему «1».

Следовательно, вывод кодировщика приоритета - не что иное, как двоичный эквивалент (digital output) внешнего аналогового входного напряжения, $ V_ {i} $.

АЦП флэш-типа используется в приложениях, где скорость преобразования аналогового ввода в цифровые данные должна быть очень высокой.