Проектирование СБИС - Цифровая система

Очень крупномасштабная интеграция (СБИС) - это процесс создания integrated circuit (IC) путем объединения тысяч transistorsв одну микросхему. СБИС началась в 1970-х годах, когда сложныеsemiconductor и communicationтехнологии разрабатывались. Вmicroprocessor это устройство СБИС.

До появления технологии СБИС большинство ИС имели ограниченный набор функций, которые они могли выполнять. Anelectronic circuit может состоять из CPU, ROM, RAM и другие glue logic. СБИС позволяет разработчикам интегральных схем объединить все это в одну микросхему.

Электронная промышленность достигла феноменального роста за последние несколько десятилетий, в основном благодаря быстрому развитию крупномасштабных технологий интеграции и приложений для проектирования систем. С появлением проектов очень крупномасштабной интеграции (СБИС) количество применений интегральных схем (ИС) в высокопроизводительных вычислениях, управлении, телекоммуникациях, обработке изображений и видео, а также в бытовой электронике растет очень быстрыми темпами.

Современные передовые технологии, такие как видео с высоким разрешением и низкой скоростью передачи данных и сотовая связь, предоставляют конечным пользователям изумительное количество приложений, вычислительную мощность и портативность. Ожидается, что эта тенденция будет быстро расти, что будет иметь очень важные последствия для проектирования СБИС и систем.

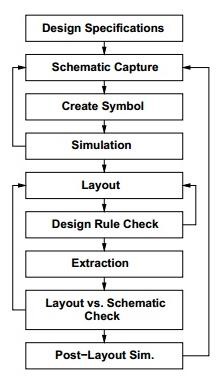

Схема проектирования СБИС

Схема проектирования микросхем СБИС показана на рисунке ниже. Различные уровни проектирования пронумерованы, а блоки показывают процессы в потоке проектирования.

Сначала идут технические характеристики, они абстрактно описывают функциональность, интерфейс и архитектуру цифровой микросхемы, которую необходимо разработать.

Затем создается описание поведения для анализа дизайна с точки зрения функциональности, производительности, соответствия заданным стандартам и других спецификаций.

Описание RTL выполняется с использованием HDL. Это RTL-описание моделируется для проверки функциональности. С этого момента нам понадобится помощь инструментов EDA.

RTL-описание затем преобразуется в список соединений на уровне ворот с использованием инструментов логического синтеза. Список соединений на уровне шлюза - это описание схемы с точки зрения вентилей и соединений между ними, которые выполнены таким образом, чтобы соответствовать спецификациям времени, мощности и площади.

Наконец, создается физический макет, который проверяется и отправляется на изготовление.

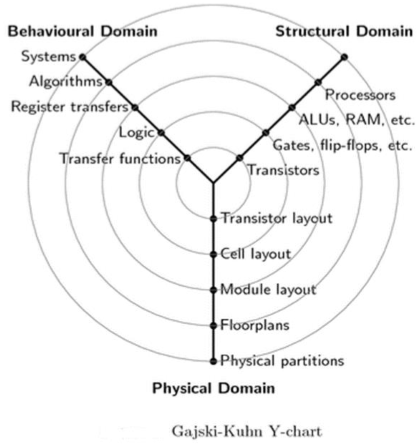

Диаграмма Y

Y-диаграмма Гайски-Куна - это модель, в которой отражены соображения при разработке полупроводниковых устройств.

Три области Y-диаграммы Гайски-Куна расположены на радиальных осях. Каждый из доменов можно разделить на уровни абстракции с помощью концентрических колец.

На верхнем уровне (внешнем кольце) мы рассматриваем архитектуру микросхемы; на нижних уровнях (внутренние кольца) мы последовательно дорабатываем дизайн до более детальной реализации -

Создание структурного описания из поведенческого достигается за счет процессов синтеза высокого уровня или логического синтеза.

Создание физического описания из структурного достигается путем синтеза компоновки.

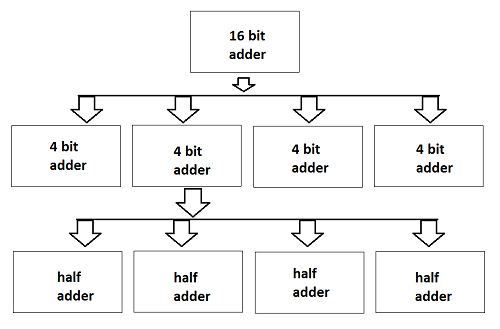

Иерархия дизайна - структурная

Иерархия дизайна включает принцип «разделяй и властвуй». Это не что иное, как разделение задачи на более мелкие задачи, пока они не достигнут простейшего уровня. Этот процесс является наиболее подходящим, поскольку последний этап эволюции дизайна стал настолько простым, что его изготовление стало проще.

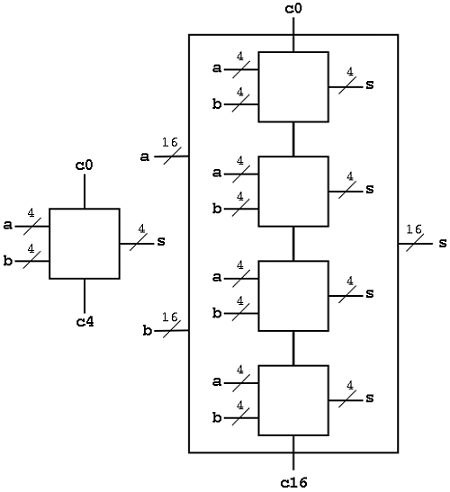

Мы можем спроектировать данную задачу в области процесса проектирования (поведенческой, структурной и геометрической). Чтобы понять это, давайте рассмотрим пример разработки 16-битного сумматора, как показано на рисунке ниже.

Здесь весь чип 16-битного сумматора разделен на четыре модуля 4-битных сумматоров. Далее, разделив 4-битный сумматор на 1-битный сумматор или полусумматор. Сложение 1 бита - это самый простой процесс проектирования, и его внутреннюю схему также легко изготовить на кристалле. Теперь, соединив все последние четыре сумматора, мы можем разработать 4-битный сумматор, а, двигаясь дальше, мы можем разработать 16-битный сумматор.