Проектирование СБИС - Краткое руководство

Очень крупномасштабная интеграция (СБИС) - это процесс создания integrated circuit (IC) путем объединения тысяч transistorsв одну микросхему. СБИС началась в 1970-х годах, когда сложныеsemiconductor и communicationтехнологии разрабатывались. Вmicroprocessor это устройство СБИС.

До появления технологии СБИС у большинства ИС был ограниченный набор функций, которые они могли выполнять. Anelectronic circuit может состоять из CPU, ROM, RAM и другие glue logic. СБИС позволяет разработчикам микросхем объединить все это в одну микросхему.

Электронная промышленность достигла феноменального роста за последние несколько десятилетий, в основном благодаря быстрому развитию крупномасштабных технологий интеграции и приложений для проектирования систем. С появлением конструкций очень крупномасштабной интеграции (СБИС) количество приложений интегральных схем (ИС) в высокопроизводительных вычислениях, системах управления, телекоммуникациях, обработке изображений и видео, а также в бытовой электронике растет очень быстрыми темпами.

Современные передовые технологии, такие как видео с высоким разрешением и низкой скоростью передачи данных и сотовая связь, предоставляют конечным пользователям изумительное количество приложений, вычислительную мощность и портативность. Ожидается, что эта тенденция будет быстро расти, что будет иметь очень важные последствия для проектирования СБИС и систем.

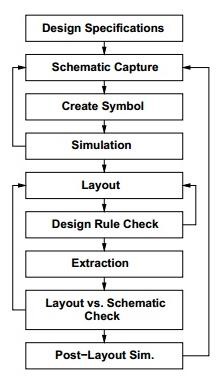

Схема проектирования СБИС

Схема проектирования микросхем СБИС показана на рисунке ниже. Различные уровни проектирования пронумерованы, а блоки показывают процессы в потоке проектирования.

Сначала идут технические характеристики, они абстрактно описывают функциональность, интерфейс и архитектуру цифровой микросхемы, которую необходимо разработать.

Затем создается описание поведения для анализа дизайна с точки зрения функциональности, производительности, соответствия заданным стандартам и других спецификаций.

Описание RTL выполняется с использованием HDL. Это описание RTL смоделировано для проверки функциональности. С этого момента нам понадобится помощь инструментов EDA.

RTL-описание затем преобразуется в список соединений на уровне ворот с использованием инструментов логического синтеза. Список соединений на уровне шлюза - это описание схемы с точки зрения вентилей и соединений между ними, которые выполнены таким образом, чтобы соответствовать спецификациям по времени, мощности и площади.

Наконец, создается физический макет, который проверяется и затем отправляется на изготовление.

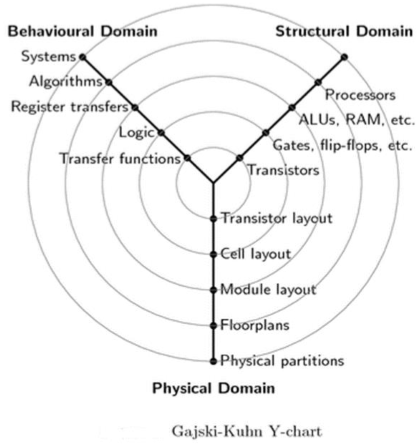

Диаграмма Y

Y-диаграмма Гайски-Куна - это модель, которая отражает соображения при проектировании полупроводниковых устройств.

Три области Y-диаграммы Гайски-Куна расположены на радиальных осях. Каждый из доменов можно разделить на уровни абстракции с помощью концентрических колец.

На верхнем уровне (внешнем кольце) мы рассматриваем архитектуру микросхемы; на нижних уровнях (внутренние кольца) мы последовательно дорабатываем дизайн до более детальной реализации -

Создание структурного описания из поведенческого достигается посредством процессов синтеза высокого уровня или логического синтеза.

Создание физического описания из структурного достигается путем синтеза компоновки.

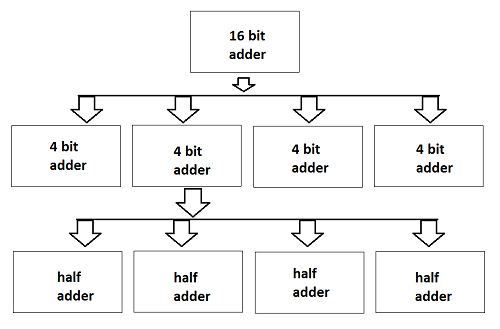

Иерархия дизайна - структурная

Иерархия дизайна включает принцип «разделяй и властвуй». Это не что иное, как разделение задачи на более мелкие задачи, пока они не достигнут простейшего уровня. Этот процесс является наиболее подходящим, потому что последний этап эволюции дизайна стал настолько простым, что его изготовление стало проще.

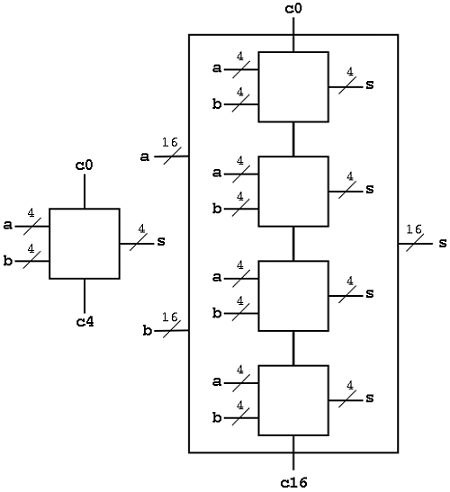

Мы можем спроектировать данную задачу в области процесса проектирования (поведенческой, структурной и геометрической). Чтобы понять это, давайте рассмотрим пример разработки 16-битного сумматора, как показано на рисунке ниже.

Здесь весь чип 16-битного сумматора разделен на четыре модуля 4-битных сумматоров. Далее, разделив 4-битный сумматор на 1-битный сумматор или полусумматор. Сложение 1 бита - это самый простой процесс проектирования, и его внутреннюю схему также легко изготовить на кристалле. Теперь, соединив все последние четыре сумматора, мы можем разработать 4-битный сумматор, а, двигаясь дальше, мы можем разработать 16-битный сумматор.

FPGA - Введение

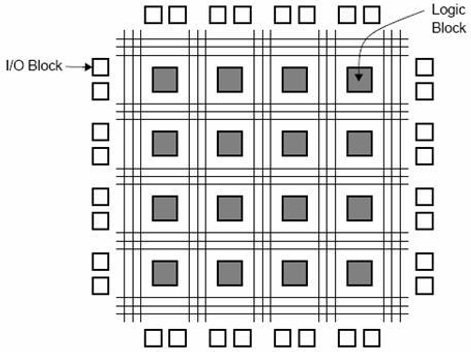

Полная форма FPGA является "Field Programmable Gate Array». Он содержит от десяти тысяч до более миллиона логических вентилей с программируемым соединением. Программируемые соединения доступны для пользователей или дизайнеров, чтобы легко выполнять заданные функции. Типичная модель микросхемы FPGA показана на данном рисунке. Существуют блоки ввода / вывода, которые спроектированы и пронумерованы в соответствии с функциями. Для каждого модуля композиции логического уровня существуютCLB’s (Configurable Logic Blocks).

CLB выполняет логическую операцию, заданную модулю. Взаимодействие между CLB и блоками ввода / вывода осуществляется с помощью каналов горизонтальной маршрутизации, каналов вертикальной маршрутизации и PSM (программируемых мультиплексоров).

Количество CLB, которое он содержит, решает только сложность FPGA. Функциональные возможности CLB и PSM разработаны с помощью VHDL или любого другого языка описания оборудования. После программирования CLB и PSM помещаются на микросхему и соединяются между собой каналами маршрутизации.

Преимущества

- На это требуется очень мало времени; начиная от процесса проектирования до функционального чипа.

- В нем нет никаких физических этапов производства.

- Единственный недостаток в том, что это дороже, чем в других стилях.

Дизайн решетки ворот

В gate array (GA)занимает второе место после FPGA по возможности быстрого прототипирования. В то время как пользовательское программирование важно для реализации проекта микросхемы FPGA, проектирование и обработка металлических масок используются для GA. Реализация массива вентилей требует двухэтапного производственного процесса.

Результатом первой фазы является массив незакрепленных транзисторов на каждой микросхеме GA. Эти незафиксированные микросхемы могут быть сохранены для дальнейшей настройки, которая завершается определением металлических межсоединений между транзисторами массива. Создание рисунка металлических межсоединений выполняется в конце процесса изготовления микросхемы, поэтому время восстановления может быть коротким, от нескольких дней до нескольких недель. На приведенном ниже рисунке показаны основные этапы обработки для реализации вентильной матрицы.

Типичные платформы вентильных матриц используют выделенные области, называемые каналами, для межячейковой маршрутизации между строками или столбцами МОП-транзисторов. Они упрощают межсоединения. Шаблоны соединений, которые выполняют основные логические элементы, хранятся в библиотеке, которую затем можно использовать для настройки строк незафиксированных транзисторов в соответствии со списком соединений.

В большинстве современных GA для маршрутизации каналов используется несколько металлических слоев. С использованием нескольких взаимосвязанных уровней маршрутизация может быть достигнута по активным областям ячеек; так что каналы маршрутизации могут быть удалены, как в микросхемах Sea-of-Gates (SOG). Здесь вся поверхность чипа покрыта незафиксированными транзисторами nMOS и pMOS. Соседние транзисторы можно настроить с помощью металлической маски для формирования основных логических вентилей.

Для межячейковой маршрутизации некоторые незафиксированные транзисторы должны быть принесены в жертву. Этот стиль дизайна обеспечивает большую гибкость для соединений и, как правило, более высокую плотность. Коэффициент использования микросхемы GA измеряется делением используемой площади кристалла на общую площадь кристалла. Он выше, чем у ПЛИС, как и скорость чипа.

Стандартный дизайн на основе ячеек

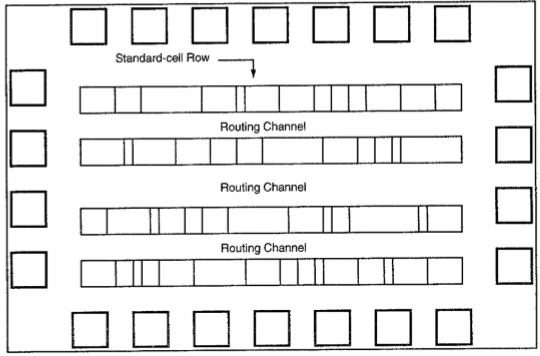

Стандартный дизайн на основе ячеек требует разработки полного настраиваемого набора масок. Стандартная ячейка также известна как поликлетка. При таком подходе все обычно используемые логические ячейки разрабатываются, характеризуются и хранятся в стандартной библиотеке ячеек.

Библиотека может содержать несколько сотен ячеек, включая инверторы, вентили NAND, вентили NOR, сложные AOI, вентили OAI, D-защелки и триггеры. Каждый тип ворот может быть реализован в нескольких версиях, чтобы обеспечить адекватную управляемость для различных разветвлений. Затвор инвертора может иметь стандартный, двойной и четырехкратный размер, чтобы разработчик микросхемы мог выбрать правильный размер для получения высокой скорости схемы и плотности размещения.

Каждая ячейка характеризуется несколькими различными категориями характеристик, такими как,

- Время задержки в зависимости от емкости нагрузки

- Имитационная модель схемы

- Временная имитационная модель

- Имитационная модель неисправности

- Данные ячеек для места и маршрута

- Данные маски

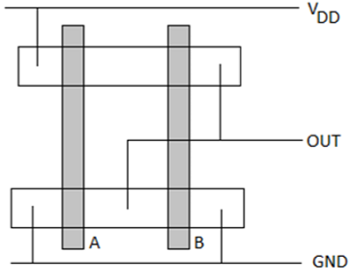

Для автоматического размещения ячеек и маршрутизации каждый макет ячеек имеет фиксированную высоту, так что несколько ячеек могут быть ограничены бок о бок для формирования строк. Шины питания и заземления проходят параллельно верхней и нижней границам ячейки. Таким образом, соседние ячейки имеют общую шину питания и общую шину заземления. На рисунке, показанном ниже, показан план для проектирования на основе стандартных ячеек.

Полный индивидуальный дизайн

В полностью индивидуальном дизайне весь дизайн маски создается новым без использования какой-либо библиотеки. Стоимость разработки этого стиля дизайна растет. Таким образом, становится популярной концепция повторного использования дизайна, позволяющая сократить время цикла проектирования и стоимость разработки.

Самым сложным полностью нестандартным дизайном может быть конструкция ячейки памяти, будь то статическая или динамическая. Для проектирования логической микросхемы хорошее согласование может быть достигнуто с использованием комбинации различных стилей проектирования на одной микросхеме, т. Е. Стандартных ячеек, ячеек тракта данных иprogrammable logic arrays (PLAs).

Практически дизайнер полностью настраивает компоновку, то есть геометрию, ориентацию и размещение каждого транзистора. Продуктивность проектирования обычно очень низкая; обычно несколько десятков транзисторов в день на одного разработчика. В цифровых CMOS VLSI полностью нестандартная конструкция практически не используется из-за высокой стоимости рабочей силы. Эти стили дизайна включают в себя проектирование продуктов большого объема, таких как микросхемы памяти, высокопроизводительные микропроцессоры и FPGA.

Технология комплементарных полевых МОП-транзисторов (CMOS) широко используется сегодня для формирования схем в многочисленных и разнообразных приложениях. Современные компьютеры, процессоры и сотовые телефоны используют CMOS благодаря нескольким ключевым преимуществам. CMOS обеспечивает низкое рассеивание мощности, относительно высокую скорость, высокий запас шума в обоих состояниях и будет работать в широком диапазоне входных и исходных напряжений (при условии, что напряжение источника фиксировано)

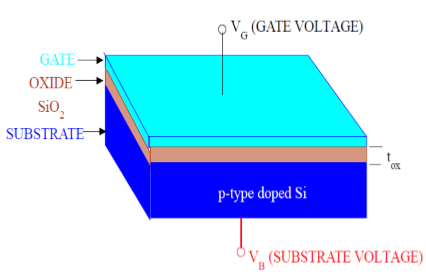

Для процессов, которые мы будем обсуждать, доступен тип транзистора - полевой транзистор металл-оксид-полупроводник (MOSFET). Эти транзисторы сформированыas a ‘sandwich’состоящий из полупроводникового слоя, обычно среза или пластины, из монокристалла кремния; слой диоксида кремния (оксид) и слой металла.

Структура полевого МОП-транзистора

Как показано на рисунке, структура МОП состоит из трех слоев:

The Metal Gate Electrode

The Insulating Oxide Layer (SiO2)

P – type Semiconductor (Substrate)

Структура МОП образует конденсатор, затвор и подложка представляют собой две пластины, а оксидный слой - как диэлектрический материал. Толщина диэлектрического материала (SiO 2 ) обычно составляет от 10 нм до 50 нм. Концентрацией и распределением носителей в подложке можно управлять с помощью внешнего напряжения, подаваемого на затвор и вывод подложки. Теперь, чтобы понять структуру МОП, сначала рассмотрим основные электрические свойства полупроводниковой подложки P-типа.

Концентрация носителя в полупроводниковом материале всегда соответствует Mass Action Law. Закон массового действия дается -

$$n.p=n_{i}^{2}$$

Где,

n - концентрация носителей электронов

p концентрация носителей дырок

ni - собственная концентрация носителей кремния

Теперь предположим , что субстрат равномерно легированный акцепторной (бор) концентрации N A . Итак, концентрация электронов и дырок в подложке p-типа равна

$$n_{po}=\frac{n_{i}^{2}}{N_{A}}$$

$$p_{po}=N_{A}$$

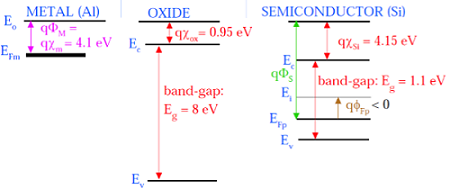

Здесь концентрация легирования NAна (от 10 15 до 10 16 см -3 ) больше, чем собственная концентрация ni. Теперь, чтобы понять структуру МОП, рассмотрим диаграмму энергетических уровней кремниевой подложки p-типа.

Как показано на рисунке, ширина запрещенной зоны между зоной проводимости и валентной зоной составляет 1,1 эВ. Здесь потенциал Ферми Φ F - это разность между собственным уровнем Ферми (E i ) и уровнем Ферми (E FP ).

Где уровень Ферми E F зависит от концентрации легирования. Потенциал Ферми Φ F - это разность между собственным уровнем Ферми (E i ) и уровнем Ферми (E FP ).

Математически,

$$\Phi_{Fp}=\frac{E_{F}-E_{i}}{q}$$

Разность потенциалов между зоной проводимости и свободным пространством называется сродством к электрону и обозначается qx.

Таким образом, энергия, необходимая электрону для перехода с уровня Ферми в свободное пространство, называется работой выхода (qΦ S ) и определяется выражением

$$q\Phi _{s}=(E_{c}-E_{F})+qx$$

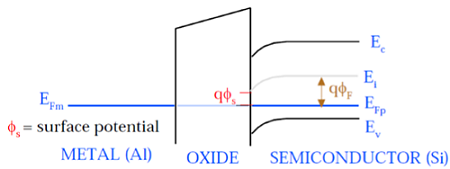

На следующем рисунке показана диаграмма энергетических зон компонентов, составляющих МОП.

Как показано на рисунке выше, изолирующий слой SiO 2 имеет большую ширину запрещенной зоны 8 эВ и работу выхода 0,95 эВ. Металлический затвор имеет работу выхода 4,1 эВ. Здесь рабочие функции разные, поэтому это приведет к падению напряжения в системе MOS. На приведенном ниже рисунке показана комбинированная диаграмма энергетических зон МОП-системы.

Как показано на этом рисунке, уровни ферми-потенциала металлического затвора и полупроводника (Si) имеют одинаковый потенциал. Потенциал Ферми на поверхности называется поверхностным потенциалом Φ S, и по величине он меньше потенциала Ферми Φ F.

Работа полевого МОП-транзистора

МОП-транзистор состоит из МОП-конденсатора с двумя pn-переходами, закрытыми в области канала, и эта область контролируется напряжением на затворе. Чтобы сделать оба p-n-перехода смещенными в обратном направлении, потенциал подложки поддерживается ниже, чем потенциал трех других клемм.

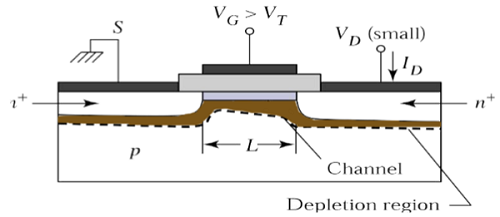

Если напряжение затвора будет увеличено сверх порогового напряжения (V GS > V TO ), на поверхности установится инверсионный слой и между истоком и стоком образуется канал n - типа. Этот канал n - типа будет передавать ток стока в соответствии со значением V DS .

При разном значении V DS полевой МОП-транзистор может работать в разных регионах, как описано ниже.

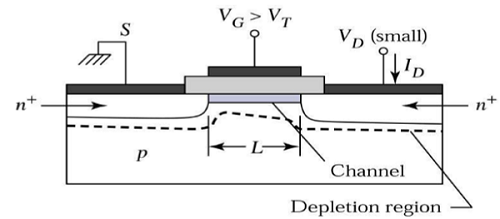

Линейная область

При V DS = 0 в области перевернутого канала существует тепловое равновесие и ток стока I D = 0. Теперь, если приложено небольшое напряжение стока, V DS > 0, ток стока, пропорциональный V DS , начнет течь от истока к слив через канал.

Канал обеспечивает непрерывный путь прохождения тока от истока к стоку. Этот режим работы называетсяlinear region. Поперечное сечение n-канального MOSFET, работающего в линейной области, показано на рисунке ниже.

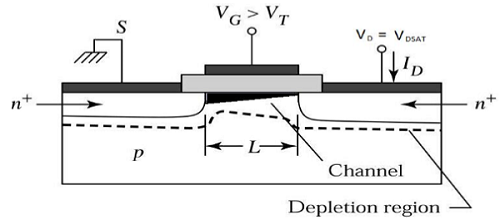

На границе области насыщения

Теперь, если V DS увеличивается, заряды в канале и глубина канала уменьшаются в конце слива. При V DS = V DSAT расходы в канале уменьшаются до нуля, что называетсяpinch – off point. Поперечное сечение n-канального MOSFET, работающего на границе области насыщения, показано на рисунке ниже.

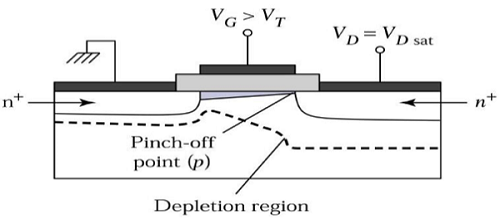

Область насыщенности

При V DS > V DSAT обедненная поверхность образуется рядом со стоком, и при увеличении напряжения на стоке эта обедненная область распространяется до истока.

Этот режим работы называется Saturation region. Электроны, идущие от истока к концу канала, попадают в область сток-истощение и ускоряются по направлению к стоку в сильном электрическом поле.

Ток полевого МОП-транзистора - характеристики напряжения

Чтобы понять вольт-амперную характеристику полевого МОП-транзистора, выполняется аппроксимация для канала. Без этого приближения трехмерный анализ МОП-системы становится сложным. ВGradual Channel Approximation (GCA) для вольт-амперной характеристики уменьшит проблему анализа.

Постепенное приближение канала (GCA)

Рассмотрим поперечный разрез n-канального MOSFET, работающего в линейном режиме. Здесь источник и подложка соединены с землей. В S = V B = 0. Ворота - к - источник (V GS ) и сливом - к - источника напряжения (V DS ) напряжения являются внешние параметры , которые контролируют утечку тока I D .

Напряжение V GS устанавливается равным напряжению, превышающему пороговое напряжение V TO , чтобы создать канал между истоком и стоком. Как показано на рисунке, направление x перпендикулярно поверхности, а направление y параллельно поверхности.

Здесь y = 0 на конце источника, как показано на рисунке. Напряжение канала по отношению к источнику представлено какVC(Y). Предположим, что пороговое напряжение VTO постоянно вдоль области канала от y = 0 до y = L. Граничное условие для напряжения V C канала :

$$V_{c}\left ( y = 0 \right ) = V_{s} = 0 \,and\,V_{c}\left ( y = L \right ) = V_{DS}$$

Мы также можем предположить, что

$$V_{GS}\geq V_{TO}$$ и

$$V_{GD} = V_{GS}-V_{DS}\geq V_{TO}$$

Пусть Q1 (y) - полный заряд подвижных электронов в поверхностном инверсионном слое. Этот заряд электрона можно выразить как -

$$Q1(y)=-C_{ox}.[V_{GS}-V_{C(Y)}-V_{TO}]$$

На приведенном ниже рисунке показана пространственная геометрия поверхностного инверсионного слоя и указаны его размеры. Слой инверсии сужается по мере продвижения от стока к истоку. Теперь, если мы рассмотрим небольшую область dy длины канала L, то дополнительное сопротивление dR, обеспечиваемое этой областью, можно выразить как -

$$dR=-\frac{dy}{w.\mu _{n}.Q1(y)}$$

Здесь знак минус обусловлен отрицательной полярностью заряда инверсионного слоя Q1, а μ n - поверхностная подвижность, которая постоянна. Теперь подставьте значение Q1 (y) в уравнение dR -

$$dR=-\frac{dy}{w.\mu _{n}.\left \{ -C_{ox}\left [ V_{GS}-V_{C\left ( Y \right )} \right ]-V_{TO} \right \}}$$

$$dR=\frac{dy}{w.\mu _{n}.C_{ox}\left [ V_{GS}-V_{C\left ( Y \right )} \right ]-V_{TO}}$$

Теперь падение напряжения в небольшой области dy может быть выражено как

$$dV_{c}=I_{D}.dR$$

Поместите значение dR в приведенное выше уравнение

$$dV_{C}=I_{D}.\frac{dy}{w.\mu_{n}.C_{ox}\left [ V_{GS}-V_{C(Y)} \right ]-V_{TO}}$$

$$w.\mu _{n}.C_{ox}\left [ V_{GS}-V_{C(Y)}-V_{TO} \right ].dV_{C}=I_{D}.dy$$

Чтобы получить ID тока стока по всей области канала, приведенное выше уравнение можно проинтегрировать по каналу от y = 0 до y = L и напряжений от V C (y) = 0 до V C (y) = V DS ,

$$C_{ox}.w.\mu _{n}.\int_{V_{c}=0}^{V_{DS}} \left [ V_{GS}-V_{C\left ( Y \right )}-V_{TO} \right ].dV_{C} = \int_{Y=0}^{L}I_{D}.dy$$

$$\frac{C_{ox}.w.\mu _{n}}{2}\left ( 2\left [ V_{GS}-V_{TO} \right ] V_{DS}-V_{DS}^{2}\right ) = I_{D}\left [ L-0 \right ]$$

$$I_{D} = \frac{C_{ox}.\mu _{n}}{2}.\frac{w}{L}\left ( 2\left [ V_{GS}-V_{TO} \right ]V_{DS}-V_{DS}^{2} \right )$$

Для линейной области V DS <V GS - V TO . Для области насыщения значение V DS больше, чем (V GS - V TO ). Следовательно, для области насыщения V DS = (V GS - V TO ).

$$I_{D} = C_{ox}.\mu _{n}.\frac{w}{2}\left ( \frac{\left [ 2V_{DS} \right ]V_{DS}-V_{DS}^{2}}{L} \right )$$

$$I_{D} = C_{ox}.\mu _{n}.\frac{w}{2}\left ( \frac{2V_{DS}^{2}-V_{DS}^{2}}{L} \right )$$

$$I_{D} = C_{ox}.\mu _{n}.\frac{w}{2}\left ( \frac{V_{DS}^{2}}{L} \right )$$

$$I_{D} = C_{ox}.\mu _{n}.\frac{w}{2}\left ( \frac{\left [ V_{GS}-V_{TO} \right ]^{2}}{L} \right )$$

Инвертор действительно является ядром всех цифровых устройств. Как только его работа и свойства будут четко изучены, разработка более сложных структур, таких как вентили NAND, сумматоры, умножители и микропроцессоры, значительно упростится. Электрическое поведение этих сложных цепей можно почти полностью вывести путем экстраполяции результатов, полученных для инверторов.

Анализ инверторов можно расширить, чтобы объяснить поведение более сложных вентилей, таких как NAND, NOR или XOR, которые, в свою очередь, образуют строительные блоки для таких модулей, как умножители и процессоры. В этой главе мы сосредоточимся на одном единственном воплощении затвора инвертора, а именно на статическом КМОП-инверторе, короче говоря, на КМОП-инверторе. Это, безусловно, самый популярный в настоящее время и поэтому заслуживает особого внимания.

Принцип действия

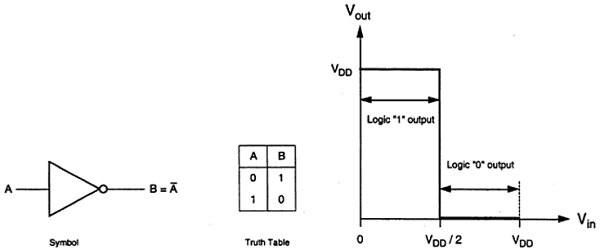

Логический символ и таблица истинности идеального инвертора показаны на рисунке ниже. Здесь A - вход, а B - инвертированный выход, представленный их узловыми напряжениями. Используя положительную логику, логическое значение логической 1 представлено как V dd, а логический 0 представлен как 0. V th - пороговое напряжение инвертора, которое равно V dd / 2, где V dd - выходное напряжение.

Выход переключается с 0 на V dd, когда входной сигнал меньше V th . Таким образом, для 0 <V in <V th выход равен входу логического 0, а V th <V in <V dd равен входу логической 1 для инвертора.

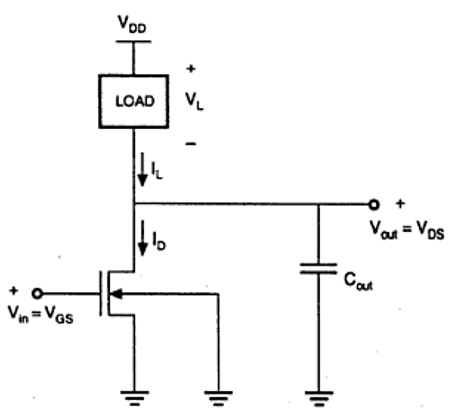

Показанные на рисунке характеристики идеальны. Обобщенная структура схемы инвертора nMOS показана на рисунке ниже.

Из приведенного рисунка видно, что входное напряжение инвертора равно напряжению затвор-исток транзистора nMOS, а выходное напряжение инвертора равно напряжению сток-исток транзистора nMOS. Напряжение между источником и подложкой nMOS также называется драйвером для заземленного транзистора; поэтому V SS = 0. Выходной узел соединен с сосредоточенной емкостью, используемой для VTC.

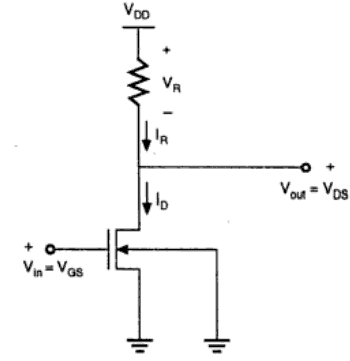

Инвертор резистивной нагрузки

Базовая структура инвертора с резистивной нагрузкой показана на рисунке ниже. Здесь в качестве задающего транзистора выступает nMOS типа расширения. Нагрузка состоит из простого линейного резистора R L . Питания схемы является V DD и ток стока I D равно тока нагрузки I R .

Схема работы

Когда на входе транзистора драйвера меньше порогового напряжения V TH (V in <V TH ), транзистор драйвера находится в области отсечки и не проводит никакого тока. Таким образом, падение напряжения на нагрузочном резисторе равно НУЛЮ, а выходное напряжение равно V DD . Теперь, когда входное напряжение увеличивается, транзистор драйвера начинает проводить ненулевой ток, и nMOS переходит в область насыщения.

Математически,

$$I_{D} = \frac{K_{n}}{2}\left [ V_{GS}-V_{TO} \right ]^{2}$$

При дальнейшем увеличении входного напряжения транзистор драйвера войдет в линейную область и выходной сигнал транзистора драйвера уменьшится.

$$I_{D} = \frac{K_{n}}{2}2\left [ V_{GS}-V_{TO} \right ]V_{DS}-V_{DS}^{2}$$

VTC инвертора резистивной нагрузки, показанный ниже, указывает рабочий режим транзистора драйвера и точки напряжения.

Инвертор с нагрузкой MOSFET типа N

Основное преимущество использования полевого МОП-транзистора в качестве устройства нагрузки состоит в том, что площадь кремния, занимаемая транзистором, меньше площади, занимаемой резистивной нагрузкой. Здесь MOSFET является активной нагрузкой, а инвертор с активной нагрузкой дает лучшую производительность, чем инвертор с резистивной нагрузкой.

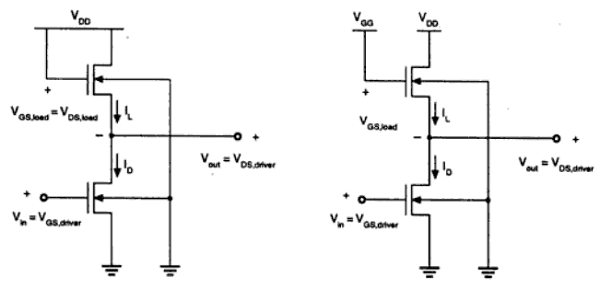

Расширение загрузки NMOS

На рисунке показаны два инвертора с нагрузочным устройством расширенного типа. Нагрузочный транзистор может работать либо в области насыщения, либо в линейной области, в зависимости от напряжения смещения, приложенного к его клемме затвора. Инвертор увеличивающей нагрузки с насыщением показан на рис. (а). Это требует один источник напряжения и простой процесс изготовления и так V OH ограничена V DD - V T .

Инвертор нагрузки линейного увеличения показан на рис. (б). Он всегда работает в линейной области; поэтому уровень V OH равен V DD .

Инвертор с линейной нагрузкой имеет более высокий запас помехоустойчивости по сравнению с инвертором с усилением насыщения. Но недостатком инвертора с линейным улучшением является то, что он требует двух отдельных источников питания, и обе цепи страдают от высокого рассеяния мощности. Следовательно, повышающие инверторы не используются в каких-либо крупномасштабных цифровых приложениях.

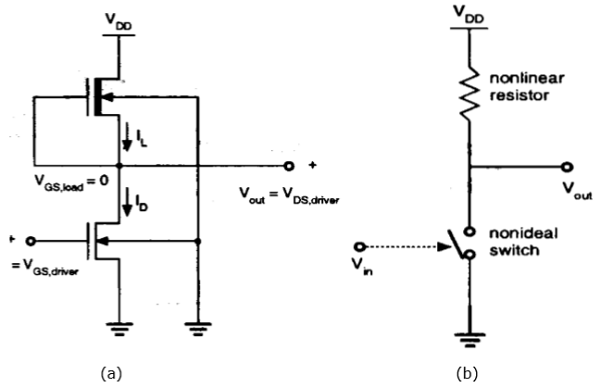

Истощение нагрузки NMOS

Недостатки инвертора с увеличенной нагрузкой могут быть преодолены с помощью инвертора с уменьшенной нагрузкой. По сравнению с инвертором с увеличенной нагрузкой, инвертор с уменьшающейся нагрузкой требует еще несколько этапов изготовления канального имплантата для регулировки порогового напряжения нагрузки.

Преимуществами инвертора с обедненной нагрузкой являются резкий переход VTC, лучший запас шума, единый источник питания и меньшая общая площадь компоновки.

Как показано на рисунке, затвор и исток нагрузки соединены; Итак, V GS = 0. Таким образом, пороговое напряжение нагрузки отрицательное. Следовательно,

$$V_{GS,load}> V_{T,load}$$ доволен

Таким образом, нагрузочное устройство всегда имеет канал проводимости независимо от уровня входного и выходного напряжения.

Когда нагрузочный транзистор находится в области насыщения, ток нагрузки определяется выражением

$$I_{D,load} = \frac{K_{n,load}}{2}\left [ -V_{T,load}\left ( V_{out} \right ) \right ]^{2}$$

Когда нагрузочный транзистор находится в линейной области, ток нагрузки определяется выражением

$$I_{D,load} = \frac{K_{n,load}}{2}\left [ 2\left | V_{T,load}\left ( V_{out} \right ) \right |.\left ( V_{DD}-V_{out} \right )-\left ( V_{DD}-V_{out} \right )^{2} \right ]$$

Характеристики передачи напряжения инвертора с истощенной нагрузкой показаны на рисунке ниже -

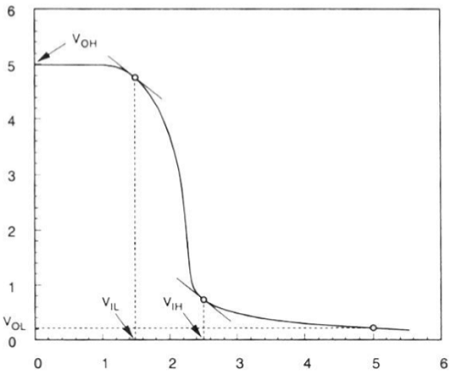

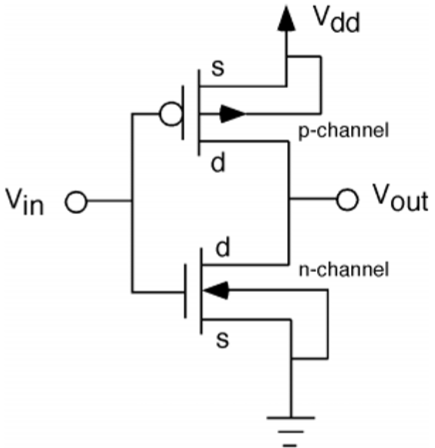

Инвертор CMOS - схема, работа и описание

Схема инвертора CMOS показана на рисунке. Здесь транзисторы nMOS и pMOS работают как транзисторы драйвера; когда один транзистор включен, другой выключен.

Эта конфигурация называется complementary MOS (CMOS). Вход подключается к клемме затвора обоих транзисторов, так что оба могут управляться напрямую входными напряжениями. Подложка nMOS подключается к земле, а подложка pMOS подключается к источнику питания V DD .

Итак, V SB = 0 для обоих транзисторов.

$$V_{GS,n}=V_{in}$$

$$V_{DS,n}=V_{out}$$

И,

$$V_{GS,p}=V_{in}-V_{DD}$$

$$V_{DS,p}=V_{out}-V_{DD}$$

Когда вход nMOS меньше порогового напряжения (V in <V TO, n ), nMOS отключается, и pMOS находится в линейной области. Итак, ток стока обоих транзисторов равен нулю.

$$I_{D,n}=I_{D,p}=0$$

Следовательно, выходное напряжение V OH равно напряжению питания.

$$V_{out}=V_{OH}=V_{DD}$$

Когда входное напряжение больше, чем V DD + V TO, p , pMOS-транзистор находится в области отсечки, а nMOS - в линейной области, поэтому ток стока обоих транзисторов равен нулю.

$$I_{D,n}=I_{D,p}=0$$

Следовательно, выходное напряжение V OL равно нулю.

$$V_{out}=V_{OL}=0$$

NMOS работает в области насыщения, если V in > V TO и если выполняются следующие условия.

$$V_{DS,n}\geq V_{GS,n}-V_{TO,n} $$

$$V_{out}\geq V_{in}-V_{TO,n} $$

PMOS работает в области насыщения, если V in <V DD + V TO, p и если выполняются следующие условия.

$$V_{DS,p}\leq V_{GS,p}-V_{TO,p} $$

$$V_{out}\leq V_{in}-V_{TO,p} $$

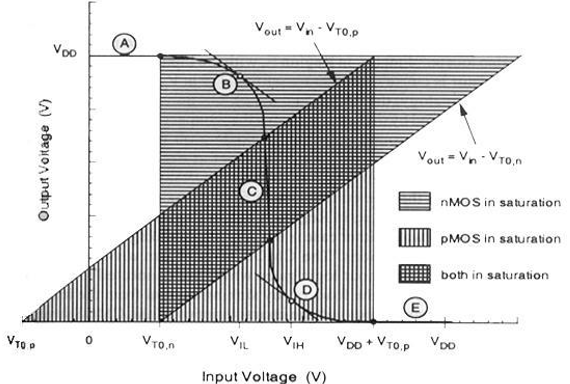

Для разных значений входных напряжений рабочие регионы указаны ниже для обоих транзисторов.

| Область | V в | V из | nMOS | pMOS |

|---|---|---|---|---|

| A | < VTO, n | VOH | Cut – off | Linear |

| B | VIL | High ≈ VOH | Saturation | Linear |

| C | Vth | Vth | Saturation | Saturation |

| D | VIH | Low ≈ VOL | Linear | Saturation |

| E | > (VDD + VTO, p) | VOL | Linear | Cut – off |

The VTC of CMOS is shown in the figure below −

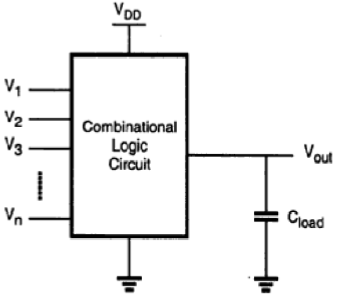

Combinational logic circuits or gates, which perform Boolean operations on multiple input variables and determine the outputs as Boolean functions of the inputs, are the basic building blocks of all digital systems. We will examine simple circuit configurations such as two-input NAND and NOR gates and then expand our analysis to more general cases of multiple-input circuit structures.

Next, the CMOS logic circuits will be presented in a similar fashion. We will stress the similarities and differences between the nMOS depletion-load logic and CMOS logic circuits and point out the advantages of CMOS gates with examples. In its most general form, a combinational logic circuit, or gate, performing a Boolean function can be represented as a multiple-input, single-output system, as depicted in the figure.

Node voltages, referenced to the ground potential, represent all input variables. Using positive logic convention, the Boolean (or logic) value of "1" can be represented by a high voltage of VDD, and the Boolean (or logic) value of "0" can be represented by a low voltage of 0. The output node is loaded with a capacitance CL, which represents the combined capacitances of the parasitic device in the circuit.

CMOS Logic Circuits

CMOS Two input NOR Gate

The circuit consists of a parallel-connected n-net and a series-connected complementary p-net. The input voltages VX and VY are applied to the gates of one nMOS and one pMOS transistor.

When either one or both inputs are high, i.e., when the n-net creates a conducting path between the output node and the ground, the p-net is cut—off. If both input voltages are low, i.e., the n-net is cut-off, then the p-net creates a conducting path between the output node and the supply voltage.

For any given input combination, the complementary circuit structure is such that the output is connected either to VDD or to ground via a low-resistance path and a DC current path between the VDD and ground is not established for any input combinations. The output voltage of the CMOS, two input NOR gate will get a logic-low voltage of VOL = 0 and a logic-high voltage of VOH = VDD. The equation of the switching threshold voltage Vth is given by

$$V_{th}\left ( NOR2 \right ) = \frac{V_{T,n}+\frac{1}{2}\sqrt{\frac{k_{p}}{k_{n}}\left ( V_{DD}-\left | V_{T,p} \right | \right )}}{1+\frac{1}{2}\sqrt{\frac{k_{p}}{k_{n}}}}$$

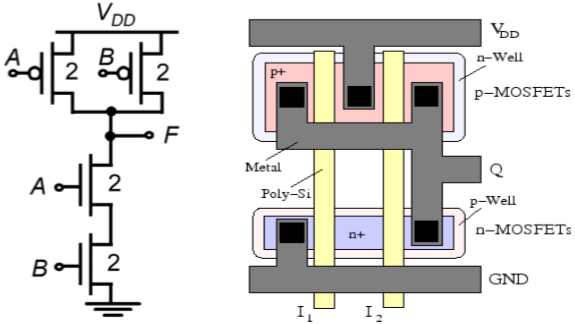

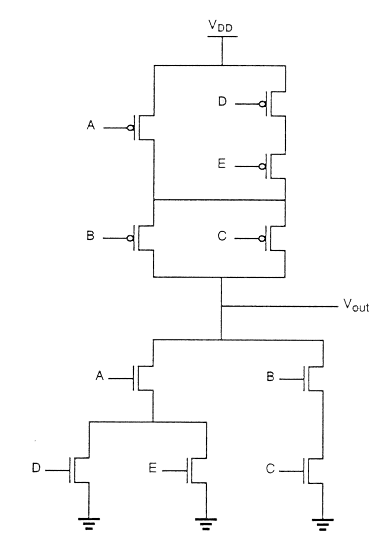

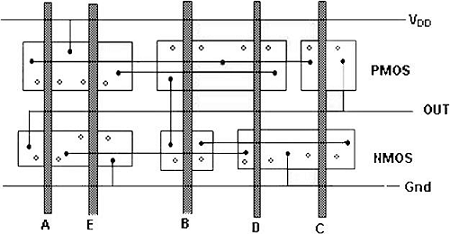

Layout of CMOS 2-input NOR Gate

The figure shows a sample layout of CMOS 2-input NOR gate, using single-layer metal and single-layer polysilicon. The features of this layout are −

- Single vertical polylines for each input

- Single active shapes for N and P devices, respectively

- Metal buses running horizontal

The stick diagram for the CMOS N0R2 gate is shown in the figure given below; which corresponds directly to the layout, but does not contain W and L information. The diffusion areas are depicted by rectangles, the metal connections and solid lines and circles, respectively represent contacts, and the crosshatched strips represent the polysilicon columns. Stick diagram is useful for planning optimum layout topology.

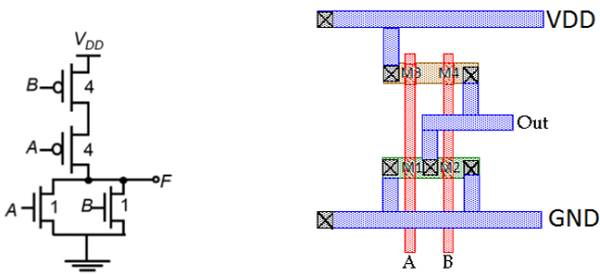

CMOS Two-input NAND Gate

The circuit diagram of the two input CMOS NAND gate is given in the figure below.

The principle of operation of the circuit is exact dual of the CMOS two input NOR operation. The n – net consisting of two series connected nMOS transistor creates a conducting path between the output node and the ground, if both input voltages are logic high. Both of the parallelly connected pMOS transistor in p-net will be off.

For all other input combination, either one or both of the pMOS transistor will be turn ON, while p – net is cut off, thus, creating a current path between the output node and the power supply voltage. The switching threshold for this gate is obtained as −

$$V_{th}\left ( NAND2 \right ) = \frac{V_{T,n}+2\sqrt{\frac{k_{p}}{k_{n}}\left ( V_{DD}-\left | V_{T,p} \right | \right )}}{1+2\sqrt{\frac{k_{p}}{k_{n}}}}$$

The features of this layout are as follows −

- Single polysilicon lines for inputs run vertically across both N and P active regions.

- Single active shapes are used for building both nMOS devices and both pMOS devices.

- Power bussing is running horizontal across top and bottom of layout.

- Output wires runs horizontal for easy connection to neighboring circuit.

Complex Logic Circuits

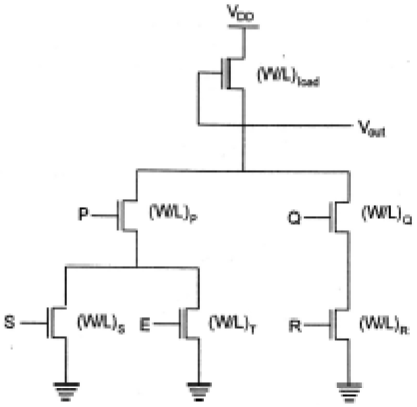

NMOS Depletion Load Complex Logic Gate

To realize complex functions of multiple input variables, the basic circuit structures and design principles developed for NOR and NAND can be extended to complex logic gates. The ability to realize complex logic functions, using a small number of transistors is one of the most attractive features of nMOS and CMOS logic circuits. Consider the following Boolean function as an example.

$$\overline{Z=P\left ( S+T \right )+QR}$$

The nMOS depletion-load complex logic gate used to realize this function is shown in figure. In this figure, the left nMOS driver branch of three driver transistors is used to perform the logic function P (S + T), while the right-hand side branch performs the function QR. By connecting the two branches in parallel, and by placing the load transistor between the output node and the supply voltage VDD, we obtain the given complex function. Each input variable is assigned to only one driver.

Inspection of the circuit topology gives simple design principles of the pull-down network −

- OR operations are performed by parallel-connected drivers.

- AND operations are performed by series-connected drivers.

- Inversion is provided by the nature of MOS circuit operation.

If all input variables are logic-high in the circuit realizing the function, the equivalent driver (W/L) ratio of the pull-down network consisting of five nMOS transistors is

$$\frac{W}{L}=\frac{1}{\frac{1}{\left ( W/L \right )Q}+\frac{1}{\left ( W/L \right )R}}+\frac{1}{\frac{1}{\left ( W/L \right )P}+\frac{1}{\left ( W/L \right )S+\left ( W/L \right )Q}}$$

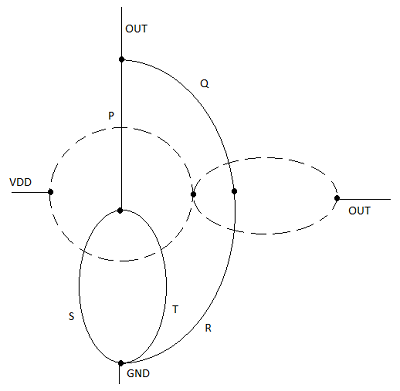

Complex CMOS Logic Gates

The realization of the n-net, or pull-down network, is based on the same basic design principles examined for nMOS depletion-load complex logic gate. The pMOS pull-up network must be the dual network of the n-net.

It means all parallel connections in the nMOS network will correspond to a series connection in the pMOS network, and all series connection in the nMOS network correspond to a parallel connection in the pMOS network. The figure shows a simple construction of the dual p-net (pull-up) graph from the n-net (pull-down) graph.

Each driver transistor in the pull-down network is shown by ai and each node is shown by a vertex in the pull-down graph. Next, a new vertex is created within each confined area in the pull graph, and neighboring vertices are connected by edges which cross each edge in the pull-down graph only once. This new graph shows the pull-up network.

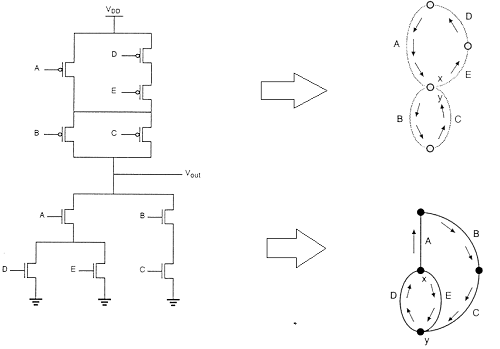

Layout Technique using Euler Graph Method

The figure shows the CMOS implementation of a complex function and its stick diagram done with arbitrary gate ordering that gives a very non-optimum layout for the CMOS gate.

In this case, the separation between the polysilicon columns must allow diffusion-todiffusion separation in between. This certainly consumes a considerably amount of extra silicon area.

By using the Euler path, we can obtain an optimum layout. The Euler path is defined as an uninterrupted path that traverses each edge (branch) of the graph exactly once. Find Euler path in both the pull-down tree graph and the pull-up tree graph with identical ordering of the inputs.

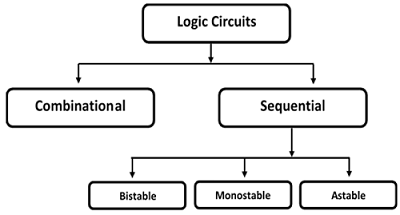

Logic circuits are divided into two categories − (a) Combinational Circuits, and (b) Sequential Circuits.

In Combinational circuits, the output depends only on the condition of the latest inputs.

In Sequential circuits, the output depends not only on the latest inputs, but also on the condition of earlier inputs. Sequential circuits contain memory elements.

Sequential circuits are of three types −

Bistable − Bistable circuits have two stable operating points and will be in either of the states. Example − Memory cells, latches, flip-flops and registers.

Monostable − Monostable circuits have only one stable operating point and even if they are temporarily perturbed to the opposite state, they will return in time to their stable operating point. Example: Timers, pulse generators.

Astable − circuits have no stable operating point and oscillate between several states. Example − Ring oscillator.

CMOS Logic Circuits

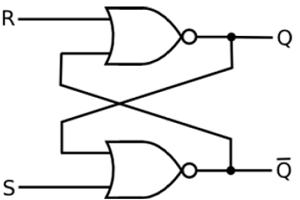

SR Latch based on NOR Gate

If the set input (S) is equal to logic "1" and the reset input is equal to logic "0." then the output Q will be forced to logic "1". While $\overline{Q}$ is forced to logic "0". This means the SR latch will be set, irrespective of its previous state.

Similarly, if S is equal to "0" and R is equal to "1" then the output Q will be forced to "0" while $\overline{Q}$ is forced to "1". This means the latch is reset, regardless of its previously held state. Finally, if both of the inputs S and R are equal to logic "1" then both output will be forced to logic "0" which conflicts with the complementarity of Q and $\overline{Q}$.

Therefore, this input combination is not allowed during normal operation. Truth table of NOR based SR Latch is given in table.

| S | R | Q | $\overline{Q}$ | Operation |

|---|---|---|---|---|

| 0 | 0 | Q | $\overline{Q}$ | Hold |

| 1 | 0 | 1 | 0 | Set |

| 0 | 1 | 0 | 1 | Reset |

| 1 | 1 | 0 | 0 | Not allowed |

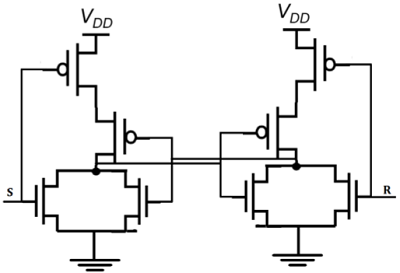

CMOS SR latch based on NOR gate is shown in the figure given below.

If the S is equal to VOH and the R is equal to VOL, both of the parallel-connected transistors M1 and M2 will be ON. The voltage on node $\overline{Q}$ will assume a logic-low level of VOL = 0.

At the same time, both M3 and M4 are turned off, which results in a logic-high voltage VOH at node Q. If the R is equal to VOH and the S is equal to VOL, M1 and M2 turned off and M3 and M4 turned on.

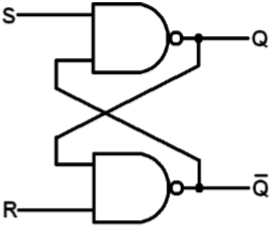

SR Latch based on NAND Gate

Block diagram and gate level schematic of NAND based SR latch is shown in the figure. The small circles at the S and R input terminals represents that the circuit responds to active low input signals. The truth table of NAND based SR latch is given in table

| S | R | Q | Q′ | |

| 0 | 0 | NC | NC | No change. Latch remained in present state. |

| 1 | 0 | 1 | 0 | Latch SET. |

| 0 | 1 | 0 | 1 | Latch RESET. |

| 1 | 1 | 0 | 0 | Invalid condition. |

If S goes to 0 (while R = 1), Q goes high, pulling $\overline{Q}$ low and the latch enters Set state

S = 0 then Q = 1 (if R = 1)

If R goes to 0 (while S = 1), Q goes high, pulling $\overline{Q}$ low and the latch is Reset

R = 0 then Q = 1 (if S = 1)

Hold state requires both S and R to be high. If S = R = 0 then output is not allowed, as it would result in an indeterminate state. CMOS SR Latch based on NAND Gate is shown in figure.

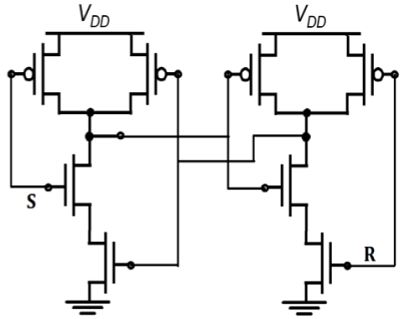

Depletion-load nMOS SR Latch based on NAND Gate is shown in figure. The operation is similar to that of CMOS NAND SR latch. The CMOS circuit implementation has low static power dissipation and high noise margin.

CMOS Logic Circuits

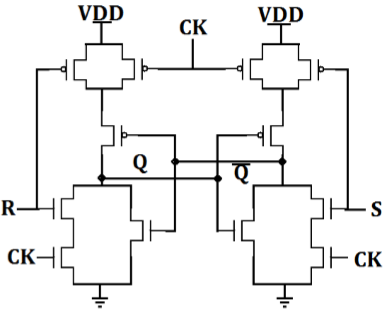

Clocked SR Latch

The figure shows a NOR-based SR latch with a clock added. The latch is responsive to inputs S and R only when CLK is high.

When CLK is low, the latch retains its current state. Observe that Q changes state −

- When S goes high during positive CLK.

- On leading CLK edge after changes in S & R during CLK low time.

- A positive glitch in S while CLK is high

- When R goes high during positive CLK.

CMOS AOI implementation of clocked NOR based SR latch is shown in the figure. Note that only 12 transistors required.

When CLK is low, two series terminals in N tree N are open and two parallel transistors in tree P are ON, thus retaining state in the memory cell.

When clock is high, the circuit becomes simply a NOR based CMOS latch which will respond to input S and R.

Clocked SR Latch based on NAND Gate

Circuit is implemented with four NAND gates. If this circuit is implemented with CMOS then it requires 16 transistors.

- The latch is responsive to S or R only if CLK is high.

- If both input signals and the CLK signals are active high: i.e., the latch output Q will be set when CLK = "1" S = "1" and R = "0"

- Similarly, the latch will be reset when CLK = "1," S = "0," and

When CLK is low, the latch retains its present state.

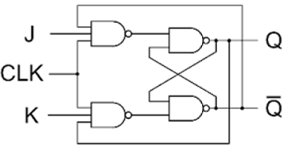

Clocked JK Latch

The figure above shows a clocked JK latch, based on NAND gates. The disadvantage of an SR latch is that when both S and R are high, its output state becomes indeterminant. The JK latch eliminates this problem by using feedback from output to input, such that all input states of the truth table are allowable. If J = K = 0, the latch will hold its present state.

If J = 1 and K = 0, the latch will set on the next positive-going clock edge, i.e. Q = 1, $\overline{Q}$ = 0

If J = 0 and K = 1, the latch will reset on the next positive-going clock edge, i.e. Q = 1 and $\overline{Q}$ = 0.

If J = K = 1, the latch will toggle on the next positive-going clock edge

The operation of the clocked JK latch is summarized in the truth table given in table.

J |

K |

Q |

$\overline{Q}$ | S |

R |

Q |

$\overline{Q}$ | Operation |

| 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | Hold |

| 1 | 0 | 1 | 1 | 1 | 0 | |||

| 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | Reset |

| 1 | 0 | 1 | 0 | 0 | 1 | |||

| 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | Set |

| 1 | 0 | 1 | 1 | 1 | 0 | |||

| 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | toggle |

| 1 | 0 | 1 | 0 | 0 | 1 |

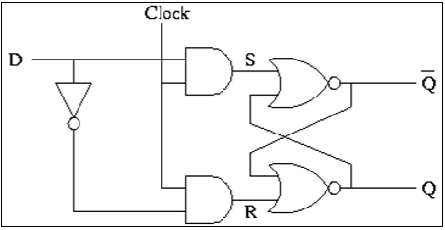

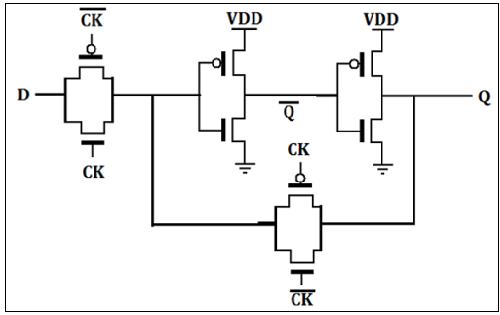

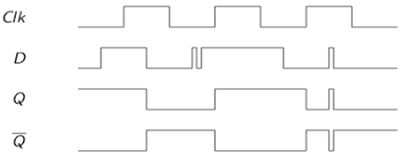

CMOS D Latch Implementation

The D latch is normally, implemented with transmission gate (TG) switches as shown in the figure. The input TG is activated with CLK while the latch feedback loop TG is activated with CLK. Input D is accepted when CLK is high. When CLK goes low, the input is opencircuited and the latch is set with the prior data D.

VHDL stands for very high-speed integrated circuit hardware description language. It is a programming language used to model a digital system by dataflow, behavioral and structural style of modeling. This language was first introduced in 1981 for the department of Defense (DoD) under the VHSIC program.

Describing a Design

In VHDL an entity is used to describe a hardware module. An entity can be described using,

- Entity declaration

- Architecture

- Configuration

- Package declaration

- Package body

Let’s see what are these?

Entity Declaration

It defines the names, input output signals and modes of a hardware module.

Syntax −

entity entity_name is

Port declaration;

end entity_name;An entity declaration should start with ‘entity’ and end with ‘end’ keywords. The direction will be input, output or inout.

| In | Port can be read |

| Out | Port can be written |

| Inout | Port can be read and written |

| Buffer | Port can be read and written, it can have only one source. |

Architecture −

Architecture can be described using structural, dataflow, behavioral or mixed style.

Syntax -

architecture architecture_name of entity_name

architecture_declarative_part;

begin

Statements;

end architecture_name;Здесь мы должны указать имя объекта, для которого мы пишем тело архитектуры. Операторы архитектуры должны быть внутри ключевых слов 'begin' и 'énd'. Декларативная часть архитектуры может содержать переменные, константы или объявление компонента.

Моделирование потока данных

В этом стиле моделирования поток данных через объект выражается с помощью параллельного (параллельного) сигнала. Параллельные операторы в VHDL - это WHEN и GENERATE.

Помимо них, для построения кода также можно использовать присвоения с использованием только операторов (AND, NOT, +, *, sll и т. Д.).

Наконец, в коде этого типа можно использовать особый вид присваивания, называемый BLOCK.

В параллельном коде можно использовать следующее:

- Operators

- Оператор WHEN (WHEN / ELSE или WITH / SELECT / WHEN);

- Оператор GENERATE;

- Заявление BLOCK

Поведенческое моделирование

В этом стиле моделирования поведение объекта как набора операторов выполняется последовательно в указанном порядке. Только операторы, помещенные внутри PROCESS, FUNCTION или PROCEDURE, являются последовательными.

ПРОЦЕССЫ, ФУНКЦИИ и ПРОЦЕДУРЫ - единственные разделы кода, которые выполняются последовательно.

Однако в целом любой из этих блоков по-прежнему является параллельным с любыми другими операторами, размещенными за его пределами.

Одним из важных аспектов кода поведения является то, что он не ограничивается последовательной логикой. Действительно, с его помощью мы можем создавать как последовательные схемы, так и комбинационные схемы.

Операторы поведения - IF, WAIT, CASE и LOOP. ПЕРЕМЕННЫЕ также ограничены, и они должны использоваться только в последовательном коде. VARIABLE никогда не может быть глобальным, поэтому его значение нельзя передать напрямую.

Структурное моделирование

В этом моделировании объект описывается как набор взаимосвязанных компонентов. Оператор создания экземпляра компонента является параллельным оператором. Следовательно, порядок этих утверждений не имеет значения. Структурный стиль моделирования описывает только взаимосвязь компонентов (рассматриваемых как черные ящики), не подразумевая какого-либо поведения самих компонентов или объекта, который они вместе представляют.

В структурном моделировании тело архитектуры состоит из двух частей - декларативной части (перед ключевым словом begin) и части инструкции (после ключевого слова begin).

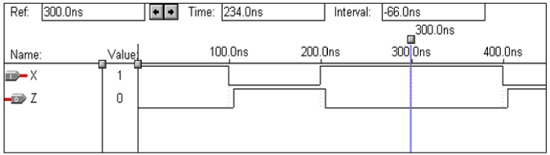

Логическая операция - И ВОРОТА

| Икс | Y | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity and1 is

port(x,y:in bit ; z:out bit);

end and1;

architecture virat of and1 is

begin

z<=x and y;

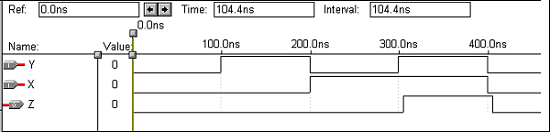

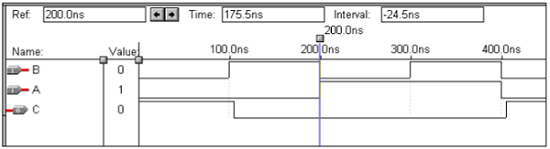

end virat;Формы волны

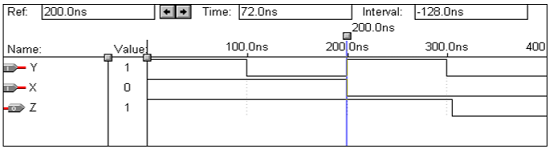

Логическая операция - OR Gate

| Икс | Y | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity or1 is

port(x,y:in bit ; z:out bit);

end or1;

architecture virat of or1 is

begin

z<=x or y;

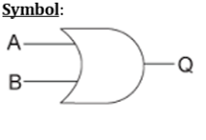

end virat;Формы волны

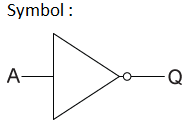

Логическая операция - НЕ Ворота

| Икс | Y |

|---|---|

| 0 | 1 |

| 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity not1 is

port(x:in bit ; y:out bit);

end not1;

architecture virat of not1 is

begin

y<=not x;

end virat;Формы волны

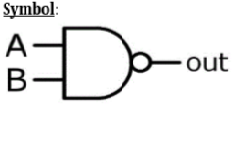

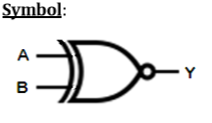

Логическая операция - NAND Gate

| Икс | Y | z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity nand1 is

port(a,b:in bit ; c:out bit);

end nand1;

architecture virat of nand1 is

begin

c<=a nand b;

end virat;Формы волны

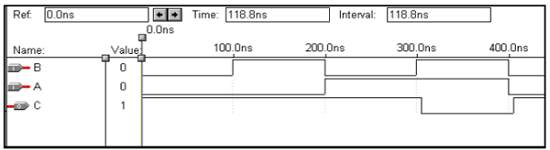

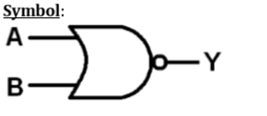

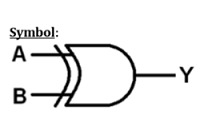

Логическая операция - NOR Gate

| Икс | Y | z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity nor1 is

port(a,b:in bit ; c:out bit);

end nor1;

architecture virat of nor1 is

begin

c<=a nor b;

end virat;Формы волны

Логическая операция - XOR Gate

| Икс | Y | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity xor1 is

port(a,b:in bit ; c:out bit);

end xor1;

architecture virat of xor1 is

begin

c<=a xor b;

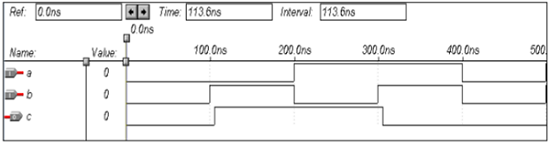

end virat;Формы волны

Логическая операция - X-NOR Gate

| Икс | Y | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity xnor1 is

port(a,b:in bit ; c:out bit);

end xnor1;

architecture virat of xnor1 is

begin

c<=not(a xor b);

end virat;Формы волны

В этой главе объясняется программирование VHDL для комбинационных схем.

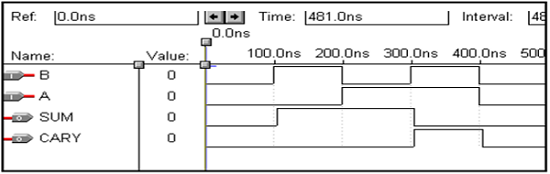

Код VHDL для полусумматора

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity half_adder is

port(a,b:in bit; sum,carry:out bit);

end half_adder;

architecture data of half_adder is

begin

sum<= a xor b;

carry <= a and b;

end data;Формы волны

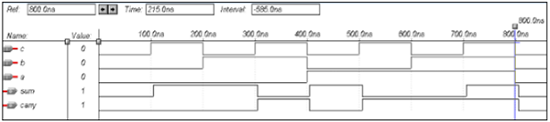

Код VHDL для полного сумматора

Library ieee;

use ieee.std_logic_1164.all;

entity full_adder is port(a,b,c:in bit; sum,carry:out bit);

end full_adder;

architecture data of full_adder is

begin

sum<= a xor b xor c;

carry <= ((a and b) or (b and c) or (a and c));

end data;Формы волны

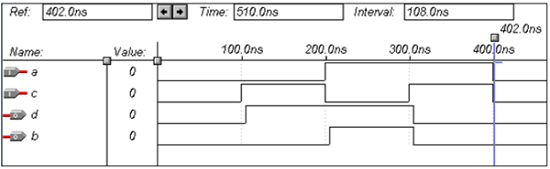

Код VHDL для полувычитателя

Library ieee;

use ieee.std_logic_1164.all;

entity half_sub is

port(a,c:in bit; d,b:out bit);

end half_sub;

architecture data of half_sub is

begin

d<= a xor c;

b<= (a and (not c));

end data;Формы волны

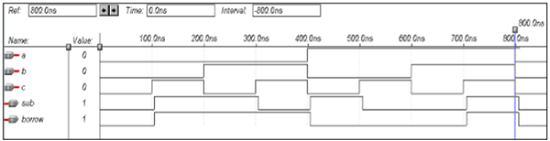

Код VHDL для полного вычитателя

Library ieee;

use ieee.std_logic_1164.all;

entity full_sub is

port(a,b,c:in bit; sub,borrow:out bit);

end full_sub;

architecture data of full_sub is

begin

sub<= a xor b xor c;

borrow <= ((b xor c) and (not a)) or (b and c);

end data;Формы волны

Код VHDL для мультиплексора

Library ieee;

use ieee.std_logic_1164.all;

entity mux is

port(S1,S0,D0,D1,D2,D3:in bit; Y:out bit);

end mux;

architecture data of mux is

begin

Y<= (not S0 and not S1 and D0) or

(S0 and not S1 and D1) or

(not S0 and S1 and D2) or

(S0 and S1 and D3);

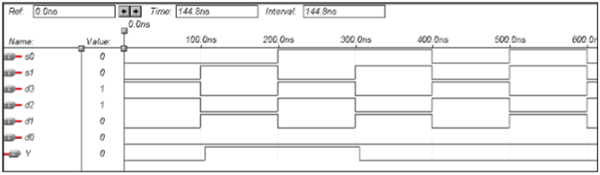

end data;Формы волны

Код VHDL для демультиплексора

Library ieee;

use ieee.std_logic_1164.all;

entity demux is

port(S1,S0,D:in bit; Y0,Y1,Y2,Y3:out bit);

end demux;

architecture data of demux is

begin

Y0<= ((Not S0) and (Not S1) and D);

Y1<= ((Not S0) and S1 and D);

Y2<= (S0 and (Not S1) and D);

Y3<= (S0 and S1 and D);

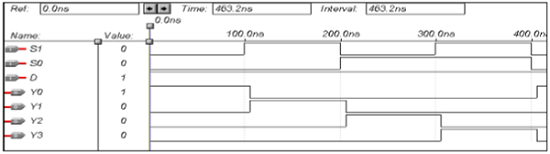

end data;Формы волны

Код VHDL для кодировщика 8 x 3

library ieee;

use ieee.std_logic_1164.all;

entity enc is

port(i0,i1,i2,i3,i4,i5,i6,i7:in bit; o0,o1,o2: out bit);

end enc;

architecture vcgandhi of enc is

begin

o0<=i4 or i5 or i6 or i7;

o1<=i2 or i3 or i6 or i7;

o2<=i1 or i3 or i5 or i7;

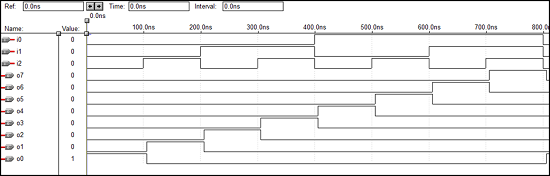

end vcgandhi;Формы волны

Код VHDL для декодера 3 x 8

library ieee;

use ieee.std_logic_1164.all;

entity dec is

port(i0,i1,i2:in bit; o0,o1,o2,o3,o4,o5,o6,o7: out bit);

end dec;

architecture vcgandhi of dec is

begin

o0<=(not i0) and (not i1) and (not i2);

o1<=(not i0) and (not i1) and i2;

o2<=(not i0) and i1 and (not i2);

o3<=(not i0) and i1 and i2;

o4<=i0 and (not i1) and (not i2);

o5<=i0 and (not i1) and i2;

o6<=i0 and i1 and (not i2);

o7<=i0 and i1 and i2;

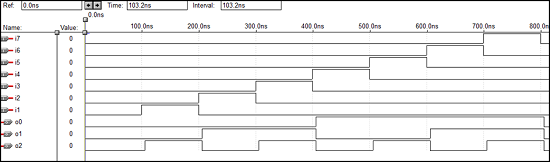

end vcgandhi;Формы волны

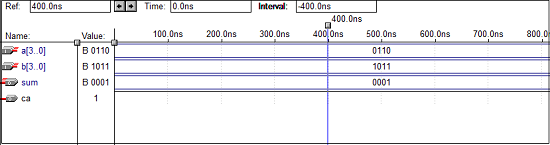

Код VHDL - 4-битный параллельный сумматор

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity pa is

port(a : in STD_LOGIC_VECTOR(3 downto 0);

b : in STD_LOGIC_VECTOR(3 downto 0);

ca : out STD_LOGIC;

sum : out STD_LOGIC_VECTOR(3 downto 0)

);

end pa;

architecture vcgandhi of pa is

Component fa is

port (a : in STD_LOGIC;

b : in STD_LOGIC;

c : in STD_LOGIC;

sum : out STD_LOGIC;

ca : out STD_LOGIC

);

end component;

signal s : std_logic_vector (2 downto 0);

signal temp: std_logic;

begin

temp<='0';

u0 : fa port map (a(0),b(0),temp,sum(0),s(0));

u1 : fa port map (a(1),b(1),s(0),sum(1),s(1));

u2 : fa port map (a(2),b(2),s(1),sum(2),s(2));

ue : fa port map (a(3),b(3),s(2),sum(3),ca);

end vcgandhi;Формы волны

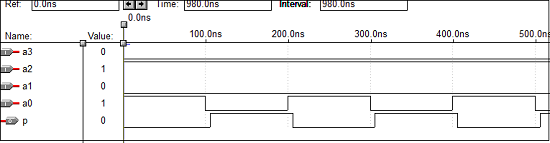

Код VHDL - 4-битная проверка четности

library ieee;

use ieee.std_logic_1164.all;

entity parity_checker is

port (a0,a1,a2,a3 : in std_logic;

p : out std_logic);

end parity_checker;

architecture vcgandhi of parity_checker is

begin

p <= (((a0 xor a1) xor a2) xor a3);

end vcgandhi;Формы волны

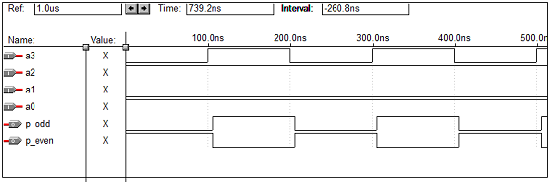

Код VHDL - 4-битный генератор четности

library ieee;

use ieee.std_logic_1164.all;

entity paritygen is

port (a0, a1, a2, a3: in std_logic; p_odd, p_even: out std_logic);

end paritygen;

architecture vcgandhi of paritygen is

begin

process (a0, a1, a2, a3)

if (a0 ='0' and a1 ='0' and a2 ='0' and a3 =’0’)

then odd_out <= "0";

even_out <= "0";

else

p_odd <= (((a0 xor a1) xor a2) xor a3);

p_even <= not(((a0 xor a1) xor a2) xor a3);

end vcgandhiФормы волны

В этой главе объясняется, как программировать VHDL для последовательных цепей.

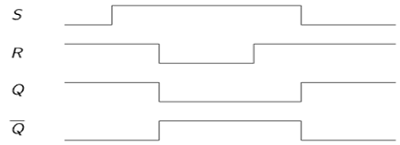

Код VHDL для защелки SR

library ieee;

use ieee.std_logic_1164.all;

entity srl is

port(r,s:in bit; q,qbar:buffer bit);

end srl;

architecture virat of srl is

signal s1,r1:bit;

begin

q<= s nand qbar;

qbar<= r nand q;

end virat;Формы волны

Код VHDL для D-защелки

library ieee;

use ieee.std_logic_1164.all;

entity Dl is

port(d:in bit; q,qbar:buffer bit);

end Dl;

architecture virat of Dl is

signal s1,r1:bit;

begin

q<= d nand qbar;

qbar<= d nand q;

end virat;Формы волны

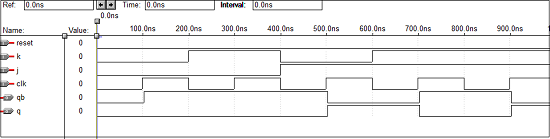

Код VHDL для SR триггера

library ieee;

use ieee.std_logic_1164.all;

entity srflip is

port(r,s,clk:in bit; q,qbar:buffer bit);

end srflip;

architecture virat of srflip is

signal s1,r1:bit;

begin

s1<=s nand clk;

r1<=r nand clk;

q<= s1 nand qbar;

qbar<= r1 nand q;

end virat;Формы волны

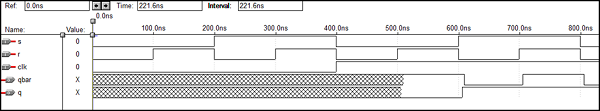

Код VHDL для JK Flip Flop

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity jk is

port(

j : in STD_LOGIC;

k : in STD_LOGIC;

clk : in STD_LOGIC;

reset : in STD_LOGIC;

q : out STD_LOGIC;

qb : out STD_LOGIC

);

end jk;

architecture virat of jk is

begin

jkff : process (j,k,clk,reset) is

variable m : std_logic := '0';

begin

if (reset = '1') then

m : = '0';

elsif (rising_edge (clk)) then

if (j/ = k) then

m : = j;

elsif (j = '1' and k = '1') then

m : = not m;

end if;

end if;

q <= m;

qb <= not m;

end process jkff;

end virat;Формы волны

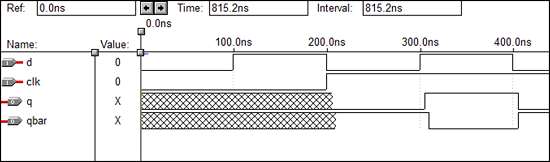

Код VHDL для D-триггера

Library ieee;

use ieee.std_logic_1164.all;

entity dflip is

port(d,clk:in bit; q,qbar:buffer bit);

end dflip;

architecture virat of dflip is

signal d1,d2:bit;

begin

d1<=d nand clk;

d2<=(not d) nand clk;

q<= d1 nand qbar;

qbar<= d2 nand q;

end virat;Формы волны

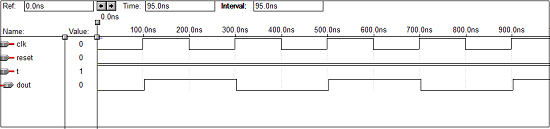

Код VHDL для T-триггера

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity Toggle_flip_flop is

port(

t : in STD_LOGIC;

clk : in STD_LOGIC;

reset : in STD_LOGIC;

dout : out STD_LOGIC

);

end Toggle_flip_flop;

architecture virat of Toggle_flip_flop is

begin

tff : process (t,clk,reset) is

variable m : std_logic : = '0';

begin

if (reset = '1') then

m : = '0';

elsif (rising_edge (clk)) then

if (t = '1') then

m : = not m;

end if;

end if;

dout < = m;

end process tff;

end virat;Формы волны

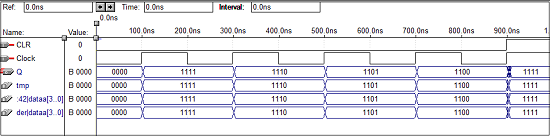

Код VHDL для 4-битного счетчика вверх

library IEEE;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity counter is

port(Clock, CLR : in std_logic;

Q : out std_logic_vector(3 downto 0)

);

end counter;

architecture virat of counter is

signal tmp: std_logic_vector(3 downto 0);

begin

process (Clock, CLR)

begin

if (CLR = '1') then

tmp < = "0000";

elsif (Clock'event and Clock = '1') then

mp <= tmp + 1;

end if;

end process;

Q <= tmp;

end virat;Формы волны

Код VHDL для 4-битного обратного счетчика

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity dcounter is

port(Clock, CLR : in std_logic;

Q : out std_logic_vector(3 downto 0));

end dcounter;

architecture virat of dcounter is

signal tmp: std_logic_vector(3 downto 0);

begin

process (Clock, CLR)

begin

if (CLR = '1') then

tmp <= "1111";

elsif (Clock'event and Clock = '1') then

tmp <= tmp - 1;

end if;

end process;

Q <= tmp;

end virat;Формы волны

Verilog - это ЯЗЫК ОПИСАНИЯ АППАРАТНОГО ОБЕСПЕЧЕНИЯ (HDL). Это язык, используемый для описания цифровой системы, такой как сетевой коммутатор, микропроцессор, память или триггер. Это означает, что с помощью HDL мы можем описать любое цифровое оборудование на любом уровне. Проекты, описанные в HDL, не зависят от технологии, очень просты для проектирования и отладки и обычно более полезны, чем схемы, особенно для больших схем.

Verilog поддерживает дизайн на многих уровнях абстракции. Основные три -

- Поведенческий уровень

- Уровень регистрации-передачи

- Уровень ворот

Поведенческий уровень

Этот уровень описывает систему с помощью параллельных алгоритмов (поведенческих). Каждый алгоритм является последовательным, что означает, что он состоит из набора инструкций, которые выполняются одна за другой. Функции, задачи и блоки - это основные элементы. Нет никакого отношения к структурной реализации дизайна.

Регистр-Уровень передачи

Проекты, использующие уровень передачи регистров, определяют характеристики схемы, использующей операции и передачу данных между регистрами. Современное определение кода RTL: «Любой код, который можно синтезировать, называется кодом RTL».

Уровень ворот

На логическом уровне характеристики системы описываются логическими связями и их временными характеристиками. Все сигналы дискретные. Они могут иметь только определенные логические значения («0», «1», «X», «Z»). Используемые операции - это предопределенные логические примитивы (базовые вентили). Моделирование на уровне ворот может быть неправильной идеей для логического проектирования. Код уровня ворот генерируется с использованием таких инструментов, как инструменты синтеза, а его список соединений используется для моделирования уровня ворот и для бэкэнда.

Лексические токены

Исходные текстовые файлы на языке Verilog представляют собой поток лексических токенов. Токен состоит из одного или нескольких символов, и каждый отдельный символ находится ровно в одном токене.

Основные лексические токены, используемые Verilog HDL, аналогичны токенам в языке программирования C. Verilog чувствителен к регистру. Все ключевые слова в нижнем регистре.

Белое пространство

Пробелы могут содержать символы для пробелов, табуляции, новых строк и каналов формы. Эти символы игнорируются, кроме случаев, когда они служат для разделения токенов.

Символы пробела - это пустое пространство, табуляция, возврат каретки, новая строка и подача формы.

Комментарии

Есть две формы для представления комментариев

- 1) Однострочные комментарии начинаются с токена // и заканчиваются возвратом каретки.

Пример: // это однострочный синтаксис

- 2) Многострочные комментарии начинаются с токена / * и заканчиваются токеном * /

Пример: / * это многострочный синтаксис * /

Числа

Вы можете указать число в двоичном, восьмеричном, десятичном или шестнадцатеричном формате. Отрицательные числа представлены двумя дополнительными числами. Verilog позволяет использовать целые и действительные числа, а также числа со знаком и без знака.

Синтаксис задается - <размер> <основание> <значение>

Размер или число без размера можно определить в <Size>, а <radix> определяет, является ли он двоичным, восьмеричным, шестнадцатеричным или десятичным.

Идентификаторы

Идентификатор - это имя, используемое для определения объекта, такого как функция, модуль или регистр. Идентификаторы должны начинаться с буквенного символа или символа подчеркивания. Ex. A_Z, a_z, _

Идентификаторы представляют собой комбинацию букв, цифр, подчеркивания и символов $. Они могут иметь длину до 1024 символов.

Операторы

Операторы - это специальные символы, используемые для задания условий или работы с переменными. Для выполнения операций с переменными используются один, два, а иногда и три символа.

Ex. >, +, ~, &! знак равно

Ключевые слова Verilog

Слова, имеющие особое значение в Verilog, называются ключевыми словами Verilog. Например, assign, case, while, wire, reg, and, or, nand и module. Их не следует использовать в качестве идентификаторов. Ключевые слова Verilog также включают директивы компилятора, а также системные задачи и функции.

Моделирование на уровне ворот

Verilog имеет встроенные примитивы, такие как логические вентили, шлюзы передачи и переключатели. Они редко используются для проектных работ, но они используются в мире постсинтеза для моделирования ячеек ASIC / FPGA.

Моделирование на уровне ворот демонстрирует два свойства:

Drive strength- Мощность выходных вентилей определяется силой привода. Выход будет самым сильным, если есть прямое соединение с источником. Сила уменьшается, если соединение осуществляется через проводящий транзистор, и меньше всего - через резистивный подтягивающий / понижающий резистор. Сила привода обычно не указывается, и в этом случае по умолчанию используются значения strong1 и strong0.

Delays- Если задержки не указаны, то у шлюзов нет задержек распространения; если указаны две задержки, то первая представляет задержку нарастания, а вторая - задержку спада; если указана только одна задержка, то и подъем, и спад равны. При синтезе задержки можно не учитывать.

Примитивы ворот

В Verilog используются базовые логические элементы, использующие один выход и множество входов. GATE использует одно из ключевых слов - and, nand, or, nor, xor, xnor для использования в Verilog для числа N входов и 1 выхода.

Example:

Module gate()

Wire ot0;

Wire ot1;

Wire ot2;

Reg in0,in1,in2,in3;

Not U1(ot0,in0);

Xor U2(ot1,in1,in2,in3);

And U3(ot2, in2,in3,in0)Примитивы шлюза передачи

Примитивы шлюза передачи включают как буферы, так и инверторы. У них есть один вход и один или несколько выходов. В синтаксисе создания экземпляра шлюза, показанном ниже, GATE означает ключевое слово buf или NOT gate.

Пример: Not, buf, bufif0, bufif1, notif0, notif1.

Not - n outout инвертор

Buf - n выходной буфер

Bufifo - трехсторонний буфер, активный низкий уровень включения

Bufif1 - трехсторонний буфер, активный высокий уровень включения

Notifo - трехступенчатый инвертор, активный низкий уровень разрешения

Notif1 - трехступенчатый инвертор, активный высокий уровень разрешения

Example:

Module gate()

Wire out0;

Wire out1;

Reg in0,in1;

Not U1(out0,in0);

Buf U2(out0,in0);Типы данных

Набор значений

Verilog состоит, в основном, из четырех основных ценностей. Все типы данных Verilog, которые используются в Verilog, хранят эти значения -

0 (логический ноль или ложное состояние)

1 (логическая единица, или истинное состояние)

x (неизвестное логическое значение)

z (состояние с высоким импедансом)

использование x и z для синтеза очень ограничено.

провод

Провод используется для обозначения физического провода в цепи и используется для соединения ворот или модулей. Значение провода можно только прочитать и не присвоить функции или блоку. Провод не может хранить значение, но всегда управляется оператором непрерывного присваивания или подключением провода к выходу элемента / модуля. Другие особые типы проводов:

Wand (wired-AND) - здесь значение Wand зависит от логического И всех подключенных к нему драйверов устройств.

Wor (wired-OR) - здесь значение Wor зависит от логического ИЛИ всех подключенных к нему драйверов устройств.

Tri (three-state) - здесь все драйверы, подключенные к tri, должны быть z, кроме одного (который определяет значение tri).

Example:

Wire [msb:lsb] wire_variable_list;

Wirec // simple wire

Wand d;

Assign d = a; // value of d is the logical AND of

Assign d = b; // a and b

Wire [9:0] A; // a cable (vector) of 10 wires.

Wand [msb:lsb] wand_variable_list;

Wor [msb:lsb] wor_variable_list;

Tri [msb:lsb] tri_variable_list;регистр

Reg (регистр) - это объект данных, который хранит значение от одного процедурного присвоения к следующему и используется только в различных функциях и процедурных блоках. Reg - это простой Verilog регистр переменного типа, который не может подразумевать физический регистр. В многобитовых регистрах данные хранятся в виде чисел без знака, и знаковое расширение не используется.

Пример -

reg c; // одиночная 1-битная регистровая переменная

рег [5: 0] драгоценный камень; // 6-битный вектор;

рег [6: 0] д, д; // две 7-битные переменные

Вход, выход, вход

Эти ключевые слова используются для объявления портов ввода, вывода и двунаправленных портов задачи или модуля. Здесь входные и входные порты, которые относятся к проводному типу, а выходной порт сконфигурирован как провод, рег, палочка, рабочий или тройной тип. Всегда по умолчанию используется тип провода.

Example

Module sample(a, c, b, d);

Input c; // An input where wire is used.

Output a, b; // Two outputs where wire is used.

Output [2:0] d; /* A three-bit output. One must declare type in a separate statement. */

reg [1:0] a; // The above ‘a’ port is for declaration in reg.Целое число

Целые числа используются в переменных общего назначения. Они используются в основном в индикаторах циклов, константах и параметрах. Они относятся к типу данных reg. Они хранят данные как числа со знаком, тогда как явно объявленные типы reg хранят их как данные без знака. Если целое число не определено во время компиляции, то размер по умолчанию будет 32 бита.

Если целое число содержит константу, синтезатор настраивает их на минимальную ширину, необходимую во время компиляции.

Example

Integer c; // single 32-bit integer

Assign a = 63; // 63 defaults to a 7-bit variable.Supply0, Supply1

Supply0 определяет провода, привязанные к логическому 0 (земля), а supply1 определяет провода, связанные с логической 1 (питание).

Example

supply0 logic_0_wires;

supply0 gnd1; // equivalent to a wire assigned as 0

supply1 logic_1_wires;

supply1 c, s;Время

Время - это 64-битная величина, которую можно использовать вместе с системной задачей $ time для хранения времени моделирования. Время не поддерживается для синтеза и поэтому используется только для целей моделирования.

Example

time time_variable_list;

time c;

c = $time; //c = current simulation timeПараметр

Параметр определяет константу, которая может быть установлена при использовании модуля, что позволяет настраивать модуль в процессе создания экземпляра.

Example

Parameter add = 3’b010, sub = 2’b11;

Parameter n = 3;

Parameter [2:0] param2 = 3’b110;

reg [n-1:0] jam; /* A 3-bit register with length of n or above. */

always @(z)

y = {{(add - sub){z}};

if (z)

begin

state = param2[1];

else

state = param2[2];

endОператоры

Арифметические операторы

Эти операторы выполняют арифметические операции. + И - используются как унарные (x) или как бинарные (z − y) операторы.

Операторы, которые включены в арифметические операции:

+ (сложение), - (вычитание), * (умножение), / (деление),% (модуль)

Example -

parameter v = 5;

reg[3:0] b, d, h, i, count;

h = b + d;

i = d - v;

cnt = (cnt +1)%16; //Can count 0 thru 15.Операторы отношения

Эти операторы сравнивают два операнда и возвращают результат в виде одного бита, 1 или 0.

Переменные Wire и reg положительны. Таким образом, (−3'd001) = = 3'd111 и (−3b001)> 3b110.

Операторы, которые включены в реляционную операцию:

- == (равно)

- != (Не равно)

- > (больше чем)

- > = (больше или равно)

- <(меньше чем)

- <= (меньше или равно)

Example

if (z = = y) c = 1;

else c = 0; // Compare in 2’s compliment; d>b

reg [3:0] d,b;

if (d[3]= = b[3]) d[2:0] > b[2:0];

else b[3];

Equivalent Statement

e = (z == y);Битовые операторы

Побитовые операторы, выполняющие побитовое сравнение двух операндов.

Операторы, которые включены в побитовую операцию:

- & (побитовое И)

- | (побитовое ИЛИ)

- ~ (побитовое НЕ)

- ^ (побитовое исключающее ИЛИ)

- ~ ^ или ^ ~ (побитовое исключающее ИЛИ)

Example

module and2 (d, b, c);

input [1:0] d, b;

output [1:0] c;

assign c = d & b;

end moduleЛогические операторы

Логические операторы - это побитовые операторы, которые используются только для однобитовых операндов. Они возвращают одно битовое значение, 0 или 1. Они могут работать с целыми числами или группой битов, выражениями и обрабатывать все ненулевые значения как 1. Логические операторы обычно используются в условных операторах, поскольку они работают с выражениями.

Операторы, которые включены в логическую операцию:

- ! (логическое НЕ)

- && (логическое И)

- || (логическое ИЛИ)

Example

wire[7:0] a, b, c; // a, b and c are multibit variables.

reg x;

if ((a == b) && (c)) x = 1; //x = 1 if a equals b, and c is nonzero.

else x = !a; // x =0 if a is anything but zero.Операторы редукции

Операторы сокращения являются унарной формой побитовых операторов и работают со всеми битами вектора операнда. Они также возвращают однобитовое значение.

Операторы, которые включены в операцию сокращения:

- & (сокращение И)

- | (уменьшение ИЛИ)

- ~ & (сокращение NAND)

- ~ | (сокращение NOR)

- ^ (сокращение XOR)

- ~ ^ или ^ ~ (сокращение XNOR)

Example

Module chk_zero (x, z);

Input [2:0] x;

Output z;

Assign z = & x; // Reduction AND

End moduleОператоры смены

Операторы сдвига, которые сдвигают первый операнд на количество бит, указанное вторым операндом в синтаксисе. Вакантные должности заполняются нулями для обоих направлений, сдвигов влево и вправо (расширение знака не используется).

Операторы, которые включены в операцию Shift:

- << (сдвиг влево)

- >> (сдвиг вправо)

Example

Assign z = c << 3; /* z = c shifted left 3 bits;Вакансии заполняются нулями * /

Оператор конкатенации

Оператор конкатенации объединяет два или более операнда для формирования большего вектора.

Оператор, включенный в операцию конкатенации, - {} (конкатенация)

Example

wire [1:0] a, h; wire [2:0] x; wire [3;0] y, Z;

assign x = {1’b0, a}; // x[2] = 0, x[1] = a[1], x[0] = a[0]

assign b = {a, h}; /* b[3] = a[1], b[2] = a[0], b[1] = h[1],

b[0] = h[0] */

assign {cout, b} = x + Z; // Concatenation of a resultОператор репликации

Оператор репликации создает несколько копий элемента.

Оператор, используемый в операции репликации, - {n {item}} (n-кратная репликация элемента)

Example

Wire [1:0] a, f; wire [4:0] x;

Assign x = {2{1’f0}, a}; // Equivalent to x = {0,0,a }

Assign y = {2{a}, 3{f}}; //Equivalent to y = {a,a,f,f}

For synthesis, Synopsis did not like a zero replication.

For example:-

Parameter l = 5, k = 5;

Assign x = {(l-k){a}}Условный оператор

Условный оператор синтезирует мультиплексор. Это тот же тип, что и в C / C ++, и вычисляет одно из двух выражений на основе условия.

Оператор, используемый в условной операции, -

(Состояние) ? (Результат, если условие истинно) -

(результат, если условие ложно)

Example

Assign x = (g) ? a : b;

Assign x = (inc = = 2) ? x+1 : x-1;

/* if (inc), x = x+1, else x = x-1 */Операнды

Литералы

Литералы - это операнды с постоянным знаком, которые используются в выражениях Verilog. Два обычно используемых литерала Verilog:

String - Операнд строкового литерала - это одномерный массив символов, заключенный в двойные кавычки ("").

Numeric - Операнд постоянного числа указывается в виде двоичного, восьмеричного, десятичного или шестнадцатеричного числа.

Example

n - целое число, представляющее количество битов

F - один из четырех возможных базовых форматов -

b для двоичного, o для восьмеричного, d для десятичного, h для шестнадцатеричного.

“time is” // string literal

267 // 32-bit decimal number

2’b01 // 2-bit binary

20’hB36F // 20-bit hexadecimal number

‘062 // 32-bit octal numberПровода, регистры и параметры

Провода, регистры и параметры - это типы данных, используемые в качестве операндов в выражениях Verilog.

Выбор битов «x [2]» и выбор партии «x [4: 2]»

Выбор битов и выбор части используются для выбора одного и нескольких битов, соответственно, из провода, регистра или вектора параметров с использованием квадратных скобок «[]». Выборки по битам и выборки по частям также используются в качестве операндов в выражениях таким же образом, как и их основные объекты данных.

Example

reg [7:0] x, y;

reg [3:0] z;

reg a;

a = x[7] & y[7]; // bit-selects

z = x[7:4] + y[3:0]; // part-selectsВызов функций

В вызовах функций возвращаемое значение функции используется непосредственно в выражении без необходимости сначала назначать его регистру или проводу. Он просто помещает вызов функции как один из типов операндов. Необходимо убедиться, что вы знаете разрядность возвращаемого значения вызова функции.

Example

Assign x = y & z & chk_yz(z, y); // chk_yz is a function

. . ./* Definition of the function */

Function chk_yz; // function definition

Input z,y;

chk_yz = y^z;

End functionМодули

Объявление модуля

В Verilog модуль является основным элементом дизайна. Это указывает имя и список портов (аргументы). Следующие несколько строк определяют тип ввода / вывода (ввод, вывод или ввод) и ширину каждого порта. Ширина порта по умолчанию составляет всего 1 бит. Переменные порта должны быть объявлены wire, wand ,. . ., рег. Переменная порта по умолчанию - wire. Обычно входы являются проводными, потому что их данные фиксируются вне модуля. Выходы относятся к типу reg, если их сигналы хранятся внутри.

Example

module sub_add(add, in1, in2, out);

input add; // defaults to wire

input [7:0] in1, in2; wire in1, in2;

output [7:0] out; reg out;

... statements ...

End moduleНепрерывное присвоение

Непрерывное присвоение в модуле используется для присвоения значения проводу, которое является нормальным назначением, используемым вне всегда или начальных блоков. Это присвоение выполняется с помощью явного оператора assign или для присвоения значения проводнику во время его объявления. Непрерывное присвоение непрерывно выполняется во время моделирования. Порядок операторов присваивания на это не влияет. Если вы сделаете какие-либо изменения в любом из сигналов правого входа, это изменит выходной сигнал левого края.

Example

Wire [1:0] x = 2’y01; // assigned on declaration

Assign y = c | d; // using assign statement

Assign d = a & b;

/* the order of the assign statements does not matter. */Модульные экземпляры

Объявления модулей - это шаблоны для создания реальных объектов. Модули создаются внутри других модулей, и каждый экземпляр создает один объект из этого шаблона. Исключением является модуль верхнего уровня, который является его собственным экземпляром. Порты модуля должны соответствовать тем, которые определены в шаблоне. Уточнено -

By name, используя точку «.template имя порта (имя провода, подключенного к порту)». Или же

By position, поместив порты в одно и то же место в списках портов как в шаблоне, так и в экземпляре.

Example

MODULE DEFINITION

Module and4 (x, y, z);

Input [3:0] x, y;

Output [3:0] z;

Assign z = x | y;

End moduleПоведенческие модели в Verilog содержат процедурные операторы, которые управляют симуляцией и манипулируют переменными типов данных. Все эти утверждения содержатся в процедурах. Каждая процедура имеет связанный с ней поток действий.

Во время симуляции поведенческой модели все потоки, определяемые операторами «всегда» и «начальный», начинаются вместе в «нулевом» времени симуляции. Начальные операторы выполняются один раз, а операторы always - повторно. В этой модели регистровые переменные a и b инициализируются двоичными значениями 1 и 0 соответственно в нулевое время моделирования. Затем начальный оператор завершается и больше не выполняется во время этого прогона моделирования. Этот начальный оператор содержит начальный и конечный блок (также называемый последовательным блоком) операторов. В этом блоке типа начало-конец сначала инициализируется a, а затем b.

Пример поведенческого моделирования

module behave;

reg [1:0]a,b;

initial

begin

a = ’b1;

b = ’b0;

end

always

begin

#50 a = ~a;

end

always

begin

#100 b = ~b;

end

End moduleПроцедурные задания

Процедурные назначения предназначены для обновления переменных reg, integer, time и memory. Существует значительная разница между процедурным назначением и непрерывным назначением, как описано ниже -

Непрерывные назначения управляют сетевыми переменными и оцениваются и обновляются всякий раз, когда входной операнд меняет значение.

Процедурные назначения обновляют значение регистровых переменных под контролем окружающих их процедурных конструкций потока.