Проектирование СБИС - последовательные логические схемы МОП

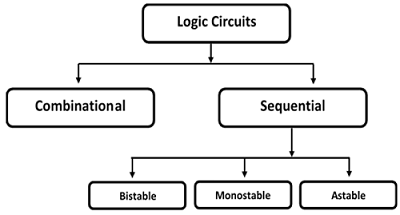

Логические схемы делятся на две категории: (а) Комбинационные схемы и (б) Последовательные схемы.

В комбинационных схемах выход зависит только от состояния последних входов.

В последовательных схемах выход зависит не только от последних входов, но и от состояния более ранних входов. Последовательные схемы содержат элементы памяти.

Последовательные схемы бывают трех типов -

Bistable- Бистабильные схемы имеют две устойчивые рабочие точки и будут находиться в любом из состояний. Пример - ячейки памяти, защелки, триггеры и регистры.

Monostable- Моностабильные схемы имеют только одну стабильную рабочую точку, и даже если они временно переведены в противоположное состояние, они со временем вернутся к своей стабильной рабочей точке. Пример: таймеры, генераторы импульсов.

Astable- схемы не имеют стабильной рабочей точки и колеблются между несколькими состояниями. Пример - кольцевой генератор.

Логические схемы CMOS

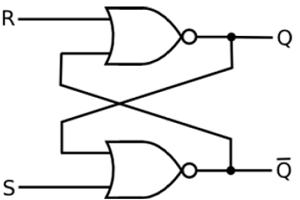

Защелка SR на базе NOR Gate

Если установленный вход (S) равен логическому "1" а вход сброса равен логике "0." тогда выход Q будет переведен в логическую "1". Пока $ \ overline {Q} $ вынужден использовать логику"0". Это означает, что защелка SR будет установлена независимо от ее предыдущего состояния.

Аналогично, если S равно «0», а R равно "1" тогда выход Q будет вынужден "0" в то время как $ \ overline {Q} $ вынужден "1". Это означает, что защелка сбрасывается независимо от ее ранее удерживаемого состояния. Наконец, если оба входа S и R равны логическому"1" тогда оба выхода будут переведены в логическую "0" что противоречит дополнительности Q и $ \ overline {Q} $.

Поэтому такая комбинация входов недопустима во время нормальной работы. Таблица истинности SR Latch на основе NOR приведена в таблице.

| S | р | Q | $ \ overline {Q} $ | Операция |

|---|---|---|---|---|

| 0 | 0 | Q | $ \ overline {Q} $ | Держать |

| 1 | 0 | 1 | 0 | Набор |

| 0 | 1 | 0 | 1 | Сброс |

| 1 | 1 | 0 | 0 | Не допускается |

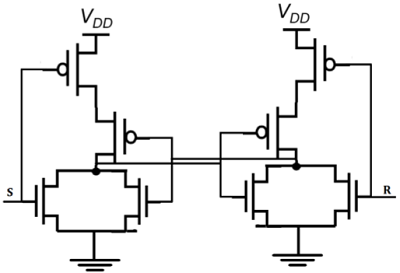

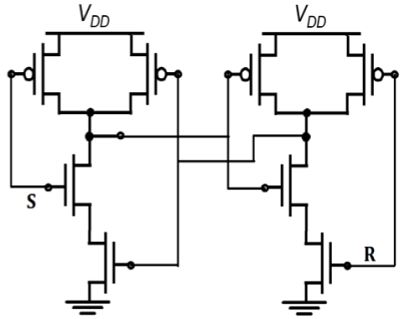

Защелка CMOS SR на основе логического элемента ИЛИ-НЕ показана на рисунке ниже.

Если S равно V OH, а R равно V OL , оба параллельно соединенных транзистора M1 и M2 будут включены. Напряжение на узле $ \ overline {Q} $ примет низкий логический уровень V OL = 0.

В то же время оба M3 и M4 выключены, что приводит к высокому логическому напряжению V OH в узле Q. Если R равно V OH, а S равно V OL , M1 и M2 выключены и Включились М3 и М4.

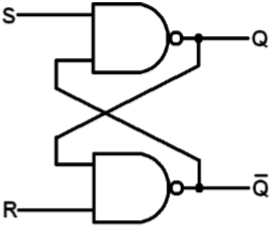

Защелка SR на основе NAND Gate

Блок-схема и схема уровня затвора защелки SR на основе NAND показана на рисунке. Маленькие кружки на входных клеммах S и R показывают, что схема реагирует на активные низкие входные сигналы. Таблица истинности SR защелки на основе NAND приведена в таблице.

| S | р | Q | Q ′ | |

| 0 | 0 | NC | NC | Без изменений. Защелка осталась в нынешнем состоянии. |

| 1 | 0 | 1 | 0 | Защелка SET. |

| 0 | 1 | 0 | 1 | Защелкните RESET. |

| 1 | 1 | 0 | 0 | Неверное состояние. |

Если S переходит в 0 (в то время как R = 1), Q переходит в высокий уровень, тянет $ \ overline {Q} $ на низкий уровень, и защелка переходит в состояние Set.

S = 0 тогда Q = 1 (если R = 1)

Если R переходит в 0 (в то время как S = 1), Q становится высоким, тянет $ \ overline {Q} $ на низкий уровень и защелка сбрасывается

R = 0 тогда Q = 1 (если S = 1)

Состояние удержания требует, чтобы как S, так и R. Если S = R = 0, то вывод не разрешен, так как это приведет к неопределенному состоянию. Защелка CMOS SR на основе NAND Gate показана на рисунке.

Защелка nMOS SR для истощения нагрузки на основе NAND Gate показана на рисунке. Работа аналогична защелке CMOS NAND SR. Реализация схемы CMOS имеет низкое статическое рассеяние мощности и высокий запас шума.

Логические схемы CMOS

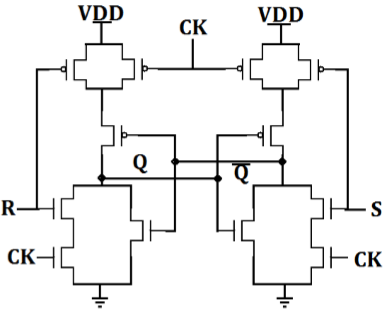

Тактовая защелка SR

На рисунке показана защелка SR на основе NOR с добавленными часами. Защелка реагирует на входы S и R только при высоком уровне CLK.

Когда CLK низкий, защелка сохраняет свое текущее состояние. Обратите внимание, что Q меняет состояние -

- Когда S становится высоким во время положительного CLK.

- На переднем фронте CLK после изменений в S&R во время низкого уровня CLK.

- Положительный сбой в S при высоком уровне CLK

- Когда R становится высоким во время положительного CLK.

Реализация CMOS AOI синхронизированной защелки SR на основе NOR показана на рисунке. Обратите внимание, что требуется всего 12 транзисторов.

Когда CLK низкий, два последовательных терминала в дереве N открыты, а два параллельных транзистора в дереве P включены, таким образом сохраняя состояние в ячейке памяти.

Когда тактовый сигнал высокий, схема становится просто защелкой CMOS на основе ИЛИ-НЕ, которая будет реагировать на входные сигналы S и R.

Clocked SR Latch based on NAND Gate

Схема реализована с четырьмя вентилями NAND. Если эта схема реализована на КМОП-матрице, то требуется 16 транзисторов.

- Защелка реагирует на S или R, только если CLK высокий.

- Если и входные сигналы, и сигналы CLK активны на высоком уровне: то есть, выход защелки Q будет установлен, когда CLK = "1", S = "1" и R = "0"

- Точно так же защелка будет сброшена, когда CLK = "1", S = "0" и

Когда CLK низкий, защелка сохраняет свое текущее состояние.

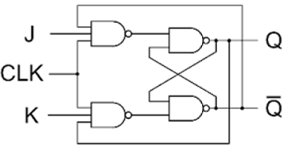

Тактовая защелка JK

На рисунке выше показана защелка JK с синхронизацией на основе вентилей NAND. Недостатком защелки SR является то, что, когда и S, и R высокие, ее выходное состояние становится неопределенным. Защелка JK устраняет эту проблему, используя обратную связь от выхода ко входу, так что все входные состояния таблицы истинности допустимы. Если J = K = 0, защелка сохранит свое текущее состояние.

Если J = 1 и K = 0, защелка будет установлена на следующем положительном фронте тактового сигнала, то есть Q = 1, $ \ overline {Q} $ = 0

Если J = 0 и K = 1, защелка будет сброшена на следующем положительном фронте тактового сигнала, т.е. Q = 1 и $ \ overline {Q} $ = 0.

Если J = K = 1, защелка переключится на следующий положительный фронт синхросигнала.

Работа синхронизированной защелки JK суммирована в таблице истинности, приведенной в таблице.

J |

K |

Q |

$ \ overline {Q} $ | S |

R |

Q |

$ \ overline {Q} $ | Operation |

| 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | Держать |

| 1 | 0 | 1 | 1 | 1 | 0 | |||

| 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | Сброс |

| 1 | 0 | 1 | 0 | 0 | 1 | |||

| 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | Набор |

| 1 | 0 | 1 | 1 | 1 | 0 | |||

| 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | переключить |

| 1 | 0 | 1 | 0 | 0 | 1 |

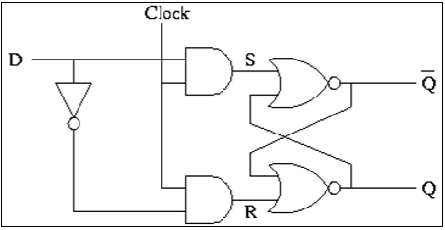

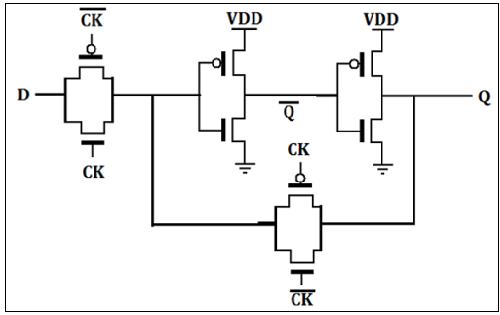

Реализация защелки CMOS D

D-защелка обычно реализуется с помощью переключателей затвора передачи (TG), как показано на рисунке. Вход TG активируется с помощью CLK, в то время как петля обратной связи с защелкой TG активируется с помощью CLK. Вход D принимается, когда CLK высокий. Когда CLK становится низким, вход разомкнут и фиксатор устанавливается с предыдущими данными D.