Circuito integrado de bucle de bloqueo de fase

Bucle de fase bloqueada (PLL)es uno de los bloques vitales en los sistemas lineales. Es útil en sistemas de comunicación como radares, satélites, FM, etc.

Este capítulo trata en detalle sobre el diagrama de bloques de PLL e IC 565.

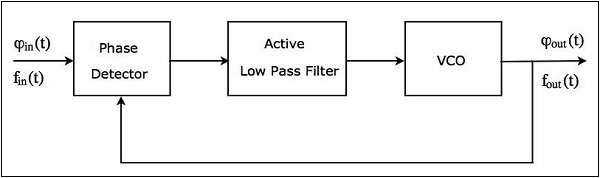

Diagrama de bloques de PLL

Un bucle de bloqueo de fase (PLL) consta principalmente de lo siguiente three blocks -

- Detector de fase

- Filtro de paso bajo activo

- Oscilador controlado por voltaje (VCO)

los block diagram de PLL se muestra en la siguiente figura:

La salida de un detector de fase se aplica como entrada del filtro de paso bajo activo. De manera similar, la salida del filtro de paso bajo activo se aplica como entrada de VCO.

los working de un PLL es el siguiente:

Phase detector produce un voltaje de CC, que es proporcional a la diferencia de fase entre la señal de entrada que tiene una frecuencia de $ f_ {in} $ y la señal de retroalimentación (salida) que tiene una frecuencia de $ f_ {out} $.

UN Phase detector es un multiplicador y produce dos componentes de frecuencia en su salida: suma de las frecuencias $ f_ {in} $ y $ f_ {out} $ y diferencia de frecuencias $ f_ {in} $ & $ f_ {out} $.

Un active low pass filterproduce un voltaje de CC en su salida, después de eliminar el componente de alta frecuencia presente en la salida del detector de fase. También amplifica la señal.

UN VCOproduce una señal que tiene una cierta frecuencia, cuando no se le aplica ninguna entrada. Esta frecuencia se puede cambiar a cualquier lado aplicándole un voltaje de CC. Por lo tanto, la desviación de frecuencia es directamente proporcional al voltaje de CC presente en la salida de un filtro de paso bajo.

Las operaciones anteriores tienen lugar hasta que la frecuencia del VCO es igual a la frecuencia de la señal de entrada. Según el tipo de aplicación, podemos utilizar la salida del filtro de paso bajo activo o la salida de un VCO. Los PLL se utilizan en muchosapplications como demodulador de FM, generador de reloj, etc.

PLL opera en uno de los following three modes -

- Modo de ejecución libre

- Modo de captura

- Modo de bloqueo

Inicialmente, PLL opera en free running modecuando no se le aplica ninguna entrada. Cuando se aplica una señal de entrada que tiene alguna frecuencia a PLL, entonces la frecuencia de la señal de salida de VCO comenzará a cambiar. En esta etapa, se dice que el PLL está operando en elcapture mode. La frecuencia de la señal de salida de VCO cambiará continuamente hasta que sea igual a la frecuencia de la señal de entrada. Ahora, se dice que PLL está operando en ellock mode.

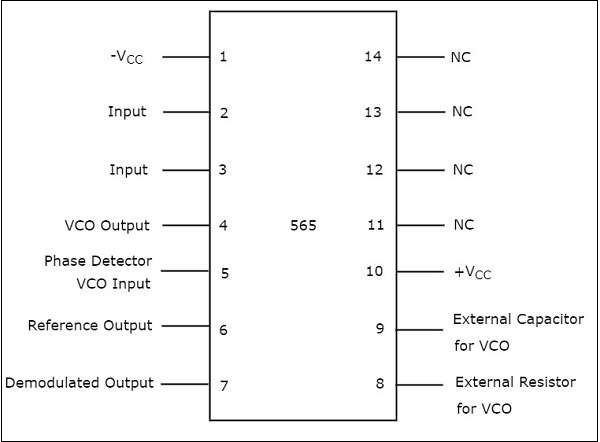

IC 565

IC 565 es el circuito integrado de bucle de bloqueo de fase más utilizado. Es un paquete de doble línea (DIP) de 14 pines. lospin diagram del IC 565 se muestra en la siguiente figura:

El propósito de cada pin se explica por sí mismo en el diagrama anterior. De 14 pines, solo 10 pines (pin número 1 a 10) se utilizan para el funcionamiento de PLL. Por lo tanto, los 4 pines restantes (número de pin 11 a 14) están etiquetados con NC (Sin conexión).

los VCOproduce una salida en el pin número 4 del IC 565, cuando los pin números 2 y 3 están conectados a tierra. Matemáticamente, podemos escribir la frecuencia de salida, $ f_ {out} $ del VCO como.

$$ f_ {out} = \ frac {0.25} {R_VC_V} $$

dónde,

$ R_ {V} $ es la resistencia externa que está conectada al pin número 8

$ C_ {V} $ es el condensador externo que está conectado al pin número 9

Al elegir los valores adecuados de $ R_ {V} $ y $ C_ {V} $, podemos fijar (determinar) la frecuencia de salida, $ f_ {out} $ de VCO.

Pin numbers 4 and 5deben estar en cortocircuito con un cable externo para que la salida de VCO pueda aplicarse como una de las entradas del detector de fase.

IC 565 tiene una resistencia interna de $ 3.6K \ Omega $. Un condensador, C tiene que estar conectado entre los pines números 7 y 10 para hacer unlow pass filter con esa resistencia interna.

Tenga en cuenta que según el requisito, tenemos que configurar correctamente los pines del IC 565.