フェーズロックループIC

フェーズロックループ (PLL)線形システムの重要なブロックの1つです。レーダー、衛星、FMなどの通信システムで役立ちます。

この章では、PLLとIC565のブロック図について詳しく説明します。

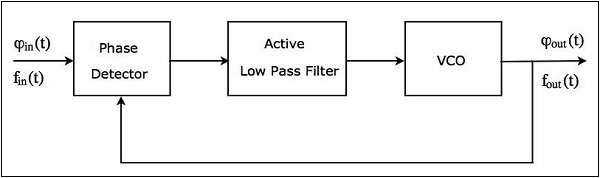

PLLのブロック図

フェーズロックループ(PLL)は、主に次のもので構成されます。 three blocks −

- 位相検出器

- アクティブローパスフィルター

- 電圧制御発振器(VCO)

ザ・ block diagram PLLの図を次の図に示します-

位相検出器の出力は、アクティブローパスフィルターの入力として適用されます。同様に、アクティブローパスフィルターの出力はVCOの入力として適用されます。

ザ・ working PLLの概要は次のとおりです。

Phase detector $ f_ {in} $の周波数を持つ入力信号と$ f_ {out} $の周波数を持つフィードバック(出力)信号の間の位相差に比例するDC電圧を生成します。

A Phase detector は乗数であり、出力で2つの周波数成分を生成します。周波数$ f_ {in} $と$ f_ {out} $の合計、および周波数の差$ f_ {in} $と$ f_ {out} $です。

アン active low pass filter位相検出器の出力に存在する高周波成分を除去した後、出力にDC電圧を生成します。また、信号を増幅します。

A VCO入力が適用されていないときに、特定の周波数を持つ信号を生成します。この周波数は、DC電圧を印加することでどちらの側にもシフトできます。したがって、周波数偏差は、ローパスフィルタの出力に存在するDC電圧に正比例します。

上記の操作は、VCO周波数が入力信号周波数と等しくなるまで行われます。アプリケーションのタイプに基づいて、アクティブローパスフィルターの出力またはVCOの出力のいずれかを使用できます。PLLは多くの場所で使用されていますapplications FM復調器、クロックジェネレータなど。

PLLは、 following three modes −

- フリーランニングモード

- キャプチャモード

- ロックモード

当初、PLLは free running mode入力が適用されていない場合。ある周波数の入力信号がPLLに印加されると、VCOの出力信号周波数が変化し始めます。この段階では、PLLはで動作していると言われていますcapture mode。VCOの出力信号周波数は、入力信号周波数と等しくなるまで連続的に変化します。現在、PLLはで動作していると言われていますlock mode。

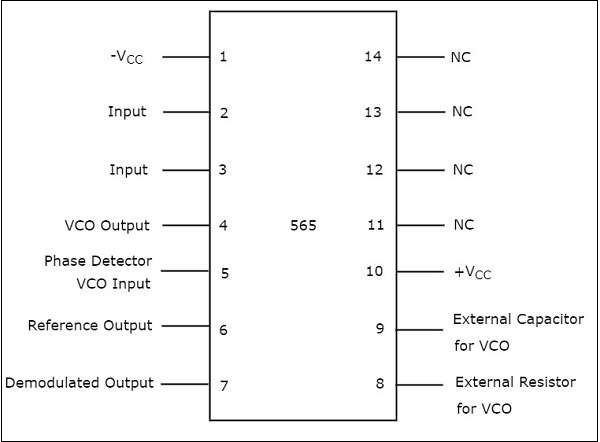

IC 565

IC 565は、最も一般的に使用されているフェーズロックループICです。これは、14ピンのデュアルインラインパッケージ(DIP)です。ザ・pin diagram IC565の概要を次の図に示します。

各ピンの目的は、上の図から自明です。14ピンのうち、PLLの動作には10ピン(ピン番号1〜10)のみが使用されます。したがって、残りの4つのピン(ピン番号11〜14)にはNC(接続なし)のラベルが付いています。

ザ・ VCOピン番号2と3が接地されている場合、IC565のピン番号4に出力を生成します。数学的には、VCOの出力周波数$ f_ {out} $をとして書くことができます。

$$ f_ {out} = \ frac {0.25} {R_VC_V} $$

どこ、

$ R_ {V} $は、ピン番号8に接続されている外部抵抗です。

$ C_ {V} $は、ピン番号9に接続されている外部コンデンサです。

$ R_ {V} $と$ C_ {V} $の適切な値を選択することにより、VCOの出力頻度$ f_ {out} $を修正(決定)できます。

Pin numbers 4 and 5VCOの出力を位相検出器の入力の1つとして適用できるように、外部ワイヤで短絡する必要があります。

IC565の内部抵抗は$ 3.6K \ Omega $です。コンデンサCは、ピン番号7と10の間に接続してlow pass filter その内部抵抗で。

要件に従って、IC565のピンを適切に構成する必要があることに注意してください。