Kluczowanie kwadraturowe z przesunięciem fazowym

Plik Quadrature Phase Shift Keying (QPSK) jest odmianą BPSK, a także jest schematem modulacji Double Side Band Suppressed Carrier (DSBSC), który wysyła jednocześnie dwa bity informacji cyfrowej, nazywany bigits.

Zamiast przekształcać bity cyfrowe w serię strumienia cyfrowego, konwertuje je na pary bitów. Zmniejsza to szybkość transmisji danych o połowę, co pozostawia miejsce dla innych użytkowników.

Modulator QPSK

Modulator QPSK wykorzystuje rozdzielacz bitów, dwa mnożniki z lokalnym oscylatorem, 2-bitowy konwerter szeregowy na równoległy oraz obwód letni. Poniżej znajduje się schemat blokowy tego samego.

Na wejściu modulatora, sygnał wiadomości nawet bitów (to znaczy, 2 nd bit 4 ty bit 6 ty bit, etc.) i nieparzystych bitów (to znaczy, 1 bit, 3 rd nieco, 5 ty bit, etc.) są oddzielone przez rozdzielacz bitów i są mnożone przez tę samą nośną w celu wygenerowania nieparzystego BPSK (nazywanego jakoPSKI), a nawet BPSK (tzw PSKQ). PlikPSKQ sygnał jest w każdym razie przesunięty fazowo o 90 ° przed modulacją.

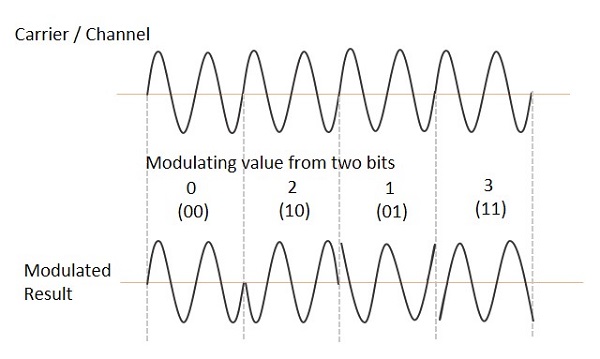

Przebieg QPSK dla wejścia dwubitowego jest następujący, który przedstawia modulowany wynik dla różnych instancji wejść binarnych.

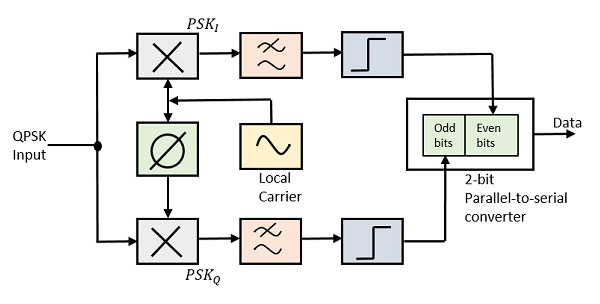

Demodulator QPSK

Demodulator QPSK wykorzystuje dwa obwody demodulatora produktu z lokalnym oscylatorem, dwoma filtrami pasmowo-przepustowymi, dwoma obwodami integratora i 2-bitowym konwerterem równoległym do szeregowego. Poniżej znajduje się schemat tego samego.

Dwa detektory produktu na wejściu demodulatora jednocześnie demodulują dwa sygnały BPSK. Para bitów jest tutaj odzyskiwana z oryginalnych danych. Sygnały te po przetworzeniu są przekazywane do konwertera równoległego na szeregowy.