Projekt VLSI - falownik MOS

Falownik jest naprawdę jądrem wszystkich projektów cyfrowych. Po jasnym zrozumieniu jego działania i właściwości projektowanie bardziej skomplikowanych struktur, takich jak bramki NAND, sumatory, mnożniki i mikroprocesory, jest znacznie uproszczone. Zachowanie elektryczne tych złożonych obwodów można prawie całkowicie wyliczyć poprzez ekstrapolację wyników uzyskanych dla falowników.

Analizę falowników można rozszerzyć, aby wyjaśnić zachowanie bardziej złożonych bramek, takich jak NAND, NOR lub XOR, które z kolei stanowią elementy składowe modułów, takich jak mnożniki i procesory. W tym rozdziale skupimy się na jednym wcieleniu bramki falownika, będącej statycznym falownikiem CMOS - lub w skrócie falownikiem CMOS. Jest to z pewnością obecnie najpopularniejszy i dlatego zasługuje na naszą szczególną uwagę.

Zasada działania

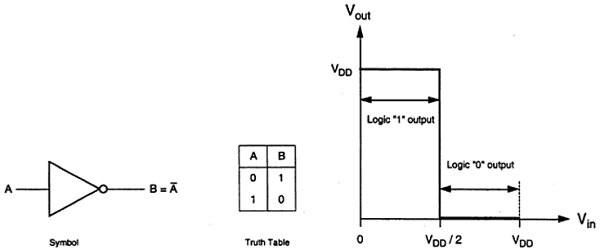

Symbol logiczny i tabela prawdy idealnego falownika pokazano na poniższym rysunku. Tutaj A to wejście, a B to odwrócone wyjście reprezentowane przez ich napięcia węzłowe. Korzystając z logiki dodatniej, wartość logiczna logiki 1 jest reprezentowana przez V dd, a logika 0 jest reprezentowana przez 0. V th jest napięciem progowym falownika, które wynosi V dd / 2, gdzie V dd jest napięciem wyjściowym.

Wyjście jest przełączane z 0 na V dd, gdy wejście jest mniejsze niż V th . Tak więc, dla 0 <V w <V th wyjściowy jest równy logicznej 0 wejściowego i V th <V w <V dd jest równa wartości logicznej 1 dla wejścia przetwornicy.

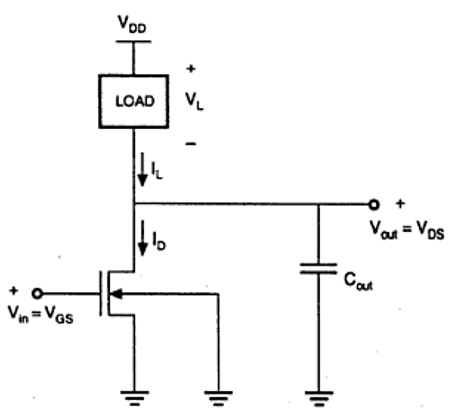

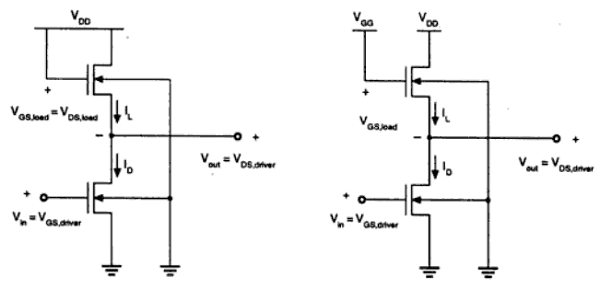

Cechy przedstawione na rysunku są idealne. Uogólnioną strukturę obwodu falownika nMOS pokazano na poniższym rysunku.

Z podanego rysunku widać, że napięcie wejściowe falownika jest równe napięciu bramki do źródła tranzystora nMOS, a napięcie wyjściowe falownika jest równe napięciu drenu do źródła tranzystora nMOS. Źródło napięcia podłoża nMOS jest również nazywane sterownikiem dla tranzystora, który jest uziemiony; więc V SS = 0. Węzeł wyjściowy jest połączony z kondensowaną pojemnością używaną dla VTC.

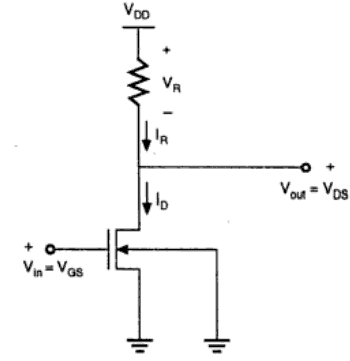

Rezystancyjny falownik obciążenia

Podstawową strukturę rezystancyjnego falownika obciążenia pokazano na poniższym rysunku. W tym przypadku jako tranzystor sterujący działa wzmacniacz typu nMOS. Obciążenia składa się prostą liniową rezystor R L . Zasilanie układu jest U DD i pobór prądu, że D jest równa obciążenia prądowego I R .

Działanie obwodu

Gdy napięcie wejściowe tranzystora sterownika jest mniejsze niż napięcie progowe V TH (V in <V TH ), tranzystor sterownika znajduje się w obszarze odcięcia i nie przewodzi prądu. Zatem spadek napięcia na rezystorze obciążenia wynosi ZERO, a napięcie wyjściowe jest równe V DD . Teraz, gdy napięcie wejściowe dalej rośnie, tranzystor sterownika zacznie przewodzić niezerowy prąd i nMOS przejdzie w obszar nasycenia.

Matematycznie,

$$I_{D} = \frac{K_{n}}{2}\left [ V_{GS}-V_{TO} \right ]^{2}$$

Zwiększając dalej napięcie wejściowe, tranzystor sterujący wejdzie w obszar liniowy, a wyjście tranzystora sterującego zmniejszy się.

$$I_{D} = \frac{K_{n}}{2}2\left [ V_{GS}-V_{TO} \right ]V_{DS}-V_{DS}^{2}$$

VTC falownika obciążenia rezystancyjnego, pokazane poniżej, wskazuje tryb pracy tranzystora sterownika i punkty napięciowe.

Falownik z obciążeniem MOSFET typu N.

Główną zaletą stosowania tranzystora MOSFET jako urządzenia obciążającego jest to, że obszar krzemu zajmowany przez tranzystor jest mniejszy niż obszar zajmowany przez obciążenie rezystancyjne. Tutaj MOSFET jest obciążeniem aktywnym, a falownik z aktywnym obciążeniem zapewnia lepszą wydajność niż falownik z obciążeniem rezystancyjnym.

Zwiększenie obciążenia NMOS

Rysunek przedstawia dwa falowniki z dodatkowym urządzeniem obciążającym. Tranzystor obciążający może działać w obszarze nasycenia lub w obszarze liniowym, w zależności od napięcia polaryzacji przyłożonego do jego zacisku bramki. Na rys. 1 przedstawiono nasycony falownik obciążenia wzmocnionego. (za). To wymaga pojedynczego napięcia zasilania i prosty sposób wytwarzania i tak V OH jest ograniczony do V DD - V , T .

Liniowy falownik wzmacniający obciążenie pokazano na rys. (b). Zawsze działa w regionie liniowym; więc poziom V OH jest równy V DD .

Liniowy falownik obciążenia ma wyższy margines szumów w porównaniu z nasyconym falownikiem wzmacniającym. Jednak wadą falownika ze wzmocnieniem liniowym jest to, że wymaga dwóch oddzielnych zasilaczy, a oba obwody mają duże straty mocy. Dlatego falowniki wzmacniające nie są używane w żadnych aplikacjach cyfrowych na dużą skalę.

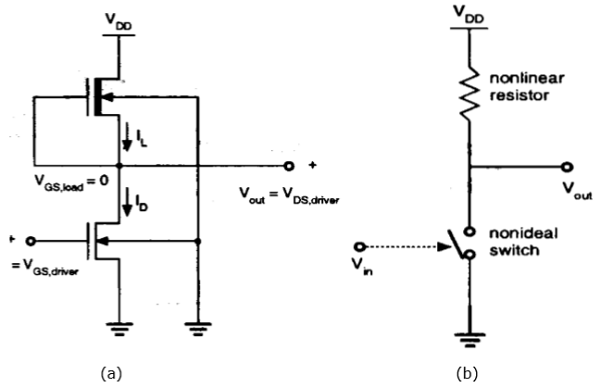

Wyczerpanie obciążenia NMOS

Wady falownika zwiększającego obciążenie można przezwyciężyć za pomocą falownika zubożonego obciążenia. W porównaniu z falownikiem wzmacniającym, falownik obciążenia zubożonego wymaga kilku dodatkowych kroków produkcyjnych w celu implantacji kanału w celu dostosowania napięcia progowego obciążenia.

Zaletami inwertera obciążenia wyczerpującego są - ostre przejście VTC, lepszy margines szumów, pojedynczy zasilacz i mniejszy całkowity obszar układu.

Jak pokazano na rysunku, bramka i zacisk źródła obciążenia są połączone; Zatem V GS = 0. Zatem napięcie progowe obciążenia jest ujemne. W związku z tym,

$$V_{GS,load}> V_{T,load}$$ jest spełniony

Dlatego urządzenie obciążające zawsze ma kanał przewodzący, niezależnie od poziomu napięcia wejściowego i wyjściowego.

Gdy tranzystor obciążenia znajduje się w obszarze nasycenia, prąd obciążenia jest określony przez

$$I_{D,load} = \frac{K_{n,load}}{2}\left [ -V_{T,load}\left ( V_{out} \right ) \right ]^{2}$$

Gdy tranzystor obciążenia jest w obszarze liniowym, prąd obciążenia jest określony przez

$$I_{D,load} = \frac{K_{n,load}}{2}\left [ 2\left | V_{T,load}\left ( V_{out} \right ) \right |.\left ( V_{DD}-V_{out} \right )-\left ( V_{DD}-V_{out} \right )^{2} \right ]$$

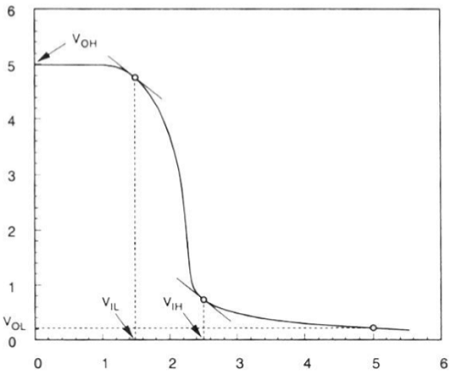

Charakterystykę przenoszenia napięcia falownika obciążenia zubożonego przedstawiono na poniższym rysunku -

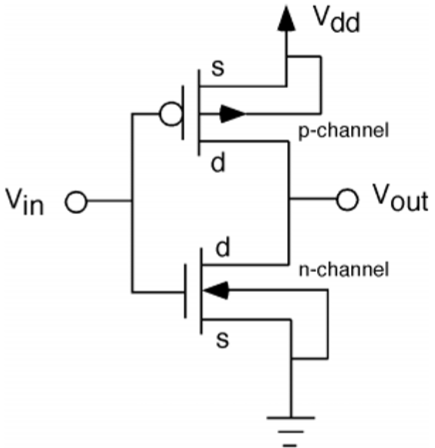

Falownik CMOS - obwód, działanie i opis

Obwód falownika CMOS pokazano na rysunku. Tutaj tranzystory nMOS i pMOS działają jako tranzystory sterownika; gdy jeden tranzystor jest włączony, drugi jest wyłączony.

Ta konfiguracja nazywa się complementary MOS (CMOS). Wejście jest podłączone do zacisku bramki obu tranzystorów tak, że oba mogą być bezpośrednio zasilane napięciem wejściowym. Podłoże nMOS jest podłączone do uziemienia, a podłoże pMOS jest podłączone do źródła zasilania V DD .

Więc V SB = 0 dla obu tranzystorów.

$$V_{GS,n}=V_{in}$$

$$V_{DS,n}=V_{out}$$

I,

$$V_{GS,p}=V_{in}-V_{DD}$$

$$V_{DS,p}=V_{out}-V_{DD}$$

Gdy wejście nMOS jest mniejsze niż napięcie progowe (V w <V TO, n ), nMOS jest odcięte i pMOS jest w obszarze liniowym. Zatem prąd drenu obu tranzystorów wynosi zero.

$$I_{D,n}=I_{D,p}=0$$

Dlatego napięcie wyjściowe V OH jest równe napięciu zasilania.

$$V_{out}=V_{OH}=V_{DD}$$

Gdy napięcie wejściowe jest większe niż V DD + V TO, p , tranzystor pMOS znajduje się w obszarze odcięcia, a nMOS jest w obszarze liniowym, więc prąd drenu obu tranzystorów wynosi zero.

$$I_{D,n}=I_{D,p}=0$$

Dlatego napięcie wyjściowe V OL jest równe zeru.

$$V_{out}=V_{OL}=0$$

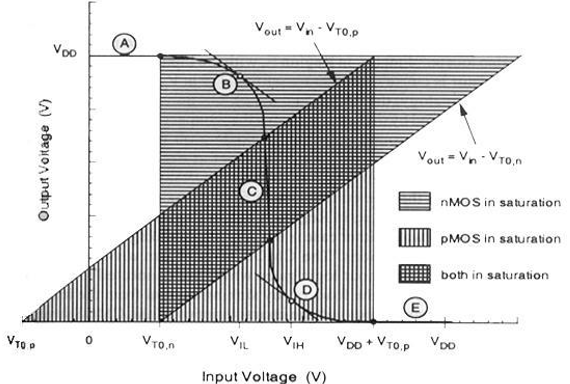

NMOS działa w obszarze nasycenia, jeśli V w > V TO i jeśli spełnione są następujące warunki.

$$V_{DS,n}\geq V_{GS,n}-V_{TO,n} $$

$$V_{out}\geq V_{in}-V_{TO,n} $$

PMOS działa w obszarze nasycenia, jeśli V w <V DD + V TO, p i jeśli spełnione są następujące warunki.

$$V_{DS,p}\leq V_{GS,p}-V_{TO,p} $$

$$V_{out}\leq V_{in}-V_{TO,p} $$

Dla różnych wartości napięć wejściowych, obszary pracy są wymienione poniżej dla obu tranzystorów.

| Region | V w | V się | nMOS | pMOS |

|---|---|---|---|---|

| ZA | <V TO, rz | V OH | Odciąć | Liniowy |

| b | V IL | Wysoka ≈ V OH | Nasycenie | Liniowy |

| do | V th | V th | Nasycenie | Nasycenie |

| re | V IH | Niski ≈ V OL | Liniowy | Nasycenie |

| mi | > (V DD + V TO, p ) | V OL | Liniowy | Odciąć |

VTC CMOS pokazano na poniższym rysunku -