Projekt VLSI - sekwencyjne obwody logiczne MOS

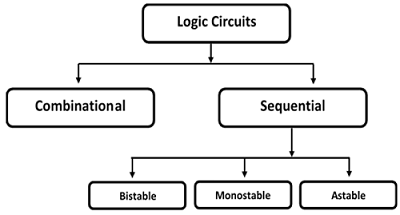

Obwody logiczne są podzielone na dwie kategorie - (a) Obwody kombinacyjne i (b) Obwody sekwencyjne.

W obwodach kombinacyjnych wyjście zależy tylko od stanu najnowszych wejść.

W układach sekwencyjnych wyjście zależy nie tylko od najnowszych wejść, ale także od stanu wcześniejszych wejść. Układy sekwencyjne zawierają elementy pamięci.

Obwody sekwencyjne są trzech typów -

Bistable- Obwody bistabilne mają dwa stabilne punkty pracy i będą w każdym ze stanów. Przykład - komórki pamięci, zatrzaski, przerzutniki i rejestry.

Monostable- Obwody monostabilne mają tylko jeden stabilny punkt pracy i nawet jeśli są chwilowo zakłócone do stanu przeciwnego, z czasem powrócą do swojego stabilnego punktu pracy. Przykład: timery, generatory impulsów.

Astable- obwody nie mają stabilnego punktu pracy i oscylują między kilkoma stanami. Przykład - oscylator pierścieniowy.

Obwody logiczne CMOS

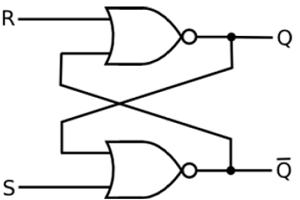

SR Latch oparty na bramie NOR

Jeśli ustawione wejście (S) jest równe logice "1" a wejście resetowania jest równe logice "0." wtedy wyjście Q będzie zmuszone do logiki "1". Podczas$\overline{Q}$ jest zmuszony do logiki "0". Oznacza to, że zatrzask SR zostanie ustawiony niezależnie od poprzedniego stanu.

Podobnie, jeśli S jest równe „0” i R jest równe "1" wtedy wyjście Q zostanie zmuszone do "0" podczas $\overline{Q}$ jest do tego zmuszony "1". Oznacza to, że zatrzask jest resetowany, niezależnie od wcześniejszego stanu wstrzymania. Wreszcie, jeśli oba wejścia S i R są równe logice"1" wtedy oba wyjścia będą zmuszone do logiki "0" co jest sprzeczne z komplementarnością Q i $\overline{Q}$.

Dlatego ta kombinacja wejść jest niedozwolona podczas normalnej pracy. Tabela prawdy SR Latch na bazie NOR jest podana w tabeli.

| S | R | Q | $\overline{Q}$ | Operacja |

|---|---|---|---|---|

| 0 | 0 | Q | $\overline{Q}$ | Trzymać |

| 1 | 0 | 1 | 0 | Zestaw |

| 0 | 1 | 0 | 1 | Resetowanie |

| 1 | 1 | 0 | 0 | Nie dozwolony |

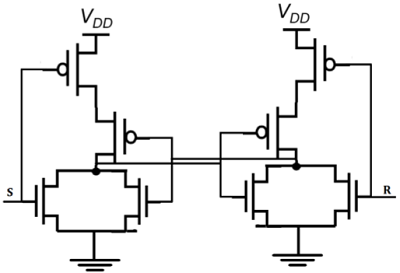

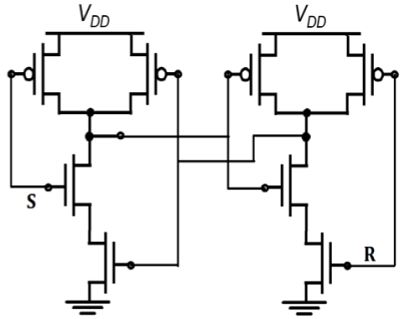

Na poniższym rysunku pokazano zatrzask CMOS SR oparty na bramce NOR.

Jeśli S jest równe V OH, a R jest równe V OL , oba równolegle połączone tranzystory M1 i M2 będą włączone. Napięcie na węźle$\overline{Q}$przyjmie niski poziom logiczny V OL = 0.

W tym samym czasie zarówno M3, jak i M4 są wyłączone, co skutkuje wysokim napięciem logicznym V OH w węźle Q. Jeśli R jest równe V OH, a S jest równe V OL , M1 i M2 są wyłączone i Włączone M3 i M4.

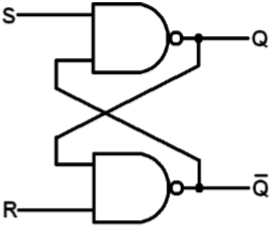

Zatrzask SR oparty na bramce NAND

Schemat blokowy i schemat poziomu bramki zatrzasku SR opartego na NAND pokazano na rysunku. Małe kółka na zaciskach wejściowych S i R oznaczają, że obwód reaguje na aktywne niskie sygnały wejściowe. Tabela prawdy zatrzasku SR opartego na NAND jest podana w tabeli

| S | R | Q | Q ′ | |

| 0 | 0 | NC | NC | Bez zmiany. Zatrzask pozostał w obecnym stanie. |

| 1 | 0 | 1 | 0 | Zestaw zatrzasków. |

| 0 | 1 | 0 | 1 | RESET zatrzasku. |

| 1 | 1 | 0 | 0 | Nieprawidłowy stan. |

Jeśli S idzie do 0 (podczas gdy R = 1), Q idzie wysoko, ciągnąc $\overline{Q}$ niski i zatrzask przechodzi w stan Set

S = 0 wtedy Q = 1 (jeśli R = 1)

Jeśli R osiągnie 0 (podczas gdy S = 1), Q idzie wysoko, ciągnąc $\overline{Q}$ niski i zatrzask jest resetowany

R = 0 wtedy Q = 1 (jeśli S = 1)

Stan wstrzymania wymaga, aby zarówno S, jak i R były wysokie. Jeśli S = R = 0, wyjście nie jest dozwolone, ponieważ spowodowałoby to stan nieokreślony. Zatrzask CMOS SR oparty na bramce NAND pokazano na rysunku.

Obciążenie wyczerpujące nMOS SR Zatrzask oparty na bramce NAND pokazano na rysunku. Działanie jest podobne do działania zatrzasku CMOS NAND SR. Implementacja obwodu CMOS ma niskie rozpraszanie mocy statycznej i wysoki margines szumów.

Obwody logiczne CMOS

Taktowany zatrzask SR

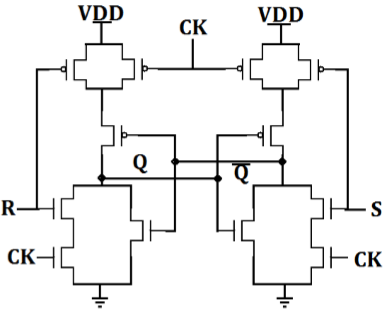

Rysunek przedstawia zatrzask SR oparty na NOR z dodanym zegarem. Zatrzask reaguje na wejścia S i R tylko wtedy, gdy CLK jest wysoki.

Gdy CLK jest niski, zatrzask zachowuje swój aktualny stan. Zauważ, że Q zmienia stan -

- Kiedy S rośnie podczas dodatniego CLK.

- Na wiodącym zboczu CLK po zmianach S i R podczas niskiego czasu CLK.

- Pozytywny błąd w S, podczas gdy CLK jest wysokie

- Kiedy R rośnie podczas dodatniego CLK.

Implementacja CMOS AOI taktowanego zatrzasku SR opartego na NOR jest pokazana na rysunku. Zauważ, że potrzeba tylko 12 tranzystorów.

Gdy CLK jest niski, dwa zaciski szeregowe w drzewie N są otwarte, a dwa równoległe tranzystory w drzewie P są włączone, zachowując w ten sposób stan w komórce pamięci.

Gdy zegar jest wysoki, obwód staje się po prostu zatrzaskiem CMOS opartym na NOR, który zareaguje na wejście S i R.

Clocked SR Latch based on NAND Gate

Obwód jest realizowany z czterema bramkami NAND. Jeśli ten obwód jest zaimplementowany z CMOS, to wymaga 16 tranzystorów.

- Zatrzask reaguje na S lub R tylko wtedy, gdy CLK jest wysoki.

- Jeśli oba sygnały wejściowe i sygnały CLK są aktywne w stanie wysokim: tj. Wyjście zatrzaskowe Q zostanie ustawione, gdy CLK = „1” S = „1” i R = „0”

- Podobnie, zatrzask zostanie zresetowany, gdy CLK = "1," S = "0" i

Gdy CLK jest niski, zatrzask zachowuje swój obecny stan.

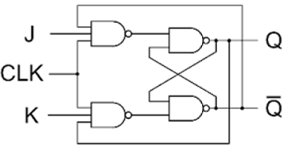

Taktowany zatrzask JK

Powyższy rysunek przedstawia taktowany zatrzask JK oparty na bramkach NAND. Wadą zatrzasku SR jest to, że gdy oba S i R są wysokie, jego stan wyjściowy staje się nieokreślony. Zatrzask JK eliminuje ten problem, wykorzystując sprzężenie zwrotne od wyjścia do wejścia, tak że wszystkie stany wejściowe tabeli prawdy są dopuszczalne. Jeśli J = K = 0, zatrzask utrzyma swój obecny stan.

Jeśli J = 1 i K = 0, zatrzask ustawi się na kolejnym dodatnim zboczu zegara, tj. Q = 1, $\overline{Q}$ = 0

Jeśli J = 0 i K = 1, zatrzask zresetuje się przy następnym dodatnim zboczu zegara, tj. Q = 1 i $\overline{Q}$ = 0.

Jeśli J = K = 1, zatrzask przełączy się na następnej dodatniej krawędzi zegara

Działanie taktowanego zatrzasku JK podsumowano w tabeli prawdy podanej w tabeli.

J |

K |

Q |

$\overline{Q}$ | S |

R |

Q |

$\overline{Q}$ | Operation |

| 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | Trzymać |

| 1 | 0 | 1 | 1 | 1 | 0 | |||

| 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | Resetowanie |

| 1 | 0 | 1 | 0 | 0 | 1 | |||

| 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | Zestaw |

| 1 | 0 | 1 | 1 | 1 | 0 | |||

| 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | przełącznik |

| 1 | 0 | 1 | 0 | 0 | 1 |

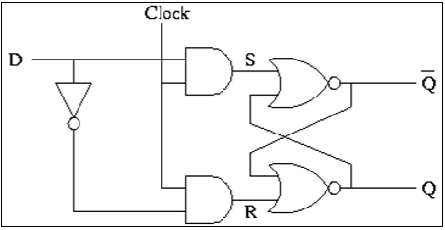

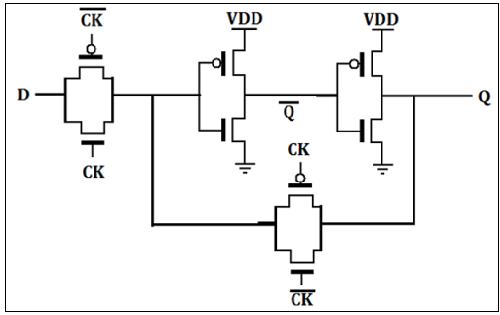

Implementacja zatrzasku CMOS D.

Zatrzask D jest zwykle realizowany z przełącznikami bramki transmisyjnej (TG), jak pokazano na rysunku. Wejście TG jest aktywowane za pomocą CLK, podczas gdy pętla sprzężenia zwrotnego zatrzasku TG jest aktywowana przez CLK. Wejście D jest akceptowane, gdy CLK jest wysoki. Kiedy CLK idzie w stan niski, wejście jest rozwarte, a zatrzask jest ustawiony z wcześniejszymi danymi D.