เครื่องใช้ไฟฟ้าพื้นฐาน - JFET

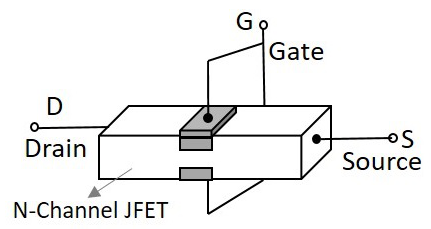

JFET ย่อมาจาก Junction Field Effect Transistor. JFET ก็เหมือนกับ FET ทั่วไป ประเภทของ JFET คือ n-channel FET และ P-channel FET วัสดุประเภท p จะถูกเพิ่มลงในวัสดุพิมพ์ชนิด n ใน N-channel FET ในขณะที่วัสดุประเภท n จะถูกเพิ่มลงในวัสดุพิมพ์ ptype ใน p-channel FET ดังนั้นจึงเพียงพอที่จะพูดคุยเกี่ยวกับ FET ประเภทหนึ่งเพื่อทำความเข้าใจทั้งสองอย่าง

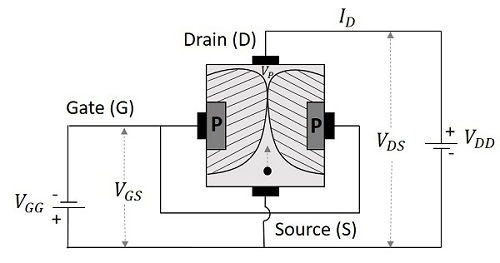

N-Channel FET

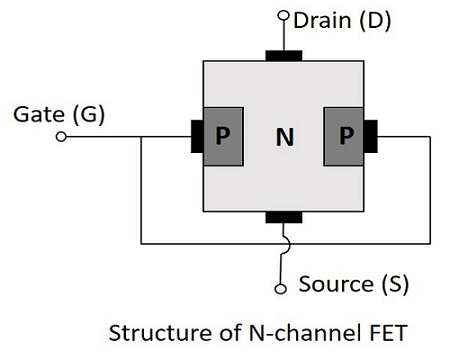

N-channel FET เป็นทรานซิสเตอร์ Field Effect ที่ใช้กันมากที่สุด สำหรับการผลิต Nchannel FET จะใช้แท่งเซมิคอนดักเตอร์ชนิด N แคบ ๆ ซึ่งวัสดุประเภท P เกิดจากการแพร่กระจายที่ด้านตรงข้าม ทั้งสองด้านนี้เชื่อมต่อกันเพื่อเชื่อมต่อเดียวสำหรับเทอร์มินัลประตู สิ่งนี้สามารถเข้าใจได้จากรูปต่อไปนี้

การสะสมประตูทั้งสองนี้ (วัสดุประเภท p) สร้างไดโอด PN สองตัว พื้นที่ระหว่างประตูเรียกว่าเป็นchannel. ผู้ให้บริการส่วนใหญ่ผ่านช่องนี้ ดังนั้นรูปแบบหน้าตัดของ FET จึงเข้าใจได้ดังรูปต่อไปนี้

หน้าสัมผัส Ohmic ทำขึ้นที่ปลายทั้งสองของแถบเซมิคอนดักเตอร์ชนิด n ซึ่งเป็นแหล่งกำเนิดและท่อระบายน้ำ แหล่งที่มาและขั้วท่อระบายน้ำอาจมีการเปลี่ยนแปลง

การทำงานของ N-channel FET

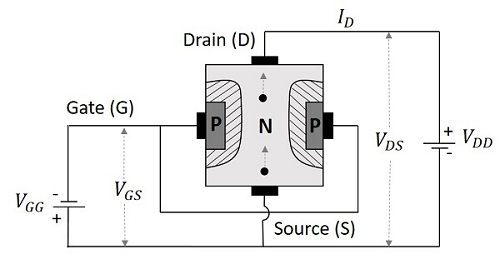

ก่อนที่จะเข้าสู่การทำงานของ FET เราควรทำความเข้าใจว่าเลเยอร์พร่องเกิดขึ้นได้อย่างไร สำหรับสิ่งนี้ให้เราสมมติว่าแรงดันไฟฟ้าที่ขั้วประตูบอกว่าVGG จะเอนเอียงย้อนกลับในขณะที่แรงดันไฟฟ้าที่ขั้วท่อระบายน้ำบอกว่า VDDไม่ได้ใช้ ให้เป็นกรณีนี้ 1.

ใน case 1, เมื่อไหร่ VGG กลับลำเอียงและ VDDไม่ได้นำไปใช้พื้นที่พร่องระหว่างชั้น P และ N มักจะขยายตัว สิ่งนี้เกิดขึ้นเมื่อใช้แรงดันไฟฟ้าลบดึงดูดรูจากเลเยอร์ประเภท p ไปที่ขั้วประตู

ใน case 2, เมื่อไหร่ VDD ถูกนำไปใช้ (ขั้วบวกเพื่อระบายและขั้วลบไปยังแหล่งที่มา) และ VGG ไม่ได้ใช้อิเล็กตรอนจะไหลจากแหล่งที่มาไปยังท่อระบายน้ำซึ่งเป็นกระแสระบาย ID.

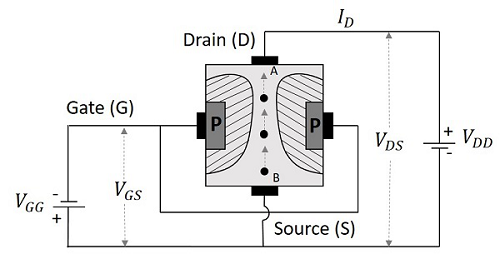

ตอนนี้ให้เราพิจารณารูปต่อไปนี้เพื่อทำความเข้าใจว่าจะเกิดอะไรขึ้นเมื่อได้รับเสบียงทั้งสอง

แหล่งจ่ายที่ขั้วประตูทำให้ชั้นพร่องเพิ่มขึ้นและแรงดันไฟฟ้าที่ขั้วท่อระบายน้ำช่วยให้กระแสระบายจากแหล่งจ่ายไปยังขั้วท่อระบายน้ำ สมมติว่าจุดที่เทอร์มินัลต้นทางคือ B และจุดที่เทอร์มินัลท่อระบายน้ำคือ A จากนั้นความต้านทานของช่องจะเท่ากับว่าแรงดันตกที่ขั้ว A มากกว่าแรงดันตกที่ขั้ว B ซึ่งหมายความว่า

VA>VB

ดังนั้นแรงดันไฟฟ้าจึงลดลงตามความยาวของช่องสัญญาณ ดังนั้นเอฟเฟกต์การให้น้ำหนักย้อนกลับจึงแข็งแกร่งกว่าที่ขั้วท่อระบายน้ำมากกว่าที่ขั้วต้นทาง นี่คือสาเหตุที่ชั้นพร่องมีแนวโน้มที่จะเจาะเข้าไปในช่องสัญญาณที่จุด A มากกว่าที่จุด B เมื่อทั้งสองอย่างVGG และ VDDถูกนำไปใช้ รูปต่อไปนี้อธิบายสิ่งนี้

ตอนนี้เราเข้าใจพฤติกรรมของ FET แล้วให้เราไปถึงการทำงานจริงของ FET

โหมดพร่องของการทำงาน

เนื่องจากความกว้างของเลเยอร์พร่องมีบทบาทสำคัญในการทำงานของ FET โหมดการลดชื่อของการดำเนินการจึงมีความหมาย เรามีโหมดอื่นที่เรียกว่าโหมดการเพิ่มประสิทธิภาพของการทำงานซึ่งจะกล่าวถึงในการทำงานของ MOSFET แต่JFETs have only depletion mode ของการดำเนินการ

ให้เราพิจารณาว่าไม่มีความเป็นไปได้ที่จะใช้ระหว่างขั้วประตูและขั้วต้นทางและศักยภาพ VDDถูกนำไปใช้ระหว่างท่อระบายน้ำและแหล่งที่มา ตอนนี้กระแสIDไหลจากท่อระบายน้ำไปยังขั้วต้นทางสูงสุดเนื่องจากความกว้างของช่องสัญญาณมากขึ้น ให้แรงดันไฟฟ้าที่ใช้ระหว่างประตูและขั้วต้นทางVGGกลับลำเอียง สิ่งนี้จะเพิ่มความกว้างการพร่องดังที่กล่าวไว้ข้างต้น เมื่อเลเยอร์เติบโตขึ้นหน้าตัดของช่องจะลดลงและด้วยเหตุนี้การระบายกระแสID ยังลดลง

เมื่อกระแสระบายนี้เพิ่มขึ้นอีกขั้นจะเกิดขึ้นซึ่งทั้งสองชั้นพร่องสัมผัสกันและป้องกันกระแสไฟฟ้า IDไหล. สิ่งนี้แสดงให้เห็นอย่างชัดเจนในรูปต่อไปนี้

แรงดันไฟฟ้าที่ชั้นพร่องทั้งสองนี้เรียกตามตัวอักษรว่า "สัมผัส" เรียกว่า "Pinch off voltage”. ถูกระบุว่าเป็น VP ณ จุดนี้กระแสระบายเป็นศูนย์อย่างแท้จริง ดังนั้นกระแสท่อระบายน้ำจึงเป็นฟังก์ชันของแรงดันไบอัสย้อนกลับที่ประตู

เนื่องจากแรงดันเกตควบคุมกระแสท่อระบายน้ำ FET จึงเรียกว่า voltage controlled device. สิ่งนี้เข้าใจได้ชัดเจนยิ่งขึ้นจากเส้นโค้งลักษณะท่อระบายน้ำ

ลักษณะการระบายน้ำของ JFET

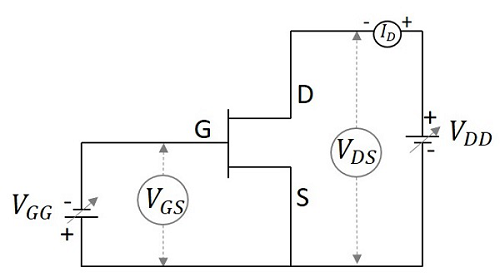

ให้เราพยายามสรุปฟังก์ชันของ FET ซึ่งเราสามารถหาเส้นโค้งลักษณะเฉพาะสำหรับการระบาย FET ได้ วงจรของ FET เพื่อให้ได้คุณสมบัติเหล่านี้แสดงไว้ด้านล่าง

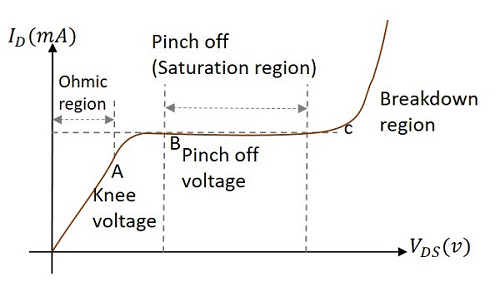

เมื่อแรงดันไฟฟ้าระหว่างประตูและแหล่งจ่าย VGS เป็นศูนย์หรือลัดวงจรปัจจุบัน ID จากแหล่งที่มาไปยังท่อระบายน้ำก็เป็นศูนย์เช่นกันเนื่องจากไม่มี VDSนำไปใช้ เป็นแรงดันไฟฟ้าระหว่างท่อระบายน้ำและแหล่งจ่ายVDS เพิ่มขึ้นกระแสปัจจุบัน IDจากแหล่งที่มาสู่การระบายน้ำเพิ่มขึ้น การเพิ่มขึ้นของกระแสไฟฟ้านี้เป็นเชิงเส้นจนถึงจุดหนึ่งAหรือที่เรียกว่า Knee Voltage.

ขั้วประตูจะอยู่ภายใต้สภาพเอนเอียงย้อนกลับและเป็น IDเพิ่มขึ้นบริเวณที่พร่องมีแนวโน้มที่จะหดตัว การหดตัวนี้มีความยาวไม่เท่ากันทำให้บริเวณเหล่านี้เข้ามาใกล้ท่อระบายน้ำมากขึ้นและไกลออกไปที่ท่อระบายน้ำซึ่งนำไปสู่pinch offแรงดันไฟฟ้า. แรงดันไฟฟ้าที่ดึงออกมาถูกกำหนดให้เป็นท่อระบายน้ำขั้นต่ำไปยังแรงดันไฟฟ้าต้นทางโดยที่กระแสระบายเข้าใกล้ค่าคงที่ (ค่าความอิ่มตัว) จุดที่แรงดันไฟฟ้าที่ดึงออกมานี้เรียกว่าเป็นPinch off pointแสดงเป็น B.

เช่น VDS เพิ่มขึ้นอีกความต้านทานของช่องก็เพิ่มขึ้นในลักษณะที่ IDในทางปฏิบัติยังคงที่ ศาสนาBC เป็นที่รู้จักกันในชื่อ saturation regionหรือภูมิภาคเครื่องขยายเสียง ทั้งหมดนี้พร้อมกับจุด A, B และ C ถูกพล็อตในกราฟด้านล่าง

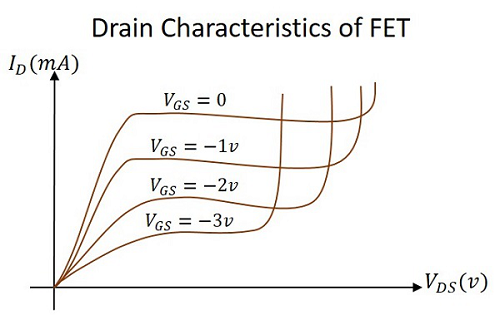

มีการกำหนดลักษณะท่อระบายน้ำสำหรับกระแสระบาย ID กับแรงดันไฟฟ้าของแหล่งระบายน้ำ VDSสำหรับค่าต่าง ๆ ของแรงดันไฟฟ้าแหล่งเกต VGS ลักษณะท่อระบายน้ำโดยรวมสำหรับแรงดันไฟฟ้าอินพุตต่างๆดังกล่าวเป็นไปตามที่ระบุไว้

เนื่องจากแรงดันเกตลบควบคุมกระแสระบาย FET จึงเรียกว่าเป็นอุปกรณ์ควบคุมแรงดันไฟฟ้า ลักษณะท่อระบายน้ำบ่งบอกถึงประสิทธิภาพของ FET คุณลักษณะของท่อระบายน้ำที่แสดงไว้ข้างต้นใช้เพื่อให้ได้ค่าความต้านทานท่อระบายน้ำค่าความเหนี่ยวนำและปัจจัยการขยาย