รีจิสเตอร์ดิจิทัล

Flip-Flop เป็นเซลล์หน่วยความจำ 1 บิตซึ่งสามารถใช้สำหรับจัดเก็บข้อมูลดิจิทัล ในการเพิ่มความจุในแง่ของจำนวนบิตเราต้องใช้ฟลิปฟล็อปกลุ่มหนึ่ง กลุ่มฟลิปฟล็อปดังกล่าวเรียกว่ากRegister. n-bit register จะประกอบด้วย n จำนวนฟลิปฟล็อปและสามารถจัดเก็บไฟล์ n-bit คำ.

ข้อมูลไบนารีในรีจิสเตอร์สามารถย้ายภายในรีจิสเตอร์จากฟลิปฟล็อปหนึ่งไปยังอีกฟล็อปได้ การลงทะเบียนที่อนุญาตให้ถ่ายโอนข้อมูลดังกล่าวเรียกว่าเป็นshift registers. มีสี่โหมดการทำงานของการลงทะเบียนกะ

- อินพุตอนุกรมเอาต์พุตอนุกรม

- อินพุตอนุกรมเอาต์พุตขนาน

- อินพุตอนุกรมเอาต์พุตแบบขนาน

- อินพุตแบบขนานเอาต์พุตแบบขนาน

อินพุตอนุกรมเอาต์พุตอนุกรม

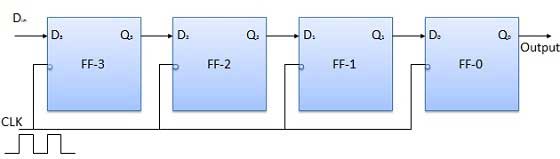

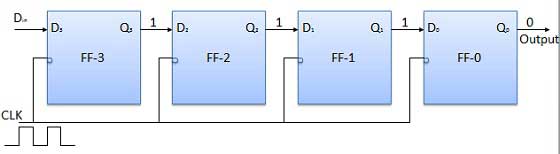

ให้ฟลิปฟล็อปทั้งหมดเริ่มต้นในเงื่อนไขการรีเซ็ตเช่น Q 3 = Q 2 = Q 1 = Q 0 = 0 หากมีการป้อนเลขฐานสองสี่บิต 1 1 1 1 ลงในรีจิสเตอร์หมายเลขนี้ควรเป็น นำไปใช้กับDinบิตที่มีการใช้บิต LSB ก่อน อินพุต D ของ FF-3 เช่น D 3เชื่อมต่อกับอินพุตข้อมูลอนุกรมDin. เอาต์พุตของ FF-3 เช่น Q 3เชื่อมต่อกับอินพุตของฟลิปฟล็อปถัดไปเช่น D 2เป็นต้น

แผนภาพบล็อก

การดำเนินการ

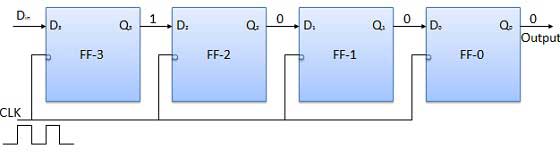

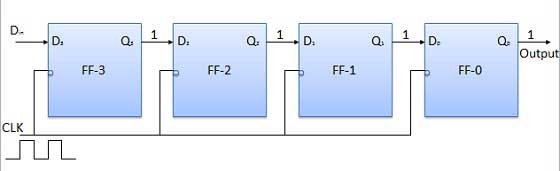

ก่อนที่จะประยุกต์ใช้สัญญาณนาฬิกาให้ Q 3 Q 2 Q 1 Q 0 = 0000 และใช้ LSB บิตของจำนวนที่จะป้อนให้กับ D ใน ดังนั้น D in = D 3 = 1 ใช้นาฬิกา ในช่วงขอบนาฬิกาแรก FF-3 ถูกตั้งค่าและคำที่เก็บไว้ในรีจิสเตอร์คือ Q 3 Q 2 Q 1 Q 0 = 1000

สมัครบิตต่อไปที่จะพัฒนาใน ดังนั้น D in = 1 ทันทีที่ขอบด้านลบถัดไปของนาฬิกากระทบ FF-2 จะตั้งค่าและคำที่เก็บไว้จะเปลี่ยนเป็น Q 3 Q 2 Q 1 Q 0 = 1100

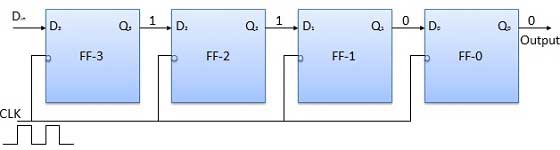

Apply บิตถัดไปจะถูกเก็บไว้คือ 1 ถึง D ใน ใช้ชีพจรนาฬิกา ทันทีที่ขอบนาฬิกาเชิงลบที่สามกระทบ FF-1 จะถูกตั้งค่าและเอาต์พุตจะถูกแก้ไขเป็น Q 3 Q 2 Q 1 Q 0 = 1110

ในทำนองเดียวกันกับ D in = 1 และเมื่อมาถึงขอบนาฬิกาเชิงลบที่สี่คำที่เก็บไว้ในรีจิสเตอร์คือ Q 3 Q 2 Q 1 Q 0 = 1111

ตารางความจริง

รูปคลื่น

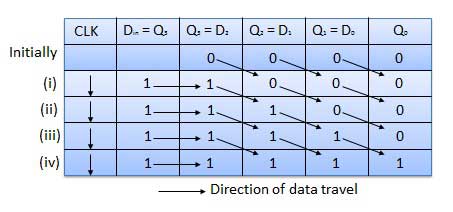

อินพุตอนุกรมเอาต์พุตขนาน

ในการดำเนินการประเภทดังกล่าวข้อมูลจะถูกป้อนตามลำดับและนำออกมาแบบคู่ขนาน

ข้อมูลถูกโหลดทีละบิต เอาต์พุตถูกปิดใช้งานตราบเท่าที่ข้อมูลกำลังโหลด

ทันทีที่การโหลดข้อมูลเสร็จสมบูรณ์ฟลิปฟล็อปทั้งหมดจะมีข้อมูลที่ต้องการเอาต์พุตจะเปิดใช้งานเพื่อให้ข้อมูลที่โหลดทั้งหมดพร้อมใช้งานบนบรรทัดเอาต์พุตทั้งหมดในเวลาเดียวกัน

ต้องใช้ 4 รอบนาฬิกาเพื่อโหลดคำสี่บิต ดังนั้นความเร็วในการทำงานของโหมด SIPO จึงเหมือนกับโหมด SISO

แผนภาพบล็อก

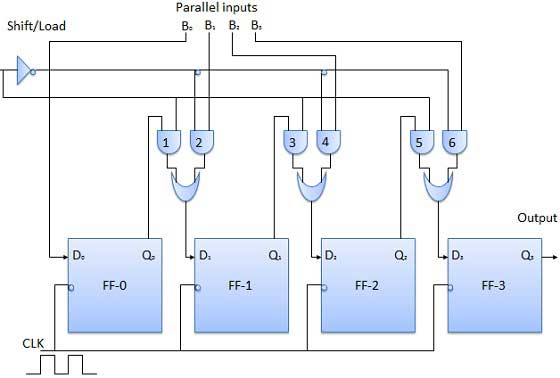

อินพุตอนุกรมเอาต์พุตแบบขนาน (PISO)

บิตข้อมูลถูกป้อนแบบขนาน

วงจรที่แสดงด้านล่างคือรีจิสเตอร์เอาต์พุตอนุกรมอินพุตแบบขนานสี่บิต

เอาต์พุตของ Flip Flop ก่อนหน้านี้เชื่อมต่อกับอินพุตของอันถัดไปผ่านวงจรรวม

คำป้อนไบนารี B 0 , B 1 , B 2 , B 3ถูกนำไปใช้แม้ว่าจะใช้วงจรผสมเดียวกัน

มีสองโหมดที่วงจรนี้สามารถทำงานได้คือ - โหมดกะหรือโหมดโหลด

โหลดโหมด

เมื่อเส้น shift / load bar อยู่ในระดับต่ำ (0) AND gate 2, 4 และ 6 จะทำงานพวกเขาจะส่ง B 1 , B 2 , B 3บิตไปยัง flip-flop ที่เกี่ยวข้อง ที่ขอบนาฬิกาต่ำอินพุตไบนารี B 0 , B 1 , B 2 , B 3จะโหลดลงในฟลิปฟล็อปที่เกี่ยวข้อง ดังนั้นการโหลดแบบขนานจึงเกิดขึ้น

โหมด Shift

เมื่อเส้นกะ / โหลดบาร์อยู่ในระดับต่ำ (1) ประตู AND 2, 4 และ 6 จะไม่ทำงาน ดังนั้นการโหลดข้อมูลแบบขนานจึงเป็นไปไม่ได้ แต่ประตู AND 1,3 และ 5 เริ่มทำงาน ดังนั้นการเปลี่ยนข้อมูลจากซ้ายไปขวาทีละนิดในการประยุกต์ใช้พัลส์นาฬิกา ดังนั้นการดำเนินการแบบขนานในอนุกรมออกจึงเกิดขึ้น

แผนภาพบล็อก

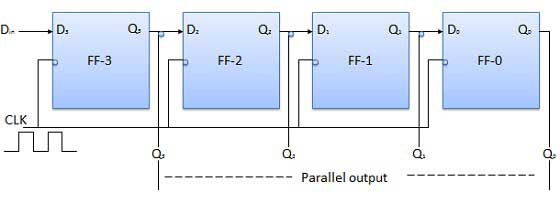

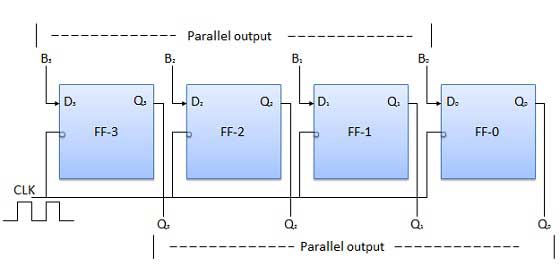

อินพุตแบบขนานเอาต์พุตแบบขนาน (PIPO)

ในโหมดนี้อินพุตไบนารี 4 บิต B 0 , B 1 , B 2 , B 3จะใช้กับอินพุตข้อมูล D 0 , D 1 , D 2 , D 3ตามลำดับของฟลิปฟล็อปทั้งสี่ ทันทีที่ใช้ขอบนาฬิกาเชิงลบบิตไบนารีอินพุตจะถูกโหลดลงในฟลิปฟล็อปพร้อมกัน บิตที่โหลดจะปรากฏพร้อมกันที่ด้านเอาต์พุต สัญญาณนาฬิกาเท่านั้นที่จำเป็นในการโหลดบิตทั้งหมด

แผนภาพบล็อก

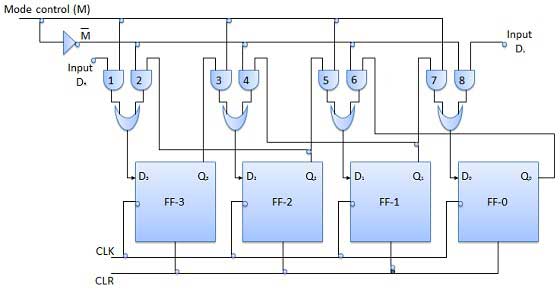

การลงทะเบียนกะแบบสองทิศทาง

หากเลขฐานสองถูกเลื่อนไปทางซ้ายทีละตำแหน่งก็จะเท่ากับการคูณเลขเดิมด้วย 2 ในทำนองเดียวกันถ้าเลขฐานสองถูกเลื่อนไปทางขวาทีละตำแหน่งจะเท่ากับการหารเลขเดิมด้วย 2

ดังนั้นหากเราต้องการใช้ shift register เพื่อคูณและหารเลขฐานสองที่กำหนดเราก็ควรจะสามารถย้ายข้อมูลไปในทิศทางซ้ายหรือขวา

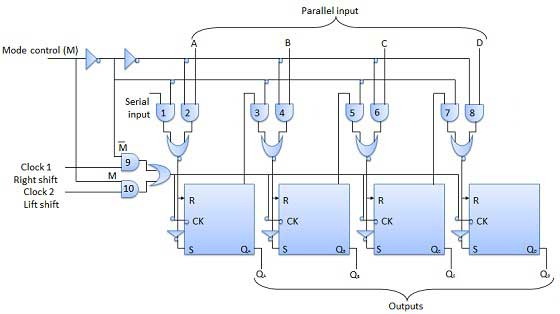

การลงทะเบียนดังกล่าวเรียกว่าการลงทะเบียนสองทิศทาง ทะเบียนกะสองทิศทางสี่บิตแสดงในรูป

มีอินพุตอนุกรมสองตัวคืออินพุตข้อมูลเลื่อนขวาแบบอนุกรม DR และอินพุตข้อมูลกะซ้ายแบบอนุกรม DL พร้อมกับอินพุตเลือกโหมด (M)

แผนภาพบล็อก

การดำเนินการ

| SN | เงื่อนไข | การดำเนินการ |

|---|---|---|

| 1 | With M = 1 − Shift right operation | ถ้า M = 1 แล้วประตู AND 1, 3, 5 และ 7 จะเปิดใช้งานในขณะที่ประตู AND ที่เหลือ 2, 4, 6 และ 8 จะถูกปิดใช้งาน ข้อมูลที่ D Rจะเลื่อนไปทางขวาทีละนิดจาก FF-3 เป็น FF-0 ในการประยุกต์ใช้พัลส์นาฬิกา ดังนั้นด้วย M = 1 เราจะได้รับการดำเนินการกะขวาแบบอนุกรม |

| 2 | With M = 0 − Shift left operation | เมื่อตัวควบคุมโหมด M เชื่อมต่อกับ 0 แล้วประตู AND 2, 4, 6 และ 8 จะเปิดใช้งานในขณะที่ 1, 3, 5 และ 7 ถูกปิดใช้งาน ข้อมูลที่ D Lจะเลื่อนไปทางซ้ายทีละนิดจาก FF-0 เป็น FF-3 ในการประยุกต์ใช้พัลส์นาฬิกา ดังนั้นด้วย M = 0 เราจะได้รับการดำเนินการกะขวาแบบอนุกรม |

ทะเบียนกะสากล

ทะเบียนกะที่สามารถเลื่อนข้อมูลไปในทิศทางเดียวเรียกว่าทะเบียนกะทิศทางเดียว ทะเบียนกะซึ่งสามารถเปลี่ยนข้อมูลได้ทั้งสองทิศทางเรียกว่าทะเบียนกะสองทิศทาง การใช้ตรรกะเดียวกันการลงทะเบียนกะซึ่งสามารถเปลี่ยนข้อมูลได้ทั้งสองทิศทางและโหลดแบบขนานเรียกว่าทะเบียนกะสากล shift register สามารถดำเนินการดังต่อไปนี้ -

- โหลดแบบขนาน

- เลื่อนซ้าย

- การขยับขวา

อินพุตควบคุมโหมดเชื่อมต่อกับลอจิก 1 สำหรับการทำงานโหลดแบบขนานในขณะที่เชื่อมต่อกับ 0 สำหรับการเปลี่ยนเกียร์แบบอนุกรม ด้วยพินควบคุมโหมดที่เชื่อมต่อกับกราวด์ทะเบียนกะสากลจะทำหน้าที่เป็นรีจิสเตอร์สองทิศทาง สำหรับการทำงานแบบอนุกรมซ้ายอินพุตจะถูกนำไปใช้กับอินพุตแบบอนุกรมซึ่งไปที่ AND gate-1 ที่แสดงในรูป ในขณะที่การดำเนินการ shift ขวาอินพุตแบบอนุกรมจะใช้กับอินพุต D

แผนภาพบล็อก