วงจรลำดับ

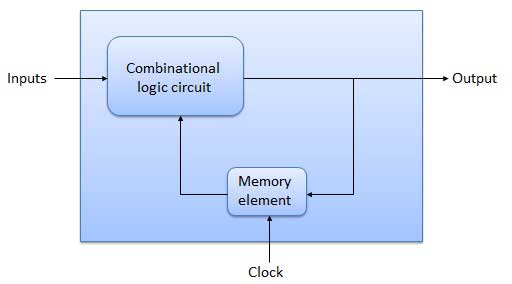

วงจรผสมไม่ใช้หน่วยความจำใด ๆ ดังนั้นสถานะก่อนหน้าของอินพุตจึงไม่มีผลใด ๆ ต่อสถานะปัจจุบันของวงจร แต่วงจรตามลำดับมีหน่วยความจำดังนั้นเอาต์พุตจึงแตกต่างกันไปตามอินพุต วงจรประเภทนี้ใช้อินพุตเอาต์พุตนาฬิกาและองค์ประกอบหน่วยความจำก่อนหน้า

แผนภาพบล็อก

รองเท้าแตะ

ฟลิปฟล็อปเป็นวงจรต่อเนื่องซึ่งโดยทั่วไปจะสุ่มตัวอย่างอินพุตและเปลี่ยนเอาต์พุตในช่วงเวลาหนึ่ง ๆ เท่านั้นและไม่ต่อเนื่อง ฟลิปฟล็อปกล่าวได้ว่ามีความไวต่อขอบหรือขอบที่ถูกทริกเกอร์แทนที่จะเป็นระดับที่เรียกเหมือนสลัก

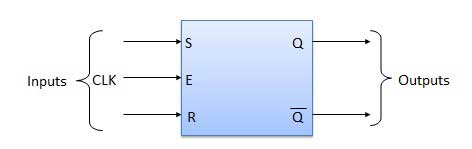

SR Flip Flop

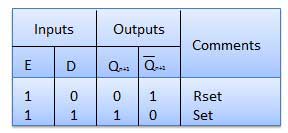

โดยทั่วไปแล้วสลัก SR โดยใช้ NAND gates เพิ่มเติม enableอินพุต. เรียกอีกอย่างว่าระดับที่เรียกใช้ SR-FF สำหรับสิ่งนี้วงจรอินพุทจะเกิดขึ้นก็ต่อเมื่อเปิดใช้งานอินพุต (E) เท่านั้น ในการลัดวงจรวงจรนี้จะทำงานเป็นสลัก SR ถ้า E = 1 แต่ไม่มีการเปลี่ยนแปลงในเอาต์พุตถ้า E = 0

แผนภาพบล็อก

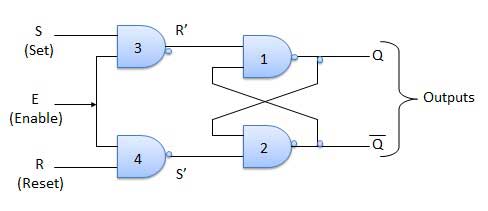

แผนภูมิวงจรรวม

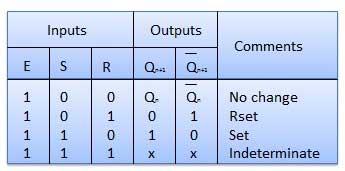

ตารางความจริง

การดำเนินการ

| SN | เงื่อนไข | การดำเนินการ |

|---|---|---|

| 1 | S = R = 0 : No change |

ถ้า S = R = 0 เอาต์พุตของ NAND ประตู 3 และ 4 จะถูกบังคับให้กลายเป็น 1 ดังนั้น R 'และ S' ทั้งสองจะเท่ากับ 1 เนื่องจาก S 'และ R' เป็นอินพุตของสลัก SR พื้นฐานโดยใช้ประตู NAND จะไม่มีการเปลี่ยนแปลงสถานะของเอาต์พุต |

| 2 | S = 0, R = 1, E = 1 |

เนื่องจาก S = 0 เอาต์พุตของ NAND-3 คือ R '= 1 และ E = 1 ผลลัพธ์ของ NAND-4 คือ S' = 0 ดังนั้น Q n + 1 = 0 และ Q n + 1 bar = 1 นี่คือเงื่อนไขการรีเซ็ต |

| 3 | S = 1, R = 0, E = 1 |

เอาต์พุตของ NAND-3 คือ R '= 0 และเอาต์พุตของ NAND-4 เช่น S' = 1 ดังนั้นเอาต์พุตของสลัก SR NAND คือ Q n + 1 = 1 และ Q n + 1 bar = 0 นี่คือเงื่อนไขการรีเซ็ต |

| 4 | S = 1, R = 1, E = 1 |

ในฐานะที่เป็น S = 1, R = 1 และ E = 1 เอาต์พุตของประตู NAND 3 และ 4 ทั้งสองเป็น 0 เช่น S '= R' = 0 ดังนั้น Race เงื่อนไขจะเกิดขึ้นในสลัก NAND พื้นฐาน |

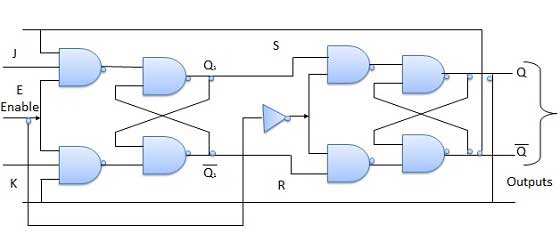

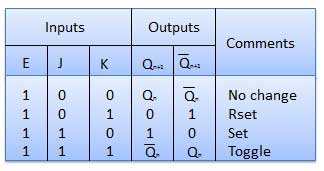

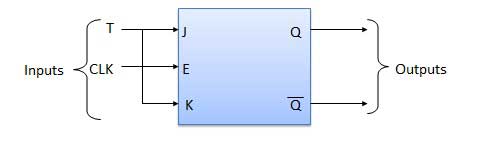

Master Slave JK Flip Flop

Master slave JK FF เป็นน้ำตกของ SR FF สองตัวพร้อมข้อเสนอแนะจากเอาต์พุตของวินาทีไปยังอินพุตของตัวแรก Master เป็นระดับบวกที่ถูกกระตุ้น แต่เนื่องจากการมีอินเวอร์เตอร์อยู่ในสายนาฬิกาทาสจะตอบสนองต่อระดับลบ ดังนั้นเมื่อนาฬิกา = 1 (ระดับบวก) ต้นแบบทำงานอยู่และทาสไม่ได้ใช้งาน ในขณะที่นาฬิกา = 0 (ระดับต่ำ) ทาสจะทำงานและมาสเตอร์ไม่ได้ใช้งาน

แผนภูมิวงจรรวม

ตารางความจริง

การดำเนินการ

| SN | เงื่อนไข | การดำเนินการ |

|---|---|---|

| 1 | J = K = 0 (No change) |

เมื่อนาฬิกา = 0 ทาสจะทำงานและมาสเตอร์ไม่ทำงาน แต่เนื่องจากอินพุต S และ R ไม่ได้เปลี่ยนแปลงเอาต์พุตของสเลฟก็จะไม่เปลี่ยนแปลงเช่นกัน ดังนั้นเอาต์พุตจะไม่เปลี่ยนแปลงถ้า J = K = 0 |

| 2 | J = 0 and K = 1 (Reset) |

นาฬิกา = 1 - ใช้งานหลักทาสไม่ใช้งาน ดังนั้นผลลัพธ์ของต้นแบบจึงกลายเป็น Q 1 = 0 และ Q 1 bar = 1 นั่นหมายความว่า S = 0 และ R = 1 นาฬิกา = 0 - ทาสใช้งานอยู่ไม่ได้ใช้งานหลัก ดังนั้นผลลัพธ์ของทาสจึงกลายเป็น Q = 0 และ Q bar = 1 นาฬิกาอีกครั้ง = 1 - ใช้งานหลักทาสไม่ใช้งาน ดังนั้นแม้จะมีเอาต์พุตที่เปลี่ยนแปลง Q = 0 และ Q bar = 1 ที่ป้อนกลับไปยังมาสเตอร์เอาต์พุตจะเป็น Q1 = 0 และ Q1 bar = 1 นั่นหมายความว่า S = 0 และ R = 1 ดังนั้นเมื่อนาฬิกา = 0 และทาสเริ่มทำงานผลลัพธ์ของทาสจะยังคงเป็น Q = 0 และแถบ Q = 1 ดังนั้นเราจึงได้ผลลัพธ์ที่เสถียรจาก Master slave |

| 3 | J = 1 and K = 0 (Set) |

นาฬิกา = 1 - ใช้งานหลักทาสไม่ใช้งาน ดังนั้นผลลัพธ์ของต้นแบบจึงกลายเป็น Q 1 = 1 และ Q 1 bar = 0 นั่นหมายความว่า S = 1 และ R = 0 นาฬิกา = 0 - ทาสใช้งานอยู่ไม่ได้ใช้งานหลัก ดังนั้นผลลัพธ์ของทาสจึงกลายเป็น Q = 1 และ Q bar = 0 นาฬิกาอีกครั้ง = 1 - จากนั้นจะแสดงให้เห็นว่าเอาต์พุตของทาสมีความเสถียรที่ Q = 1 และ Q bar = 0 |

| 4 | J = K = 1 (Toggle) |

นาฬิกา = 1 - ใช้งานหลักทาสไม่ใช้งาน ผลลัพธ์ของต้นแบบจะสลับ ดังนั้น S และ R ก็จะกลับด้านด้วย นาฬิกา = 0 - ทาสใช้งานอยู่ไม่ได้ใช้งานหลัก ผลลัพธ์ของทาสจะสลับ เอาต์พุตที่เปลี่ยนแปลงเหล่านี้จะถูกส่งกลับไปยังอินพุตหลัก แต่เนื่องจากนาฬิกา = 0 นาฬิกาหลักจึงยังไม่ทำงาน ดังนั้นจึงไม่ตอบสนองต่อผลลัพธ์ที่เปลี่ยนแปลงเหล่านี้ สิ่งนี้หลีกเลี่ยงการสลับหลายรายการซึ่งนำไปสู่การแข่งขันรอบเงื่อนไข รองเท้าแตะระดับมาสเตอร์ทาสจะหลีกเลี่ยงสภาพการแข่งขัน |

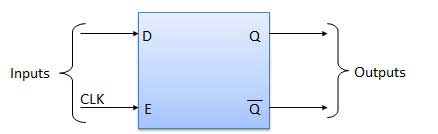

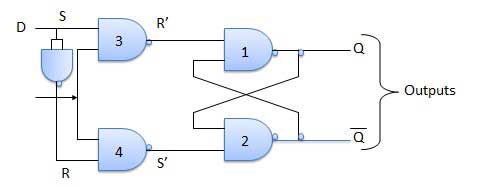

ดีเลย์ Flip Flop / D Flip Flop

Delay Flip Flop หรือ D Flip Flop เป็นสลัก SR ที่มีรั้วรอบขอบชิดแบบธรรมดาที่มีอินเวอร์เตอร์ NAND เชื่อมต่อระหว่างอินพุต S และ R มีเพียงอินพุตเดียว ข้อมูลอินพุตจะปรากฏที่เอาต์พุตหลังจากเวลาผ่านไปสักครู่ เนื่องจากความล่าช้าของข้อมูลระหว่าง i / p และ o / p จึงเรียกว่าดีเลย์ flip flop S และ R จะเป็นส่วนเติมเต็มซึ่งกันและกันเนื่องจากอินเวอร์เตอร์ NAND ดังนั้น S = R = 0 หรือ S = R = 1 เงื่อนไขการป้อนข้อมูลเหล่านี้จะไม่ปรากฏขึ้น ปัญหานี้หลีกเลี่ยงโดยเงื่อนไข SR = 00 และ SR = 1

แผนภาพบล็อก

แผนภูมิวงจรรวม

ตารางความจริง

การดำเนินการ

| SN | เงื่อนไข | การดำเนินการ |

|---|---|---|

| 1 | E = 0 |

สลักถูกปิดใช้งาน ดังนั้นจึงไม่มีการเปลี่ยนแปลงในผลลัพธ์ |

| 2 | E = 1 and D = 0 |

ถ้า E = 1 และ D = 0 แล้ว S = 0 และ R = 1 ดังนั้นโดยไม่คำนึงถึงสถานะปัจจุบันสถานะถัดไปคือ Q n + 1 = 0 และ Q n + 1 bar = 1 นี่คือเงื่อนไขการรีเซ็ต |

| 3 | E = 1 and D = 1 |

ถ้า E = 1 และ D = 1 ดังนั้น S = 1 และ R = 0 สิ่งนี้จะตั้งค่าสลักและ Q n + 1 = 1 และ Q n + 1 bar = 0 โดยไม่คำนึงถึงสถานะปัจจุบัน |

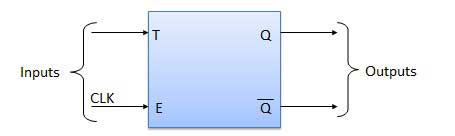

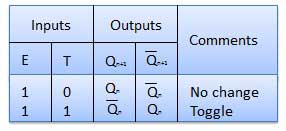

สลับ Flip Flop / T Flip Flop

Toggle flip flop โดยพื้นฐานแล้ว flip flop JK ที่มีขั้ว J และ K เชื่อมต่อกันอย่างถาวร มีเฉพาะอินพุตที่แสดงโดยTดังแสดงใน Symbol Diagram สัญลักษณ์สำหรับขอบบวกที่ทริกเกอร์ T flip flop จะแสดงในแผนภาพบล็อก

แผนภาพสัญลักษณ์

แผนภาพบล็อก

ตารางความจริง

การดำเนินการ

| SN | เงื่อนไข | การดำเนินการ |

|---|---|---|

| 1 | T = 0, J = K = 0 | แถบเอาต์พุต Q และ Q จะไม่เปลี่ยนแปลง |

| 2 | T = 1, J = K = 1 | เอาท์พุตจะสลับตามสัญญาณนาฬิกาทุกขอบชั้นนำ |