집적 회로의 기초

안 electronic circuit 특정 목적으로 연결된 전자 부품 그룹입니다.

개별 전자 부품 및 연결이 거의 필요하지 않기 때문에 간단한 전자 회로를 쉽게 설계 할 수 있습니다. 그러나 복잡한 전자 회로를 설계하는 것은 더 많은 수의 개별 전자 부품과 연결이 필요하기 때문에 어렵습니다. 또한 이러한 복잡한 회로를 구축하는 데 시간이 걸리며 신뢰성도 떨어집니다. 이러한 어려움은 집적 회로로 극복 할 수 있습니다.

집적 회로 (IC)

여러 전자 부품이 반도체 재료의 단일 칩에 상호 연결되어있는 경우 해당 칩을 Integrated Circuit (IC). 능동 및 수동 구성 요소로 구성됩니다.

이 장에서는 IC의 장점과 유형에 대해 설명합니다.

집적 회로의 장점

집적 회로는 많은 이점을 제공합니다. 아래에서 설명합니다.

Compact size − 특정 기능에 대해 개별 회로를 사용하여 구축 된 것과 비교하여 IC를 사용하여 더 작은 크기의 회로를 얻을 수 있습니다.

Lesser weight− IC로 구축 된 회로는 동일한 IC 기능을 구현하는 데 사용되는 개별 회로의 무게에 비해 무게가 더 가볍습니다. 개별 회로를 사용하여 구축 된 것과 비교하여 IC를 사용하는 것입니다.

Low power consumption − IC는 크기와 구조가 작기 때문에 기존 회로보다 낮은 전력을 소비합니다.

Reduced cost − IC는 제조 기술과 이산 회로보다 적은 재료를 사용하기 때문에 이산 회로보다 훨씬 저렴한 비용으로 사용할 수 있습니다.

Increased reliability − 더 적은 연결을 사용하기 때문에 IC는 디지털 회로에 비해 높은 신뢰성을 제공합니다.

Improved operating speeds − IC는 스위칭 속도가 빠르고 전력 소비가 적기 때문에 향상된 속도로 작동합니다.

집적 회로의 유형

집적 회로는 두 가지 유형이 있습니다. − Analog Integrated Circuits and Digital Integrated Circuits.

아날로그 집적 회로

신호 진폭의 연속 값의 전체 범위에서 작동하는 집적 회로를 Analog Integrated Circuits. 이것들은 여기에서 논의 된 것처럼 두 가지 유형으로 더 분류됩니다.

Linear Integrated Circuits− 아날로그 IC는 전압과 전류 사이에 선형 관계가있는 경우 선형이라고합니다. 8 핀 DIP (Dual In-line Package) 연산 증폭기 인 IC 741은 선형 IC의 예입니다.

Radio Frequency Integrated Circuits− 아날로그 IC는 전압과 전류 사이에 비선형 관계가있는 경우 비선형이라고합니다. 비선형 IC는 무선 주파수 IC라고도합니다.

디지털 집적 회로

집적 회로가 신호 진폭의 연속 값의 전체 범위에 대해 작동하지 않고 미리 정의 된 몇 가지 수준에서만 작동하는 경우이를 다음과 같이 호출합니다. Digital Integrated Circuits.

다음 장에서는 다양한 선형 집적 회로와 그 응용에 대해 논의 할 것입니다.

연산 증폭기라고도하는 연산 증폭기는 다양한 선형, 비선형 및 수학적 연산을 수행하는 데 사용할 수있는 집적 회로입니다. 연산 증폭기는direct coupled high gain amplifier. AC 및 DC 신호로 연산 증폭기를 작동 할 수 있습니다. 이 장에서는 연산 증폭기의 특성과 유형에 대해 설명합니다.

연산 증폭기의 구성

연산 증폭기는 차동 증폭기, 레벨 변환기 및 출력 단계로 구성됩니다. 차동 증폭기는 연산 증폭기의 입력 단계에 있으므로 연산 증폭기는two input terminals. 이러한 터미널 중 하나는inverting terminal 다른 하나는 non-inverting terminal. 터미널은 각각의 입력과 출력 간의 위상 관계에 따라 이름이 지정됩니다.

연산 증폭기의 특성

연산 증폭기의 중요한 특성 또는 매개 변수는 다음과 같습니다.

- 개방 루프 전압 이득

- 출력 오프셋 전압

- 공통 모드 제거 비율

- 슬 루율

이 섹션에서는 이러한 특성을 아래에 자세히 설명합니다.

개방 루프 전압 이득

연산 증폭기의 개방 루프 전압 이득은 피드백 경로가없는 차동 이득입니다.

수학적으로 연산 증폭기의 개방 루프 전압 이득은 다음과 같이 표현됩니다.

$$A_{v}= \frac{v_0}{v_1-v_2}$$

출력 오프셋 전압

차동 입력 전압이 0 일 때 연산 증폭기의 출력에 존재하는 전압을 다음과 같이 호출합니다. output offset voltage.

공통 모드 제거 비율

공통 모드 제거 비율 (CMRR)의 연산 증폭기는 폐쇄 루프 차동 이득의 비율로 정의되며, $A_{d}$ 공통 모드 이득, $A_{c}$.

수학적으로 CMRR은 다음과 같이 나타낼 수 있습니다.

$$CMRR=\frac{A_{d}}{A_{c}}$$

공통 모드 이득, $A_{c}$ 연산 증폭기의 공통 모드 출력 전압과 공통 모드 입력 전압의 비율입니다.

슬 루율

연산 증폭기의 슬 루율은 스텝 입력 전압으로 인한 출력 전압의 최대 변화율로 정의됩니다.

수학적으로 슬 루율 (SR)은 다음과 같이 나타낼 수 있습니다.

$$SR=Maximum\:of\:\frac{\text{d}V_{0}}{\text{d}t}$$

어디, $V_{0}$출력 전압입니다. 일반적으로 슬 루율은$V/\mu\:Sec$ 또는 $V/m\:Sec$.

연산 증폭기의 유형

연산 증폭기는 입력 2 개와 출력 1 개가있는 삼각형 기호로 표시됩니다.

연산 증폭기에는 두 가지 유형이 있습니다. Ideal Op-Amp 과 Practical Op-Amp.

아래에 주어진대로 자세히 설명합니다.

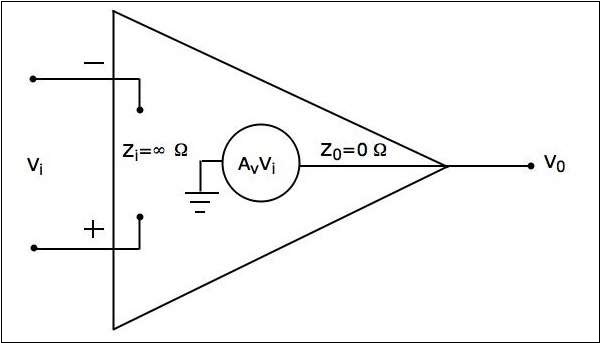

이상적인 연산 증폭기

이상적인 연산 증폭기는 이론적으로 만 존재하며 실제로 존재하지 않습니다. 그만큼equivalent circuit 이상적인 연산 증폭기는 아래 그림에 나와 있습니다.

안 ideal op-amp 다음과 같은 특성을 나타냅니다-

입력 임피던스 $Z_{i}=\infty\Omega$

출력 임피던스 $Z_{0}=0\Omega$

개방 루프 전압 이득 $A_{v}=\infty$

(차동) 입력 전압 $V_{i}=0V$, 출력 전압은 $V_{0}=0V$

대역폭은 infinity. 즉, 이상적인 연산 증폭기는 감쇠없이 모든 주파수의 신호를 증폭합니다.

공통 모드 제거 비율 (CMRR) 이다 infinity.

슬 루율 (SR) 이다 infinity. 즉, 이상적인 연산 증폭기는 입력 단계 전압에 응답하여 즉시 출력 변화를 생성합니다.

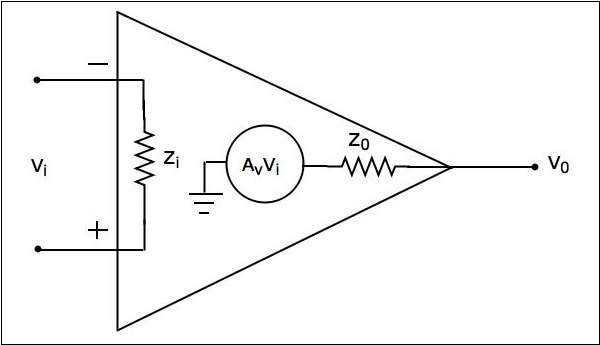

실용적인 연산 증폭기

실제로 연산 증폭기는 이상적이지 않으며 제조 중 일부 결함으로 인해 이상적인 특성에서 벗어납니다. 그만큼equivalent circuit 실용적인 연산 증폭기의 다음 그림은-

ㅏ practical op-amp 다음과 같은 특성을 나타냅니다-

입력 임피던스, $Z_{i}$ 순서대로 Mega ohms.

출력 임피던스, $Z_{0}$ 순서대로 few ohms..

개방 루프 전압 이득, $A_{v}$ 될거야 high.

실용적인 연산 증폭기를 선택할 때 다음 조건을 충족하는지 확인해야합니다.

입력 임피던스, $Z_{i}$ 가능한 한 높아야합니다.

출력 임피던스, $Z_{0}$ 가능한 한 낮아야합니다.

개방 루프 전압 이득, $A_{v}$ 가능한 한 높아야합니다.

출력 오프셋 전압은 가능한 낮아야합니다.

작동 대역폭은 가능한 한 높아야합니다.

CMRR은 가능한 한 높아야합니다.

슬 루율은 가능한 한 높아야합니다.

Note − IC 741 연산 증폭기는 가장 인기 있고 실용적인 연산 증폭기입니다.

회로는 linear, 입력과 출력 사이에 선형 관계가있는 경우. 마찬가지로 회로는non-linear, 입력과 출력 사이에 비선형 관계가있는 경우.

연산 증폭기는 선형 및 비선형 애플리케이션 모두에서 사용할 수 있습니다. 다음은 연산 증폭기의 기본 응용 프로그램입니다-

- 반전 증폭기

- 비 반전 증폭기

- 전압 추종자

이 장에서는 이러한 기본 응용 프로그램에 대해 자세히 설명합니다.

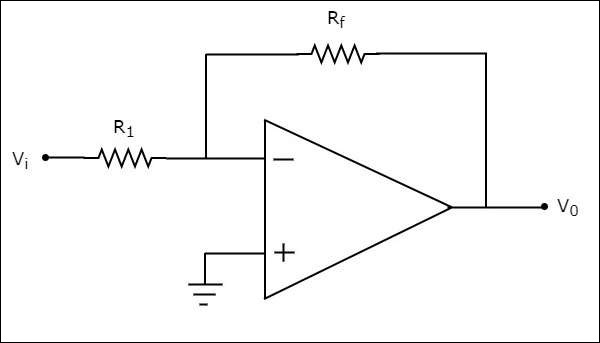

반전 증폭기

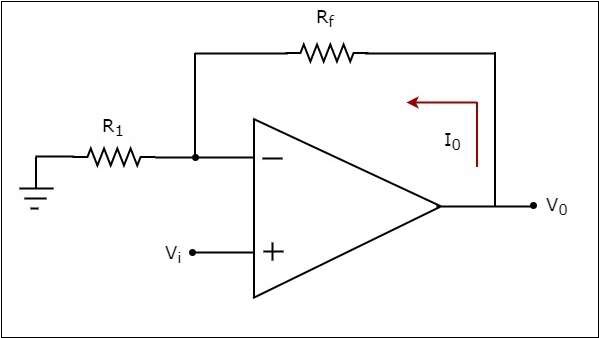

반전 증폭기는 저항을 통해 반전 단자를 통해 입력을받습니다. $R_{1}$, 출력으로 증폭 된 버전을 생성합니다. 이 증폭기는 입력을 증폭 할뿐만 아니라 반전 (부호 변경)도합니다.

그만큼 circuit diagram 반전 증폭기의 다음 그림은-

연산 증폭기의 경우 반전 입력 단자의 전압은 비 반전 입력 단자의 전압과 동일합니다. 물리적으로이 두 터미널 사이에는 단락이 없지만virtually, 그들은 short 서로 서로 함께.

위에 표시된 회로에서 비 반전 입력 단자는 접지에 연결됩니다. 즉, 연산 증폭기의 비 반전 입력 단자에 제로 볼트가 적용됩니다.

에 따르면 virtual short concept, 연산 증폭기의 반전 입력 단자의 전압은 0V가됩니다.

그만큼 nodal equation 이 터미널의 노드는 아래와 같습니다.

$$\frac{0-V_i}{R_1}+ \frac{0-V_0}{R_f}=0$$

$$=>\frac{-V_i}{R_1}= \frac{V_0}{R_f}$$

$$=>V_{0}=\left(\frac{-R_f}{R_1}\right)V_{t}$$

$$=>\frac{V_0}{V_i}= \frac{-R_f}{R_1}$$

출력 전압의 비율 $V_{0}$ 및 입력 전압 $V_{i}$증폭기의 전압 이득 또는 이득입니다. 따라서gain of inverting amplifier 와 동등하다 $-\frac{R_f}{R_1}$.

반전 증폭기의 이득은 negative sign. 입력과 출력간에 180 0 위상차 가 있음을 나타냅니다 .

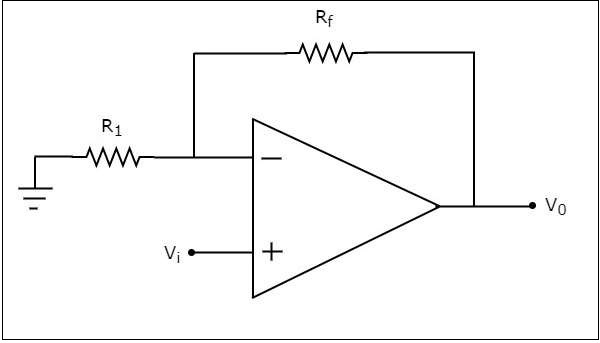

비 반전 증폭기

비 반전 증폭기는 비 반전 단자를 통해 입력을 받아 증폭 된 버전을 출력으로 생성합니다. 이름에서 알 수 있듯이이 앰프는 출력 부호를 반전하거나 변경하지 않고 입력을 증폭합니다.

그만큼 circuit diagram 비 반전 증폭기의 다음 그림은-

위의 회로에서 입력 전압 $V_{i}$연산 증폭기의 비 반전 입력 단자에 직접 적용됩니다. 따라서 연산 증폭기의 비 반전 입력 단자의 전압은$V_{i}$.

사용하여 voltage division principle, 우리는 아래와 같이 연산 증폭기의 반전 입력 단자에서 전압을 계산할 수 있습니다.

$$=>V_{1} = V_{0}\left(\frac{R_1}{R_1+R_f}\right)$$

에 따르면 virtual short concept, 연산 증폭기의 반전 입력 단자의 전압은 비 반전 입력 단자의 전압과 동일합니다.

$$=>V_{1} = V_{i}$$

$$=>V_{0}\left(\frac{R_1}{R_1+R_f}\right)=V_{i}$$

$$=>\frac{V_0}{V_i}=\frac{R_1+R_f}{R_1}$$

$$=>\frac{V_0}{V_i}=1+\frac{R_f}{R_1}$$

이제 출력 전압의 비율 $V_{0}$ 및 입력 전압 $V_{i}$ 또는 전압 이득 또는 gain of the non-inverting amplifier 와 동등하다 $1+\frac{R_f}{R_1}$.

비 반전 증폭기의 이득은 positive sign. 입력과 출력 사이에 위상차가 없음을 나타냅니다.

전압 추종자

ㅏ voltage follower입력 전압을 따르는 출력을 생성하는 전자 회로입니다. 비 반전 증폭기의 특수한 경우입니다.

피드백 저항의 값을 고려하면 $R_{f}$0 옴 및 (또는) 저항 값, 무한 옴으로 1이면 비 반전 증폭기가 전압 팔로워가됩니다. 그만큼circuit diagram 전압 팔로워의 다음 그림은-

위의 회로에서 입력 전압 $V_{i}$연산 증폭기의 비 반전 입력 단자에 직접 적용됩니다. 따라서 연산 증폭기의 비 반전 입력 단자의 전압은 다음과 같습니다.$V_{i}$. 여기서 출력은 opamp의 반전 입력 단자에 직접 연결됩니다. 따라서 연산 증폭기의 반전 입력 단자의 전압은 다음과 같습니다.$V_{0}$.

에 따르면 virtual short concept, 연산 증폭기의 반전 입력 단자의 전압은 비 반전 입력 단자의 전압과 동일합니다.

$$=>V_{0} = V_{i}$$

따라서 출력 전압 $V_{0}$ 전압 팔로워의 입력 전압과 같습니다. $V_{i}$.

그래서 gain of a voltage follower 둘 다 출력 전압이므로 1과 같습니다. $V_{0}$ 및 입력 전압 $V_{i}$ 전압 추종자의 수는 동일합니다.

이전 장에서 연산 증폭기의 기본 응용 프로그램에 대해 논의했습니다. 연산 증폭기의 선형 작동하에 있습니다. 이 장에서는 연산 증폭기의 선형 응용 프로그램이기도 한 산술 회로에 대해 논의하겠습니다.

산술 연산을 수행하는 전자 회로는 arithmetic circuits. 연산 증폭기를 사용하면 다음과 같은 기본 산술 회로를 구축 할 수 있습니다.adder 그리고 subtractor. 이 장에서는 각각에 대해 자세히 알아 봅니다.

가산기

가산기는 적용된 입력의 합과 동일한 출력을 생성하는 전자 회로입니다. 이 섹션에서는 연산 증폭기 기반 가산기 회로에 대해 설명합니다.

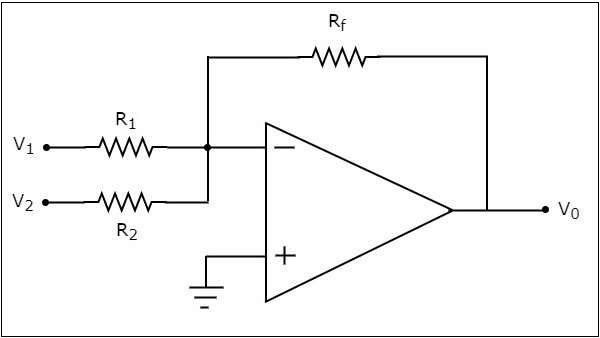

연산 증폭기 기반 가산기는 반전 단자에 적용된 입력 전압의 합과 동일한 출력을 생성합니다. 그것은 또한summing amplifier, 출력이 증폭 된 것이므로.

그만큼 circuit diagram 연산 증폭기 기반 가산기는 다음 그림에 나와 있습니다.

위의 회로에서 연산 증폭기의 비 반전 입력 단자는 접지에 연결됩니다. 즉, 비 반전 입력 단자에 제로 볼트가 적용됩니다.

에 따르면 virtual short concept, 연산 증폭기의 반전 입력 단자의 전압은 비 반전 입력 단자의 전압과 동일합니다. 따라서 연산 증폭기의 반전 입력 단자의 전압은 0V가됩니다.

그만큼 nodal equation 반전 입력 터미널의 노드에서

$$\frac{0-V_1}{R_1}+\frac{0-V_2}{R_2}+\frac{0-V_0}{R_f}=0$$

$$=>\frac{V_1}{R_1}-\frac{V_2}{R_2}=\frac{V_0}{R_f}$$

$$=>V_{0}=R_{f}\left(\frac{V_1}{R_1}+\frac{V_2}{R_2}\right)$$

만약 $R_{f}=R_{1}=R_{2}=R$, 출력 전압 $V_{0}$ 될 것입니다-

$$V_{0}=-R{}\left(\frac{V_1}{R}+\frac{V_2}{R}\right)$$

$$=>V_{0}=-(V_{1}+V_{2})$$

따라서 위에서 설명한 연산 증폭기 기반 가산기 회로는 두 입력 전압의 합을 생성합니다. $v_{1}$ 과 $v_{1}$, 회로에있는 모든 저항이 동일한 값일 때 출력으로. 출력 전압$V_{0}$ 가산기 회로의 negative sign, 이는 입력과 출력간에 180 0 위상차 가 있음을 나타냅니다 .

Subtractor

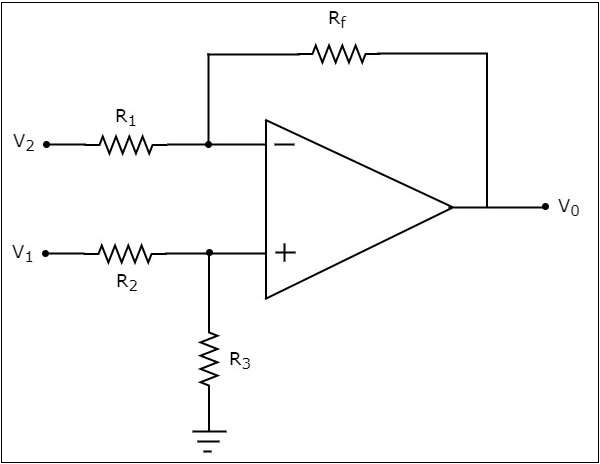

A subtractor is an electronic circuit that produces an output, which is equal to the difference of the applied inputs. This section discusses about the op-amp based subtractor circuit.

An op-amp based subtractor produces an output equal to the difference of the input voltages applied at its inverting and non-inverting terminals. It is also called as a difference amplifier, since the output is an amplified one.

The circuit diagram of an op-amp based subtractor is shown in the following figure −

Now, let us find the expression for output voltage $V_{0}$ of the above circuit using superposition theorem using the following steps −

Step 1

Firstly, let us calculate the output voltage $V_{01}$ by considering only $V_{1}$.

For this, eliminate $V_{2}$ by making it short circuit. Then we obtain the modified circuit diagram as shown in the following figure −

Now, using the voltage division principle, calculate the voltage at the non-inverting input terminal of the op-amp.

$$=>V_{p}=V_{1}\left(\frac{R_3}{R_2+R_3}\right)$$

Now, the above circuit looks like a non-inverting amplifier having input voltage $V_{p}$. Therefore, the output voltage $V_{01}$ of above circuit will be

$$V_{01}=V_{p}\left(1+\frac{R_f}{R_1}\right)$$

Substitute, the value of $V_{p}$ in above equation, we obtain the output voltage $V_{01}$ by considering only $V_{1}$, as −

$$V_{01}=V_{1}\left(\frac{R_3}{R_2+R_3}\right)\left(1+\frac{R_f}{R_1}\right)$$

Step 2

In this step, let us find the output voltage, $V_{02}$ by considering only $V_{2}$. Similar to that in the above step, eliminate $V_{1}$ by making it short circuit. The modified circuit diagram is shown in the following figure.

You can observe that the voltage at the non-inverting input terminal of the op-amp will be zero volts. It means, the above circuit is simply an inverting op-amp. Therefore, the output voltage $V_{02}$ of above circuit will be −

$$V_{02}=\left(-\frac{R_f}{R_1}\right)V_{2}$$

Step 3

In this step, we will obtain the output voltage $V_{0}$ of the subtractor circuit by adding the output voltages obtained in Step1 and Step2. Mathematically, it can be written as

$$V_{0}=V_{01}+V_{02}$$

Substituting the values of $V_{01}$ and $V_{02}$ in the above equation, we get −

$$V_{0}=V_{1}\left(\frac{R_3}{R_2+R_3}\right)\left(1+\frac{R_f}{R_1}\right)+\left(-\frac{R_f}{R_1}\right)V_{2}$$

$$=>V_{0}=V_{1}\left(\frac{R_3}{R_2+R_3}\right)\left(1+\frac{R_f}{R_1}\right)-\left(\frac{R_f}{R_1}\right)V_{2}$$

If $R_{f}=R_{1}=R_{2}=R_{3}=R$, then the output voltage $V_{0}$ will be

$$V_{0}=V_{1}\left(\frac{R}{R+R}\right)\left(1+\frac{R}{R}\right)-\left(\frac{R}{R}\right)V_{2}$$

$$=>V_{0}=V_{1}\left(\frac{R}{2R}\right)(2)-(1)V_{2}$$

$$V_{0}=V_{1}-V_{2}$$

Thus, the op-amp based subtractor circuit discussed above will produce an output, which is the difference of two input voltages $V_{1}$ and $V_{2}$, when all the resistors present in the circuit are of same value.

The electronic circuits which perform the mathematical operations such as differentiation and integration are called as differentiator and integrator, respectively.

This chapter discusses in detail about op-amp based differentiator and integrator. Please note that these also come under linear applications of op-amp.

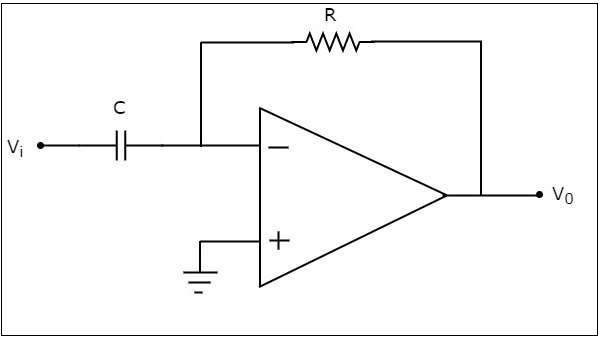

Differentiator

A differentiator is an electronic circuit that produces an output equal to the first derivative of its input. This section discusses about the op-amp based differentiator in detail.

An op-amp based differentiator produces an output, which is equal to the differential of input voltage that is applied to its inverting terminal. The circuit diagram of an op-amp based differentiator is shown in the following figure −

In the above circuit, the non-inverting input terminal of the op-amp is connected to ground. That means zero volts is applied to its non-inverting input terminal.

According to the virtual short concept, the voltage at the inverting input terminal of opamp will be equal to the voltage present at its non-inverting input terminal. So, the voltage at the inverting input terminal of op-amp will be zero volts.

The nodal equation at the inverting input terminal's node is −

$$C\frac{\text{d}(0-V_{i})}{\text{d}t}+\frac{0-V_0}{R}=0$$

$$=>-C\frac{\text{d}V_{i}}{\text{d}t}=\frac{V_0}{R}$$

$$=>V_{0}=-RC\frac{\text{d}V_{i}}{\text{d}t}$$

If $RC=1\sec$, then the output voltage $V_{0}$ will be −

$$V_{0}=-\frac{\text{d}V_{i}}{\text{d}t}$$

Thus, the op-amp based differentiator circuit shown above will produce an output, which is the differential of input voltage $V_{i}$, when the magnitudes of impedances of resistor and capacitor are reciprocal to each other.

Note that the output voltage $V_{0}$ is having a negative sign, which indicates that there exists a 1800 phase difference between the input and the output.

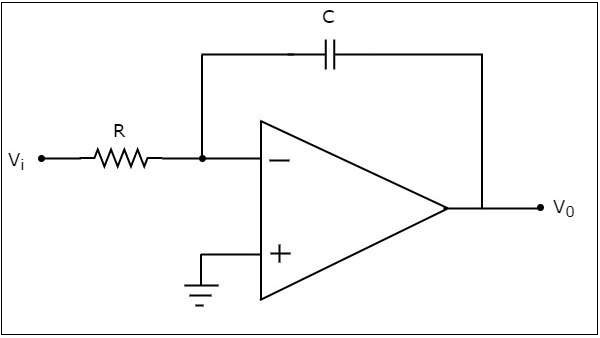

Integrator

An integrator is an electronic circuit that produces an output that is the integration of the applied input. This section discusses about the op-amp based integrator.

An op-amp based integrator produces an output, which is an integral of the input voltage applied to its inverting terminal. The circuit diagram of an op-amp based integrator is shown in the following figure −

In the circuit shown above, the non-inverting input terminal of the op-amp is connected to ground. That means zero volts is applied to its non-inverting input terminal.

According to virtual short concept, the voltage at the inverting input terminal of op-amp will be equal to the voltage present at its non-inverting input terminal. So, the voltage at the inverting input terminal of op-amp will be zero volts.

The nodal equation at the inverting input terminal is −

$$\frac{0-V_i}{R}+C\frac{\text{d}(0-V_{0})}{\text{d}t}=0$$

$$=>\frac{-V_i}{R}=C\frac{\text{d}V_{0}}{\text{d}t}$$

$$=>\frac{\text{d}V_{0}}{\text{d}t}=-\frac{V_i}{RC}$$

$$=>{d}V_{0}=\left(-\frac{V_i}{RC}\right){\text{d}t}$$

Integrating both sides of the equation shown above, we get −

$$\int{d}V_{0}=\int\left(-\frac{V_i}{RC}\right){\text{d}t}$$

$$=>V_{0}=-\frac{1}{RC}\int V_{t}{\text{d}t}$$

If $RC=1\sec$, then the output voltage, $V_{0}$ will be −

$$V_{0}=-\int V_{i}{\text{d}t}$$

So, the op-amp based integrator circuit discussed above will produce an output, which is the integral of input voltage $V_{i}$, when the magnitude of impedances of resistor and capacitor are reciprocal to each other.

Note − The output voltage, $V_{0}$ is having a negative sign, which indicates that there exists 1800 phase difference between the input and the output.

Voltage and current are the basic electrical quantities. They can be converted into one another depending on the requirement. Voltage to Current Converter and Current to Voltage Converter are the two circuits that help in such conversion. These are also linear applications of op-amps. This chapter discusses them in detail.

Voltage to Current Converter

A voltage to current converter or V to I converter, is an electronic circuit that takes current as the input and produces voltage as the output. This section discusses about the op-amp based voltage to current converter.

An op-amp based voltage to current converter produces an output current when a voltage is applied to its non-inverting terminal. The circuit diagram of an op-amp based voltage to current converter is shown in the following figure.

In the circuit shown above, an input voltage $V_{i}$ is applied at the non-inverting input terminal of the op-amp. According to the virtual short concept, the voltage at the inverting input terminal of an op-amp will be equal to the voltage at its non-inverting input terminal . So, the voltage at the inverting input terminal of the op-amp will be $V_{i}$.

The nodal equation at the inverting input terminal's node is −

$$\frac{V_i}{R_1}-I_{0}=0$$

$$=>I_{0}=\frac{V_t}{R_1}$$

Thus, the output current $I_{0}$ of a voltage to current converter is the ratio of its input voltage $V_{i}$ and resistance $R_{1}$.

We can re-write the above equation as −

$$\frac{I_0}{V_i}=\frac{1}{R_1}$$

The above equation represents the ratio of the output current $I_{0}$ and the input voltage $V_{i}$ & it is equal to the reciprocal of resistance $R_{1}$ The ratio of the output current $I_{0}$ and the input voltage $V_{i}$ is called as Transconductance.

We know that the ratio of the output and the input of a circuit is called as gain. So, the gain of an voltage to current converter is the Transconductance and it is equal to the reciprocal of resistance $R_{1}$.

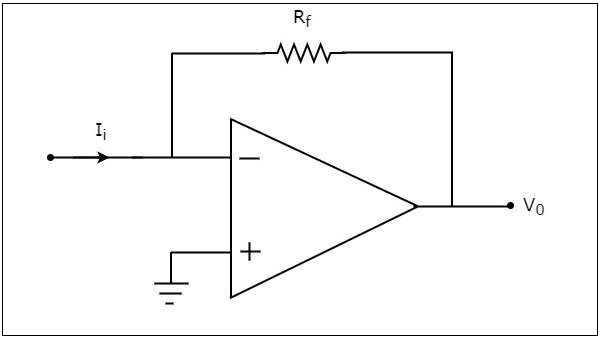

Current to Voltage Converter

A current to voltage converter or I to V converter is an electronic circuit that takes current as the input and produces voltage as the output. This section discusses about the op-amp based current to voltage converter.

An op-amp based current to voltage converter produces an output voltage when current is applied to its inverting terminal. The circuit diagram of an op-amp based current to voltage converter is shown in the following figure.

In the circuit shown above, the non-inverting input terminal of the op-amp is connected to ground. That means zero volts is applied at its non-inverting input terminal.

According to the virtual short concept, the voltage at the inverting input terminal of an op-amp will be equal to the voltage at its non-inverting input terminal. So, the voltage at the inverting input terminal of the op-amp will be zero volts.

The nodal equation at the inverting terminal's node is −

$$-I_{i}+\frac{0-V_0}{R_f}=0$$

$$-I_{i}=\frac{V_0}{R_f}$$

$$V_{0}=-R_{t}I_{i}$$

Thus, the output voltage, $V_{0}$ of current to voltage converter is the (negative) product of the feedback resistance, $R_{f}$ and the input current, $I_{t}$. Observe that the output voltage, $V_{0}$ is having a negative sign, which indicates that there exists a 1800 phase difference between the input current and output voltage.

We can re-write the above equation as −

$$\frac{V_0}{I_i}=-R_{f}$$

The above equation represents the ratio of the output voltage $V_{0}$ and the input current $I_{i}$, and it is equal to the negative of feedback resistance, $R_{f}$. The ratio of output voltage $V_{0}$ and input current $I_{i}$ is called as Transresistance.

We know that the ratio of output and input of a circuit is called as gain. So, the gain of a current to voltage converter is its trans resistance and it is equal to the (negative) feedback resistance $R_{f}$ .

A comparator is an electronic circuit, which compares the two inputs that are applied to it and produces an output. The output value of the comparator indicates which of the inputs is greater or lesser. Please note that comparator falls under non-linear applications of ICs.

An op-amp consists of two input terminals and hence an op-amp based comparator compares the two inputs that are applied to it and produces the result of comparison as the output. This chapter discusses about op-amp based comparators.

Types of Comparators

Comparators are of two types : Inverting and Non-inverting. This section discusses about these two types in detail.

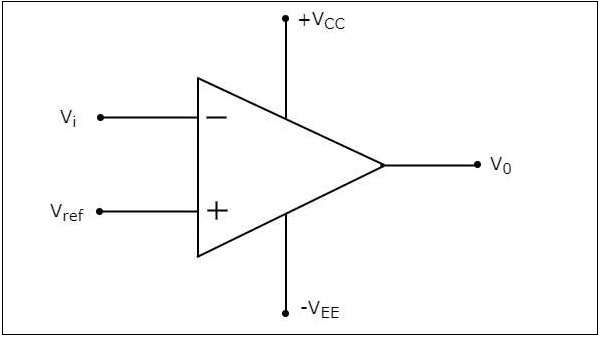

Inverting Comparator

An inverting comparator is an op-amp based comparator for which a reference voltage is applied to its non-inverting terminal and the input voltage is applied to its inverting terminal. This comparator is called as inverting comparator because the input voltage, which has to be compared is applied to the inverting terminal of op-amp.

The circuit diagram of an inverting comparator is shown in the following figure.

The operation of an inverting comparator is very simple. It produces one of the two values, $+V_{sat}$ and $-V_{sat}$ at the output based on the values of its input voltage $V_{i}$ and the reference voltage $V_{ref}$.

The output value of an inverting comparator will be $-V_{sat}$, for which the input $V_{i}$ voltage is greater than the reference voltage $V_{ref}$.

The output value of an inverting comparator will be $+V_{sat}$, for which the input $V_{i}$ is less than the reference voltage $V_{ref}$.

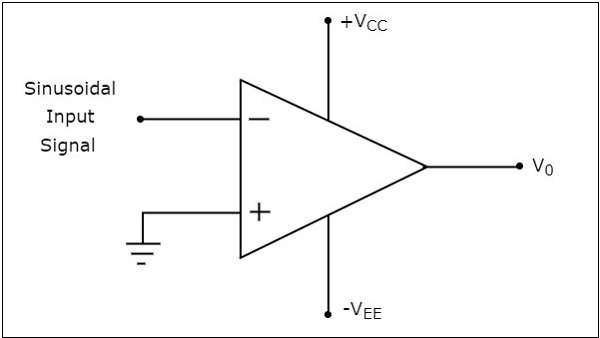

Example

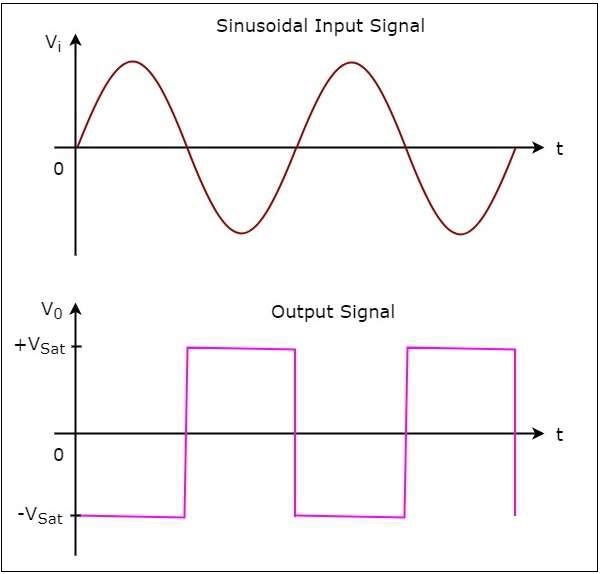

Let us draw the output wave form of an inverting comparator, when a sinusoidal input signal and a reference voltage of zero volts are applied to its inverting and non-inverting terminals respectively.

The operation of the inverting comparator shown above is discussed below −

During the positive half cycle of the sinusoidal input signal, the voltage present at the inverting terminal of op-amp is greater than zero volts. Hence, the output value of the inverting comparator will be equal to $-V_{sat}$ during positive half cycle of the sinusoidal input signal.

Similarly, during the negative half cycle of the sinusoidal input signal, the voltage present at the inverting terminal of the op-amp is less than zero volts. Hence, the output value of the inverting comparator will be equal to $+V_{sat}$ during negative half cycle of the sinusoidal input signal.

The following figure shows the input and output waveforms of an inverting comparator, when the reference voltage is zero volts.

In the figure shown above, we can observe that the output transitions either from $-V_{sat}$ to $+V_{sat}$ or from $+V_{sat}$ to $-V_{sat}$ whenever the sinusoidal input signal is crossing zero volts. In other words, output changes its value when the input is crossing zero volts. Hence, the above circuit is also called as inverting zero crossing detector.

Non-Inverting Comparator

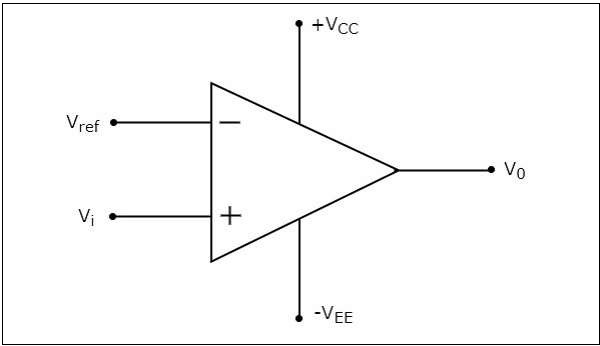

A non-inverting comparator is an op-amp based comparator for which a reference voltage is applied to its inverting terminal and the input voltage is applied to its non-inverting terminal. This op-amp based comparator is called as non-inverting comparator because the input voltage, which has to be compared is applied to the non-inverting terminal of the op-amp.

The circuit diagram of a non-inverting comparator is shown in the following figure

The operation of a non-inverting comparator is very simple. It produces one of the two values, $+V_{sat}$ and $-V_{sat}$ at the output based on the values of input voltage $V_{t}$ and the reference voltage $+V_{ref}$.

The output value of a non-inverting comparator will be $+V_{sat}$, for which the input voltage $V_{i}$ is greater than the reference voltage $+V_{ref}$.

The output value of a non-inverting comparator will bee $-V_{sat}$, for which the input voltage $V_{i}$ is less than the reference voltage $+V_{ref}$.

Example

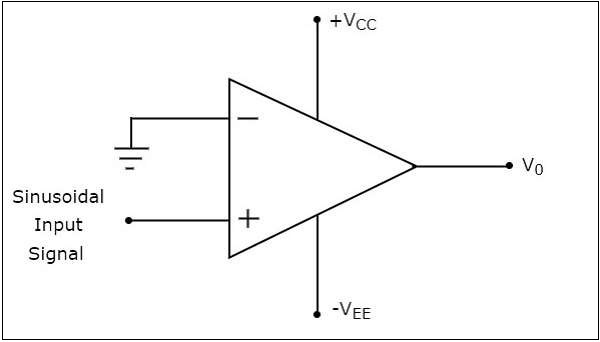

Let us draw the output wave form of a non-inverting comparator, when a sinusoidal input signal and reference voltage of zero volts are applied to the non-inverting and inverting terminals of the op-amp respectively.

The operation of a non-inverting comparator is explained below −

During the positive half cycle of the sinusoidal input signal, the voltage present at the non-inverting terminal of op-amp is greater than zero volts. Hence, the output value of a non-inverting comparator will be equal to $+V_{sat}$ during the positive half cycle of the sinusoidal input signal.

Similarly, during the negative half cycle of the sinusoidal input signal, the voltage present at the non-inverting terminal of op-amp is less than zero volts. Hence, the output value of non-inverting comparator will be equal to $-V_{sat}$ during the negative half cycle of the sinusoidal input signal.

The following figure shows the input and output waveforms of a non-inverting comparator, when the reference voltage is zero volts.

From the figure shown above, we can observe that the output transitions either from $+V_{sat}$ to $-V_{sat}$ or from $-V_{sat}$ to $+V_{sat}$ whenever the sinusoidal input signal crosses zero volts. That means, the output changes its value when the input is crossing zero volts. Hence, the above circuit is also called as non-inverting zero crossing detector.

The electronic circuits which perform the mathematical operations such as logarithm and anti-logarithm (exponential) with an amplification are called as Logarithmic amplifier and Anti-Logarithmic amplifier respectively.

This chapter discusses about the Logarithmic amplifier and Anti-Logarithmic amplifier in detail. Please note that these amplifiers fall under non-linear applications.

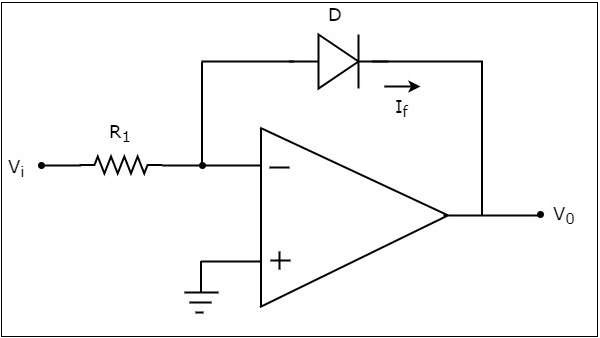

Logarithmic Amplifier

A logarithmic amplifier, or a log amplifier, is an electronic circuit that produces an output that is proportional to the logarithm of the applied input. This section discusses about the op-amp based logarithmic amplifier in detail.

An op-amp based logarithmic amplifier produces a voltage at the output, which is proportional to the logarithm of the voltage applied to the resistor connected to its inverting terminal. The circuit diagram of an op-amp based logarithmic amplifier is shown in the following figure −

In the above circuit, the non-inverting input terminal of the op-amp is connected to ground. That means zero volts is applied at the non-inverting input terminal of the op-amp.

According to the virtual short concept, the voltage at the inverting input terminal of an op-amp will be equal to the voltage at its non-inverting input terminal. So, the voltage at the inverting input terminal will be zero volts.

The nodal equation at the inverting input terminal’s node is −

$$\frac{0-V_i}{R_1}+I_{f}=0$$

$$=>I_{f}=\frac{V_i}{R_1}......Equation 1$$

The following is the equation for current flowing through a diode, when it is in forward bias −

$$I_{f}=I_{s} e^{(\frac{V_f}{nV_T})} ......Equation 2$$

where,

$I_{s}$ is the saturation current of the diode,

$V_{f}$ is the voltage drop across diode, when it is in forward bias,

$V_{T}$ is the diode’s thermal equivalent voltage.

The KVL equation around the feedback loop of the op amp will be −

$$0-V_{f}-V_{0}=0$$

$$=>V_{f}=-V_{0}$$

Substituting the value of $V_{f}$ in Equation 2, we get −

$$I_{f}=I_{s} e^{\left(\frac{-V_0}{nV_T}\right)} ......Equation 3$$

Observe that the left hand side terms of both equation 1 and equation 3 are same. Hence, equate the right hand side term of those two equations as shown below −

$$\frac{V_i}{R_1}=I_{s}e^{\left(\frac{-V_0}{nV_T}\right)}$$

$$\frac{V_i}{R_1I_s}= e^{\left(\frac{-V_0}{nV_T}\right)}$$

Applying natural logarithm on both sides, we get −

$$In\left(\frac{V_i}{R_1I_s}\right)= \frac{-V_0}{nV_T}$$

$$V_{0}=-{nV_T}In\left(\frac{V_i}{R_1I_s}\right)$$

Note that in the above equation, the parameters n, ${V_T}$ and $I_{s}$ are constants. So, the output voltage $V_{0}$ will be proportional to the natural logarithm of the input voltage $V_{i}$ for a fixed value of resistance $R_{1}$.

Therefore, the op-amp based logarithmic amplifier circuit discussed above will produce an output, which is proportional to the natural logarithm of the input voltage ${V_T}$, when ${R_1I_s}=1V$.

Observe that the output voltage $V_{0}$ has a negative sign, which indicates that there exists a 1800 phase difference between the input and the output.

Anti-Logarithmic Amplifier

An anti-logarithmic amplifier, or an anti-log amplifier, is an electronic circuit that produces an output that is proportional to the anti-logarithm of the applied input. This section discusses about the op-amp based anti-logarithmic amplifier in detail.

An op-amp based anti-logarithmic amplifier produces a voltage at the output, which is proportional to the anti-logarithm of the voltage that is applied to the diode connected to its inverting terminal.

The circuit diagram of an op-amp based anti-logarithmic amplifier is shown in the following figure −

In the circuit shown above, the non-inverting input terminal of the op-amp is connected to ground. It means zero volts is applied to its non-inverting input terminal.

According to the virtual short concept, the voltage at the inverting input terminal of op-amp will be equal to the voltage present at its non-inverting input terminal. So, the voltage at its inverting input terminal will be zero volts.

The nodal equation at the inverting input terminal’s node is −

$$-I_{f}+\frac{0-V_0}{R_f}=0$$

$$=>-\frac{V_0}{R_f}=I_{f}$$

$$=>V_{0}=-R_{f}I_{f}.........Equation 4$$

We know that the equation for the current flowing through a diode, when it is in forward bias, is as given below −

$$I_{f}=I_{s} e^{\left(\frac{V_f}{nV_T}\right)}$$

Substituting the value of $I_{f}$ in Equation 4, we get

$$V_{0}=-R_{f}\left \{{I_{s} e^{\left(\frac{V_f}{nV_T}\right)}}\right \}$$

$$V_{0}=-R_{f}{I_{s} e^{\left(\frac{V_f}{nV_T}\right)}}......Equation 5$$

The KVL equation at the input side of the inverting terminal of the op amp will be

$$V_{i}-V_{f}=0$$

$$V_{f}=V_{i}$$

Substituting, the value of in the Equation 5, we get −

$$V_{0}=-R_{f}{I_{s} e^{\left(\frac{V_i}{nV_T}\right)}}$$

Note that, in the above equation the parameters n, ${V_T}$ and $I_{s}$ are constants. So, the output voltage ${V_0}$ will be proportional to the anti-natural logarithm (exponential) of the input voltage ${V_i}$, for a fixed value of feedback resistance ${R_f}$.

Therefore, the op-amp based anti-logarithmic amplifier circuit discussed above will produce an output, which is proportional to the anti-natural logarithm (exponential) of the input voltage ${V_i}$ when, ${R_fI_s}= 1V$. Observe that the output voltage ${V_0}$ is having a negative sign, which indicates that there exists a 1800 phase difference between the input and the output.

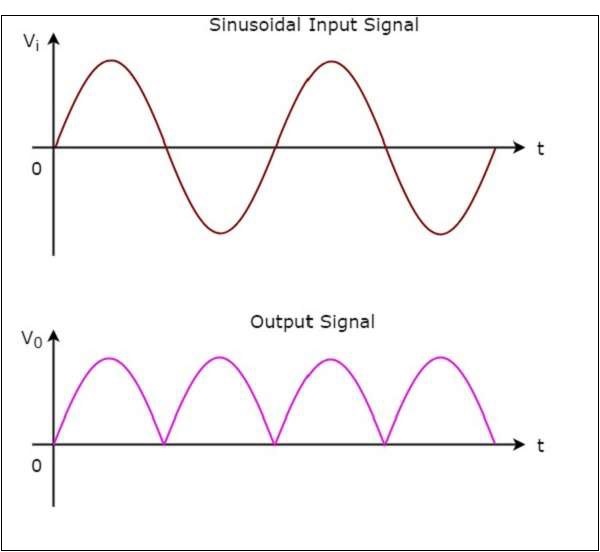

AC and DC are two frequent terms that you encounter while studying the flow of electrical charge. Alternating Current (AC) has the property to change its state continuously. For example, if we consider a sine wave, the current flows in one direction for positive half cycle and in the opposite direction for negative half cycle. On the other hand, Direct Current (DC) flows only in one direction.

An electronic circuit, which produces either DC signal or a pulsated DC signal, when an AC signal is applied to it is called as a rectifier. This chapter discusses about op-amp based rectifiers in detail.

Types of Rectifiers

Rectifiers are classified into two types: Half wave rectifier and Full wave rectifier. This section discusses about these two types in detail.

Half wave Rectifier

A half wave rectifier is a rectifier that produces positive half cycles at the output for one half cycle of the input and zero output for the other half cycle of the input.

The circuit diagram of a half wave rectifier is shown in the following figure.

Observe that the circuit diagram of a half wave rectifier shown above looks like an inverting amplifier, with two diodes D1 and D2 in addition.

The working of the half wave rectifier circuit shown above is explained below

For the positive half cycle of the sinusoidal input, the output of the op-amp will be negative. Hence, diode D1 will be forward biased.

When diode D1 is in forward bias, output voltage of the op-amp will be -0.7 V. So, diode D2 will be reverse biased. Hence, the output voltage of the above circuit is zero volts.

Therefore, there is no (zero) output of half wave rectifier for the positive half cycle of a sinusoidal input.

For the negative half cycle of sinusoidal input, the output of the op-amp will be positive. Hence, the diodes D1 and D2 will be reverse biased and forward biased respectively. So, the output voltage of above circuit will be −

$$V_0=-\left(\frac{R_f}{R_1}\right)V_1$$

Therefore, the output of a half wave rectifier will be a positive half cycle for a negative half cycle of the sinusoidal input.

Wave forms

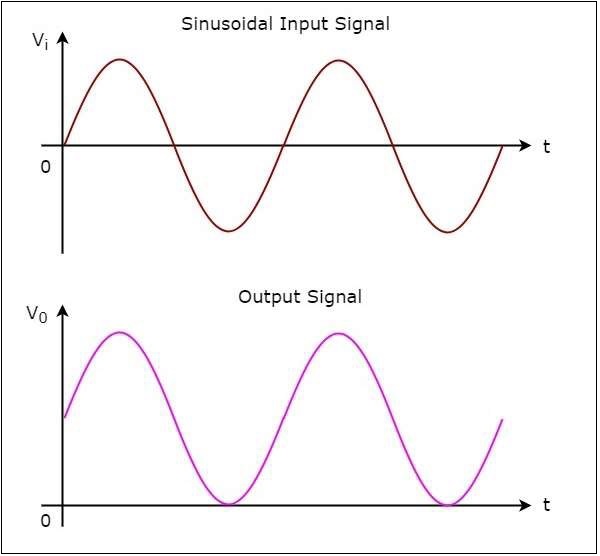

The input and output waveforms of a half wave rectifier are shown in the following figure

As you can see from the above graph, the half wave rectifier circuit diagram that we discussed will produce positive half cycles for negative half cycles of sinusoidal input and zero output for positive half cycles of sinusoidal input

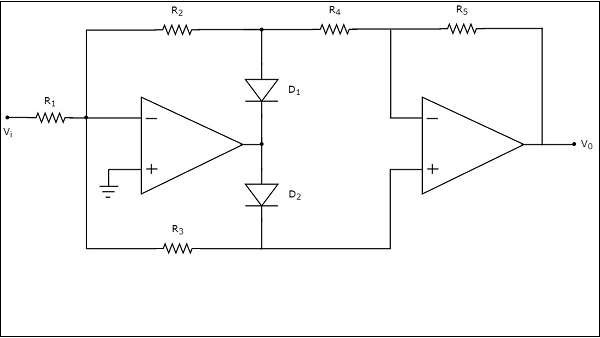

Full wave Rectifier

A full wave rectifier produces positive half cycles at the output for both half cycles of the input.

The circuit diagram of a full wave rectifier is shown in the following figure −

The above circuit diagram consists of two op-amps, two diodes, D1 & D2 and five resistors, R1 to R5. The working of the full wave rectifier circuit shown above is explained below −

For the positive half cycle of a sinusoidal input, the output of the first op-amp will be negative. Hence, diodes D1 and D2 will be forward biased and reverse biased respectively.

Then, the output voltage of the first op-amp will be −

$$V_{01}=-\left(\frac{R_2}{R_1}\right)V_i$$

Observe that the output of the first op-amp is connected to a resistor R4, which is connected to the inverting terminal of the second op-amp. The voltage present at the non-inverting terminal of second op-amp is 0 V. So, the second op-amp with resistors, R4 and R4 acts as an inverting amplifier.

The output voltage of the second op-amp will be

$$V_0=-\left(\frac{R_5}{R_4}\right)V_{01}$$

Substituting the value of $V_{01}$ in the above equation, we get −

$$=>V_{0}=-\left(\frac{R_5}{R_4}\right)\left \{ -\left(\frac{R_2}{R_1}\right)V_{i} \right \}$$

$$=>V_{0}=\left(\frac{R_2R_5}{R_1R_4}\right)V_{i}$$

Therefore, the output of a full wave rectifier will be a positive half cycle for the positive half cycle of a sinusoidal input. In this case, the gain of the output is $\frac{R_2R_5}{R_1R_4}$. If we consider $R_{1}=R_{2}=R_{4}=R_{5}=R$, then the gain of the output will be one.

For the negative half cycle of a sinusoidal input, the output of the first op-amp will be positive. Hence, diodes D1 and D2 will be reverse biased and forward biased respectively.

The output voltage of the first op-amp will be −

$$V_{01}=-\left(\frac{R_3}{R_1}\right)V_{i}$$

The output of the first op-amp is directly connected to the non-inverting terminal of the second op-amp. Now, the second op-amp with resistors, R4 and R5 acts as a non-inverting amplifier.

The output voltage of the second op-amp will be −

$$V_{0}=\left(1+\frac{R_5}{R_4}\right)V_{01}$$

Substituting the value of $V_{01}$ in the above equation, we get

$$=>V_{0}=\left(1+\frac{R_5}{R_4}\right) \left\{-\left(\frac{R_3}{R_1}\right)V_{i}\right \} $$

$$=>V_{0}=-\left(\frac{R_3}{R_1}\right)\left(1+\frac{R_5}{R_4}\right)V_{i}$$

Therefore, the output of a full wave rectifier will be a positive half cycle for the negative half cycle of sinusoidal input also. In this case, the magnitude of the gain of the output is $\left(\frac{R_3}{R_1}\right)\left(1+\frac{R_5}{R_4}\right)$. If we consider $R_{1}=2R_{3}=R_{4}=R_{5}=R$ then the gain of the output will be one.

The input and output waveforms of a full wave rectifier are shown in the following figure

위 그림에서 볼 수 있듯이 우리가 고려한 전파 정류기 회로도는 positive half cycles 정현파 입력의 양수 및 음수 반주기 모두에 대해.

Wave shaping circuits적용된 입력 파형의 출력에서 원하는 모양을 생성하는 전자 회로입니다. 이 회로는 두 가지 기능을 수행합니다.

- 적용된 파동 감쇠

- 적용된 파동의 DC 레벨을 변경합니다.

웨이브 쉐이핑 회로에는 두 가지 유형이 있습니다. Clippers 과 Clampers. 이 장에서는 클리퍼에 대해 자세히 배웁니다.

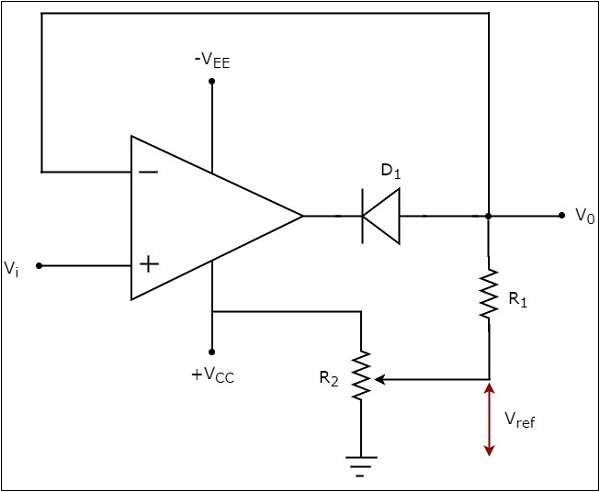

연산 증폭기 기반 클리퍼

ㅏ clipper입력의 일부를 기준 값 위 또는 아래로 제거하여 출력을 생성하는 전자 회로입니다. 즉, 클리퍼의 출력은 잘린 부분이 아닌 다른 입력의 출력과 동일합니다. 이로 인해 클리퍼 출력의 피크 대 피크 진폭은 항상 입력의 진폭보다 작습니다.

클리퍼의 가장 큰 장점은 ac 신호의 진폭에 존재하는 원치 않는 노이즈를 제거한다는 것입니다.

Clippers는 입력의 클리핑 부분에 따라 다음 두 가지 유형으로 분류 할 수 있습니다.

- 포지티브 클리퍼

- 네거티브 클리퍼

이것들은 아래에 주어진 것처럼 자세히 논의됩니다-

포지티브 클리퍼

ㅏ positive clipper 입력 신호의 양의 부분 만 클리핑하는 클리퍼입니다.

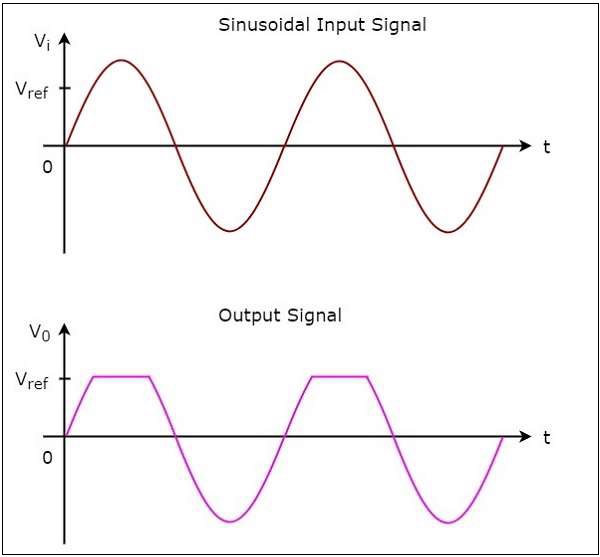

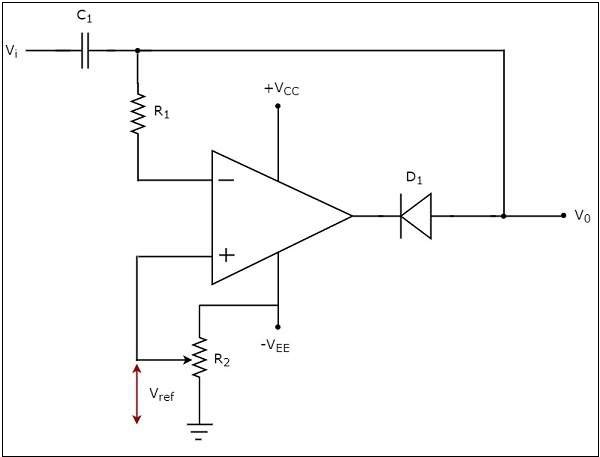

그만큼 circuit diagram포지티브 클리퍼의 다음 그림은-

위에 표시된 회로에서 정현파 전압 신호 $V_{t}$연산 증폭기의 비 반전 단자에 적용됩니다. 기준 전압의 값$V_{ref}$ 저항을 변경하여 선택할 수 있습니다. $R_{2}$.

그만큼 operation 위에 표시된 회로의 설명은 다음과 같습니다.

입력 전압의 값이 $V_i$ 기준 전압의 값보다 작습니다. $V_{ref}$, 다이오드 D 1이 전도됩니다. 그런 다음 위에 주어진 회로는voltage follower. 따라서 출력 전압$V_{0}$ 위 회로의 입력 전압과 동일합니다 $V_{i}$, for $V_{i}$ < $V_{ref}$.

입력 전압의 값이 $V_{i}$ 기준 전압 값보다 큽니다. $V_{ref}$, 다이오드 D 1 이 꺼집니다. 이제 연산 증폭기는 피드백 경로가 열려 있기 때문에 개방 루프에서 작동합니다. 따라서 출력 전압$V_{0}$ 위 회로의 기준 전압의 값과 같을 것입니다 $V_{ref}$, for $V_{i}$ > $V_{ref}$.

그만큼 input wave form 및 해당 output wave form 양의 기준 전압에 대한 양의 클리퍼의 $V_{ref}$, 다음 그림에 나와 있습니다-

네거티브 클리퍼

ㅏ negative clipper입력 신호의 음의 부분 만 클리핑하는 클리퍼입니다. 양극 클리퍼에 대해 본 회로에서 다이오드를 반전하고 기준 전압의 역 극성을 취함으로써 음극 클리퍼의 회로를 얻을 수 있습니다.

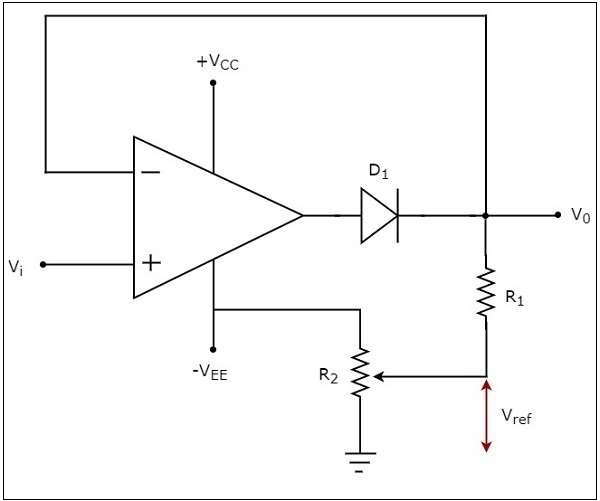

그만큼 circuit diagram 네거티브 클리퍼의 다음 그림은-

위의 회로에서 정현파 전압 신호 $V_{i}$연산 증폭기의 비 반전 단자에 적용됩니다. 기준 전압의 값$V_{ref}$ 저항을 변경하여 선택할 수 있습니다. $R_{2}$.

그만큼 operation 네거티브 클리퍼 회로의 설명은 다음과 같습니다.

입력 전압의 값이 $V_{t}$ 기준 전압 값보다 큽니다. $V_{ref}$, 다이오드 D 1이 전도됩니다. 그런 다음 위의 회로는voltage follower. 따라서 출력 전압$V_{0}$ 위 회로의 입력 전압과 동일합니다 $V_{i}$ ...에 대한 $V_{i}$> $V_{ref}$.

입력 전압의 값이 $V_{i}$기준 전압 값보다 작 으면 다이오드 D 1 이 꺼집니다. 이제 연산 증폭기는 피드백 경로가 열려 있으므로 개방 루프에서 작동합니다. 따라서 출력 전압$V_{0}$ 위 회로의 기준 전압의 값과 같을 것입니다,$V_{ref}$ ...에 대한 $V_{i}$ < $V_{ref}$.

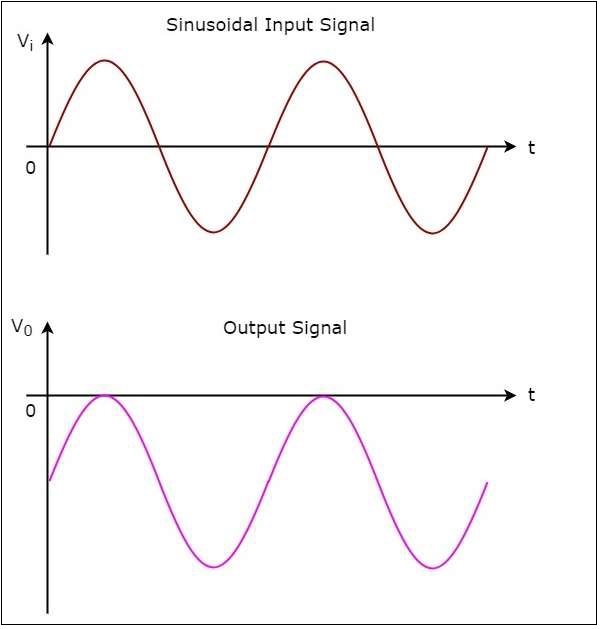

그만큼 input wave form 및 해당 output wave form 음의 기준 전압에 대해 음의 깎기의 $V_{ref}$, 다음 그림에 나와 있습니다-

이전 장에서 우리는 가위에 대해 논의했습니다. 이제 다른 유형의 파형 형성 회로, 즉 클램퍼에 대해 논의하겠습니다.

연산 증폭기 기반 클램퍼

ㅏ clamper입력과 유사하지만 DC 레벨이 이동하는 출력을 생성하는 전자 회로입니다. 즉, 클램퍼의 출력은 입력의 정확한 복제입니다. 따라서 클램퍼 출력의 피크 대 피크 진폭은 항상 입력의 진폭과 동일합니다.

클램퍼는 출력에서 입력 신호의 DC 레벨을 도입하거나 복원하는 데 사용됩니다. 있습니다two types 입력의 DC 시프트를 기반으로 연산 증폭기 기반 클램퍼의.

- 긍정적 인 클램퍼

- 네거티브 클램퍼

이 섹션에서는 이러한 두 가지 유형의 클램퍼에 대해 자세히 설명합니다.

긍정적 인 클램퍼

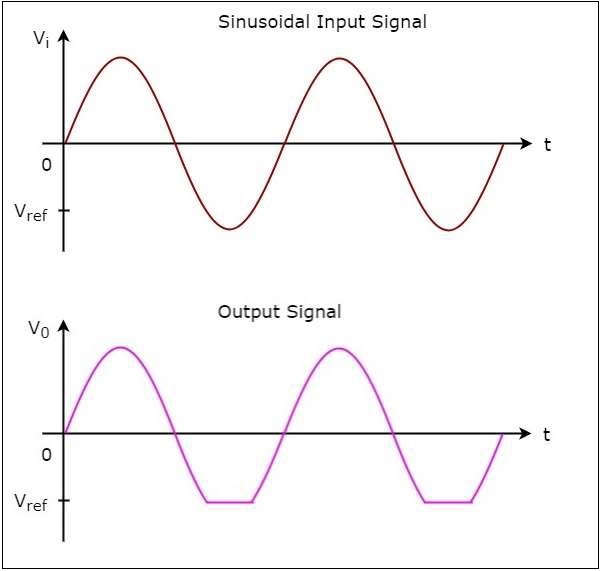

포지티브 클램퍼는 입력 신호가 양의 DC 값만큼 수직으로 이동하는 방식으로 출력을 생성하는 클램퍼 회로입니다.

그만큼 circuit diagram 포지티브 클램퍼의 그림은 다음과 같습니다.

위의 회로에서 sinusoidal voltage signal, $V_{i}$ 커패시터로 구성된 네트워크를 통해 연산 증폭기의 반전 단자에 적용됩니다. $C_{1}$ 및 저항 $R_{1}$. 즉, AC 전압 신호가 연산 증폭기의 반전 단자에 적용됩니다.

그만큼 DC reference voltage $V_{ref}$ 연산 증폭기의 비 반전 단자에 적용됩니다. 기준 전압 값$V_{ref}$ 저항을 변경하여 선택할 수 있습니다. $R_{2}$. 이 경우 기준 전압을 얻습니다.$V_{ref}$ 긍정적 인 가치.

위의 회로는 output, 어느 is the combination (resultant sum) 정현파 전압 신호의 $V_{i}$ 및 기준 전압 $V_{ref}$. 즉, 클램퍼 회로는 정현파 전압 신호가$V_{i}$ 기준 전압 값만큼 수직으로 위쪽으로 이동합니다. $V_{ref}$.

포지티브 클램퍼의 입력 파형과 해당 출력 파형은 위 그림과 같습니다.

위 그림에서 포지티브 클램퍼가 적용된 입력 파형을 이동시키는 것을 볼 수 있습니다. vertically upward출력에서. 이동량은 DC 기준 전압 값에 따라 달라집니다.

네거티브 클램퍼

ㅏ negative clamper 입력 신호가 음의 DC 값만큼 수직으로 이동하는 방식으로 출력을 생성하는 클램퍼 회로입니다.

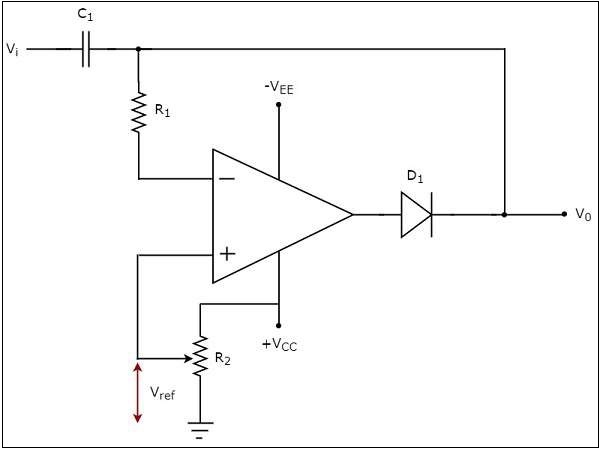

그만큼 circuit diagram 네거티브 클램퍼의 그림은 다음과 같습니다.

위의 회로에서 sinusoidal voltage signal $V_{i}$ 커패시터 C 1 과 저항으로 구성된 네트워크를 통해 연산 증폭기의 반전 단자에 적용됩니다.$R_{1}$. 즉, AC 전압 신호가 연산 증폭기의 반전 단자에 적용됩니다.

그만큼 DC reference voltage $V_{ref}$ 연산 증폭기의 비 반전 단자에 적용됩니다. 기준 전압의 값 $V_{ref}$ 저항을 변경하여 선택할 수 있습니다. $R_{2}$. 이 경우 기준 전압을 얻습니다.$V_{ref}$ 음수 값.

위의 회로는 정현파 전압 신호의 조합 (결과 합계) 인 출력을 생성합니다. $V_{i}$ 및 기준 전압 $V_{ref}$. 즉, 클램퍼 회로는 정현파 전압 신호가$V_{i}$ 기준 전압 값만큼 수직으로 아래쪽으로 이동합니다. $V_{ref}$.

네거티브 클램퍼의 입력 파형과 해당 출력 파형은 다음 그림과 같습니다.

출력에서 음의 클램퍼가 적용된 입력 파형을 이동시키는 것을 볼 수 있습니다. vertically downward출력에서. 이동량은 DC 기준 전압 값에 따라 달라집니다.

Filters특정 주파수 구성 요소를 허용하거나 다른 구성 요소를 거부하는 전자 회로입니다. 네트워크 이론 튜토리얼에서 필터를 접했을 수 있습니다. 이들은 수동적이며 저항, 커패시터 및 (또는) 인덕터와 같은 수동 요소로 구성된 전기 회로 또는 네트워크입니다.

이 장에서는 다음에 대해 설명합니다. active filters 상세히.

활성 필터의 유형

능동 필터는 저항 및 커패시터와 같은 수동 소자와 함께 연산 증폭기와 같은 능동 소자로 구성된 전자 회로입니다.

능동 필터는 주로 다음과 같이 분류됩니다. four types 허용 및 / 또는 거부하는 주파수 대역에 따라

- 액티브 로우 패스 필터

- 액티브 하이 패스 필터

- 활성 대역 통과 필터

- 활성 대역 정지 필터

액티브 로우 패스 필터

활성 필터가 허용 (통과) 만 허용하는 경우 low frequency 다른 모든 고주파 성분을 거부 (차단) 한 다음 active low pass filter.

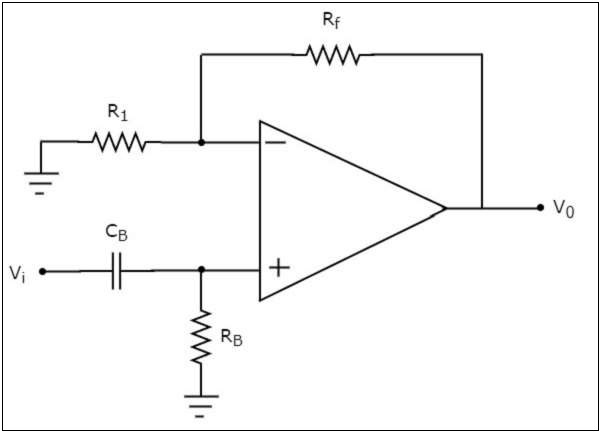

그만큼 circuit diagram 활성 저역 통과 필터는 다음 그림에 나와 있습니다.

연산 증폭기의 비 반전 단자에 연결된 전기 네트워크가 passive low pass filter. 따라서 opamp의 비 반전 단자의 입력은 수동 저역 통과 필터의 출력입니다.

위의 회로가 non-inverting amplifier. 그것은 연산 증폭기의 비 반전 단자에 대한 입력으로 수동 저역 통과 필터의 출력을 가지고 있습니다. 따라서 출력을 생성합니다.$\left(1+\frac{R_f}{R_1}\right)$ 비 반전 터미널에 존재하는 입력의 배.

우리는 가치를 선택할 수 있습니다 $R_{f}$ 과 $R_{1}$ 적합하게 얻기 위해 desired gain출력에서. 저항 값을 고려하면$R_{f}$ 과 $R_{1}$ 제로 옴과 무한 옴으로 위의 회로는 unity gain 저역 통과 필터 출력.

액티브 하이 패스 필터

활성 필터가 허용 (통과) 만 허용하는 경우 high frequency 다른 모든 저주파 구성 요소를 거부 (차단) 한 다음 active high pass filter.

그만큼 circuit diagram 활성 고역 통과 필터는 다음 그림에 나와 있습니다.

연산 증폭기의 비 반전 단자에 연결된 전기 네트워크가 passive high pass filter. 따라서 opamp의 비 반전 단자의 입력은 수동 고역 통과 필터의 출력입니다.

이제 위의 회로는 non-inverting amplifier. 그것은 op-amp의 비 반전 단자에 대한 입력으로 수동 고역 통과 필터의 출력을 가지고 있습니다. 따라서 출력을 생성합니다.$\left(1+\frac{R_f}{R_1}\right)$ 비 반전 터미널에있는 입력을 곱합니다.

우리는 가치를 선택할 수 있습니다 $R_f$ 과 $R_1$ 적합하게 얻기 위해 desired gain출력에서. 저항 값을 고려하면$R_{f}$ 과 $R_{1}$ 제로 옴과 무한 옴으로 위의 회로는 unity gain 고역 통과 필터 출력.

활성 대역 통과 필터

활성 필터가 하나의 주파수 대역 만 허용 (통과)하는 경우이를 active band pass filter. 일반적으로이 주파수 대역은 저주파 범위와 고주파 범위 사이에 있습니다. 따라서 능동 대역 통과 필터는 저주파 및 고주파 성분을 모두 거부 (차단)합니다.

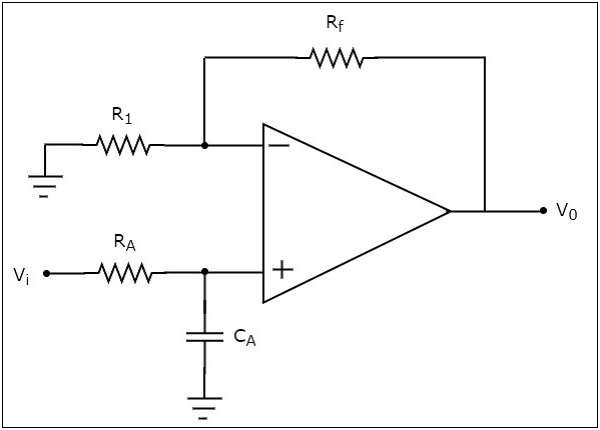

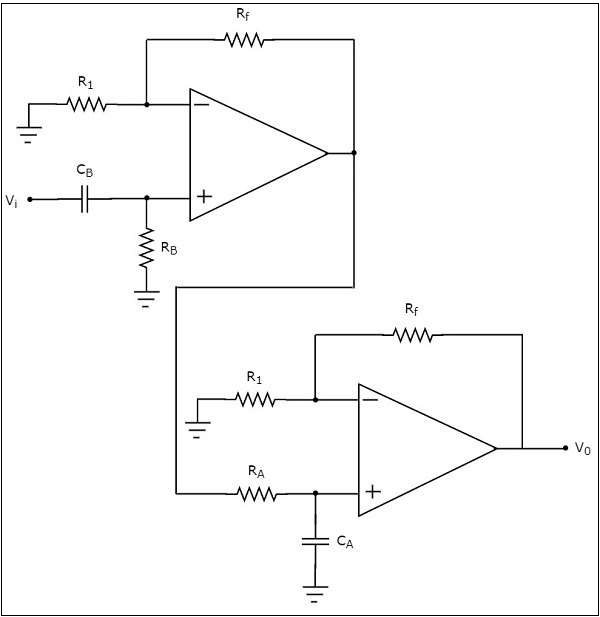

그만큼 circuit diagram 활성 대역 통과 필터는 다음 그림에 나와 있습니다.

있는지 관찰하십시오 two parts 활성 대역 통과 필터의 회로도에서 : 첫 번째 부분은 활성 고역 통과 필터이고 두 번째 부분은 활성 저역 통과 필터입니다.

액티브 하이 패스 필터의 출력은 액티브 로우 패스 필터의 입력으로 적용되므로 액티브 하이 패스 필터와 액티브 로우 패스 필터가 모두 cascaded 특정 주파수 대역 만 포함하는 방식으로 출력을 얻기 위해.

그만큼 active high pass filter, 첫 번째 단계에있는 경우보다 더 큰 주파수를 허용합니다. lower cut-off frequency활성 대역 통과 필터의. 그래서 우리는 값을 선택해야합니다$R_{B}$ 과 $C_{B}$ 적절하게, 원하는 것을 얻기 위해 lower cut-off frequency 활성 대역 통과 필터의.

마찬가지로 active low pass filter두 번째 단계에있는, 이는 활성 대역 통과 필터의 높은 차단 주파수보다 작은 주파수를 허용합니다. 그래서 우리는 값을 선택해야합니다$R_{A}$ 과 $C_{A}$ 원하는 것을 얻기 위해 적합하게 higher cut-off frequency 활성 대역 통과 필터의.

따라서 위에서 설명한 다이어그램의 회로는 활성 대역 통과 필터 출력을 생성합니다.

활성 대역 정지 필터

능동 필터가 특정 주파수 대역을 거부 (차단)하면 active band stop filter. 일반적으로이 주파수 대역은 저주파 범위와 고주파 범위 사이에 있습니다. 따라서 활성 대역 차단 필터는 저주파 및 고주파 성분을 모두 허용 (통과)합니다.

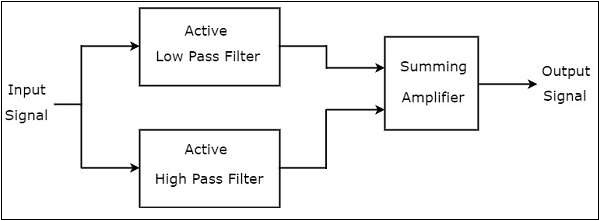

그만큼 block diagram 다음 그림은 활성 대역 정지 필터의 예입니다.

활성 대역 차단 필터의 블록 다이어그램이 첫 번째 단계에서 활성 로우 패스 필터와 활성 하이 패스 필터의 두 블록으로 구성되어 있습니다. 이 두 블록의 출력은 두 번째 단계에있는 블록에 대한 입력으로 적용됩니다. 그래서summing amplifier 활성 로우 패스 필터와 활성 하이 패스 필터의 출력 합계를 증폭 한 버전 인 출력을 생성합니다.

따라서 위 블록 다이어그램의 출력은 output of an active band stop , 저역 통과 필터의 차단 주파수를 고역 통과 필터의 차단 주파수보다 작게 선택할 때.

그만큼 circuit diagram 다음 그림은 활성 대역 정지 필터의 예입니다.

우리는 이미 액티브 로우 패스 필터, 액티브 하이 패스 필터 및 합산 증폭기의 회로도를 보았습니다. 위의 내용을 확인하십시오.circuit diagram 활성 대역 정지 필터의 블록 다이어그램에서 블록을 각각의 회로 다이어그램으로 대체하여 활성 대역 정지 필터의

발진기는주기적인 신호를 생성하는 전자 회로입니다. 오실레이터가 정현파 진동을 생성하는 경우이를sinusoidal oscillator. DC 소스의 입력 에너지를 주기적 신호의 AC 출력 에너지로 변환합니다. 이 주기적 신호는 특정 주파수와 진폭을 갖습니다.

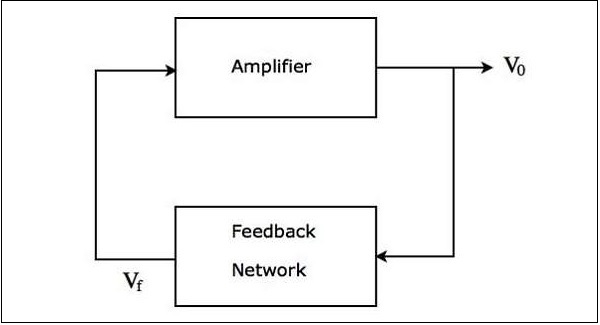

그만큼 block diagram 정현파 발진기의 다음 그림은-

위의 그림은 주로 two blocks: 증폭기 및 피드백 네트워크. 피드백 네트워크는 증폭기 출력의 일부를 입력으로 받아 전압 신호를 생성합니다. 이 전압 신호는 증폭기에 대한 입력으로 적용됩니다.

위에 표시된 사인파 오실레이터의 블록 다이어그램은 다음과 같은 경우 사인파 진동을 생성합니다. two conditions 만족합니다-

그만큼 loop gain $A_{v}\beta$ 정현파 발진기의 위 블록 다이어그램에서 다음보다 크거나 같아야합니다. unity. 여기,$A_{v}$ 과 $\beta$ 증폭기의 이득과 피드백 네트워크의 이득입니다.

전체 phase shift 정현파 발진기의 위 블록 다이어그램 루프 주변은 다음 중 하나 여야합니다. 00 또는 3600.

위의 두 가지 조건을 함께 호출합니다. Barkhausen criteria.

연산 증폭기 기반 발진기

있습니다 two 연산 증폭기 기반 발진기의 유형.

- RC 위상 편이 발진기

- 빈 브리지 발진기

이 섹션에서는 각각에 대해 자세히 설명합니다.

RC 위상 편이 발진기

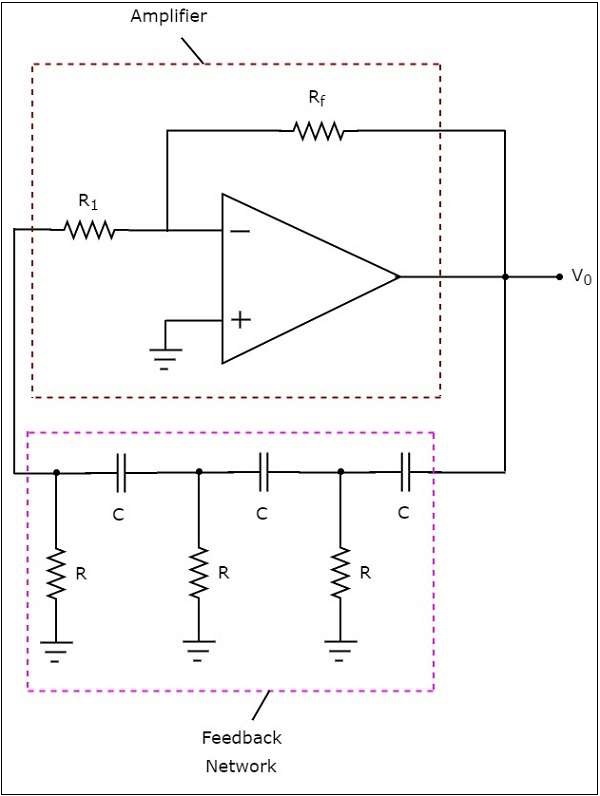

반전 증폭기와 피드백 네트워크의 도움으로 출력에서 정현파 전압 신호를 생성하는 연산 증폭기 기반 오실레이터는 RC phase shift oscillator. 이 피드백 네트워크는 세 개의 계단식 RC 섹션으로 구성됩니다.

그만큼 circuit diagram RC 위상 편이 발진기의 그림은 다음과 같습니다.

위의 회로에서 연산 증폭기는 inverting mode. 따라서 180 0 의 위상 편이를 제공합니다 . 위의 회로에있는 피드백 네트워크는 또한 각 RC 섹션이 60 0 의 위상 편이를 제공하기 때문에 180 0 의 위상 편이를 제공합니다 . 따라서 위의 회로는 일부 주파수에서 360 0 의 총 위상 편이를 제공합니다 .

그만큼 output frequency RC 위상 편이 발진기의-

$$f=\frac{1}{2\Pi RC\sqrt[]{6}}$$

그만큼 gain $A_{v}$ 반전 증폭기의 -29보다 크거나 같아야합니다.

$$i.e.,-\frac{R_f}{R_1}\geq-29$$

$$=>\frac{R_f}{R_1}\geq-29$$

$$=>R_{f}\geq29R_{1}$$

따라서 피드백 저항의 값을 고려해야합니다. $R_{f}$, 저항 값의 최소 29 배 $R_{1}$, RC 위상 편이 발진기의 출력에서 지속적인 발진을 생성합니다.

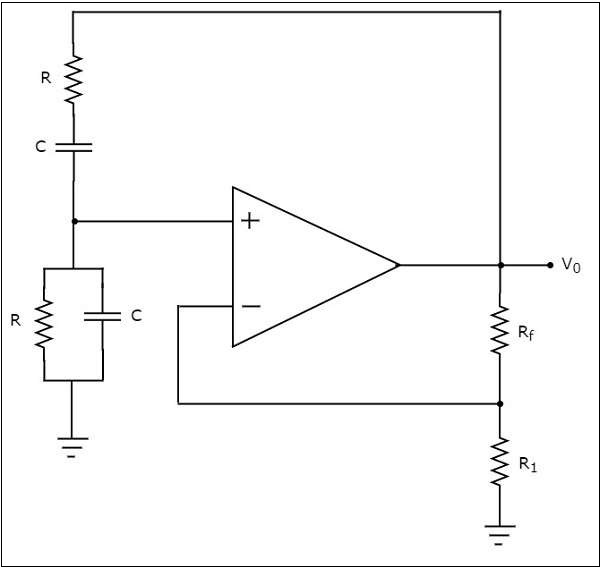

빈 브리지 발진기

비 반전 증폭기와 피드백 네트워크의 도움으로 출력에서 정현파 전압 신호를 생성하는 연산 증폭기 기반 발진기는 다음과 같이 알려져 있습니다. Wien bridge oscillator.

그만큼 circuit diagram Wien 브리지 오실레이터의 그림은 다음과 같습니다.

위의 Wein 브리지 발진기 회로에서 연산 증폭기는 non inverting mode. 따라서 00의 위상 편이를 제공합니다. 따라서 위 회로에있는 피드백 네트워크는 위상 편이를 제공하지 않아야합니다.

피드백 네트워크가 약간의 위상 편이를 제공하는 경우 balance the bridge위상 편이가 없어야합니다. 따라서 위의 회로는 일부 주파수에서 0 0 의 총 위상 편이를 제공합니다 .

그만큼 output frequency Wien 브리지 발진기의

$$f=\frac{1}{2\Pi RC}$$

그만큼 gain $A_{v}$ 비 반전 증폭기의 3 이상이어야합니다.

$$i.e.,1+\frac{R_f}{R_1}\geq3$$

$$=>\frac{R_f}{R_1}\geq2$$

$$=>R_{f}\geq2R_{1}$$

따라서 피드백 저항의 값을 고려해야합니다. $R_{f}$ 저항 값의 두 배 이상, $R_{1}$ Wien 브리지 발진기의 출력에서 지속적인 진동을 생성하기 위해.

ㅏ waveform generator표준 파를 생성하는 전자 회로입니다. 연산 증폭기 기반 파형 발생기에는 두 가지 유형이 있습니다.

- 구형파 발생기

- 삼각파 발생기

이 장에서는 이러한 각 연산 증폭기 기반 파형 발생기에 대해 자세히 설명합니다.

구형파 생성기

ㅏ square wave generator구형파를 생성하는 전자 회로입니다. 이 섹션에서는 연산 증폭기 기반 구형파 생성기에 대해 설명합니다.

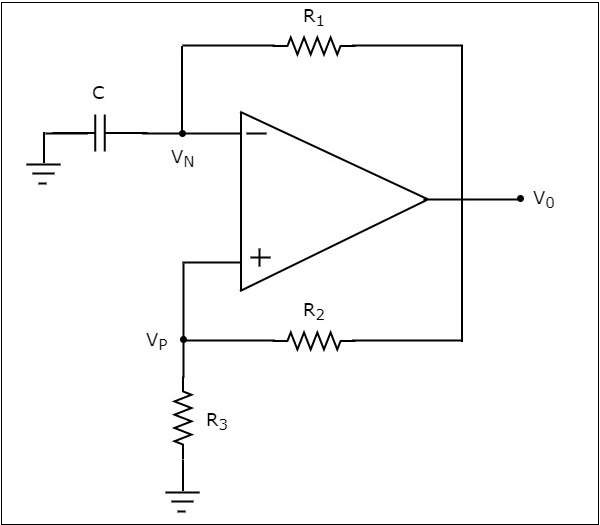

그만큼 circuit diagram 연산 증폭기 기반 구형파 발생기의 다음 그림은

위에 표시된 회로도에서 저항이 $R_{1}$연산 증폭기의 반전 입력 단자와 연산 증폭기의 출력 사이에 연결됩니다. 그래서 저항$R_{1}$ 사용됩니다 negative feedback. 마찬가지로 저항$R_{2}$연산 증폭기의 비 반전 입력 단자와 출력 사이에 연결됩니다. 그래서 저항$R_{2}$ 사용됩니다 positive feedback 통로.

커패시터 C는 연산 증폭기의 반전 입력 단자와 접지 사이에 연결됩니다. 그래서voltage across capacitor C연산 증폭기의이 반전 단자에서 입력 전압이됩니다. 마찬가지로 저항$R_{3}$연산 증폭기의 비 반전 입력 단자와 접지 사이에 연결됩니다. 그래서voltage across resistor $R_{3}$ 연산 증폭기의이 비 반전 단자의 입력 전압이됩니다.

그만큼 operation 구형파 발생기의 설명은 다음과 같습니다.

가정, no charge초기에 커패시터에 저장됩니다. 그러면 연산 증폭기의 반전 단자에 존재하는 전압은 0V입니다. 그러나 연산 증폭기의 비 반전 단자에는 약간의 오프셋 전압이 있습니다. 이로 인해 위 회로의 출력에 존재하는 값은$+V_{sat}$.

이제 커패시터 C가 시작됩니다. charging 저항기를 통해 $R_{1}$. 위 회로의 출력에 존재하는 값은 다음과 같이 변경됩니다.$-V_{sat}$, 커패시터 C 양단의 전압이 저항 양단의 전압 (양수 값)보다 크게 도달 할 때 $R_{3}$.

커패시터 C가 시작됩니다. discharging 저항기를 통해 $R_{1}$, 위 회로의 출력이 $-V_{sat}$. 위 회로의 출력에 존재하는 값은 다음과 같이 변경됩니다.$+V_{sat}$, 커패시터 C 양단의 전압이 저항 양단의 전압 (음수 값)보다 약간 낮을 때 (더 음의 값) $R_{3}$.

따라서 위의 다이어그램에 표시된 회로는 square wave 다음 그림과 같이 출력에서-

위의 그림에서 구형파 생성기의 출력이 두 값 중 하나를 갖는 것을 볼 수 있습니다. $+V_{sat}$ 과 $-V_{sat}$. 따라서 출력은 일정 기간 동안 한 값으로 유지 된 다음 다른 값으로 전환되고 일정 기간 동안 그대로 유지됩니다. 이런 식으로 계속됩니다.

삼각파 생성기

삼각파 생성기는 삼각파를 생성하는 전자 회로입니다. 그만큼block diagram 삼각파 생성기의 그림은 다음과 같습니다.

삼각파 생성기의 블록 다이어그램에는 주로 구형파 생성기와 적분기의 두 블록이 포함됩니다. 이 두 블록은cascaded. 즉, 사각 파 발생기의 출력이 적분기의 입력으로 적용됩니다. 구형파의 적분은 삼각파에 지나지 않습니다.

그만큼 circuit diagram 연산 증폭기 기반 삼각파 발생기의 다음 그림은 다음과 같습니다.

우리는 이미 구형파 발생기와 적분기의 회로도를 보았습니다. 위의 내용을 확인하십시오.circuit diagram 삼각파 생성기의 블록 다이어그램에서 블록을 각 회로 다이어그램으로 대체하여 연산 증폭기 기반 삼각파 생성기의.

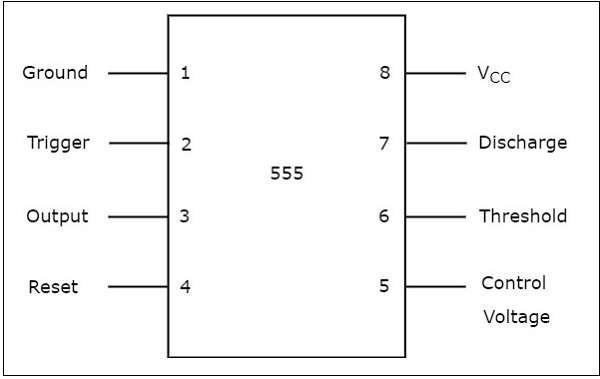

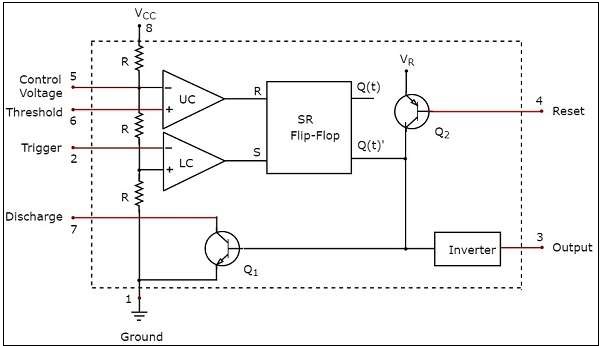

그만큼 555 Timer IC는 세 가지에서 이름을 얻었습니다. $5K\Omega$전압 분배기 네트워크에 사용되는 저항. 이 IC는 정확한 시간 지연 및 진동을 생성하는 데 유용합니다. 이 장에서는 555 타이머에 대해 자세히 설명합니다.

핀 다이어그램 및 기능 다이어그램

이 섹션에서는 먼저 555 Timer IC의 핀 다이어그램과 기능 다이어그램에 대해 논의하겠습니다.

핀 다이어그램

555 타이머 IC는 8 핀 미니 DIP (Dual-Inline Package)입니다. 그만큼pin diagram 555 타이머 IC의 다음 그림은-

각 핀의 중요성은 위의 다이어그램에서 자명합니다. 이 555 타이머 IC는 + 5V ~ + 18V의 DC 전원으로 작동 할 수 있습니다. 주로 생성에 유용합니다.non-sinusoidal 정사각형, 램프, 펄스 등과 같은 파형

기능 다이어그램

555 타이머의 내부 세부 정보를 보여주는 그림 표현을 기능 다이어그램이라고합니다.

그만큼 functional diagram 555 Timer IC의 다음 그림은-

555 Timer의 기능 다이어그램에는 전압 분배기 네트워크, 비교기 2 개, SR 플립 플롭 1 개, 트랜지스터 2 개 및 인버터가 포함되어 있습니다. 이 섹션에서는 각 블록 또는 구성 요소의 목적에 대해 자세히 설명합니다.

전압 분배기 네트워크

전압 분배기 네트워크는 세 개의 $5K\Omega$ 공급 전압 사이에 직렬로 연결된 저항 $V_{cc}$ 그리고 땅.

이 네트워크는 $\frac{V_{cc} }{3}$ 지점과지면 사이에 하나만있는 경우 $5K\Omega$저항기. 마찬가지로 전압을 제공합니다.$\frac{2V_{cc} }{3}$ 지점과지면 사이에 두 개만있는 경우 $5K\Omega$ 저항기.

비교기

555 타이머 IC의 기능 다이어그램은 상위 비교기 (UC)와 하위 비교기 (LC)의 두 비교기로 구성됩니다.

기억하십시오 comparator 적용된 두 입력을 비교하여 출력을 생성합니다.

연산 증폭기의 비 반전 단자에 존재하는 전압이 반전 단자에 존재하는 전압보다 크면 비교기의 출력은 $+V_{sat}$. 이것은 다음과 같이 간주 될 수 있습니다.Logic High ( '1') 디지털 표현.

연산 증폭기의 비 반전 단자에 존재하는 전압이 반전 단자의 전압보다 작거나 같으면 비교기의 출력은 다음과 같습니다. $-V_{sat}$. 이것은 다음과 같이 간주 될 수 있습니다.Logic Low ( '0') 디지털 표현.

SR 플립 플롭

기억하십시오 SR flip-flop포지티브 클록 전환 또는 네거티브 클록 전환으로 작동합니다. 두 개의 입력 : S와 R, 두 개의 출력 : Q (t) 및 Q (t) '가 있습니다. 출력 Q (t) 및 Q (t) '는 서로 보완됩니다.

다음 표는 state table SR 플립 플롭의

| 에스 | 아르 자형 | Q (t + 1) |

|---|---|---|

| 0 | 0 | Q (t) |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | - |

여기서 Q (t)와 Q (t + 1)은 각각 현재 상태와 다음 상태입니다. 따라서 SR 플립 플롭은 클럭 신호의 포지티브 (네거티브) 전환이 적용될 때 입력 조건에 따라 홀드, 리셋 및 설정과 같은 세 가지 기능 중 하나에 사용할 수 있습니다.

LC (Lower Comparator) 및 UC (Upper Comparator)의 출력은 다음과 같이 적용됩니다. inputs of SR flip-flop 555 Timer IC의 기능 다이어그램에 나와 있습니다.

트랜지스터 및 인버터

555 타이머 IC의 기능 다이어그램은 하나의 npn 트랜지스터로 구성됩니다. $Q_{1}$ 그리고 하나의 pnp 트랜지스터 $Q_{2}$. NPN 트랜지스터$Q_{1}$이미 터 전압에 대한베이스가 양이고 컷인 전압보다 큰 경우 켜집니다. 그렇지 않으면 꺼집니다.

pnp 트랜지스터 $Q_{2}$ 다음과 같이 사용됩니다. buffer SR 플립 플롭 및 npn 트랜지스터에서 리셋 입력을 분리하기 위해 $Q_{1}$.

그만큼 inverter 555 타이머 IC의 기능 다이어그램에 사용 된 것은 반전 동작을 수행 할뿐만 아니라 전력 레벨을 증폭합니다.

555 타이머 IC는 출력에서 펄스를 생성하기 위해 모노 안정 작동에서 사용할 수 있습니다. 마찬가지로, 출력에서 구형파를 생성하기 위해 불안정한 작동에 사용할 수 있습니다.

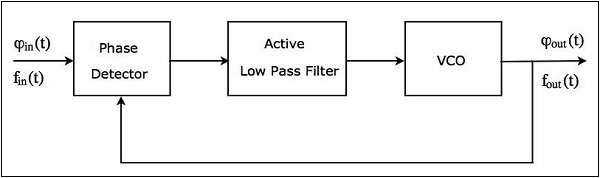

위상 고정 루프 (PLL)선형 시스템의 핵심 블록 중 하나입니다. 레이더, 위성, FM 등과 같은 통신 시스템에 유용합니다.

이 장에서는 PLL 및 IC 565의 블록 다이어그램에 대해 자세히 설명합니다.

PLL의 블록 다이어그램

위상 고정 루프 (PLL)는 주로 다음으로 구성됩니다. three blocks −

- 위상 검출기

- 액티브 로우 패스 필터

- 전압 제어 발진기 (VCO)

그만큼 block diagram PLL의 값은 다음 그림에 나와 있습니다.

위상 검출기의 출력은 액티브 로우 패스 필터의 입력으로 적용됩니다. 마찬가지로 액티브 로우 패스 필터의 출력은 VCO의 입력으로 적용됩니다.

그만큼 working PLL의 다음과 같습니다-

Phase detector 주파수가 다음과 같은 입력 신호 간의 위상차에 비례하는 DC 전압을 생성합니다. $f_{in}$ 및 주파수를 갖는 피드백 (출력) 신호 $f_{out}$.

ㅏ Phase detector 곱셈기이며 출력에서 두 개의 주파수 성분을 생성합니다-주파수의 합 $f_{in}$ 과 $f_{out}$ 그리고 주파수의 차이 $f_{in}$ & $f_{out}$.

안 active low pass filter위상 검출기의 출력에 존재하는 고주파 성분을 제거한 후 출력에서 DC 전압을 생성합니다. 또한 신호를 증폭합니다.

ㅏ VCO입력이 없을 때 특정 주파수의 신호를 생성합니다. 이 주파수는 DC 전압을 적용하여 양쪽으로 이동할 수 있습니다. 따라서 주파수 편차는 저역 통과 필터의 출력에 존재하는 DC 전압에 정비례합니다.

위의 작업은 VCO 주파수가 입력 신호 주파수와 같을 때까지 발생합니다. 애플리케이션 유형에 따라 액티브 로우 패스 필터의 출력 또는 VCO의 출력을 사용할 수 있습니다. PLL은 많은 분야에서 사용됩니다.applications FM 복조기, 클록 발생기 등

PLL은 다음 중 하나에서 작동합니다. following three modes −

- 자유 실행 모드

- 캡처 모드

- 잠금 모드

처음에 PLL은 free running mode입력이 적용되지 않을 때. PLL에 어느 정도의 주파수를 갖는 입력 신호가 적용되면 VCO의 출력 신호 주파수가 변경되기 시작합니다. 이 단계에서 PLL은capture mode. VCO의 출력 신호 주파수는 입력 신호 주파수와 같을 때까지 계속 변경됩니다. 이제 PLL이 운영 중이라고합니다.lock mode.

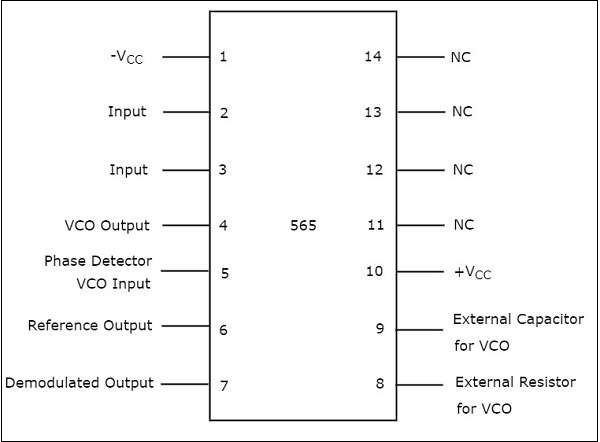

IC 565

IC 565는 가장 일반적으로 사용되는 위상 고정 루프 IC입니다. 이는 14 핀 DIP (Dual-Inline Package)입니다. 그만큼pin diagram IC 565의 다음 그림은-

각 핀의 목적은 위의 다이어그램에서 자명합니다. 14 핀 중 10 핀 (핀 번호 1 ~ 10) 만 PLL 작동에 사용됩니다. 따라서 나머지 4 개의 핀 (핀 번호 11 ~ 14)에는 NC (연결 없음)라는 레이블이 지정됩니다.

그만큼 VCO핀 번호 2와 3이 접지 될 때 IC 565의 핀 번호 4에서 출력을 생성합니다. 수학적으로 출력 주파수를 쓸 수 있습니다.$f_{out}$ VCO의.

$$f_{out}=\frac{0.25}{R_VC_V}$$

어디,

$R_{V}$ 핀 번호 8에 연결된 외부 저항입니다.

$C_{V}$ 핀 번호 9에 연결된 외부 커패시터입니다.

적절한 가치를 선택함으로써 $R_{V}$ 과 $C_{V}$, 출력 주파수를 고정 (결정) 할 수 있습니다. $f_{out}$ VCO의.

Pin numbers 4 and 5VCO의 출력이 위상 검출기의 입력 중 하나로 적용될 수 있도록 외부 와이어로 단락되어야합니다.

IC 565의 내부 저항은 $3.6K\Omega$. 커패시터 C는 핀 번호 7과 10 사이에 연결되어야합니다.low pass filter 내부 저항으로.

요구 사항에 따라 IC 565의 핀을 적절하게 구성해야합니다.

의 기능 voltage regulator입력에서 전압 변동 및 (또는) 부하 전류의 변동에 관계없이 출력에서 일정한 DC 전압을 유지하는 것입니다. 즉, 전압 조정기는 조정 된 DC 출력 전압을 생성합니다.

전압 조정기는 IC (Integrated Circuits) 형태로도 제공됩니다. 이것들은voltage regulator ICs.

전압 조정기의 유형

있습니다 two types 전압 조정기 수 −

- 고정 전압 조정기

- 조정 가능한 전압 조정기

이 장에서는 이러한 두 가지 유형의 전압 조정기에 대해 하나씩 설명합니다.

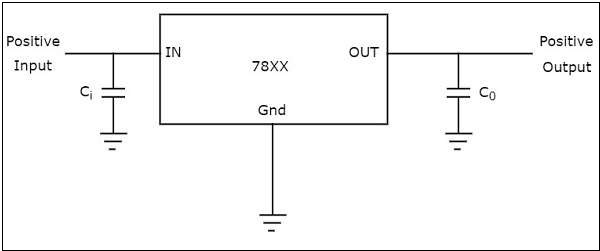

고정 전압 조정기

ㅏ fixed voltage regulator고정 된 DC 출력 전압을 생성하며 이는 양수 또는 음수입니다. 즉, 일부 고정 전압 조정기는 양의 고정 DC 전압 값을 생성하고 다른 일부는 음의 고정 DC 전압 값을 생성합니다.

78xx 전압 조정기 IC는 양의 고정 DC 전압 값을 생성하는 반면, 79xx 전압 조정기 IC는 음의 고정 DC 전압 값을 생성합니다.

작업하는 동안 다음 사항에 유의해야합니다. 78xx 과 79xx 전압 조정기 IC −

"xx"는 두 자리 숫자에 해당하며 전압 조정기 IC가 생성하는 전압의 양 (크기)을 나타냅니다.

78xx 및 79xx 전압 조정기 IC 모두 3 pins 각각과 세 번째 핀은 출력을 수집하는 데 사용됩니다.

이 두 가지 유형의 IC의 첫 번째 및 두 번째 핀의 목적은 다릅니다.

의 첫 번째 및 두 번째 핀 78xx 전압 조정기 IC는 입력과 접지를 각각 연결하는 데 사용됩니다.

의 첫 번째 및 두 번째 핀 79xx 전압 조정기 IC는 각각 접지와 입력을 연결하는 데 사용됩니다.

예

- 7805 전압 조정기 IC는 + 5V의 DC 전압을 생성합니다.

- 7905 전압 조정기 IC는 -5V의 DC 전압을 생성합니다.

다음 그림은 fixed positive voltage 필요한 연결이있는 고정 된 포지티브 전압 조정기를 사용하여 출력에서.

고정 된 포지티브 전압 레귤레이터를 보여주는 위 그림에서 입력 커패시터 C i 는 원치 않는 발진을 방지하는 데 사용되며 출력 커패시터 C 0 은 과도 응답을 개선하는 라인 필터 역할을합니다.

Note − 얻을 fixed negative voltage 적절한 연결이있는 고정 된 네거티브 전압 레귤레이터를 사용하여 출력에서.

조정 가능한 전압 조정기

조정 가능한 전압 조정기는 특정 전압 범위의 다른 값으로 조정할 수있는 DC 출력 전압을 생성합니다. 따라서 조정 가능한 전압 조정기는variable voltage regulator.

조정 가능한 전압 조정기의 DC 출력 전압 값은 양수 또는 음수 일 수 있습니다.

LM317 전압 조정기 IC

LM317 전압 조정기 IC는 사용 가능한 전압 범위에서 원하는 양의 고정 DC 전압 값을 생성하는 데 사용할 수 있습니다.

LM317 전압 조정기 IC에는 3 개의 핀이 있습니다. 첫 번째 핀은 출력 전압 조정에 사용되고 두 번째 핀은 출력 수집에 사용되며 세 번째 핀은 입력 연결에 사용됩니다.

조정 가능한 핀 (단자)에는 출력이 넓은 범위에서 변할 수있는 가변 저항이 제공됩니다.

위 그림은 일반적으로 사용되는 LM 317 전압 조정기 IC를 구동하는 조정되지 않은 전원 공급 장치를 보여줍니다. 이 IC는 1.25V ~ 37V의 조정 가능한 출력 범위에서 1.5A의 부하 전류를 공급할 수 있습니다.

모든 실제 수량은 본질적으로 아날로그입니다. 이러한 양을 전기적으로 아날로그 신호로 나타낼 수 있습니다. 안analog signal 주어진 시간 슬롯에 대해 임의의 수의 값 (변동)이있는 시변 신호입니다.

이와 대조적으로 digital signal 한 수준에서 다른 수준으로 갑자기 변하며 주어진 시간 슬롯에 대해 유한 한 수의 값 (변형) 만 갖습니다.

이 장에서는 데이터 변환기의 유형과 사양에 대해 설명합니다.

데이터 변환기의 유형

아날로그 신호로 작동 할 수있는 전자 회로를 아날로그 회로라고합니다. 마찬가지로 디지털 신호로 작동 할 수있는 전자 회로를 디지털 회로라고합니다. 데이터 변환기는 한 형식의 데이터를 다른 형식으로 변환하는 전자 회로입니다.

두 가지가있다 types of data converters −

- 아날로그-디지털 변환기

- 디지털-아날로그 변환기

아날로그 회로의 출력을 디지털 회로의 입력으로 연결하려면 그 사이에 인터페이싱 회로를 배치해야합니다. 아날로그 신호를 디지털 신호로 변환하는이 인터페이싱 회로를Analog to Digital Converter.

마찬가지로 디지털 회로의 출력을 아날로그 회로의 입력으로 연결하려면 그 사이에 인터페이싱 회로를 배치해야합니다. 디지털 신호를 아날로그 신호로 변환하는이 인터페이싱 회로를Digital to Analog Converter.

일부 아날로그-디지털 변환기는 작동을 위해 내부 블록으로 디지털-아날로그 변환기가 필요할 수 있습니다.

명세서

다음은 specifications 데이터 변환과 관련된-

- Resolution

- 변환 시간

해결

해상도는 minimum amount of change이진 (디지털) 출력으로 나타내려면 아날로그 입력 전압에 필요합니다. 디지털 출력에 사용되는 비트 수에 따라 다릅니다.

Mathematically, 해상도는 다음과 같이 나타낼 수 있습니다.

$$Resolution=\frac{1}{2^{N}}$$

여기서 'N'은 디지털 출력에 존재하는 비트 수입니다.

위의 공식에서 우리는 inverse relationship해상도와 비트 수 사이. 따라서 비트 수가 증가하면 해상도가 감소하고 그 반대의 경우도 마찬가지입니다.

Resolution 이진수와 동등한 이진수로 표현할 수있는 최대 아날로그 입력 전압의 비율로 정의 할 수도 있습니다.

Mathematically, 해상도는 다음과 같이 나타낼 수 있습니다.

$$Resolution=\frac{V_{FS}}{2^{N}-1}$$

어디,

$V_{FS}$ 풀 스케일 입력 전압 또는 최대 아날로그 입력 전압입니다.

'N'은 디지털 출력에 존재하는 비트 수입니다.

변환 시간

한 형식의 데이터 (정보)를 다른 형식의 동등한 데이터로 변환하기 위해 데이터 변환기에 필요한 시간을 다음과 같이 호출합니다. conversion time. 두 가지 유형의 데이터 변환기가 있으므로 다음과 같은 두 가지 유형의 변환 시간이 있습니다.

- 아날로그-디지털 변환 시간

- 디지털-아날로그 변환 시간

아날로그-디지털 변환기 (ADC)가 아날로그 입력 전압을 동등한 이진 (디지털) 출력으로 변환하는 데 필요한 시간은 다음과 같습니다. Analog to Digital conversion time. 디지털 출력에 사용되는 비트 수에 따라 다릅니다.

디지털-아날로그 변환기 (DAC)가 바이너리 (디지털) 입력을 동등한 아날로그 출력 전압으로 변환하는 데 필요한 시간을 다음과 같이 호출합니다. Digital to Analog conversion time. 이진 (디지털) 입력에있는 비트 수에 따라 다릅니다.

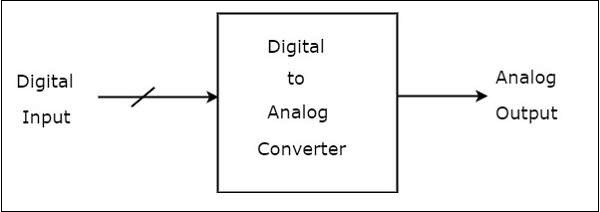

ㅏ Digital to Analog Converter (DAC)디지털 입력 신호를 아날로그 출력 신호로 변환합니다. 디지털 신호는 비트 0과 1의 조합 인 바이너리 코드로 표시됩니다.이 장에서는 디지털-아날로그 변환기에 대해 자세히 다룹니다.

그만큼 block diagram DAC의 다음 그림은-

DAC (디지털-아날로그 변환기)는 여러 이진 입력과 단일 출력으로 구성됩니다. 일반적으로number of binary inputs DAC의 2의 거듭 제곱이됩니다.

DAC 유형

있습니다 two types DAC 수

- 가중 저항 DAC

- R-2R 래더 DAC

이 섹션에서는 이러한 두 가지 유형의 DAC에 대해 자세히 설명합니다.

가중 저항 DAC

가중 저항 DAC는 다음을 사용하여 디지털 (이진) 입력과 거의 동일한 아날로그 출력을 생성합니다. binary weighted resistors반전 가산기 회로에서. 간단히 말해서, 이진 가중 저항 DAC를 가중 저항 DAC라고합니다.

그만큼 circuit diagram 3 비트 이진 가중 저항 DAC의 그림은 다음과 같습니다.

이진수의 비트는 두 값 중 하나만 가질 수 있습니다. 즉, 0 또는 1입니다.3-bit binary input 이다 $b_{2}b_{1}b_{0}$. 여기, 비트$b_{2}$ 과 $b_{0}$ 표시하다 Most Significant Bit (MSB) and Least Significant Bit (LSB) 각기.

그만큼 digital switches위 그림에 표시된대로 해당 입력 비트가 '0'과 같을 때 접지에 연결됩니다. 마찬가지로 위 그림에 표시된 디지털 스위치는 음의 기준 전압에 연결됩니다.$-V_{R}$ 해당 입력 비트가 '1'과 같을 때.

위의 회로에서 연산 증폭기의 비 반전 입력 단자는 접지에 연결됩니다. 즉, 연산 증폭기의 비 반전 입력 단자에 제로 볼트가 적용됩니다.

에 따르면 virtual short concept, opamp의 반전 입력 단자의 전압은 비 반전 입력 단자의 전압과 동일합니다. 따라서 반전 입력 단자 노드의 전압은 0 볼트가됩니다.

그만큼 nodal equation 반전 입력 터미널의 노드는 다음과 같습니다.

$$\frac{0+V_{R}b_{2}}{2^{0}R}+\frac{0+V_{R}b_{1}}{2^{1}R}+\frac{0+V_{R}b_{0}}{2^{2}R}+\frac{0-V_{0}}{R_{f}}=0$$

$$=>\frac{V_{0}}{R_{f}}=\frac{V_{R}b_{2}}{2^{0}R}+\frac{V_{R}b_{1}}{2^{1}R}+\frac{V_{R}b_{0}}{2^{2}R}$$

$$=>V_{0}=\frac{V_{R}R_{f}}{R}\left \{\frac{b_{2}}{2^{0}}+\frac{b_{1}}{2^{1}}+\frac{b_{0}}{2^{2}}\right \}$$

대체, $R=2R_{f}$ 위의 방정식에서.

$$=>V_{0}=\frac{V_{R}R_{f}}{2R_{f}}\left \{\frac{b_{2}}{2^{0}}+\frac{b_{1}}{2^{1}}+\frac{b_{0}}{2^{2}}\right \}$$

$$=>V_{0}=\frac{V_{R}}{2}\left \{\frac{b_{2}}{2^{0}}+\frac{b_{1}}{2^{1}}+\frac{b_{0}}{2^{2}}\right \}$$

위의 방정식은 output voltage equation3 비트 이진 가중 저항 DAC의. 이진 (디지털) 입력에서는 비트 수가 3 개이므로 고정 기준 전압에 대해 이진 입력을 000에서 111로 변경하여 출력 전압의 7 가지 가능한 값을 얻을 수 있습니다.$V_{R}$.

우리는 쓸 수 있습니다 generalized output voltage equation 3 비트 이진 가중 저항기 DAC의 출력 전압 방정식을 기반으로 아래에 표시된대로 N 비트 이진 가중 저항기 DAC의.

$$=>V_{0}=\frac{V_{R}}{2}\left \{ \frac{b_{N-1}}{2^{0}}+ \frac{b_{N-2}}{2^{1}}+....+\frac{b_{0}}{2^{N-1}} \right \}$$

그만큼 disadvantages 이진 가중 저항 DAC의 구성은 다음과 같습니다.

LSB 및 MSB에 해당하는 저항 값 간의 차이는 디지털 입력에 존재하는 비트 수가 증가함에 따라 증가합니다.

디지털 입력에 존재하는 비트 수가 증가함에 따라 더 정확한 저항을 설계하는 것은 어렵습니다.

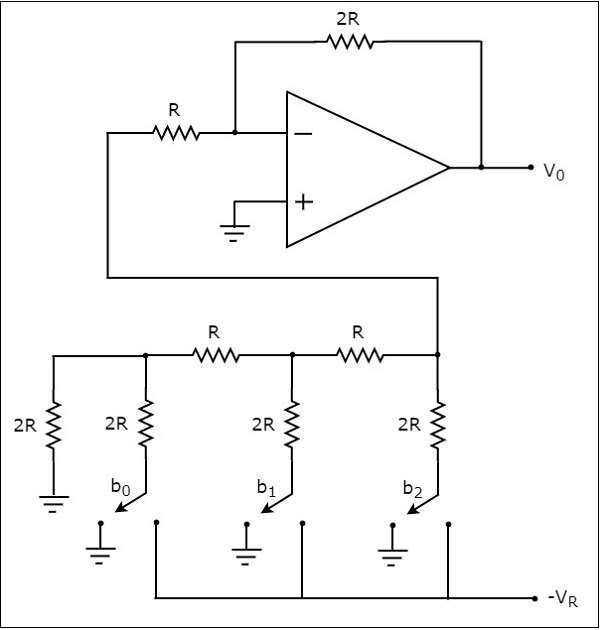

R-2R 래더 DAC

R-2R 래더 DAC는 이진 가중 저항 DAC의 단점을 극복합니다. 이름에서 알 수 있듯이 R-2R Ladder DAC는 아날로그 출력을 생성합니다. 이는 디지털 (이진) 입력과 거의 동일합니다.R-2R ladder network 반전 가산기 회로에서.

그만큼circuit diagram3 비트 R-2R 래더 DAC의 그림은 다음과 같습니다.

이진수의 비트는 두 값 중 하나만 가질 수 있습니다. 즉, 0 또는 1입니다.3-bit binary input 이다 $b_{2}b_{1}b_{0}$. 여기, 비트$b_{2}$ 과 $b_{0}$ 각각 MSB (Most Significant Bit) 및 LSB (Least Significant Bit)를 나타냅니다.

위 그림에 표시된 디지털 스위치는 해당 입력 비트가 '0'과 같을 때 접지에 연결됩니다. 마찬가지로 위 그림에 표시된 디지털 스위치는 음의 기준 전압에 연결됩니다.$-V_{R}$ when the corresponding input bits are equal to ‘1’.

It is difficult to get the generalized output voltage equation of a R-2R Ladder DAC. But, we can find the analog output voltage values of R-2R Ladder DAC for individual binary input combinations easily.

The advantages of a R-2R Ladder DAC are as follows −

R-2R Ladder DAC contains only two values of resistor: R and 2R. So, it is easy to select and design more accurate resistors.

If more number of bits are present in the digital input, then we have to include required number of R-2R sections additionally.

위의 장점으로 인해 R-2R Ladder DAC가 바이너리 가중 저항 DAC보다 선호됩니다.

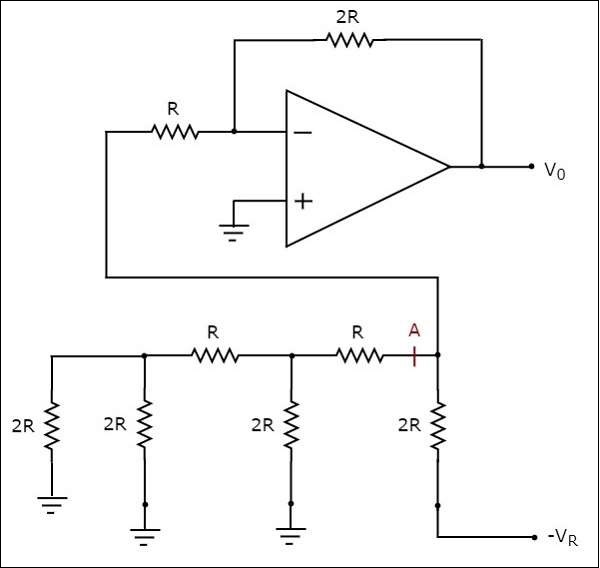

이전 장에서 두 가지 유형의 DAC에 대해 설명했습니다. 이 장에서는 R-2R 래더 DAC를 기반으로 한 예제 문제에 대해 설명합니다.

예

바이너리 입력에 대한 R-2R Ladder DAC의 아날로그 출력 전압 값을 찾아 보겠습니다. $b_{2}b_{1}b_{0}$ = 100.

회로도 및 단순화

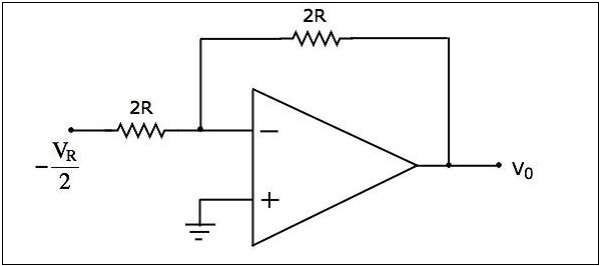

그만큼 circuit diagram 바이너리 입력일 때 3 비트 R-2R 래더 DAC의 $b_{2}b_{1}b_{0}$ = 100이 적용되면 다음 그림에 나와 있습니다.

위의 회로에서 왼쪽에 저항의 직렬 및 병렬 조합이 있습니다. point A지상과 관련하여. 따라서 전체 저항 네트워크를 저항이있는 단일 저항으로 대체 할 수 있습니다.$2R\Omega$.

그만큼 simplified circuit diagram 다음 그림에 나와 있습니다.

Thevenin의 등가 회로를 사용하여 접지와 관련하여 지점 B의 왼쪽에 연결된 네트워크 부분을 대체 할 수 있습니다. 그만큼modified circuit diagram 다음 그림에 나와 있습니다.

위의 회로에는 두 저항의 직렬 조합이 있습니다. 이 조합을 단일 저항으로 교체하십시오. 마지막circuit diagram 단순화 후 다음 그림에 표시됩니다-

이제 위의 회로도는 inverting amplifier. 입력 전압이$-\frac{V_{R}}{2}$ 볼트, 입력 저항 $2R\Omega$ 및 피드백 저항 $2R\Omega$.

그만큼 output voltage 위에 표시된 회로의-

$$V_{0}=-\frac{2R}{2R}\left(-\frac{V_{R}}{2}\right)$$

$$V_{0}=\frac{V_{R}}{2}$$

따라서 output voltage 3 비트 R-2R 래더 DAC의 $\frac{V_{R}}{2}$ 바이너리 입력의 경우 볼트, $b_{2}b_{1}b_{0}$ = 100.

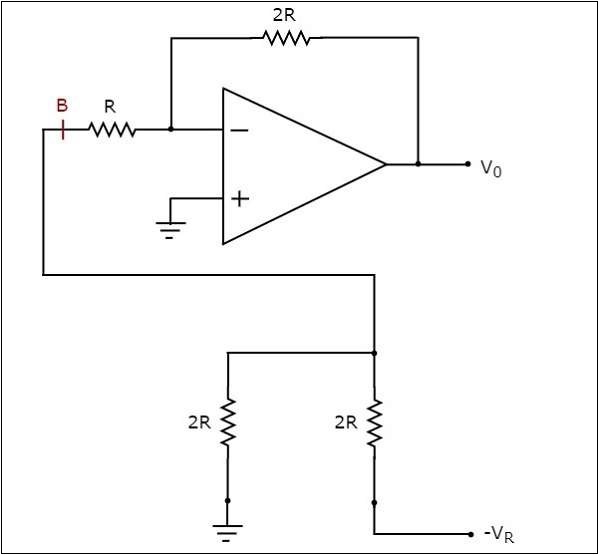

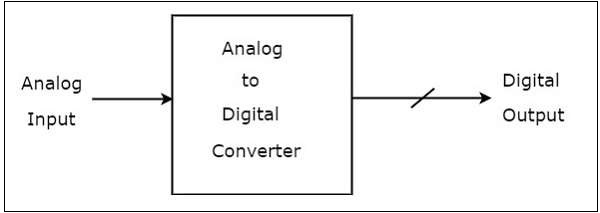

아날로그-디지털 변환기 (ADC)아날로그 신호를 디지털 신호로 변환합니다. 디지털 신호는 비트 0과 1의 조합 인 이진 코드로 표시됩니다.

그만큼 block diagram ADC의 다음 그림은-

위 그림에서 아날로그-디지털 변환기가 (ADC)단일 아날로그 입력과 많은 이진 출력으로 구성됩니다. 일반적으로 ADC의 바이너리 출력 수는 2의 거듭 제곱이됩니다.

있습니다 two typesADC 수 : 직접 형 ADC 및 간접 형 ADC. 이 장에서는 Direct type ADC에 대해 자세히 설명합니다.

ADC가 아날로그 입력과 비교하기 위해 내부적으로 생성 된 등가 디지털 (바이너리) 코드를 사용하여 아날로그에서 디지털로 직접 변환을 수행하면 다음과 같이 호출됩니다. Direct type ADC.

다음은 examples 직접 형 ADC의-

- 카운터 형 ADC

- 연속 근사 ADC

- 플래시 유형 ADC

이 섹션에서는 이러한 Direct 유형 ADC에 대해 자세히 설명합니다.

카운터 형 ADC

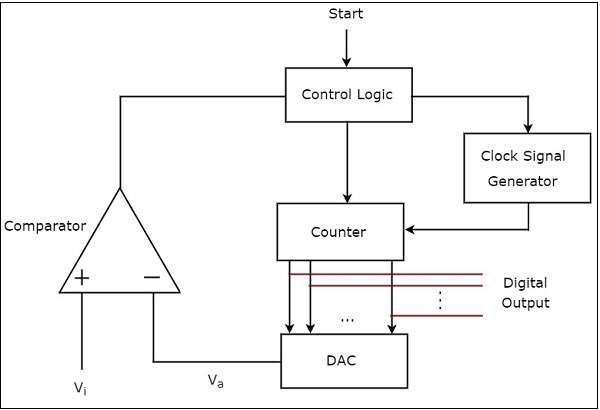

ㅏ counter type ADC 내부적으로 카운터 작동을 사용하여 아날로그 입력과 거의 동일한 디지털 출력을 생성합니다.

그만큼 block diagram 카운터 유형 ADC의 그림은 다음과 같습니다.

카운터 유형 ADC는 주로 클럭 신호 생성기, 카운터, DAC, 비교기 및 제어 로직의 5 개 블록으로 구성됩니다.

그만큼 working 카운터 타입 ADC의 다음과 같습니다-

그만큼 control logic 시작 명령 신호를 수신하면 카운터를 재설정하고 클럭 펄스를 카운터로 보내기 위해 클럭 신호 생성기를 활성화합니다.

그만큼 counter모든 클럭 펄스에 대해 1 씩 증가하며 그 값은 이진 (디지털) 형식입니다. 이 카운터의 출력은 DAC의 입력으로 적용됩니다.

DAC카운터의 출력 인 수신 된 이진 (디지털) 입력을 아날로그 출력으로 변환합니다. 비교기는이 아날로그 값을 비교합니다.$V_{a}$ 외부 아날로그 입력 값으로 $V_{i}$.

그만큼 output of comparator 될거야 ‘1’보다 큽니다. 위의 두 단계에서 언급 한 동작은 제어 로직이 비교기의 출력에서 '1'을 수신하는 한 계속됩니다.

그만큼 output of comparator 될거야 ‘0’ 언제 $V_{i}$ 보다 작거나 같음 $V_{a}$. 따라서 제어 로직은 비교기의 출력에서 '0'을받습니다. 그런 다음 제어 로직은 클럭 신호 생성기를 비활성화하여 클럭 펄스를 카운터로 보내지 않습니다.

이때 카운터의 출력은 다음과 같이 표시됩니다. digital output. 해당 외부 아날로그 입력 값과 거의 동일합니다.$V_{i}$.

연속 근사 ADC

ㅏ successive approximation type ADC 내부적으로 연속 근사 기법을 사용하여 아날로그 입력과 거의 동일한 디지털 출력을 생성합니다.

그만큼 block diagram 연속 근사 ADC의 다음 그림에 나와 있습니다.

연속 근사 ADC는 주로 클럭 신호 생성기, SAR (Successive Approximation Register), DAC, 비교기 및 제어 로직의 5 개 블록으로 구성됩니다.

그만큼 working 연속 근사 ADC의 다음과 같습니다-

그만큼 control logic SAR의 모든 비트를 재설정하고 시작 명령 신호를 수신했을 때 SAR에 클럭 펄스를 보내기 위해 클럭 신호 생성기를 활성화합니다.

이진 (디지털) 데이터 SAR비교기의 출력을 기반으로 모든 클럭 펄스에 대해 업데이트됩니다. SAR의 출력은 DAC의 입력으로 적용됩니다.

DAC 수신 된 디지털 입력 (SAR의 출력)을 아날로그 출력으로 변환합니다. 비교기는이 아날로그 값을 비교합니다.$V_{a}$ 외부 아날로그 입력 값으로 $V_{i}$.

그만큼 output of a comparator 한 '1'이 될 것입니다 $V_{i}$ 보다 큼 $V_{a}$. 마찬가지로 비교기의 출력은 '0'이됩니다.$V_{i}$ 보다 작거나 같음 $V_{a}$.

위 단계에서 언급 한 작업은 디지털 출력이 유효한 출력이 될 때까지 계속됩니다.

디지털 출력은 해당 외부 아날로그 입력 값과 거의 동일 할 때 유효한 출력이됩니다. $V_{i}$.

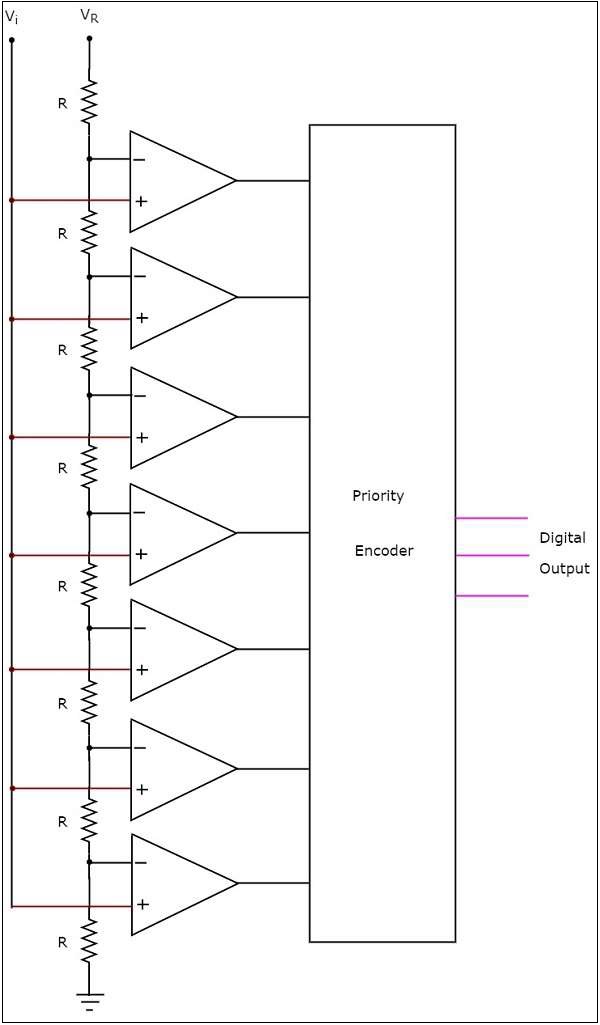

플래시 유형 ADC

ㅏ flash type ADC즉시 해당 아날로그 입력에 대해 동등한 디지털 출력을 생성합니다. 따라서 플래시 유형 ADC는 가장 빠른 ADC입니다.

그만큼 circuit diagram 3 비트 플래시 타입 ADC의 그림은 다음과 같습니다.

3 비트 플래시 유형 ADC는 전압 분배기 네트워크, 7 개의 비교기 및 우선 순위 인코더로 구성됩니다.

그만큼 working 3 비트 플래시 형 ADC의 구성은 다음과 같습니다.

그만큼 voltage divider network8 개의 동일한 저항을 포함합니다. 기준 전압$V_{R}$지상과 관련하여 전체 네트워크에 적용됩니다. 접지와 관련하여 아래에서 위로 각 저항의 전압 강하는 다음의 정수 배수 (1 ~ 8)가됩니다.$\frac{V_{R}}{8}$.

외부 input voltage $V_{i}$모든 비교기의 비 반전 단자에 적용됩니다. 접지와 관련하여 아래에서 위로 각 저항의 전압 강하는 아래에서 위로 비교기의 반전 단자에 적용됩니다.

한 번에 모든 비교기는 외부 입력 전압을 각각의 다른 입력 단자에 존재하는 전압 강하와 비교합니다. 즉, 비교 작업은 각 비교기에서 수행됩니다.parallelly.

그만큼 output of the comparator 한 '1'이 될 것입니다 $V_{i}$각각의 다른 입력 단자에 존재하는 전압 강하보다 큽니다. 마찬가지로 비교기의 출력은 '0'이됩니다.$V_{i}$ 각각의 다른 입력 단자에 존재하는 전압 강하보다 작거나 같습니다.

비교기의 모든 출력은 입력으로 연결됩니다. priority encoder이 우선 순위 인코더는 '1'이있는 높은 우선 순위 입력에 해당하는 바이너리 코드 (디지털 출력)를 생성합니다.

따라서 우선 순위 인코더의 출력은 이진 등가물 일뿐입니다. (digital output) 외부 아날로그 입력 전압, $V_{i}$.

플래시 타입 ADC는 아날로그 입력을 디지털 데이터로 변환하는 속도가 매우 높아야하는 애플리케이션에 사용됩니다.

이전 장에서 우리는 ADC가 무엇인지와 Direct 타입 ADC의 예에 대해 논의했습니다. 이 장에서는 간접 형 ADC에 대해 설명합니다.

ADC가 간접적 인 방법으로 아날로그에서 디지털로의 변환을 수행하는 경우이를 Indirect type ADC. 일반적으로 먼저 아날로그 입력을 시간 (또는 주파수)의 선형 함수로 변환 한 다음 디지털 (이진) 출력을 생성합니다.

듀얼 슬로프 ADC가 최고입니다. example간접 유형 ADC의. 이 장에서는 이에 대해 자세히 설명합니다.

듀얼 슬로프 ADC

이름에서 알 수 있듯이 dual slope ADC 두 개의 (이중) 슬로프 기술을 사용하여 해당 아날로그 입력에 대해 동등한 디지털 출력을 생성합니다.

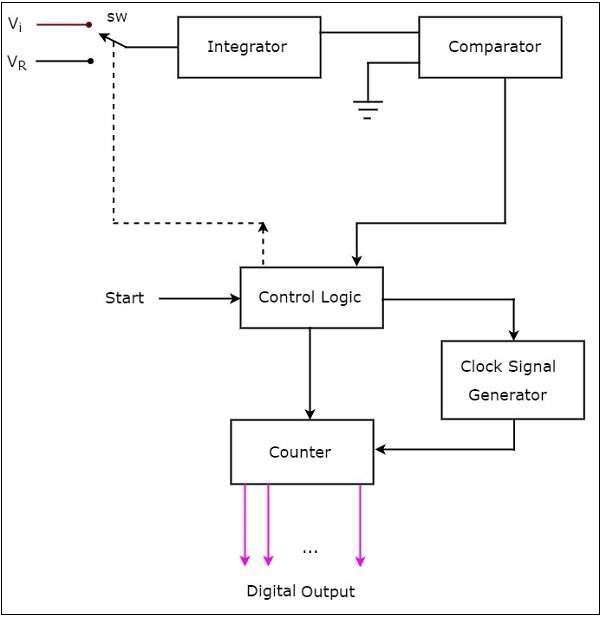

그만큼 block diagram 듀얼 슬로프 ADC의 그림은 다음과 같습니다.

듀얼 슬로프 ADC는 주로 적분기, 비교기, 클록 신호 생성기, 제어 로직 및 카운터의 5 개 블록으로 구성됩니다.

그만큼 working 듀얼 슬로프 ADC는 다음과 같습니다.

그만큼 control logic 카운터를 재설정하고 시작 명령 신호를 받으면 클럭 펄스를 카운터로 보내기 위해 클럭 신호 생성기를 활성화합니다.

제어 로직이 스위치를 밀다 sw 에 연결하기 위해 external analog input voltage $V_{i}$, 시작 명령 신호를 받으면. 이 입력 전압은 적분기에 적용됩니다.

의 출력 integrator 비교기의 두 입력 중 하나에 연결되고 비교기의 다른 입력은 접지에 연결됩니다.

Comparator 적분기의 출력을 0 볼트 (접지)와 비교하여 제어 로직에 적용되는 출력을 생성합니다.

그만큼 counter모든 클럭 펄스에 대해 1 씩 증가하며 그 값은 이진 (디지털) 형식입니다. 최대 카운트 값에 도달 한 후 증가하면 제어 로직에 오버플로 신호를 생성합니다. 이 순간 카운터의 모든 비트는 0 만 가지게됩니다.

이제 제어 로직이 스위치를 sw 에 연결하기 위해 negative reference 전압 $-V_{ref}$. 이 음의 기준 전압은 적분기에 적용됩니다. 0이 될 때까지 커패시터에 저장된 전하를 제거합니다.

이 순간 비교기의 두 입력은 모두 0 볼트입니다. 따라서 비교기는 제어 로직에 신호를 보냅니다. 이제 제어 로직은 클록 신호 생성기를 비활성화하고 카운터 값을 유지 (유지)합니다. 그만큼counter value 외부 아날로그 입력 전압에 비례합니다.

이때 카운터의 출력은 다음과 같이 표시됩니다. digital output. 해당 외부 아날로그 입력 값과 거의 동일합니다.$V_{i}$.

듀얼 슬로프 ADC는 애플리케이션에서 사용됩니다. accuracy 아날로그 입력을 동등한 디지털 (이진) 데이터로 변환하는 동안 더 중요합니다.