Circuitos Sequenciais

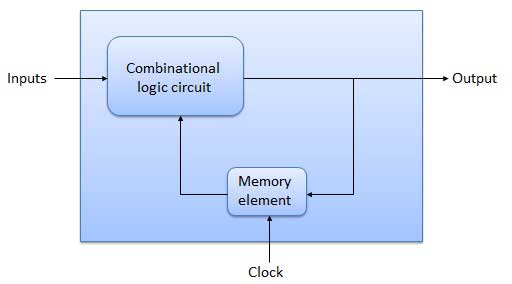

O circuito combinacional não usa nenhuma memória. Portanto, o estado anterior da entrada não tem nenhum efeito sobre o estado atual do circuito. Mas o circuito sequencial tem memória, então a saída pode variar com base na entrada. Este tipo de circuito usa entrada, saída anterior, relógio e um elemento de memória.

Diagrama de bloco

Chinelo de dedo

Flip-flop é um circuito sequencial que geralmente faz uma amostragem de suas entradas e altera suas saídas apenas em instantes específicos de tempo e não continuamente. Diz-se que o flip-flop é sensível à borda ou acionado por borda em vez de ser acionado por nível como travas.

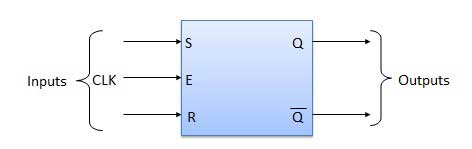

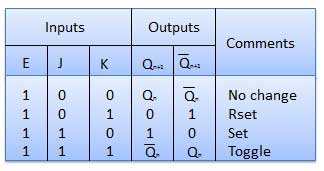

SR Flip Flop

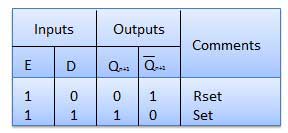

É basicamente uma trava SR usando portas NAND com um enableentrada. Também é chamado de SR-FF acionado por nível. Para isso, o circuito na saída ocorrerá se e somente se a entrada de habilitação (E) for ativada. Em suma, este circuito irá operar como uma trava SR se E = 1, mas não há nenhuma mudança na saída se E = 0.

Diagrama de bloco

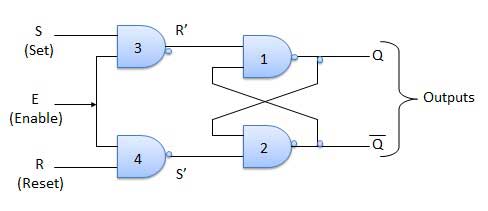

Diagrama de circuito

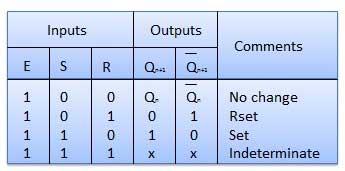

Mesa da Verdade

Operação

| SN | Doença | Operação |

|---|---|---|

| 1 | S = R = 0 : No change | Se S = R = 0, então a saída das portas NAND 3 e 4 são forçadas a se tornar 1. Conseqüentemente, R 'e S' serão ambos iguais a 1. Visto que S 'e R' são a entrada da trava SR básica usando portas NAND, não haverá mudança no estado das saídas. |

| 2 | S = 0, R = 1, E = 1 | Como S = 0, a saída de NAND-3, isto é, R '= 1 e E = 1, a saída de NAND-4, isto é, S' = 0. Portanto, Q n + 1 = 0 e Q n + 1 bar = 1. Esta é a condição de reinicialização. |

| 3 | S = 1, R = 0, E = 1 | Saída de NAND-3, ou seja, R '= 0 e saída de NAND-4, ou seja, S' = 1. Portanto, a saída do latch SR NAND é Q n + 1 = 1 e Q n + 1 bar = 0. Esta é a condição de reinicialização. |

| 4 | S = 1, R = 1, E = 1 | Como S = 1, R = 1 e E = 1, a saída das portas NAND 3 e 4 são ambas 0, isto é, S '= R' = 0. Daí o Race a condição ocorrerá na trava NAND básica. |

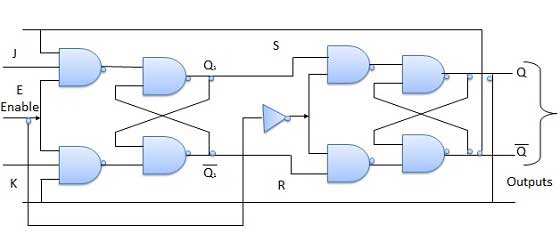

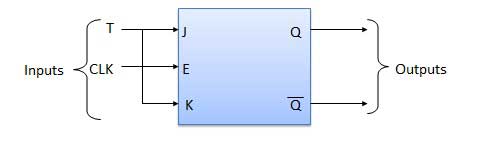

Master Slave JK Flip Flop

O escravo mestre JK FF é uma cascata de dois SR FF com feedback da saída do segundo para a entrada do primeiro. Master é um nível positivo acionado. Porém, devido à presença do inversor na linha do clock, o escravo responderá ao nível negativo. Portanto, quando o clock = 1 (nível positivo), o mestre está ativo e o escravo está inativo. Já quando clock = 0 (nível baixo) o escravo está ativo e o mestre inativo.

Diagrama de circuito

Mesa da Verdade

Operação

| SN | Doença | Operação |

|---|---|---|

| 1 | J = K = 0 (No change) | Quando clock = 0, o escravo se torna ativo e o mestre inativo. Mas, como as entradas S e R não mudaram, as saídas escravas também permanecerão inalteradas. Portanto, as saídas não mudarão se J = K = 0. |

| 2 | J = 0 and K = 1 (Reset) | Clock = 1 - Mestre ativo, escravo inativo. Portanto, as saídas do mestre tornam-se Q 1 = 0 e Q 1 bar = 1. Isso significa S = 0 e R = 1. Clock = 0 - Slave ativo, mestre inativo. Portanto, as saídas do escravo tornam-se Q = 0 e Q bar = 1. Novamente clock = 1 - Mestre ativo, escravo inativo. Portanto, mesmo com as saídas alteradas Q = 0 e Q bar = 1 realimentadas para o mestre, sua saída será Q1 = 0 e Q1 bar = 1. Isso significa S = 0 e R = 1. Portanto, com clock = 0 e o escravo se tornando ativo, as saídas do escravo permanecerão Q = 0 e Q bar = 1. Assim, obtemos uma saída estável do escravo mestre. |

| 3 | J = 1 and K = 0 (Set) | Clock = 1 - Mestre ativo, escravo inativo. Portanto, as saídas do mestre tornam-se Q 1 = 1 e Q 1 bar = 0. Isso significa S = 1 e R = 0. Clock = 0 - Slave ativo, mestre inativo. Portanto, as saídas do escravo tornam-se Q = 1 e Q bar = 0. Novamente clock = 1 - então pode-se mostrar que as saídas do escravo são estabilizadas em Q = 1 e Q bar = 0. |

| 4 | J = K = 1 (Toggle) | Clock = 1 - Mestre ativo, escravo inativo. As saídas do mestre serão alternadas. Portanto, S e R também serão invertidos. Clock = 0 - Slave ativo, mestre inativo. As saídas do escravo serão alternadas. Essas saídas alteradas são retornadas às entradas principais. Mas como clock = 0, o mestre ainda está inativo. Portanto, ele não responde a essas saídas alteradas. Isso evita a alternância múltipla que leva à condição de corrida ao redor. O flip-flop mestre escravo evitará a condição de corrida ao redor. |

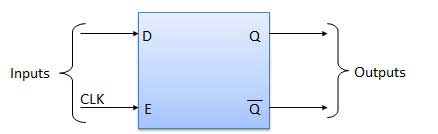

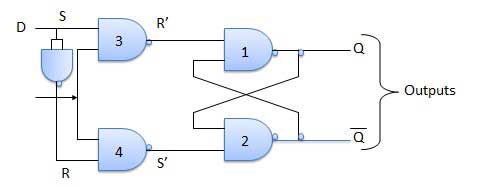

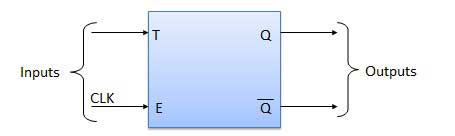

Delay Flip Flop / D Flip Flop

Delay Flip Flop ou D Flip Flop é o latch SR simples com um inversor NAND conectado entre as entradas S e R. Possui apenas uma entrada. Os dados de entrada aparecem na saída após algum tempo. Devido a esse atraso de dados entre i / p e o / p, ele é chamado de flip flop de atraso. S e R serão complementos um do outro devido ao inversor NAND. Portanto, S = R = 0 ou S = R = 1, essas condições de entrada nunca aparecerão. Este problema é evitado pelas condições SR = 00 e SR = 1.

Diagrama de bloco

Diagrama de circuito

Mesa da Verdade

Operação

| SN | Doença | Operação |

|---|---|---|

| 1 | E = 0 | A trava está desativada. Portanto, nenhuma mudança na produção. |

| 2 | E = 1 and D = 0 | Se E = 1 e D = 0, então S = 0 e R = 1. Portanto, independentemente do estado atual, o próximo estado é Q n + 1 = 0 e Q n + 1 bar = 1. Esta é a condição de reinicialização. |

| 3 | E = 1 and D = 1 | Se E = 1 e D = 1, então S = 1 e R = 0. Isso definirá a trava e Q n + 1 = 1 e Q n + 1 bar = 0 independentemente do estado atual. |

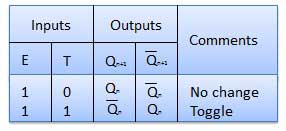

Alternar flip-flop / T flip-flop

O flip-flop alternado é basicamente um flip-flop JK com terminais J e K permanentemente conectados juntos. Tem apenas entrada denotada porTconforme mostrado no Diagrama de Símbolos. O símbolo para flip-flop T disparado por borda positiva é mostrado no Diagrama de Bloco.

Diagrama de Símbolos

Diagrama de bloco

Mesa da Verdade

Operação

| SN | Doença | Operação |

|---|---|---|

| 1 | T = 0, J = K = 0 | A barra de saída Q e Q não muda |

| 2 | T = 1, J = K = 1 | A saída irá alternar correspondendo a cada borda de ataque do sinal de clock. |