Mạch kỹ thuật số - Hướng dẫn nhanh

Nếu cơ số hoặc cơ số của một hệ thống số là 'r', thì các số hiện diện trong hệ thống số đó nằm trong khoảng từ 0 đến r-1. Tổng số có trong hệ thống số đó là 'r'. Vì vậy, chúng ta sẽ nhận được các hệ thống số khác nhau, bằng cách chọn các giá trị của cơ số lớn hơn hoặc bằng hai.

Trong chương này, chúng ta hãy thảo luận về popular number systemsvà cách biểu diễn một số trong hệ thống số tương ứng. Các hệ thống số sau đây được sử dụng phổ biến nhất.

- Hệ thống số thập phân

- Hệ thống số nhị phân

- Hệ thống số bát phân

- Hệ thống số thập lục phân

Hệ thống số thập phân

Các base hoặc cơ số của hệ thống số thập phân là 10. Vì vậy, các số từ 0 đến 9 được sử dụng trong hệ thống số này. Phần của số nằm ở bên trái củadecimal pointđược gọi là phần nguyên. Tương tự, một phần của số nằm ở bên phải của dấu thập phân được gọi là phần phân số.

Trong hệ thống số này, các vị trí liên tiếp ở bên trái của dấu thập phân có trọng số là 10 0 , 10 1 , 10 2 , 10 3 , v.v. Tương tự, các vị trí liên tiếp ở bên phải của dấu thập phân có trọng số là 10 -1 , 10 -2 , 10 -3 , v.v. Điều đó có nghĩa là, mỗi vị trí có trọng lượng cụ thể, đó làpower of base 10

Thí dụ

Xem xét decimal number 1358.246. Phần nguyên của số này là 1358 và phần thập phân của số này là 0,246. Các chữ số 8, 5, 3, 1 có trọng số lần lượt là 100, 101, 10 2 và 10 3 . Tương tự, các chữ số 2, 4, 6 có trọng số lần lượt là 10 -1 , 10 -2 và 10 -3 .

Mathematically, chúng ta có thể viết nó là

1358.246 = (1 × 10 3 ) + (3 × 10 2 ) + (5 × 10 1 ) + (8 × 10 0 ) + (2 × 10 -1 ) +

(4 × 10 -2 ) + (6 × 10 -3 )

Sau khi đơn giản hóa các số hạng bên phải, chúng ta sẽ nhận được số thập phân, nằm ở bên trái.

Hệ thống số nhị phân

Tất cả các mạch và hệ thống kỹ thuật số đều sử dụng hệ thống số nhị phân này. Cácbase hoặc cơ số của hệ thống số này là 2. Vì vậy, các số 0 và 1 được sử dụng trong hệ thống số này.

Một phần của con số, nằm ở bên trái của binary pointđược gọi là phần nguyên. Tương tự, một phần của số, nằm ở bên phải của điểm nhị phân được gọi là phần phân số.

Trong hệ thống số này, các vị trí liên tiếp ở bên trái của điểm nhị phân có trọng số là 2 0 , 2 1 , 2 2 , 2 3 , v.v. Tương tự, các vị trí liên tiếp ở bên phải của điểm nhị phân có trọng số là 2 -1 , 2 -2 , 2 -3 , v.v. Điều đó có nghĩa là, mỗi vị trí có trọng lượng cụ thể, đó làpower of base 2.

Thí dụ

Xem xét binary number 1101.011. Phần nguyên của số này là 1101 và phần thập phân của số này là 0,011. Các chữ số 1, 0, 1 và 1 của phần nguyên có trọng số lần lượt là 2 0 , 2 1 , 2 2 , 2 3 . Tương tự, các chữ số 0, 1 và 1 của phần phân số có trọng số lần lượt là 2 -1 , 2 -2 , 2 -3 .

Mathematically, chúng ta có thể viết nó là

1101.011 = (1 × 2 3 ) + (1 × 2 2 ) + (0 × 2 1 ) + (1 × 2 0 ) + (0 × 2 -1 ) +

(1 × 2 -2 ) + (1 × 2 -3 )

Sau khi đơn giản hóa các thuật ngữ bên tay phải, chúng ta sẽ nhận được một số thập phân, tương đương với số nhị phân ở bên tay trái.

Hệ thống số bát phân

Các base hoặc cơ số của hệ thống số bát phân là 8. Vì vậy, các số từ 0 đến 7 được sử dụng trong hệ thống số này. Phần của số nằm ở bên trái củaoctal pointđược gọi là phần nguyên. Tương tự, phần của số nằm ở bên phải của dấu bát phân được gọi là phần phân số.

Trong hệ thống số này, các vị trí liên tiếp bên trái của dấu bát phân có trọng số là 8 0 , 8 1 , 8 2 , 8 3 , v.v. Tương tự, các vị trí liên tiếp bên phải của bát phân có trọng số là 8 -1 , 8 -2 , 8 -3 , v.v. Điều đó có nghĩa là, mỗi vị trí có trọng lượng cụ thể, đó làpower of base 8.

Thí dụ

Xem xét octal number 1457.236. Phần nguyên của số này là 1457 và phần thập phân của số này là 0,236. Các chữ số 7, 5, 4, 1 có trọng số lần lượt là 8 0 , 8 1 , 8 2 và 8 3 . Tương tự, các chữ số 2, 3, 6 có trọng số lần lượt là 8 -1 , 8 -2 , 8 -3 .

Mathematically, chúng ta có thể viết nó là

1457.236 = (1 × 8 3 ) + (4 × 8 2 ) + (5 × 8 1 ) + (7 × 8 0 ) + (2 × 8 -1 ) +

(3 × 8 -2 ) + (6 × 8 -3 )

Sau khi đơn giản hóa các thuật ngữ bên tay phải, chúng ta sẽ nhận được một số thập phân, tương đương với số bát phân ở bên tay trái.

Hệ thống số thập lục phân

Các base hoặc cơ số của hệ thống số thập phân Hexa là 16. Vì vậy, các số từ 0 đến 9 và các chữ cái từ A đến F được sử dụng trong hệ thống số này. Tương đương thập phân của các chữ số thập lục phân từ A đến F là 10 đến 15.

Một phần của con số, nằm ở bên trái của hexadecimal pointđược gọi là phần nguyên. Tương tự, một phần của số nằm ở bên phải của dấu thập phân Hexa được gọi là phần phân số.

Trong hệ thống số này, các vị trí liên tiếp ở bên trái của dấu phẩy thập lục phân có trọng số là 16 0 , 16 1 , 16 2 , 16 3 , v.v. Tương tự, các vị trí liên tiếp ở bên phải của dấu thập lục phân có trọng số là 16 -1 , 16 -2 , 16 -3 , v.v. Điều đó có nghĩa là, mỗi vị trí có trọng lượng cụ thể, đó làpower of base 16.

Thí dụ

Xem xét Hexa-decimal number 1A05.2C4. Phần nguyên của số này là 1A05 và phần thập phân của số này là 0,2C4. Các chữ số 5, 0, A và 1 có trọng số lần lượt là 16 0 , 16 1 , 16 2 và 16 3 . Tương tự, các chữ số 2, C, 4 có trọng số lần lượt là 16 -1 , 16 -2 và 16 -3 .

Mathematically, chúng ta có thể viết nó là

1A05.2C4 = (1 × 16 3 ) + (10 × 16 2 ) + (0 × 16 1 ) + (5 × 16 0 ) + (2 × 16 -1 ) +

(12 × 16 -2 ) + (4 × 16 -3 )

Sau khi đơn giản hóa các thuật ngữ bên tay phải, chúng ta sẽ nhận được một số thập phân, tương đương với số thập phân Hexa ở bên tay trái.

Trong chương trước, chúng ta đã thấy bốn hệ thống số nổi bật. Trong chương này, chúng ta hãy chuyển đổi các số từ hệ thống số này sang hệ thống số khác để tìm giá trị tương đương.

Chuyển đổi số thập phân sang các cơ sở khác

Nếu số thập phân chứa cả phần nguyên và phần phân số, thì chuyển đổi riêng lẻ cả hai phần của số thập phân thành cơ số khác. Làm theo các bước sau để chuyển đổi số thập phân thành số tương đương của bất kỳ cơ số 'r' nào.

Làm division phần nguyên của số thập phân và successive quotientsvới cơ số 'r' và ghi lại các phần còn lại cho đến khi thương số bằng 0. Xem xét các phần dư theo thứ tự ngược lại để nhận phần nguyên của số tương đương của cơ số 'r'. Điều đó có nghĩa là, phần dư đầu tiên và cuối cùng biểu thị chữ số có nghĩa nhỏ nhất và chữ số có nghĩa nhất tương ứng.

Làm multiplication phần thập phân của số thập phân và successive fractionsvới cơ số 'r' và ghi lại giá trị thực hiện cho đến khi kết quả bằng 0 hoặc số chữ số tương đương mong muốn đạt được. Hãy xem xét chuỗi thực hiện bình thường để nhận được phần phân số của số cơ sở 'r' tương đương.

Chuyển đổi thập phân sang nhị phân

Hai loại hoạt động sau đây diễn ra, trong khi chuyển đổi số thập phân thành số nhị phân tương đương của nó.

- Phép chia phần nguyên và các thương liên tiếp với cơ số 2.

- Phép nhân một phần phân số và liên tiếp các phân số với cơ số 2.

Example

Xem xét decimal number 58.25. Ở đây, phần nguyên là 58 và phần phân số là 0,25.

Step 1 - Phép chia 58 và các thương liên tiếp với cơ số 2.

| Hoạt động | Thương số | Phần còn lại |

|---|---|---|

| 58/2 | 29 | 0 (LSB) |

| 29/2 | 14 | 1 |

| 14/2 | 7 | 0 |

| 7/2 | 3 | 1 |

| 3/2 | 1 | 1 |

| 1/2 | 0 | 1(MSB) |

⇒ (58) 10 = (111010) 2

Do đó, integer part của số nhị phân tương đương là 111010.

Step 2 - Phép nhân 0,25 và các phân số liên tiếp với cơ số 2.

| Hoạt động | Kết quả | Mang |

|---|---|---|

| 0,25 x 2 | 0,5 | 0 |

| 0,5 x 2 | 1,0 | 1 |

| - | 0,0 | - |

⇒ (.25) 10 = (.01) 2

Do đó, fractional part của số nhị phân tương đương là .01

⇒ (58,25) 10 = (111010,01) 2

Do đó, binary equivalent của số thập phân 58,25 là 111010,01.

Chuyển đổi thập phân sang bát phân

Hai loại hoạt động sau đây diễn ra, trong khi chuyển đổi số thập phân thành số bát phân tương đương của nó.

Phép chia phần nguyên và các thương liên tiếp với cơ số 8.

Phép nhân một phần phân số và các phân số liên tiếp với cơ số 8.

Example

Xem xét decimal number 58.25. Ở đây, phần nguyên là 58 và phần phân số là 0,25.

Step 1 - Phép chia 58 và các thương liên tiếp với cơ số 8.

| Hoạt động | Thương số | Phần còn lại |

|---|---|---|

| 58/8 | 7 | 2 |

| 7/8 | 0 | 7 |

⇒ (58) 10 = (72) 8

Do đó, integer part của số bát phân tương đương là 72.

Step 2 - Phép nhân 0,25 và các phân số liên tiếp với cơ số 8.

| Hoạt động | Kết quả | Mang |

|---|---|---|

| 0,25 x 8 | 2,00 | 2 |

| - | 0,00 | - |

⇒ (.25) 10 = (.2) 8

Do đó, fractional part của số bát phân tương đương là .2

⇒ (58,25) 10 = (72,2) 8

Do đó, octal equivalent của số thập phân 58,25 là 72,2.

Chuyển đổi thập phân sang thập lục phân

Hai loại hoạt động sau đây diễn ra, trong khi chuyển đổi số thập phân thành số thập lục phân tương đương của nó.

- Phép chia phần nguyên và các thương liên tiếp với cơ số 16.

- Phép nhân một phần phân số và các phân số liên tiếp với cơ số 16.

Example

Xem xét decimal number 58.25. Ở đây, phần nguyên là 58 và phần thập phân là 0,25.

Step 1 - Phép chia 58 và các thương liên tiếp với cơ số 16.

| Hoạt động | Thương số | Phần còn lại |

|---|---|---|

| 58/16 | 3 | 10 = A |

| 16/3 | 0 | 3 |

⇒ (58) 10 = (3A) 16

Do đó, integer part của số thập phân Hexa tương đương là 3A.

Step 2 - Nhân 0,25 và các phân số liên tiếp với cơ số 16.

| Hoạt động | Kết quả | Mang |

|---|---|---|

| 0,25 x 16 | 4,00 | 4 |

| - | 0,00 | - |

⇒ (.25) 10 = (.4) 16

Do đó, fractional part của số thập phân Hexa tương đương là .4.

⇒(58.25)10 = (3A.4)16

Do đó, Hexa-decimal equivalent của số thập phân 58,25 là 3A,4.

Số nhị phân sang chuyển đổi cơ sở khác

Quá trình chuyển đổi một số từ hệ nhị phân sang hệ thập phân khác với quá trình chuyển đổi một số nhị phân sang các cơ số khác. Bây giờ, chúng ta hãy thảo luận về việc chuyển đổi lần lượt một số nhị phân sang hệ thập phân, bát phân và hệ thập phân Hexa.

Chuyển đổi nhị phân sang thập phân

Để chuyển một số nhị phân thành số thập phân tương đương của nó, trước tiên hãy nhân các bit của số nhị phân với trọng số vị trí tương ứng và sau đó cộng tất cả các tích đó.

Example

Xem xét binary number 1101.11.

Mathematically, chúng ta có thể viết nó là

(1101.11) 2 = (1 × 2 3 ) + (1 × 2 2 ) + (0 × 2 1 ) + (1 × 2 0 ) + (1 × 2 -1 ) +

(1 × 2 -2 )

⇒ (1101,11) 2 = 8 + 4 + 0 + 1 + 0,5 + 0,25 = 13,75

⇒ (1101,11) 2 = (13,75) 10

Do đó, decimal equivalent của số nhị phân 1101.11 là 13,75.

Chuyển đổi nhị phân sang bát phân

Chúng ta biết rằng cơ số của hệ số nhị phân và bát phân lần lượt là 2 và 8. Ba bit của số nhị phân tương đương với một chữ số bát phân, vì 2 3 = 8.

Làm theo hai bước sau để chuyển đổi một số nhị phân thành số bát phân tương đương của nó.

Bắt đầu từ điểm nhị phân và tạo các nhóm 3 bit ở cả hai phía của điểm nhị phân. Nếu một hoặc hai bit ít hơn trong khi tạo nhóm 3 bit, thì hãy bao gồm số lượng không cần thiết ở các cạnh cực.

Viết các chữ số bát phân tương ứng với mỗi nhóm 3 bit.

Example

Xem xét binary number 101110.01101.

Step 1 - Lập nhóm 3 bit ở cả hai phía của điểm nhị phân.

101 110.011 01

Ở đây, ở phía bên phải của điểm nhị phân, nhóm cuối cùng chỉ có 2 bit. Vì vậy, hãy bao gồm một số 0 ở phía cực để làm cho nó thành nhóm 3 bit.

⇒ 101 110.011 010

Step 2 - Viết các chữ số bát phân tương ứng với mỗi nhóm 3 bit.

⇒ (101 110.011 010) 2 = (56.32) 8

Do đó, octal equivalent của số nhị phân 101110.01101 là 56,32.

Chuyển đổi từ nhị phân sang thập lục phân

Chúng ta biết rằng cơ số của hệ số nhị phân và hệ thập phân Hexa lần lượt là 2 và 16. Bốn bit của số nhị phân tương đương với một chữ số thập phân Hexa, vì 2 4 = 16.

Làm theo hai bước sau để chuyển đổi một số nhị phân thành số thập phân Hexa tương đương của nó.

Bắt đầu từ điểm nhị phân và tạo các nhóm 4 bit ở cả hai phía của điểm nhị phân. Nếu một số bit ít hơn trong khi tạo nhóm 4 bit, thì hãy bao gồm số lượng không cần thiết ở các cạnh cực.

Viết các chữ số thập phân Hexa tương ứng với mỗi nhóm 4 bit.

Example

Xem xét binary number 101110.01101

Step 1 - Lập nhóm 4 bit ở cả hai phía của điểm nhị phân.

10 1110.0110 1

Ở đây, nhóm đầu tiên chỉ có 2 bit. Vì vậy, hãy bao gồm hai số không ở bên cực để làm cho nó thành nhóm 4 bit. Tương tự, bao gồm ba số không ở bên cực để làm cho nhóm cuối cùng cũng là nhóm 4 bit.

⇒ 0010 1110.0110 1000

Step 2 - Viết các chữ số thập lục phân tương ứng với mỗi nhóm 4 bit.

⇒ (0010 1110.0110 1000) 2 = (2E.68) 16

Do đó, Hexa-decimal equivalent của số nhị phân 101110.01101 là (2E.68).

Chuyển đổi số bát phân sang các cơ sở khác

Quá trình chuyển đổi một số từ bát phân sang thập phân khác với quá trình chuyển đổi một số bát phân sang các cơ số khác. Bây giờ, chúng ta hãy thảo luận về việc chuyển đổi lần lượt một số bát phân sang hệ thập phân, nhị phân và hệ thập phân Hexa.

Chuyển đổi từ bát phân sang thập phân

Để chuyển một số bát phân thành số thập phân tương đương của nó, trước tiên hãy nhân các chữ số của số bát phân với trọng số vị trí tương ứng rồi cộng tất cả các tích đó.

Example

Xem xét octal number 145.23.

Mathematically, chúng ta có thể viết nó là

(145,23) 8 = (1 × 8 2 ) + (4 × 8 1 ) + (5 × 8 0 ) + (2 × 8 -1 ) + (3 × 8 -2 )

⇒ (145,23) 8 = 64 + 32 + 5 + 0,25 + 0,05 = 101,3

⇒ (145,23) 8 = (101,3) 10

Do đó, decimal equivalent của số bát phân 145,23 là 101,3.

Chuyển đổi bát phân sang nhị phân

Quá trình chuyển đổi một số bát phân sang một số nhị phân tương đương hoàn toàn ngược lại với quá trình chuyển đổi từ nhị phân sang bát phân. Bằng cách biểu diễn mỗi chữ số bát phân với 3 bit, chúng ta sẽ nhận được số nhị phân tương đương.

Example

Xem xét octal number 145.23.

Biểu diễn mỗi chữ số bát phân với 3 bit.

(145,23) 8 = (001 100 101.010 011) 2

Giá trị không thay đổi bằng cách loại bỏ các số không ở phía cực đoan.

⇒ (145,23) 8 = (1100101.010011) 2

Do đó, binary equivalent của số bát phân 145,23 là 1100101.010011.

Chuyển đổi từ bát phân sang thập lục phân

Làm theo hai bước sau để chuyển đổi một số bát phân thành số thập phân Hexa tương đương của nó.

- Chuyển đổi số bát phân thành số nhị phân tương đương của nó.

- Chuyển số nhị phân ở trên thành số thập phân Hexa tương đương của nó.

Example

Xem xét octal number 145.23

Trong ví dụ trước, chúng tôi nhận được tương đương nhị phân của số bát phân 145,23 là 1100101.010011.

Bằng cách làm theo quy trình chuyển đổi từ nhị phân sang thập lục phân, chúng ta sẽ nhận được

(1100101.010011) 2 = (65,4C) 16

⇒ (145,23) 8 = (65,4C) 16

Do đó, Hexa-decimal equivalentcủa bát phân số 145,23 là 65,4 C .

Số thập phân-thập phân sang chuyển đổi cơ sở khác

Quá trình chuyển đổi một số từ hệ thập phân sang hệ thập phân khác với quá trình chuyển đổi số thập phân thành các cơ số khác. Bây giờ, chúng ta hãy thảo luận về việc chuyển đổi từng hệ thống số thập phân Hexa sang hệ thập phân, nhị phân và bát phân.

Chuyển đổi thập lục phân sang thập phân

Để chuyển đổi số thập phân Hexa thành số thập phân tương đương của nó, trước tiên, nhân các chữ số của số thập phân Hexa với trọng số vị trí tương ứng và sau đó cộng tất cả các tích đó.

Example

Xem xét Hexa-decimal number 1A5.2

Mathematically, chúng ta có thể viết nó là

(1A5,2) 16 = (1 × 16 2 ) + (10 × 16 1 ) + (5 × 16 0 ) + (2 × 16 -1 )

⇒ (1A5,2) 16 = 256 + 160 + 5 + 0,125 = 421,125

⇒ (1A5,2) 16 = (421,125) 10

Do đó, decimal equivalent của số thập phân 1A5.2 là 421.125.

Chuyển đổi thập lục phân sang nhị phân

Quá trình chuyển đổi số thập phân Hexa thành số nhị phân tương đương của nó hoàn toàn ngược lại với quá trình chuyển đổi từ nhị phân sang hệ thập phân. Bằng cách biểu diễn mỗi chữ số thập phân Hexa với 4 bit, chúng ta sẽ nhận được số nhị phân tương đương.

Example

Xem xét Hexa-decimal number 65.4C

Biểu diễn mỗi chữ số thập phân Hexa với 4 bit.

(65,4C) 6 = (0110 0101.0100 1100) 2

Giá trị không thay đổi bằng cách loại bỏ các số không ở hai cạnh cực.

⇒ (65,4C) 16 = (1100101.010011) 2

Do đó, binary equivalent của số thập lục phân 65,4C là 1100101.010011.

Chuyển đổi thập lục phân sang bát phân

Hãy làm theo hai bước sau để chuyển đổi số thập phân Hexa thành số bát phân tương đương của nó.

- Chuyển đổi số thập phân Hexa thành số nhị phân tương đương của nó.

- Chuyển số nhị phân trên thành số bát phân tương đương của nó.

Example

Xem xét Hexa-decimal number 65.4C

Trong ví dụ trước, chúng tôi nhận được số tương đương nhị phân của số thập phân 65,4C là 1100101.010011.

Bằng cách làm theo quy trình chuyển đổi từ nhị phân sang bát phân, chúng ta sẽ nhận được

(1100101.010011) 2 = (145,23) 8

⇒ (65,4C) 16 = (145,23)

Do đó, octal equivalentcủa số thập lục phân 65,4 C là 145,23.

Chúng ta có thể chia các số nhị phân thành hai nhóm sau: Unsigned numbers và Signed numbers.

Số chưa ký

Các số không có dấu chỉ chứa độ lớn của số. Họ không có bất kỳ dấu hiệu nào. Điều đó có nghĩa là tất cả các số nhị phân không dấu đều dương. Như trong hệ thống số thập phân, việc đặt dấu dương trước số là tùy chọn để biểu diễn số dương. Do đó, tất cả các số dương bao gồm cả số 0 có thể được coi là số không có dấu nếu dấu dương không được gán trước số đó.

Số đã ký

Các số có dấu chứa cả dấu và độ lớn của số. Nói chung, dấu hiệu được đặt trước số. Vì vậy, chúng ta phải xét dấu dương cho số dương và dấu âm cho số âm. Do đó, tất cả các số có thể được coi là số có dấu nếu dấu tương ứng được gán trước số đó.

Nếu bit dấu bằng 0, cho biết số nhị phân là số dương. Tương tự, nếu bit dấu là một, cho biết số nhị phân là số âm.

Biểu diễn các số nhị phân chưa ký

Các bit có trong số nhị phân chưa ký giữ magnitudecủa một số. Điều đó có nghĩa là, nếu số nhị phân chưa ký có chứa‘N’ bit, sau đó là tất cả N bit đại diện cho độ lớn của số, vì nó không có bất kỳ bit dấu nào.

Example

Xem xét decimal number 108. Số tương đương nhị phân của số này là1101100. Đây là đại diện của số nhị phân không dấu.

(108) 10 = (1101100) 2

Nó có 7 bit. 7 bit này đại diện cho độ lớn của số 108.

Biểu diễn các số nhị phân đã ký

Bit quan trọng nhất (MSB) của số nhị phân có dấu được sử dụng để chỉ ra dấu của các số. Do đó, nó còn được gọi làsign bit. Dấu tích cực được biểu diễn bằng cách đặt '0' vào bit dấu. Tương tự, dấu âm được biểu diễn bằng cách đặt '1' vào bit dấu.

Nếu số nhị phân có dấu chứa các bit 'N', thì các bit (N-1) chỉ thể hiện độ lớn của số vì một bit (MSB) được dành riêng để biểu diễn dấu của số.

Có ba types of representations cho các số nhị phân có dấu

- Biểu mẫu độ lớn dấu hiệu

- Hình thức bổ sung của 1

- Hình thức bổ sung của 2

Biểu diễn một số dương ở cả 3 dạng này đều giống nhau. Tuy nhiên, chỉ biểu diễn số âm sẽ khác nhau ở mỗi dạng.

Example

Xem xét positive decimal number +108. Tương đương nhị phân về độ lớn của số này là 1101100. 7 bit này đại diện cho độ lớn của số 108. Vì nó là số dương, hãy coi bit dấu là 0, được đặt ở bên trái hầu hết độ lớn.

(+108) 10 = (01101100) 2

Do đó, signed binary representationcủa số thập phân dương +108 là. Vì vậy, biểu diễn tương tự có giá trị ở dạng dấu hiệu, dạng phần bù của 1 và dạng phần bù của 2 cho số thập phân dương +108.

Biểu mẫu độ lớn dấu hiệu

Ở dạng cường độ dấu hiệu, MSB được sử dụng để biểu diễn sign của số và các bit còn lại đại diện cho magnitudecủa số. Vì vậy, chỉ cần bao gồm bit dấu ở phía ngoài cùng bên trái của số nhị phân không dấu. Biểu diễn này tương tự như biểu diễn số thập phân có dấu.

Example

Xem xét negative decimal number -108. Độ lớn của con số này là 108. Chúng ta biết biểu diễn nhị phân không dấu của 108 là 1101100. Nó có 7 bit. Tất cả các bit này đại diện cho độ lớn.

Vì số đã cho là số âm, hãy coi bit dấu là một, được đặt ở bên trái hầu hết độ lớn.

(−108) 10 = (11101100) 2

Do đó, biểu diễn độ lớn dấu của -108 là 11101100.

Hình thức bổ sung của 1

Phần bù 1 của một số nhận được bằng complementing all the bitscủa số nhị phân có dấu. Vì vậy, phần bù của 1 của số dương cho một số âm. Tương tự, phần bù 1 của số âm cho một số dương.

Điều đó có nghĩa là, nếu bạn thực hiện hai lần phần bù 1 của một số nhị phân bao gồm cả bit dấu, thì bạn sẽ nhận được số nhị phân có dấu ban đầu.

Example

Xem xét negative decimal number -108. Độ lớn của số này là 108. Chúng ta biết biểu diễn nhị phân có dấu của 108 là 01101100.

Nó có 8 bit. MSB của số này là số 0, cho biết số dương. Phần bù của số 0 là một và ngược lại. Vì vậy, hãy thay thế các số không bằng một và một bằng các số không để nhận được số âm.

(−108) 10 = (10010011) 2

Do đó, 1’s complement of (108)10 Là (10010011)2.

Hình thức bổ sung của 2

Phần bù 2 của một số nhị phân thu được bằng adding one to the 1’s complementcủa số nhị phân có dấu. Vì vậy, phần bù của 2 của số dương cho một số âm. Tương tự, phần bù của 2 của số âm cho một số dương.

Điều đó có nghĩa là, nếu bạn thực hiện hai lần bù 2 của một số nhị phân bao gồm cả bit dấu, thì bạn sẽ nhận được số nhị phân có dấu ban đầu.

Example

Xem xét negative decimal number -108.

Chúng tôi biết phần bổ sung số 1 của (108)10 Là (10010011)2

2 lời khen của (108) 10 = 1 lời khen của (108) 10 + 1.

= 10010011 + 1

= 10010100

Do đó, 2’s complement of (108)10 Là (10010100)2.

Trong chương này, chúng ta hãy thảo luận về các phép toán số học cơ bản, có thể được thực hiện trên bất kỳ số nhị phân có hai dấu nào bằng cách sử dụng phương pháp bù của 2. Cácbasic arithmetic operations là phép cộng và phép trừ.

Phép cộng hai số nhị phân có dấu

Hãy xem xét hai số nhị phân có dấu A & B, được biểu diễn dưới dạng phần bù của 2. Chúng tôi có thể thực hiệnadditioncủa hai số này, tương tự như phép cộng hai số nhị phân không dấu. Nhưng, nếu tổng kết quả chứa thực hiện từ bit dấu, thì loại bỏ (bỏ qua) nó để nhận giá trị chính xác.

Nếu tổng kết quả là số dương, bạn có thể tìm trực tiếp độ lớn của nó. Nhưng, nếu tổng kết quả là số âm, thì lấy phần bù 2 của nó để có được độ lớn.

ví dụ 1

Hãy để chúng tôi thực hiện addition của hai số thập phân +7 and +4 sử dụng phương pháp bổ sung của 2.

Các 2’s complement biểu diễn +7 và +4 với mỗi bit 5 được hiển thị bên dưới.

(+7) 10 = (00111) 2

(+4) 10 = (00100) 2

Phép cộng của hai số này là

(+7) 10 + (+ 4) 10 = (00111) 2 + (00100) 2

⇒ (+7) 10 + (+ 4) 10 = (01011) 2 .

Tổng kết quả chứa 5 bit. Vì vậy, không có thực hiện từ bit dấu. Bit dấu '0' chỉ ra rằng tổng kết quả làpositive. Vì vậy, độ lớn của tổng là 11 trong hệ thống số thập phân. Do đó, phép cộng hai số dương sẽ cho một số dương khác.

Ví dụ 2

Hãy để chúng tôi thực hiện addition của hai số thập phân -7 và -4 sử dụng phương pháp bổ sung của 2.

Các 2’s complement biểu diễn -7 và -4 với mỗi bit 5 được hiển thị bên dưới.

(−7) 10 = (11001) 2

(−4) 10 = (11100) 2

Phép cộng của hai số này là

(−7) 10 + (−4) 10 = (11001) 2 + (11100) 2

⇒ (−7) 10 + (−4) 10 = (110101) 2 .

Tổng kết quả chứa 6 bit. Trong trường hợp này, carry thu được từ bit dấu. Vì vậy, chúng tôi có thể xóa nó

Tổng kết quả sau khi loại bỏ mang là (−7) 10 + (−4) 10 =(10101)2.

Bit dấu '1' chỉ ra rằng tổng kết quả là negative. Vì vậy, bằng cách lấy phần bù 2 của nó, chúng ta sẽ nhận được độ lớn của tổng kết quả là 11 trong hệ thống số thập phân. Do đó, phép cộng hai số âm sẽ cho một số âm khác.

Phép trừ hai số nhị phân có dấu

Hãy xem xét hai số nhị phân có dấu A & B, được biểu diễn dưới dạng phần bù của 2. Chúng ta biết rằng phần bù của 2 số dương cho một số âm. Vì vậy, bất cứ khi nào chúng ta phải trừ một số B cho số A, sau đó lấy phần bù 2 của B và cộng nó với A. Vì vậy,mathematically chúng ta có thể viết nó là

A - B = A + (2's complement of B)

Tương tự, nếu chúng ta phải trừ số A với số B, thì lấy phần bù 2 của A và cộng với B. Vì vậy, mathematically chúng ta có thể viết nó là

B - A = B + (2's complement of A)

Vì vậy, phép trừ hai số nhị phân có dấu cũng tương tự như phép cộng hai số nhị phân có dấu. Nhưng, chúng ta phải lấy phần bù của 2 của số, được cho là số bị trừ. Đây làadvantagecủa kỹ thuật bổ sung của 2. Thực hiện theo, các quy tắc tương tự của phép cộng hai số nhị phân có dấu.

Ví dụ 3

Hãy để chúng tôi thực hiện subtraction của hai số thập phân +7 and +4 sử dụng phương pháp bổ sung của 2.

Phép trừ hai số này là

(+7) 10 - (+4) 10 = (+7) 10 + (−4) 10 .

Các 2’s complement biểu diễn +7 và -4 với mỗi bit 5 được hiển thị bên dưới.

(+7) 10 = (00111) 2

(+4) 10 = (11100) 2

⇒ (+7) 10 + (+4) 10 = (00111) 2 + (11100) 2 = (00011) 2

Ở đây, thực hiện thu được từ bit dấu. Vì vậy, chúng ta có thể loại bỏ nó. Tổng kết quả sau khi loại bỏ mang là

(+7) 10 + (+4) 10 =(00011)2

Bit dấu '0' chỉ ra rằng tổng kết quả là positive. Vì vậy, độ lớn của nó là 3 trong hệ thống số thập phân. Do đó, phép trừ hai số thập phân +7 và +4 là +3.

Ví dụ 4

Hãy để chúng tôi thực hiện subtraction of hai số thập phân +4 và +7 sử dụng phương pháp bổ sung của 2.

Phép trừ hai số này là

(+4) 10 - (+7) 10 = (+4) 10 + (−7) 10 .

Các 2’s complement biểu diễn của +4 và -7 với mỗi bit 5 được hiển thị bên dưới.

(+4) 10 = (00100) 2

(-7) 10 = (11001) 2

⇒ (+4) 10 + (-7) 10 = (00100) 2 + (11001) 2 = (11101) 2

Ở đây, carry không thu được từ bit dấu. Bit dấu '1' chỉ ra rằng tổng kết quả lànegative. Vì vậy, bằng cách lấy phần bù 2 của nó, chúng ta sẽ nhận được độ lớn của tổng kết quả là 3 trong hệ thống số thập phân. Do đó, phép trừ hai số thập phân +4 và +7 là -3.

Trong mã hóa, khi số hoặc chữ cái được biểu thị bằng một nhóm ký hiệu cụ thể, nó được cho là số hoặc chữ cái đó đang được mã hóa. Nhóm ký hiệu được gọi làcode. Dữ liệu kỹ thuật số được biểu diễn, lưu trữ và truyền dưới dạng nhóm bit. Nhóm bit này còn được gọi làbinary code.

Mã nhị phân có thể được phân thành hai loại.

- Mã trọng số

- Mã không trọng số

Nếu mã có trọng số vị trí, thì nó được cho là weighted code. Nếu không, nó là một mã không có trọng số. Mã có trọng số có thể được phân loại thêm thành mã có trọng số dương và mã có trọng số âm.

Mã nhị phân cho chữ số thập phân

Bảng sau đây cho thấy các mã nhị phân khác nhau cho các chữ số thập phân từ 0 đến 9.

| Chữ số thập phân | 8421 Mã | 2421 Mã | 84-2-1 Mã | Quá 3 mã |

|---|---|---|---|---|

| 0 | 0000 | 0000 | 0000 | 0011 |

| 1 | 0001 | 0001 | 0111 | 0100 |

| 2 | 0010 | 0010 | 0110 | 0101 |

| 3 | 0011 | 0011 | 0101 | 0110 |

| 4 | 0100 | 0100 | 0100 | 0111 |

| 5 | 0101 | 1011 | 1011 | 1000 |

| 6 | 0110 | 1100 | 1010 | 1001 |

| 7 | 0111 | 1101 | 1001 | 1010 |

| số 8 | 1000 | 1110 | 1000 | 1011 |

| 9 | 1001 | 1111 | 1111 | 1100 |

Chúng tôi có 10 chữ số trong hệ thống số thập phân. Để biểu diễn 10 chữ số này dưới dạng nhị phân, chúng tôi yêu cầu tối thiểu 4 bit. Tuy nhiên, với 4 bit sẽ có 16 sự kết hợp duy nhất của số không và số một. Vì chúng ta chỉ có 10 chữ số thập phân, 6 tổ hợp số không và đơn vị khác là không bắt buộc.

8 4 2 1 mã

Các trọng số của mã này là 8, 4, 2 và 1.

Mã này có tất cả các trọng số dương. Vì vậy, nó là mộtpositively weighted code.

Mã này còn được gọi là natural BCD (Số thập phân được mã nhị phân) code.

Example

Hãy tìm BCD tương đương của số thập phân 786. Số này có 3 chữ số thập phân là 7, 8 và 6. Từ bảng này ta viết được mã BCD (8421) của 7, 8 và 6 lần lượt là 0111, 1000 và 0110 .

∴ (786)10 = (011110000110)BCD

Có 12 bit trong biểu diễn BCD, vì mỗi mã BCD của chữ số thập phân có 4 bit.

2 4 2 1 mã

Các trọng số của mã này là 2, 4, 2 và 1.

Mã này có tất cả các trọng số dương. Vì vậy, nó là mộtpositively weighted code.

Nó là một unnatural BCDmã. Tổng trọng số của mã BCD không tự nhiên bằng 9.

Nó là một self-complementingmã. Các mã tự bổ sung cung cấp phần bù của số 9 của một số thập phân, chỉ bằng cách hoán đổi số 1 và số 0 trong biểu diễn 2421 tương đương của nó.

Example

Hãy tìm 2421 tương đương của số thập phân 786. Số này có 3 chữ số thập phân 7, 8 và 6. Từ bảng, ta có thể viết 2421 mã của 7, 8 và 6 lần lượt là 1101, 1110 và 1100.

Do đó, 2421 tương đương với số thập phân 786 là 110111101100.

8 4 -2 -1 mã

Các trọng số của mã này là 8, 4, -2 và -1.

Mã này có trọng số âm cùng với trọng số dương. Vì vậy, nó là mộtnegatively weighted code.

Nó là một unnatural BCD mã.

Nó là một self-complementing mã.

Example

Hãy tìm 8 4-2-1 tương đương của số thập phân 786. Số này có 3 chữ số thập phân là 7, 8 và 6. Từ bảng, ta có thể viết các mã 8 4 -2 -1 của 7, 8 và 6 lần lượt là 1001, 1000 và 1010.

Do đó, 8 4 -2 -1 tương đương của số thập phân 786 là 100110001010.

Thừa 3 mã

Mã này không có bất kỳ trọng số nào. Vì vậy, nó là mộtun-weighted code.

Chúng ta sẽ nhận được mã thừa 3 của một số thập phân bằng cách thêm ba (0011) vào mã nhị phân tương đương của số thập phân đó. Do đó, nó được gọi là mã thừa 3.

Nó là một self-complementing mã.

Example

Ta tìm số dư 3 tương đương với số thập phân 786. Số này có 3 chữ số thập phân là 7, 8 và 6. Từ bảng, ta có thể viết 3 thừa của số 7, 8 và 6 lần lượt là 1010, 1011 và 1001.

Do đó, phần dư 3 tương đương của số thập phân 786 là 101010111001

Mã màu xám

Bảng sau đây cho thấy các mã Xám 4 bit tương ứng với mỗi mã nhị phân 4 bit.

| Số thập phân | Mã nhị phân | Mã màu xám |

|---|---|---|

| 0 | 0000 | 0000 |

| 1 | 0001 | 0001 |

| 2 | 0010 | 0011 |

| 3 | 0011 | 0010 |

| 4 | 0100 | 0110 |

| 5 | 0101 | 0111 |

| 6 | 0110 | 0101 |

| 7 | 0111 | 0100 |

| số 8 | 1000 | 1100 |

| 9 | 1001 | 1101 |

| 10 | 1010 | 1111 |

| 11 | 1011 | 1110 |

| 12 | 1100 | 1010 |

| 13 | 1101 | 1011 |

| 14 | 1110 | 1001 |

| 15 | 1111 | 1000 |

Mã này không có bất kỳ trọng số nào. Vì vậy, nó là mộtun-weighted code.

Trong bảng trên, các mã Xám kế tiếp chỉ khác nhau ở một vị trí bit. Do đó, mã này được gọi làunit distance mã.

Mã nhị phân thành Chuyển đổi mã màu xám

Làm theo các bước sau để chuyển đổi mã nhị phân thành mã Xám tương đương.

Xem xét mã nhị phân đã cho và đặt số 0 ở bên trái MSB.

So sánh hai bit liên tiếp bắt đầu từ số không. Nếu 2 bit giống nhau, thì đầu ra bằng không. Nếu không, đầu ra là một.

Lặp lại bước trên cho đến khi nhận được mã LSB of Grey.

Example

Từ bảng, chúng ta biết rằng mã Xám tương ứng với mã nhị phân 1000 là 1100. Bây giờ, chúng ta hãy xác minh nó bằng cách sử dụng quy trình trên.

Đã cho, mã nhị phân là 1000.

Step 1 - Đặt số 0 bên trái MSB, mã nhị phân sẽ là 01000.

Step 2 - Bằng cách so sánh hai bit liên tiếp của mã nhị phân mới, chúng ta sẽ nhận được mã màu xám là 1100.

Chúng ta biết rằng các bit 0 và 1 tương ứng với hai dải điện áp tương tự khác nhau. Vì vậy, trong quá trình truyền dữ liệu nhị phân từ hệ thống này sang hệ thống khác, nhiễu cũng có thể được thêm vào. Do đó, dữ liệu nhận được ở hệ thống khác có thể bị lỗi.

Điều đó có nghĩa là một bit 0 có thể thay đổi thành 1 hoặc một bit 1 có thể thay đổi thành 0. Chúng ta không thể tránh được sự can thiệp của nhiễu. Tuy nhiên, chúng tôi có thể lấy lại dữ liệu ban đầu trước tiên bằng cách phát hiện xem có bất kỳ lỗi nào hay không và sau đó sửa các lỗi đó. Với mục đích này, chúng tôi có thể sử dụng các mã sau.

- Mã phát hiện lỗi

- Mã sửa lỗi

Error detection codes- được sử dụng để phát hiện (các) lỗi có trong dữ liệu nhận được (luồng bit). Những mã này chứa (các) bit, được bao gồm (nối thêm) vào dòng bit gốc. Các mã này phát hiện lỗi, nếu nó xảy ra trong quá trình truyền dữ liệu gốc (luồng bit).Example - Mã chẵn lẻ, mã Hamming.

Error correction codes- được sử dụng để sửa (các) lỗi có trong dữ liệu đã nhận (dòng bit) để chúng ta lấy dữ liệu gốc. Mã sửa lỗi cũng sử dụng chiến lược tương tự của mã phát hiện lỗi.Example - Mã Hamming.

Do đó, để phát hiện và sửa lỗi, (các) bit bổ sung được nối vào các bit dữ liệu tại thời điểm truyền.

Mã chẵn lẻ

Có thể dễ dàng bao gồm (nối thêm) một bit chẵn lẻ ở bên trái MSB hoặc bên phải LSB của dòng bit gốc. Có hai loại mã chẵn lẻ, đó là mã chẵn lẻ và mã chẵn lẻ dựa trên loại chẵn lẻ được chọn.

Mã chẵn lẻ

Giá trị của bit chẵn lẻ phải bằng 0, nếu số bit chẵn có trong mã nhị phân. Nếu không, nó phải là một. Vì vậy, số lượng chẵn có trongeven parity code. Mã chẵn lẻ chứa các bit dữ liệu và bit chẵn lẻ.

Bảng sau đây cho thấy even parity codestương ứng với mỗi mã nhị phân 3 bit. Ở đây, bit chẵn lẻ được đưa vào bên phải LSB của mã nhị phân.

| Mã nhị phân | Bit chẵn lẻ | Mã chẵn lẻ |

|---|---|---|

| 000 | 0 | 0000 |

| 001 | 1 | 0011 |

| 010 | 1 | 0101 |

| 011 | 0 | 0110 |

| 100 | 1 | 1001 |

| 101 | 0 | 1010 |

| 110 | 0 | 1100 |

| 111 | 1 | 1111 |

Ở đây, số bit có trong mã chẵn lẻ là 4. Vì vậy, số bit chẵn có thể có trong các mã chẵn lẻ này là 0, 2 & 4.

Nếu hệ thống khác nhận được một trong các mã chẵn lẻ này, thì dữ liệu nhận được sẽ không có lỗi. Các bit khác với bit chẵn lẻ giống như bit của mã nhị phân.

Nếu hệ thống khác nhận được không phải là mã chẵn lẻ, thì sẽ có (các) lỗi trong dữ liệu đã nhận. Trong trường hợp này, chúng tôi không thể dự đoán mã nhị phân ban đầu vì chúng tôi không biết (các) vị trí bit bị lỗi.

Do đó, bit chẵn lẻ chỉ hữu ích để phát hiện lỗi trong mã chẵn lẻ nhận được. Nhưng, nó không đủ để sửa lỗi.

Mã chẵn lẻ lẻ

Giá trị của bit chẵn lẻ lẻ phải bằng 0, nếu có số lẻ trong mã nhị phân. Nếu không, nó phải là một. Vì vậy, số lẻ của những người có trongodd parity code. Mã chẵn lẻ lẻ chứa các bit dữ liệu và bit chẵn lẻ lẻ.

Bảng sau đây cho thấy odd parity codestương ứng với mỗi mã nhị phân 3 bit. Ở đây, bit chẵn lẻ lẻ được đưa vào bên phải LSB của mã nhị phân.

| Mã nhị phân | Bit chẵn lẻ lẻ | Mã chẵn lẻ lẻ |

|---|---|---|

| 000 | 1 | 0001 |

| 001 | 0 | 0010 |

| 010 | 0 | 0100 |

| 011 | 1 | 0111 |

| 100 | 0 | 1000 |

| 101 | 1 | 1011 |

| 110 | 1 | 1101 |

| 111 | 0 | 1110 |

Ở đây, số bit có trong các mã chẵn lẻ lẻ là 4. Vì vậy, số bit lẻ có thể có trong các mã chẵn lẻ lẻ này là 1 & 3.

Nếu hệ thống khác nhận được một trong các mã chẵn lẻ lẻ này, thì dữ liệu nhận được sẽ không có lỗi. Các bit khác với bit chẵn lẻ lẻ giống như bit của mã nhị phân.

Nếu hệ thống khác nhận được không phải là mã chẵn lẻ lẻ, thì có một lỗi trong dữ liệu nhận được. Trong trường hợp này, chúng tôi không thể dự đoán mã nhị phân ban đầu vì chúng tôi không biết (các) vị trí bit bị lỗi.

Do đó, bit chẵn lẻ lẻ chỉ hữu ích để phát hiện lỗi trong mã chẵn lẻ nhận được. Nhưng, nó không đủ để sửa lỗi.

Mã Hamming

Mã Hamming hữu ích cho cả việc phát hiện và sửa lỗi có trong dữ liệu nhận được. Mã này sử dụng nhiều bit chẵn lẻ và chúng ta phải đặt các bit chẵn lẻ này vào vị trí lũy thừa của 2.

Các minimum value of 'k' mà quan hệ sau là đúng (hợp lệ) không là gì ngoài số bit chẵn lẻ cần thiết.

$$2^k\geq n+k+1$$

Ở đâu,

'n' là số bit trong mã nhị phân (thông tin)

'k' là số bit chẵn lẻ

Do đó, số bit trong mã Hamming bằng n + k.

Hãy để Hamming code Là $b_{n+k}b_{n+k-1}.....b_{3}b_{2}b_{1}$ & bit chẵn lẻ $p_{k}, p_{k-1}, ....p_{1}$. Chúng ta chỉ có thể đặt các bit chẵn lẻ 'k' theo lũy thừa của 2 vị trí. Ở các vị trí bit còn lại, chúng ta có thể đặt các bit 'n' của mã nhị phân.

Dựa trên yêu cầu, chúng ta có thể sử dụng chẵn lẻ hoặc chẵn lẻ trong khi tạo mã Hamming. Tuy nhiên, kỹ thuật chẵn lẻ tương tự nên được sử dụng để tìm xem có lỗi nào xuất hiện trong dữ liệu đã nhận hay không.

Làm theo quy trình này để tìm parity bits.

Tìm giá trị của p1, dựa trên số lượng đơn vị có mặt ở các vị trí bit b 3 , b 5 , b 7 , v.v. Tất cả các vị trí bit này (hậu tố) trong hệ nhị phân tương đương của chúng có giá trị '1' ở vị trí là 2 0 .

Tìm giá trị của p2, dựa trên số lượng đơn vị có ở các vị trí bit b 3 , b 6 , b 7 , v.v. Tất cả các vị trí bit này (hậu tố) trong hệ nhị phân tương đương của chúng có giá trị '1' ở vị trí là 2 1 .

Tìm giá trị của p3, dựa trên số lượng đơn vị có ở các vị trí bit b 5 , b 6 , b 7 , v.v. Tất cả các vị trí bit này (hậu tố) trong hệ nhị phân tương đương của chúng có giá trị '1' ở vị trí là 2 2 .

Tương tự, tìm các giá trị khác của bit chẵn lẻ.

Làm theo quy trình này để tìm check bits.

Tìm giá trị của c 1 , dựa trên số đơn vị có ở các vị trí bit b 1 , b 3 , b 5 , b 7 , v.v. Tất cả các vị trí bit này (hậu tố) trong hệ nhị phân tương đương của chúng có giá trị '1' ở vị trí là 2 0 .

Tìm giá trị của c 2 , dựa trên số lượng đơn vị có mặt ở các vị trí bit b 2 , b 3 , b 6 , b 7 , v.v. Tất cả các vị trí bit này (hậu tố) trong hệ nhị phân tương đương của chúng có giá trị '1' ở vị trí là 2 1 .

Tìm giá trị của c 3 , dựa trên số lượng đơn vị có ở các vị trí bit b 4 , b 5 , b 6 , b 7 , v.v. Tất cả các vị trí bit này (hậu tố) trong hệ nhị phân tương đương của chúng có giá trị '1' ở vị trí là 2 2 .

Tương tự, tìm các giá trị khác của các bit kiểm tra.

Tương đương thập phân của các bit kiểm tra trong dữ liệu nhận được cung cấp giá trị của vị trí bit, nơi có lỗi. Chỉ cần bổ sung giá trị có trong vị trí bit đó. Do đó, chúng ta sẽ nhận được mã nhị phân ban đầu sau khi loại bỏ các bit chẵn lẻ.

ví dụ 1

Hãy để chúng tôi tìm mã Hamming cho mã nhị phân, d 4 d 3 d 2 d 1 = 1000. Xét các bit chẵn lẻ.

Số bit trong mã nhị phân đã cho là n = 4.

Chúng ta có thể tìm số lượng bit chẵn lẻ cần thiết bằng cách sử dụng quan hệ toán học sau.

$$2^k\geq n+k+1$$

Thay thế, n = 4 trong quan hệ toán học trên.

$$\Rightarrow 2^k\geq 4+k+1$$

$$\Rightarrow 2^k\geq 5+k$$

Giá trị nhỏ nhất của k thỏa mãn quan hệ trên là 3. Do đó, chúng ta yêu cầu 3 bit chẵn lẻ p 1 , p 2 và p 3 . Do đó, số bit trong mã Hamming sẽ là 7, vì có 4 bit trong mã nhị phân và 3 bit chẵn lẻ. Chúng ta phải đặt các bit chẵn lẻ và các bit của mã nhị phân trong mã Hamming như hình dưới đây.

Các 7-bit Hamming code Là $b_{7}b_{6}b_{5}b_{4}b_{3}b_{2}b_{1}=d_{4}d_{3}d_{2}p_{3}d_{1}p_{2}bp_{1}$

Bằng cách thay thế các bit của mã nhị phân, mã Hamming sẽ là $b_{7}b_{6}b_{5}b_{4}b_{3}b_{2}b_{1} = 100p_{3}Op_{2}p_{1}$. Bây giờ, chúng ta hãy tìm các bit chẵn lẻ.

$$p_{1}=b_{7}\oplus b_{5}\oplus b_{3}=1 \oplus 0 \oplus 0=1$$

$$p_{2}=b_{7}\oplus b_{6}\oplus b_{3}=1 \oplus 0 \oplus 0=1$$

$$p_{3}=b_{7}\oplus b_{6}\oplus b_{5}=1 \oplus 0 \oplus 0=1$$

Bằng cách thay thế các bit chẵn lẻ này, Hamming code sẽ là $b_{7}b_{6}b_{5}b_{4}b_{3}b_{2}b_{1}= 1001011$.

Ví dụ 2

Trong ví dụ trên, chúng ta có mã Hamming là $b_{7}b_{6}b_{5}b_{4}b_{3}b_{2}b_{1}= 1001011$. Bây giờ, chúng ta hãy tìm vị trí lỗi khi mã nhận được là$b_{7}b_{6}b_{5}b_{4}b_{3}b_{2}b_{1}= 1001111$.

Bây giờ, chúng ta hãy tìm các bit kiểm tra.

$$c_{1}=b_{7}\oplus b_{5}\oplus b_{3}\oplus b_{1}=1 \oplus 0 \oplus 1 \oplus1 =1$$

$$c_{2}=b_{7}\oplus b_{6}\oplus b_{3}\oplus b_{2}=1 \oplus 0 \oplus 1 \oplus1 =1$$

$$c_{3}=b_{7}\oplus b_{6}\oplus b_{5}\oplus b_{4}=1 \oplus 0 \oplus 0 \oplus1 =0$$

Giá trị thập phân của các bit kiểm tra cho biết vị trí của lỗi trong mã Hamming nhận được.

$$c_{3}c_{2}c_{1} = \left ( 011 \right )_{2}=\left ( 3 \right )_{10}$$

Do đó, lỗi xuất hiện ở bit thứ ba (b 3 ) của mã Hamming. Chỉ cần bổ sung giá trị có trong bit đó và loại bỏ các bit chẵn lẻ để có được mã nhị phân ban đầu.

Boolean Algebralà một đại số, xử lý các số nhị phân và các biến nhị phân. Do đó, nó còn được gọi là Đại số nhị phân hoặc Đại số lôgic. Một nhà toán học, tên là George Boole đã phát triển đại số này vào năm 1854. Các biến được sử dụng trong đại số này còn được gọi là biến Boolean.

Phạm vi điện áp tương ứng với logic 'Cao' được biểu thị bằng '1' và phạm vi điện áp tương ứng với logic 'Thấp' được biểu thị bằng '0'.

Định đề và luật cơ bản của đại số Boolean

Trong phần này, chúng ta hãy thảo luận về các định đề Boolean và các định luật cơ bản được sử dụng trong đại số Boolean. Chúng hữu ích trong việc giảm thiểu các hàm Boolean.

Định đề Boolean

Xét các số nhị phân 0 và 1, biến Boolean (x) và phần bù của nó (x '). Biến Boolean hoặc phần bổ sung của nó được gọi làliteral. Bốn khả thilogical OR các phép toán giữa các chữ và số nhị phân này được hiển thị bên dưới.

x + 0 = x

x + 1 = 1

x + x = x

x + x '= 1

Tương tự, bốn điều có thể logical AND các phép toán giữa các chữ và số nhị phân đó được hiển thị bên dưới.

x.1 = x

x.0 = 0

xx = x

x.x '= 0

Đây là những định đề Boolean đơn giản. Chúng tôi có thể xác minh những định đề này một cách dễ dàng, bằng cách thay thế biến Boolean bằng '0' hoặc '1'.

Note- Phần bù của phần bù của bất kỳ biến Boolean nào cũng bằng chính biến đó. tức là, (x ')' = x.

Luật cơ bản của đại số Boolean

Sau đây là ba định luật cơ bản của Đại số Boolean.

- Luật thay thế

- Luật kết hợp

- Luật phân phối

Luật thay thế

Nếu bất kỳ phép toán logic nào của hai biến Boolean cho cùng một kết quả bất kể thứ tự của hai biến đó, thì phép toán logic đó được cho là Commutative. Các phép toán logic OR & logic AND của hai biến Boolean x & y được hiển thị bên dưới

x + y = y + x

xy = yx

Biểu tượng '+' cho biết phép toán HOẶC logic. Tương tự, ký hiệu '.' chỉ ra hoạt động logic AND và nó là tùy chọn để đại diện. Luật giao hoán tuân theo các phép toán logic OR & logic AND.

Luật kết hợp

Nếu một phép toán logic của hai biến Boolean bất kỳ được thực hiện trước và sau đó phép toán tương tự được thực hiện với biến còn lại cho cùng một kết quả, thì phép toán logic đó được cho là Associative. Các phép toán logic OR & logic AND của ba biến Boolean x, y & z được hiển thị bên dưới.

x + (y + z) = (x + y) + z

x. (yz) = (xy) .z

Luật kết hợp tuân theo các phép toán logic OR & logic AND.

Luật phân phối

Nếu bất kỳ phép toán logic nào có thể được phân phối cho tất cả các điều khoản có trong hàm Boolean, thì phép toán logic đó được cho là Distributive. Sự phân bố các phép toán OR & logic AND của ba biến Boolean x, y & z được hiển thị bên dưới.

x. (y + z) = xy + xz

x + (yz) = (x + y). (x + z)

Luật phân phối tuân theo các phép toán logic OR và logic AND.

Đây là những luật cơ bản của đại số Boolean. Chúng ta có thể xác minh các luật này một cách dễ dàng bằng cách thay các biến Boolean bằng '0' hoặc '1'.

Định lý của Đại số Boolean

Hai định lý sau được sử dụng trong đại số Boolean.

- Định lý đối ngẫu

- Định lý DeMorgan

Định lý Đối ngẫu

Định lý này phát biểu rằng dualcủa hàm Boolean thu được bằng cách hoán đổi toán tử logic AND với toán tử OR logic và các số không với các toán tử. Với mỗi hàm Boolean, sẽ có một hàm Dual tương ứng.

Chúng ta hãy lập các phương trình Boolean (quan hệ) mà chúng ta đã thảo luận trong phần các định đề Boolean và các định luật cơ bản thành hai nhóm. Bảng sau đây cho thấy hai nhóm này.

| Nhóm 1 | Nhóm 2 |

|---|---|

| x + 0 = x | x.1 = x |

| x + 1 = 1 | x.0 = 0 |

| x + x = x | xx = x |

| x + x '= 1 | x.x '= 0 |

| x + y = y + x | xy = yx |

| x + (y + z) = (x + y) + z | x. (yz) = (xy) .z |

| x. (y + z) = xy + xz | x + (yz) = (x + y). (x + z) |

Trong mỗi hàng, có hai phương trình Boolean và chúng là đối ngẫu với nhau. Chúng ta có thể xác minh tất cả các phương trình Boolean này của Nhóm1 và Nhóm2 bằng cách sử dụng định lý đối ngẫu.

Định lý DeMorgan

Định lý này rất hữu ích trong việc tìm kiếm complement of Boolean function. Nó nói rằng phần bù của OR logic của ít nhất hai biến Boolean bằng AND logic của mỗi biến bổ sung.

Định lý DeMorgan với 2 biến Boolean x và y có thể được biểu diễn dưới dạng

(x + y) '= x'.y'

Đối ngẫu của hàm Boolean ở trên là

(xy) '= x' + y '

Do đó, phần bù của AND logic của hai biến Boolean bằng OR logic của mỗi biến bổ sung. Tương tự, chúng ta cũng có thể áp dụng định lý DeMorgan cho nhiều hơn 2 biến Boolean.

Đơn giản hóa các hàm Boolean

Cho đến bây giờ, chúng ta đã thảo luận về các định đề, định luật cơ bản và định lý của đại số Boolean. Bây giờ, chúng ta hãy đơn giản hóa một số hàm Boolean.

ví dụ 1

Hãy để chúng tôi simplify hàm Boolean, f = p'qr + pq'r + pqr '+ pqr

Chúng ta có thể đơn giản hóa hàm này bằng hai phương pháp.

Method 1

Cho hàm Boolean, f = p'qr + pq'r + pqr '+ pqr.

Step 1- Trong số hạng thứ nhất và số hạng thứ hai, r là chung và ở số hạng thứ ba và thứ tư, pq là chung. Vì vậy, hãy sử dụng các thuật ngữ chung bằng cách sử dụngDistributive law.

⇒ f = (p'q + pq ') r + pq (r' + r)

Step 2- Các thuật ngữ có trong ngoặc đơn đầu tiên có thể được đơn giản hóa thành phép toán Ex-OR. Các thuật ngữ trong ngoặc đơn thứ hai có thể được đơn giản hóa thành '1' bằng cách sử dụngBoolean postulate

⇒ f = (p ⊕q) r + pq (1)

Step 3- Thuật ngữ đầu tiên không thể được đơn giản hóa hơn nữa. Tuy nhiên, thuật ngữ thứ hai có thể được đơn giản hóa thành pq bằng cách sử dụngBoolean postulate.

⇒ f = (p ⊕q) r + pq

Do đó, hàm Boolean được đơn giản hóa là f = (p⊕q)r + pq

Method 2

Cho hàm Boolean, f = p'qr + pq'r + pqr '+ pqr.

Step 1 - Sử dụng Boolean postulate, x + x = x. Điều đó có nghĩa là, phép toán logic OR với bất kỳ biến Boolean nào 'n' lần sẽ bằng cùng một biến. Vì vậy, chúng ta có thể viết pqr số hạng cuối cùng hai lần nữa.

⇒ f = p'qr + pq'r + pqr '+ pqr + pqr + pqr

Step 2 - Sử dụng Distributive lawcho 1 st và 4 thứ về, 2 nd và 5 ngày điều khoản, 3 thứ 6 ngày về.

⇒ f = qr (p '+ p) + pr (q' + q) + pq (r '+ r)

Step 3 - Sử dụng Boolean postulate, x + x '= 1 để đơn giản hóa các thuật ngữ có trong mỗi dấu ngoặc đơn.

⇒ f = qr (1) + pr (1) + pq (1)

Step 4 - Sử dụng Boolean postulate, x.1 = x để đơn giản hóa ba số hạng trên.

⇒ f = qr + pr + pq

⇒ f = pq + qr + pr

Do đó, hàm Boolean được đơn giản hóa là f = pq + qr + pr.

Vì vậy, chúng ta có hai hàm Boolean khác nhau sau khi đơn giản hóa hàm Boolean đã cho trong mỗi phương thức. Về mặt chức năng, hai hàm Boolean đó giống nhau. Vì vậy, dựa trên yêu cầu, chúng ta có thể chọn một trong hai hàm Boolean đó.

Ví dụ 2

Hãy để chúng tôi tìm complement của hàm Boolean, f = p'q + pq '.

Phần bù của hàm Boolean là f '= (p'q + pq') '.

Step 1 - Sử dụng định lý DeMorgan, (x + y) '= x'.y'.

⇒ f '= (p'q)'. (Pq ')'

Step 2 - Sử dụng định lý DeMorgan, (xy) '= x' + y '

⇒ f '= {(p') '+ q'}. {P '+ (q') '}

Step3 - Sử dụng định đề Boolean, (x ')' = x.

⇒ f '= {p + q'}. {P '+ q}

⇒ f '= pp' + pq + p'q '+ qq'

Step 4 - Sử dụng định đề Boolean, xx '= 0.

⇒ f = 0 + pq + p'q '+ 0

⇒ f = pq + p'q '

Do đó, complement của hàm Boolean, p'q + pq 'là pq + p’q’.

Chúng ta sẽ nhận được bốn số hạng tích số Boolean bằng cách kết hợp hai biến x và y với phép toán logic AND. Các thuật ngữ sản phẩm Boolean này được gọi làmin terms hoặc là standard product terms. Các số hạng tối thiểu là x'y ', x'y, xy' và xy.

Tương tự, chúng ta sẽ nhận được bốn số hạng tổng Boolean bằng cách kết hợp hai biến x và y với phép toán OR logic. Các số hạng tổng Boolean này được gọi làMax terms hoặc là standard sum terms. Các số hạng Max là x + y, x + y ', x' + y và x '+ y'.

Bảng sau đây cho thấy sự biểu diễn của số hạng min và số hạng MAX cho 2 biến.

| x | y | Điều khoản tối thiểu | Điều khoản tối đa |

|---|---|---|---|

| 0 | 0 | m 0 = x'y ' | M 0 = x + y |

| 0 | 1 | m 1 = x'y | M 1 = x + y ' |

| 1 | 0 | m 2 = xy ' | M 2 = x '+ y |

| 1 | 1 | m 3 = xy | M 3 = x '+ y' |

Nếu biến nhị phân là '0', thì nó được biểu diễn dưới dạng phần bù của biến trong số hạng min và như chính biến đó trong số hạng Max. Tương tự, nếu biến nhị phân là '1', thì nó được biểu diễn dưới dạng phần bù của biến trong số hạng Max và như chính biến đó trong số hạng min.

Từ bảng trên, chúng ta có thể dễ dàng nhận thấy rằng các số hạng min và số hạng Max là bổ sung cho nhau. Nếu có 'n' biến Boolean, thì sẽ có 2 n số hạng min và 2 n số hạng Max.

Các dạng SoP và PoS chuẩn

Một bảng sự thật bao gồm một tập hợp các đầu vào và đầu ra. Nếu có 'n' biến đầu vào, thì sẽ có 2 n kết hợp có thể có với số không và số một. Vì vậy giá trị của mỗi biến đầu ra phụ thuộc vào sự kết hợp của các biến đầu vào. Vì vậy, mỗi biến đầu ra sẽ có '1' cho một số kết hợp của các biến đầu vào và '0' cho một số kết hợp khác của các biến đầu vào.

Do đó, chúng ta có thể biểu diễn mỗi biến đầu ra theo hai cách sau.

- Biểu mẫu SoP chuẩn

- Biểu mẫu PoS chuẩn

Biểu mẫu SoP chuẩn

Biểu mẫu SoP hợp quy có nghĩa là biểu mẫu Tổng sản phẩm hợp quy. Ở dạng này, mỗi thuật ngữ sản phẩm chứa tất cả các chữ. Vì vậy, các điều khoản sản phẩm này không là gì ngoài các điều khoản tối thiểu. Do đó, dạng SoP chuẩn còn được gọi làsum of min terms hình thức.

Đầu tiên, xác định các số hạng min mà biến đầu ra là một và sau đó thực hiện OR logic của các số hạng min đó để nhận được biểu thức Boolean (hàm) tương ứng với biến đầu ra đó. Hàm Boolean này sẽ ở dạng tổng các số hạng nhỏ nhất.

Cũng thực hiện theo quy trình tương tự cho các biến đầu ra khác, nếu có nhiều hơn một biến đầu ra.

Thí dụ

Hãy xem xét những điều sau truth table.

| Đầu vào | Đầu ra | ||

|---|---|---|---|

| p | q | r | f |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

Ở đây, đầu ra (f) là '1' cho bốn kết hợp đầu vào. Các số hạng tối thiểu tương ứng là p'qr, pq'r, pqr ', pqr. Bằng cách thực hiện logic OR của bốn số hạng nhỏ nhất này, chúng ta sẽ nhận được hàm Boolean của đầu ra (f).

Do đó, hàm Boolean của đầu ra là, f = p'qr + pq'r + pqr '+ pqr. Đây làcanonical SoP formđầu ra, f. Chúng ta cũng có thể biểu diễn hàm này bằng hai ký hiệu sau.

$$f = m_{3}+m_{5}+m_{6}+m_{7}$$

$$f = \sum m\left ( 3,5,6,7 \right )$$

Trong một phương trình, chúng tôi biểu diễn hàm dưới dạng tổng các số hạng nhỏ nhất tương ứng. Trong phương trình khác, chúng tôi sử dụng ký hiệu để tính tổng các số hạng tối thiểu đó.

Biểu mẫu PoS chuẩn

Dạng Canonical PoS nghĩa là Sản phẩm Canonical của dạng Sums. Ở dạng này, mỗi số hạng tổng chứa tất cả các chữ. Vì vậy, các điều khoản tổng này không là gì khác ngoài các điều khoản Max. Do đó, biểu mẫu PoS chuẩn còn được gọi làproduct of Max terms hình thức.

Đầu tiên, xác định các số hạng Max mà biến đầu ra là 0 và sau đó thực hiện phép logic AND của các số hạng Max đó để nhận được biểu thức Boolean (hàm) tương ứng với biến đầu ra đó. Hàm Boolean này sẽ ở dạng tích các số hạng Max.

Cũng thực hiện theo quy trình tương tự cho các biến đầu ra khác, nếu có nhiều hơn một biến đầu ra.

Example

Hãy xem xét cùng một bảng sự thật của ví dụ trước. Ở đây, đầu ra (f) là '0' cho bốn kết hợp đầu vào. Các số hạng Max tương ứng là p + q + r, p + q + r ', p + q' + r, p '+ q + r. Bằng cách thực hiện logic AND của bốn số hạng Max này, chúng ta sẽ nhận được hàm Boolean của đầu ra (f).

Do đó, hàm Boolean của đầu ra là, f = (p + q + r). (P + q + r '). (P + q' + r). (P '+ q + r). Đây làcanonical PoS formđầu ra, f. Chúng ta cũng có thể biểu diễn hàm này bằng hai ký hiệu sau.

$$f=M_{0}.M_{1}.M_{2}.M_{4}$$

$$f=\prod M\left ( 0,1,2,4 \right )$$

Trong một phương trình, chúng tôi biểu diễn hàm dưới dạng tích của các số hạng Max tương ứng. Trong phương trình khác, chúng tôi sử dụng ký hiệu để nhân các số hạng Max đó.

Hàm Boolean, f = (p + q + r). (P + q + r '). (P + q' + r). (P '+ q + r) là đối ngẫu của hàm Boolean, f = p'qr + pq'r + pqr '+ pqr.

Do đó, cả hai dạng SoP chuẩn và PoS chuẩn đều Dualcho nhau. Về mặt chức năng, hai hình thức này giống nhau. Căn cứ vào yêu cầu, chúng ta có thể sử dụng một trong hai hình thức này.

Các dạng SoP và PoS tiêu chuẩn

Chúng tôi đã thảo luận về hai dạng chính tắc biểu diễn (các) đầu ra Boolean. Tương tự, có hai dạng tiêu chuẩn biểu thị (các) đầu ra Boolean. Đây là phiên bản đơn giản hóa của các biểu mẫu chuẩn.

- Mẫu SoP tiêu chuẩn

- Mẫu PoS tiêu chuẩn

Chúng ta sẽ thảo luận về cổng Logic trong các chương sau. Chínhadvantagecủa các dạng tiêu chuẩn là số lượng đầu vào áp dụng cho các cổng logic có thể được giảm thiểu. Đôi khi, tổng số cổng logic được yêu cầu sẽ giảm.

Mẫu SoP tiêu chuẩn

Mẫu SoP tiêu chuẩn có nghĩa là Standard Sum of Productshình thức. Ở dạng này, mỗi thuật ngữ sản phẩm không cần chứa tất cả các chữ. Vì vậy, điều khoản sản phẩm có thể là điều khoản tối thiểu hoặc không. Do đó, biểu mẫu SoP chuẩn là dạng đơn giản hóa của biểu mẫu SoP chuẩn.

Chúng ta sẽ nhận được dạng SoP chuẩn của biến đầu ra trong hai bước.

- Nhận dạng SoP chuẩn của biến đầu ra

- Đơn giản hóa hàm Boolean ở trên, ở dạng SoP chính tắc.

Cũng thực hiện theo quy trình tương tự cho các biến đầu ra khác, nếu có nhiều hơn một biến đầu ra. Đôi khi, không thể đơn giản hóa biểu mẫu SoP chuẩn. Trong trường hợp đó, cả hai dạng SoP chuẩn và chuẩn đều giống nhau.

Example

Chuyển đổi hàm Boolean sau đây thành dạng SoP chuẩn.

f = p'qr + pq'r + pqr '+ pqr

Hàm Boolean đã cho ở dạng SoP chính tắc. Bây giờ, chúng ta phải đơn giản hóa hàm Boolean này để có được dạng SoP chuẩn.

Step 1 - Sử dụng Boolean postulate, x + x = x. Điều đó có nghĩa là, phép toán logic OR với bất kỳ biến Boolean nào 'n' lần sẽ bằng cùng một biến. Vì vậy, chúng ta có thể viết pqr số hạng cuối cùng hai lần nữa.

⇒ f = p'qr + pq'r + pqr '+ pqr + pqr + pqr

Step 2 - Sử dụng Distributive lawcho 1 st và 4 thứ về, 2 nd và 5 ngày điều khoản, 3 thứ 6 ngày về.

⇒ f = qr (p '+ p) + pr (q' + q) + pq (r '+ r)

Step 3 - Sử dụng Boolean postulate, x + x '= 1 để đơn giản hóa các thuật ngữ có trong mỗi dấu ngoặc đơn.

⇒ f = qr (1) + pr (1) + pq (1)

Step 4 - Sử dụng Boolean postulate, x.1 = x để đơn giản hóa ba số hạng trên.

⇒ f = qr + pr + pq

⇒ f = pq + qr + pr

Đây là hàm Boolean đơn giản hóa. Do đó,standard SoP form tương ứng với dạng SoP chuẩn đã cho là f = pq + qr + pr

Mẫu PoS tiêu chuẩn

Biểu mẫu PoS tiêu chuẩn có nghĩa là Standard Product of Sumshình thức. Ở dạng này, mỗi thuật ngữ tổng không cần chứa tất cả các chữ. Vì vậy, các điều khoản tổng có thể có hoặc không phải là các điều khoản Max. Do đó, biểu mẫu PoS chuẩn là dạng đơn giản hóa của biểu mẫu PoS chuẩn.

Chúng ta sẽ nhận được dạng chuẩn PoS của biến đầu ra trong hai bước.

- Nhận dạng PoS chuẩn của biến đầu ra

- Đơn giản hóa hàm Boolean ở trên, ở dạng PoS chính tắc.

Cũng thực hiện theo quy trình tương tự cho các biến đầu ra khác, nếu có nhiều hơn một biến đầu ra. Đôi khi, không thể đơn giản hóa biểu mẫu PoS chuẩn. Trong trường hợp đó, cả hai dạng PoS chuẩn và chuẩn đều giống nhau.

Example

Chuyển đổi hàm Boolean sau đây thành dạng PoS chuẩn.

f = (p + q + r). (p + q + r '). (p + q' + r). (p '+ q + r)

Hàm Boolean đã cho ở dạng PoS chính tắc. Bây giờ, chúng ta phải đơn giản hóa hàm Boolean này để có được biểu mẫu PoS chuẩn.

Step 1 - Sử dụng Boolean postulate, xx = x. Điều đó có nghĩa là, phép toán logic AND với bất kỳ biến Boolean nào 'n' lần sẽ bằng cùng một biến. Vì vậy, chúng ta có thể viết số hạng đầu tiên p + q + r thêm hai lần nữa.

⇒ f = (p + q + r). (P + q + r). (P + q + r). (P + q + r '). (P + q' + r). (P '+ q + r)

Step 2 - Sử dụng Distributive law,x + (yz) = (x + y). (x + z) cho 1 st và 4 thứ ngoặc, 2 nd và 5 thứ ngoặc, 3 thứ và 6 thứ ngoặc.

⇒ f = (p + q + rr '). (P + r + qq'). (Q + r + pp ')

Step 3 - Sử dụng Boolean postulate, x.x '= 0 để đơn giản hóa các thuật ngữ có trong mỗi dấu ngoặc đơn.

⇒ f = (p + q + 0). (P + r + 0). (Q + r + 0)

Step 4 - Sử dụng Boolean postulate, x + 0 = x để đơn giản hóa các thuật ngữ có trong mỗi dấu ngoặc đơn

⇒ f = (p + q). (P + r). (Q + r)

⇒ f = (p + q). (Q + r). (P + r)

Đây là hàm Boolean đơn giản hóa. Do đó,standard PoS form tương ứng với biểu mẫu PoS chuẩn nhất định là f = (p + q).(q + r).(p + r). Đây làdual của hàm Boolean, f = pq + qr + pr.

Do đó, cả hai dạng Chuẩn SoP và PoS Chuẩn là Kép với nhau.

Trong các chương trước, chúng ta đã đơn giản hóa các hàm Boolean bằng cách sử dụng các định đề và định lý Boolean. Đây là một quá trình tốn thời gian và chúng ta phải viết lại các biểu thức đã đơn giản hóa sau mỗi bước.

Để vượt qua khó khăn này, Karnaughđã giới thiệu một phương pháp đơn giản hóa các hàm Boolean một cách dễ dàng. Phương pháp này được gọi là phương pháp bản đồ Karnaugh hoặc phương pháp bản đồ K. Nó là một phương pháp đồ họa, bao gồm 2 n ô cho các biến 'n'. Các ô liền kề chỉ khác nhau ở vị trí bit đơn.

K-Maps cho 2 đến 5 biến

Phương pháp K-Map phù hợp nhất để giảm thiểu các hàm Boolean của 2 biến thành 5 biến. Bây giờ, chúng ta hãy thảo luận về K-Maps cho 2 đến 5 biến từng biến một.

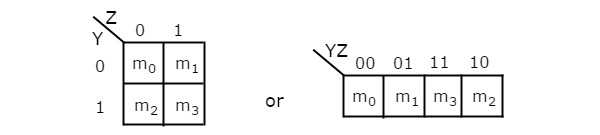

2 Bản đồ K biến

Số ô trong bản đồ K 2 biến là bốn, vì số biến là hai. Hình sau cho thấy2 variable K-Map.

Chỉ có một khả năng nhóm 4 số hạng min liền kề.

Các tổ hợp có thể có của nhóm 2 số hạng nhỏ nhất liền kề là {(m 0 , m 1 ), (m 2 , m 3 ), (m 0 , m 2 ) và (m 1 , m 3 )}.

3 Bản đồ K biến

Số ô trong 3 biến K-map là tám, vì số biến là ba. Hình sau cho thấy3 variable K-Map.

Chỉ có một khả năng nhóm 8 số hạng min liền kề.

Các tổ hợp có thể có của nhóm 4 số hạng nhỏ nhất liền kề là {(m 0 , m 1 , m 3 , m 2 ), (m 4 , m 5 , m 7 , m 6 ), (m 0 , m 1 , m 4 , m 5 ), (m 1 , m 3 , m 5 , m 7 ), (m 3 , m 2 , m 7 , m 6 ) và (m 2 , m 0 , m 6 , m 4 )}.

Các tổ hợp có thể có của nhóm 2 số hạng nhỏ nhất liền kề là {(m 0 , m 1 ), (m 1 , m 3 ), (m 3 , m 2 ), (m 2 , m 0 ), (m 4 , m 5 ) , (m 5 , m 7 ), (m 7 , m 6 ), (m 6 , m 4 ), (m 0 , m 4 ), (m 1 , m 5 ), (m 3 , m 7 ) và ( m 2 , m 6 )}.

Nếu x = 0 thì ánh xạ K 3 biến trở thành ánh xạ K 2 biến.

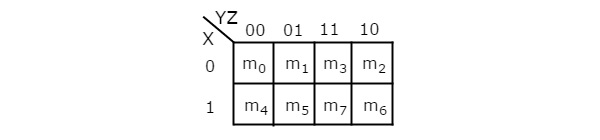

4 Bản đồ K biến

Số ô trong 4 biến K-map là mười sáu, vì số biến là bốn. Hình sau cho thấy4 variable K-Map.

Chỉ có một khả năng nhóm 16 số hạng min liền kề.

Gọi R 1 , R 2 , R 3 và R 4 lần lượt đại diện cho các số hạng tối thiểu của hàng đầu tiên, hàng thứ hai, hàng thứ ba và hàng thứ tư. Tương tự, C 1 , C 2 , C 3 và C 4 lần lượt thể hiện các số hạng tối thiểu của cột đầu tiên, cột thứ hai, cột thứ ba và cột thứ tư. Các kết hợp có thể có của nhóm 8 số hạng tối thiểu liền kề là {(R 1 , R 2 ), (R 2 , R 3 ), (R 3 , R 4 ), (R 4 , R 1 ), (C 1 , C 2 ) , (C 2 , C 3 ), (C 3 , C 4 ), (C 4 , C 1 )}.

Nếu w = 0, thì bản đồ K 4 biến trở thành bản đồ K 3 biến.

5 Bản đồ K biến

Số ô trong 5 biến K-map là ba mươi hai, vì số biến là 5. Hình sau cho thấy 5 variable K-Map.

Chỉ có một khả năng nhóm 32 số hạng min liền kề.

Có hai khả năng nhóm 16 số hạng nhỏ nhất liền kề. tức là, nhóm các số hạng nhỏ nhất từ m 0 đến m 15 và m 16 đến m 31 .

Nếu v = 0, thì bản đồ K 5 biến trở thành bản đồ K 4 biến.

Trong tất cả các bản đồ K ở trên, chúng tôi chỉ sử dụng ký hiệu thuật ngữ tối thiểu. Tương tự, bạn có thể sử dụng riêng ký hiệu điều khoản Max.

Giảm thiểu các hàm Boolean bằng K-Maps

Nếu chúng ta xem xét sự kết hợp của các đầu vào mà hàm Boolean là '1', thì chúng ta sẽ nhận được hàm Boolean, trong đó standard sum of products sau khi đơn giản hóa K-map.

Tương tự, nếu chúng ta xem xét sự kết hợp của các đầu vào mà hàm Boolean là '0', thì chúng ta sẽ nhận được hàm Boolean, trong đó standard product of sums sau khi đơn giản hóa K-map.

Làm theo những rules for simplifying K-maps để có được dạng tổng sản phẩm tiêu chuẩn.

Chọn K-map tương ứng dựa trên số lượng biến có trong hàm Boolean.

Nếu hàm Boolean được cho dưới dạng tổng của các số hạng min, thì hãy đặt chúng tại các ô số hạng min tương ứng trong K-map. Nếu hàm Boolean được cho dưới dạng tổng của các sản phẩm, thì hãy đặt các sản phẩm đó vào tất cả các ô có thể có của bản đồ K mà các điều khoản sản phẩm đã cho là hợp lệ.

Kiểm tra khả năng nhóm số lượng tối đa những cái liền kề. Nó phải là quyền hạn của hai. Bắt đầu từ công suất cao nhất của hai và tối đa là công suất nhỏ nhất của hai. Công suất cao nhất bằng số biến được xem xét trong bản đồ K và công suất nhỏ nhất bằng không.

Mỗi nhóm sẽ cung cấp một thuật ngữ theo nghĩa đen hoặc một sản phẩm. Nó được biết đến nhưprime implicant. Hàm ý chính được cho làessential prime implicant, nếu ít nhất đơn '1' không được bao phủ bởi bất kỳ nhóm nào khác mà chỉ bao gồm nhóm đó.

Ghi lại tất cả các hàm nguyên tố và hàm ý nguyên tố cần thiết. Hàm Boolean đơn giản chứa tất cả các hàm nguyên tố cần thiết và chỉ các hàm nguyên tố bắt buộc.

Note 1 - Nếu đầu ra không được xác định cho một số kết hợp đầu vào, thì các giá trị đầu ra đó sẽ được biểu diễn bằng don’t care symbol ‘x’. Điều đó có nghĩa là, chúng ta có thể coi chúng là '0' hoặc '1'.

Note 2- Nếu thuật ngữ không quan tâm cũng xuất hiện, thì địa điểm không quan tâm 'x' trong các ô tương ứng của K-map. Chỉ xem xét dấu 'x' không quan tâm hữu ích cho việc nhóm số lượng tối đa những cái liền kề. Trong những trường hợp đó, hãy coi giá trị không quan tâm là '1'.

Thí dụ

Hãy để chúng tôi simplify hàm Boolean sau đây, f(W, X, Y, Z)= WX’Y’ + WY + W’YZ’ sử dụng K-map.

Hàm Boolean đã cho có dạng tổng các sản phẩm. Nó có 4 biến W, X, Y & Z. Vì vậy, chúng tôi yêu cầu4 variable K-map. Các4 variable K-map với những người tương ứng với các điều khoản sản phẩm nhất định được hiển thị trong hình sau.

Ở đây, 1s được đặt trong các ô sau đây của K-map.

Các ô chung cho giao điểm của Hàng 4 và cột 1 & 2 tương ứng với cụm từ sản phẩm, WX’Y’.

Các ô chung cho giao điểm của Hàng 3 & 4 và cột 3 & 4 tương ứng với thuật ngữ sản phẩm, WY.

Các ô chung cho giao điểm của Hàng 1 & 2 và cột 4 tương ứng với thuật ngữ sản phẩm, W’YZ’.

Không có khả năng nhóm 16 cái liền kề hoặc 8 cái liền kề. Có ba khả năng nhóm 4 cái liền nhau. Sau ba nhóm này, không còn một nhóm nào là chưa được nhóm. Vì vậy, chúng ta không cần phải kiểm tra nhóm của 2 cái liền kề. Các4 variable K-map với ba cái này groupings được hiển thị trong hình sau.

Ở đây, chúng tôi có ba hàm ý chính WX ', WY & YZ'. Tất cả những hàm ý chính làessential bởi vì những lý do sau đây.

Hai cái (m8 & m9)của nhóm hàng thứ tư không được bao phủ bởi bất kỳ nhóm nào khác. Chỉ nhóm hàng thứ tư bao gồm hai hàng đó.

Người độc thân (m15)của nhóm hình vuông không bị bao phủ bởi bất kỳ nhóm nào khác. Chỉ nhóm hình vuông mới bao gồm nhóm đó.

Hai cái (m2 & m6)của nhóm cột thứ tư không được bao gồm bởi bất kỳ nhóm nào khác. Chỉ nhóm cột thứ tư bao gồm hai nhóm đó.

Do đó, simplified Boolean function Là

f = WX’ + WY + YZ’

Làm theo những rules for simplifying K-maps để có được sản phẩm tiêu chuẩn của dạng tổng.

Chọn K-map tương ứng dựa trên số lượng biến có trong hàm Boolean.

Nếu hàm Boolean được đưa ra dưới dạng tích của dạng số hạng Max, thì hãy đặt các số 0 tại các ô số hạng Max tương ứng trong K-map. Nếu hàm Boolean được cho dưới dạng tích của dạng tổng, thì hãy đặt các số 0 trong tất cả các ô có thể có của ánh xạ K mà các số hạng tổng đã cho là hợp lệ.

Kiểm tra khả năng nhóm số lượng số 0 liền kề tối đa. Nó phải là quyền hạn của hai. Bắt đầu từ công suất cao nhất của hai và công suất nhỏ nhất là hai. Công suất cao nhất bằng số biến được xem xét trong bản đồ K và công suất nhỏ nhất bằng không.

Mỗi nhóm sẽ cung cấp một thuật ngữ theo nghĩa đen hoặc một tổng. Nó được biết đến nhưprime implicant. Hàm ý chính được cho làessential prime implicant, nếu ít nhất đơn '0' không được bao phủ bởi bất kỳ nhóm nào khác mà chỉ bao gồm nhóm đó.

Ghi lại tất cả các hàm nguyên tố và hàm ý nguyên tố cần thiết. Hàm Boolean đơn giản chứa tất cả các hàm nguyên tố cần thiết và chỉ các hàm nguyên tố bắt buộc.

Note- Nếu thuật ngữ không quan tâm cũng xuất hiện, thì địa điểm không quan tâm 'x' trong các ô tương ứng của K-map. Chỉ xem xét dấu 'x' không quan tâm hữu ích cho việc nhóm số lượng tối đa các số 0 liền kề. Trong những trường hợp đó, hãy coi giá trị không quan tâm là '0'.

Thí dụ

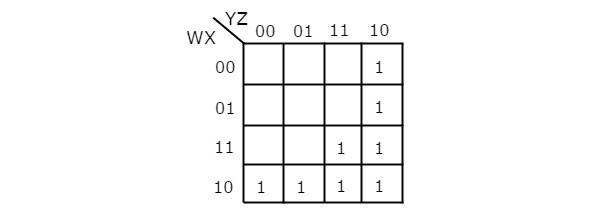

Hãy để chúng tôi simplify hàm Boolean sau đây, $f\left ( X,Y,Z \right )=\prod M\left ( 0,1,2,4 \right )$ sử dụng K-map.

Hàm Boolean đã cho là sản phẩm của dạng số hạng Max. Nó có 3 biến X, Y & Z. Vì vậy, chúng tôi yêu cầu 3 biến K-map. Các số hạng Max đã cho là M 0 , M 1 , M 2 & M 4 . 3variable K-map với các số 0 tương ứng với các số hạng Max đã cho được thể hiện trong hình sau.

Không có khả năng nhóm 8 số 0 liền kề hoặc 4 số 0 liền kề. Có ba khả năng nhóm 2 số 0 liền kề. Sau ba nhóm này, không còn số 0 nào là chưa được nhóm. Các3 variable K-map với ba cái này groupings được hiển thị trong hình sau.

Ở đây, chúng tôi có ba hàm số nguyên tố X + Y, Y + Z & Z + X. Tất cả các hàm số nguyên tố này là essential bởi vì một số 0 trong mỗi nhóm không được bao gồm bởi bất kỳ nhóm nào khác ngoại trừ các nhóm riêng lẻ của chúng.

Do đó, simplified Boolean function Là

f = (X + Y).(Y + Z).(Z + X)

Bằng cách này, chúng ta có thể dễ dàng đơn giản hóa các hàm Boolean lên đến 5 biến bằng phương pháp K-map. Đối với nhiều hơn 5 biến, rất khó để đơn giản hóa các hàm bằng K-Maps. Bởi vì, số lượngcells trong K-map được doubled bằng cách bao gồm một biến mới.

Do đó, việc kiểm tra và nhóm các số liền kề (số hạng tối thiểu) hoặc số không liền kề (số hạng tối đa) sẽ phức tạp. Chúng ta sẽ thảo luậnTabular method trong chương tiếp theo để khắc phục những khó khăn của phương pháp K-map.

Trong chương trước, chúng ta đã thảo luận về phương pháp K-map, đây là một phương pháp thuận tiện để tối thiểu hóa các hàm Boolean lên đến 5 biến. Tuy nhiên, rất khó để đơn giản hóa các hàm Boolean có nhiều hơn 5 biến bằng cách sử dụng phương pháp này.

Phương pháp bảng Quine-McClukey là một phương pháp dạng bảng dựa trên khái niệm hàm ý nguyên tố. Chúng ta biết rằngprime implicant là một số hạng tích (hoặc tổng), không thể giảm thêm bằng cách kết hợp với bất kỳ số hạng tích (hoặc tổng) nào khác của hàm Boolean đã cho.

Phương pháp dạng bảng này rất hữu ích để lấy các hàm số nguyên tố bằng cách sử dụng lặp lại nhận dạng Boolean sau đây.

xy + xy '= x (y + y') = x.1 = x

Quy trình của Phương pháp bảng Quine-McCluskey

Hãy làm theo các bước sau để đơn giản hóa các hàm Boolean bằng phương pháp bảng Quine-McClukey.

Step 1 - Sắp xếp các số hạng tối thiểu đã cho trong một ascending ordervà tạo các nhóm dựa trên số lượng nhóm có trong biểu diễn nhị phân của chúng. Vì vậy, sẽ cóat most ‘n+1’ groups nếu có 'n' biến Boolean trong một hàm Boolean hoặc 'n' bit trong hàm nhị phân tương đương với số hạng min.

Step 2 - So sánh các điều khoản tối thiểu có trong successive groups. Nếu chỉ có một thay đổi ở vị trí một bit, thì lấy cặp của hai số hạng min đó. Đặt ký hiệu '_' này ở vị trí bit khác nhau và giữ nguyên các bit còn lại.

Step 3 - Lặp lại bước 2 với các thuật ngữ mới được hình thành cho đến khi chúng ta hiểu hết prime implicants.

Step 4 - Lập công thức prime implicant table. Nó bao gồm tập hợp các hàng và cột. Hàm nguyên tố có thể được đặt trong hàng khôn ngoan và số hạng nhỏ nhất có thể được đặt trong cột khôn ngoan. Đặt '1' vào các ô tương ứng với các số hạng tối thiểu được bao hàm trong mỗi hàm ý nguyên tố.

Step 5- Tìm hàm số nguyên tố cần thiết bằng cách quan sát từng cột. Nếu số hạng tối thiểu chỉ được bao hàm bởi một hàm ý nguyên tố, thì nó làessential prime implicant. Các hàm số nguyên tố cần thiết đó sẽ là một phần của hàm Boolean đơn giản hóa.

Step 6- Giảm bảng hàm ý nguyên tố bằng cách loại bỏ hàng của mỗi hàm số nguyên tố cơ bản và các cột tương ứng với các số hạng tối thiểu được bao hàm trong hàm ý nguyên tố cần thiết đó. Lặp lại bước 5 cho bảng hàm ý nguyên tố rút gọn. Dừng quá trình này khi tất cả các số hạng tối thiểu của hàm Boolean đã cho kết thúc.

Thí dụ

Hãy để chúng tôi simplify hàm Boolean sau đây, $f\left ( W,X,Y,Z \right )=\sum m\left ( 2,6,8,9,10,11,14,15 \right )$ sử dụng phương pháp bảng Quine-McClukey.

Hàm Boolean đã cho nằm trong sum of min termshình thức. Nó có 4 biến W, X, Y & Z. Các số hạng tối thiểu đã cho là 2, 6, 8, 9, 10, 11, 14 và 15. Thứ tự tăng dần của các số hạng tối thiểu này dựa trên số hạng tử có trong chúng tương đương nhị phân là 2, 8, 6, 9, 10, 11, 14 và 15. Bảng sau đây cho thấy nhữngmin terms and their equivalent binary các đại diện.

| Tên nhóm | Điều khoản tối thiểu | W | X | Y | Z |

|---|---|---|---|---|---|

| GA1 | 2 | 0 | 0 | 1 | 0 |

| số 8 | 1 | 0 | 0 | 0 | |

| GA2 | 6 | 0 | 1 | 1 | 0 |

| 9 | 1 | 0 | 0 | 1 | |

| 10 | 1 | 0 | 1 | 0 | |

| 11 | 1 | 0 | 1 | 1 | |

| 14 | 1 | 1 | 1 | 0 | |

| GA4 | 15 | 1 | 1 | 1 | 1 |

Các số hạng tối thiểu đã cho được sắp xếp thành 4 nhóm dựa trên số lượng các số hạng có trong số tương đương nhị phân của chúng. Bảng sau đây cho thấymerging of min terms từ các nhóm liền kề.

| Tên nhóm | Điều khoản tối thiểu | W | X | Y | Z |

|---|---|---|---|---|---|

| GB1 | 2,6 | 0 | - | 1 | 0 |

| 2,10 | - | 0 | 1 | 0 | |

| 8,9 | 1 | 0 | 0 | - | |

| 8,10 | 1 | 0 | - | 0 | |

| GB2 | 6,14 | - | 1 | 1 | 0 |

| 9,11 | 1 | 0 | - | 1 | |

| 10,11 | 1 | 0 | 1 | - | |

| 10,14 | 1 | - | 1 | 0 | |

| 11,15 | 1 | - | 1 | 1 | |

| 14,15 | 1 | 1 | 1 | - |

Các số hạng min, chỉ khác ở vị trí một bit so với các nhóm liền kề được hợp nhất. Bit khác biệt đó được biểu diễn bằng ký hiệu này, '-'. Trong trường hợp này, có ba nhóm và mỗi nhóm chứa kết hợp của hai số hạng nhỏ nhất. Bảng sau đây cho thấymerging of min term pairs từ các nhóm liền kề.

| Tên nhóm | Điều khoản tối thiểu | W | X | Y | Z |

|---|---|---|---|---|---|

| GB1 | 2,6,10,14 | - | - | 1 | 0 |

| 2,10,6,14 | - | - | 1 | 0 | |

| 8,9,10,11 | 1 | 0 | - | - | |

| 8,10,9,11 | 1 | 0 | - | - | |

| GB2 | 10,11,14,15 | 1 | - | 1 | - |

| 10,14,11,15 | 1 | - | 1 | - |

Các nhóm liên tiếp của các cặp số hạng min, chỉ khác nhau ở vị trí một bit được hợp nhất. Bit khác biệt đó được biểu diễn bằng ký hiệu này, '-'. Trong trường hợp này, có hai nhóm và mỗi nhóm chứa các kết hợp của bốn số hạng nhỏ nhất. Ở đây, các kết hợp 4 số hạng tối thiểu này có sẵn trong hai hàng. Vì vậy, chúng ta có thể loại bỏ các hàng lặp lại. Bảng thu gọn sau khi loại bỏ các hàng thừa được hiển thị bên dưới.

| Tên nhóm | Điều khoản tối thiểu | W | X | Y | Z |

|---|---|---|---|---|---|

| GC1 | 2,6,10,14 | - | - | 1 | 0 |

| 8,9,10,11 | 1 | 0 | - | - | |

| GC2 | 10,11,14,15 | 1 | - | 1 | - |

Việc hợp nhất thêm các tổ hợp số hạng min từ các nhóm liền kề là không thể, vì chúng khác nhau ở vị trí nhiều hơn một bit. Có ba hàng trong bảng trên. Vì vậy, mỗi hàng sẽ cho một hàm ý nguyên tố. Do đó,prime implicants là YZ ', WX' & WY.

Các prime implicant table được hiển thị bên dưới.

| Điều khoản tối thiểu / Hàm ý chính | 2 | 6 | số 8 | 9 | 10 | 11 | 14 | 15 |

|---|---|---|---|---|---|---|---|---|

| YZ’ | 1 | 1 | 1 | 1 | ||||

| WX’ | 1 | 1 | 1 | 1 | ||||

| WY | 1 | 1 | 1 | 1 |

Hàm nguyên tố được đặt trong hàng khôn ngoan và số hạng nhỏ nhất được đặt trong cột khôn ngoan. 1s được đặt trong các ô chung của các hàng hàm ý nguyên tố và các cột số hạng tối thiểu tương ứng.

Các số hạng tối thiểu 2 và 6 chỉ được bao hàm bởi một hàm ý nguyên tố YZ’. Vì vậy, nó là mộtessential prime implicant. Đây sẽ là một phần của hàm Boolean đơn giản hóa. Bây giờ, hãy xóa hàng hàm ý nguyên tố này và các cột số hạng tối thiểu tương ứng. Bảng hàm ý nguyên tố rút gọn được hiển thị bên dưới.

| Điều khoản tối thiểu / Hàm ý chính | số 8 | 9 | 11 | 15 |

|---|---|---|---|---|

| WX’ | 1 | 1 | 1 | |

| WY | 1 | 1 |

Các số hạng tối thiểu 8 và 9 chỉ được bao hàm bởi một hàm ý chính WX’. Vì vậy, nó là mộtessential prime implicant. Đây sẽ là một phần của hàm Boolean đơn giản hóa. Bây giờ, hãy xóa hàng hàm ý nguyên tố này và các cột số hạng tối thiểu tương ứng. Bảng hàm ý nguyên tố rút gọn được hiển thị bên dưới.

| Điều khoản tối thiểu / Hàm ý chính | 15 |

|---|---|

| WY | 1 |

Thuật ngữ tối thiểu 15 chỉ được bao hàm bởi một hàm ý chính WY. Vì vậy, nó là mộtessential prime implicant. Đây sẽ là một phần của hàm Boolean đơn giản hóa.

Trong bài toán ví dụ này, chúng ta có ba hàm số nguyên tố và cả ba hàm ý đều cần thiết. Do đó,simplified Boolean function Là

f(W,X,Y,Z) = YZ’ + WX’ + WY.

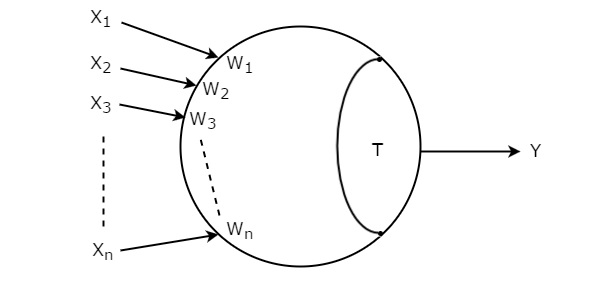

Các mạch điện tử kỹ thuật số hoạt động với điện áp của two logic levelscụ thể là Logic Low và Logic High. Phạm vi điện áp tương ứng với Logic Low được biểu thị bằng '0'. Tương tự, phạm vi điện áp tương ứng với Cao Logic được biểu thị bằng '1'.

Mạch điện tử kỹ thuật số cơ bản có một hoặc nhiều đầu vào và đầu ra duy nhất được gọi là Logic gate. Do đó, cổng Logic là khối xây dựng của bất kỳ hệ thống kỹ thuật số nào. Chúng ta có thể phân loại các cổng Logic này thành ba loại sau.

- Cổng cơ bản

- Cổng chung

- Cổng đặc biệt

Bây giờ, chúng ta hãy thảo luận về các cổng Logic theo từng loại một.

Cổng cơ bản

Trong các chương trước, chúng ta đã biết rằng các hàm Boolean có thể được biểu diễn ở dạng tổng của sản phẩm hoặc dạng tích của dạng tổng dựa trên yêu cầu. Vì vậy, chúng ta có thể thực hiện các hàm Boolean này bằng cách sử dụng các cổng cơ bản. Các cổng cơ bản là cổng VÀ, HOẶC & KHÔNG.

Và cổng

Cổng AND là một mạch kỹ thuật số có hai hoặc nhiều đầu vào và tạo ra một đầu ra, là logical ANDcủa tất cả các đầu vào đó. Nó là tùy chọn để đại diện choLogical AND với ký hiệu '.'.

Bảng sau đây cho thấy truth table cổng AND 2 đầu vào.

| A | B | Y = AB |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Ở đây A, B là đầu vào và Y là đầu ra của hai cổng AND đầu vào. Nếu cả hai đầu vào là '1', thì chỉ có đầu ra, Y là '1'. Đối với các kết hợp đầu vào còn lại, đầu ra, Y là '0'.

Hình sau cho thấy symbol của một cổng AND, có hai đầu vào A, B và một đầu ra, Y.

Cổng AND này tạo ra một đầu ra (Y), là logical ANDcủa hai đầu vào A, B. Tương tự, nếu có 'n' đầu vào, thì cổng AND tạo ra một đầu ra, là AND logic của tất cả các đầu vào đó. Điều đó có nghĩa là, đầu ra của cổng AND sẽ là '1', khi tất cả các đầu vào là '1'.

Cổng HOẶC

Cổng OR là một mạch kỹ thuật số có hai hoặc nhiều đầu vào và tạo ra một đầu ra, là OR logic của tất cả các đầu vào đó. Điều nàylogical OR được biểu diễn bằng ký hiệu '+'.

Bảng sau đây cho thấy truth table cổng OR 2 đầu vào.

| A | B | Y = A + B |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Ở đây A, B là đầu vào và Y là đầu ra của hai cổng OR đầu vào. Nếu cả hai đầu vào là '0', thì chỉ có đầu ra, Y là '0'. Đối với các kết hợp đầu vào còn lại, đầu ra, Y là '1'.

Hình sau cho thấy symbol của một cổng OR, có hai đầu vào A, B và một đầu ra, Y.

Cổng OR này tạo ra một đầu ra (Y), là logical ORcủa hai đầu vào A, B. Tương tự, nếu có 'n' đầu vào, thì cổng OR tạo ra một đầu ra, là OR logic của tất cả các đầu vào đó. Điều đó có nghĩa là, đầu ra của cổng OR sẽ là '1', khi ít nhất một trong những đầu vào đó là '1'.

Cổng KHÔNG

Cổng NOT là một mạch kỹ thuật số có một đầu vào và một đầu ra. Đầu ra của cổng NOT làlogical inversioncủa đầu vào. Do đó, cổng NOT còn được gọi là biến tần.

Bảng sau đây cho thấy truth table của cổng NOT.

| A | Y = A ' |

|---|---|

| 0 | 1 |

| 1 | 0 |

Ở đây A và Y lần lượt là đầu vào và đầu ra của cổng NOT. Nếu đầu vào, A là '0', thì đầu ra, Y là '1'. Tương tự, nếu đầu vào, A là '1', thì đầu ra, Y là '0'.

Hình sau cho thấy symbol của cổng NOT, có một đầu vào, A và một đầu ra, Y.

Cổng NOT này tạo ra một đầu ra (Y), là complement của đầu vào, A.

Cổng chung

Cổng NAND & NOR được gọi là universal gates. Bởi vì chúng ta có thể triển khai bất kỳ hàm Boolean nào, có dạng tổng hợp các sản phẩm bằng cách sử dụng cổng NAND một mình. Tương tự, chúng ta có thể triển khai bất kỳ hàm Boolean nào, ở dạng tích số bằng cách sử dụng cổng NOR một mình.

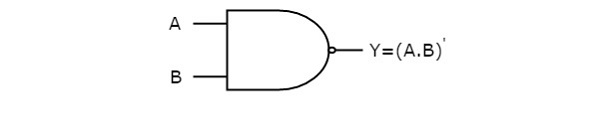

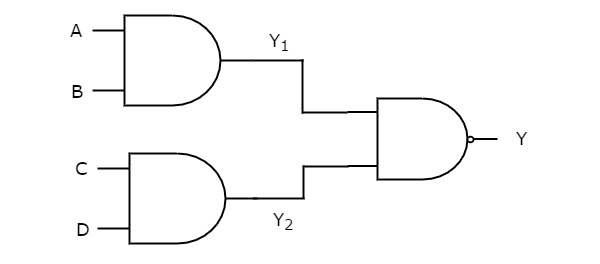

Cổng NAND

Cổng NAND là một mạch kỹ thuật số có hai hoặc nhiều đầu vào và tạo ra một đầu ra, là inversion of logical AND của tất cả các đầu vào đó.

Bảng sau đây cho thấy truth table cổng NAND 2 đầu vào.

| A | B | Y = (AB) ' |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Ở đây A, B là đầu vào và Y là đầu ra của hai cổng NAND đầu vào. Khi cả hai đầu vào là '1', đầu ra, Y là '0'. Nếu ít nhất một trong các đầu vào là 0, thì đầu ra, Y là '1'. Điều này hoàn toàn ngược lại với hoạt động của hai cổng AND đầu vào.

Hình ảnh sau đây cho thấy symbol của cổng NAND, có hai đầu vào A, B và một đầu ra, Y.

Hoạt động của cổng NAND giống như hoạt động của cổng AND theo sau bởi một biến tần. Đó là lý do tại sao biểu tượng cổng NAND được biểu diễn như vậy.

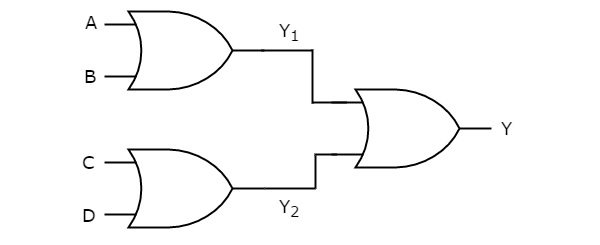

Cổng NOR

Cổng NOR là một mạch kỹ thuật số có hai đầu vào trở lên và tạo ra một đầu ra, là inversion of logical OR của tất cả các đầu vào đó.

Bảng sau đây cho thấy truth table cổng NOR 2 đầu vào

| A | B | Y = (A + B) ' |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

Ở đây A, B là đầu vào và Y là đầu ra. Nếu cả hai đầu vào là '0', thì đầu ra, Y là '1'. Nếu ít nhất một trong các đầu vào là '1', thì đầu ra, Y là '0'. Điều này trái ngược với hoạt động của hai cổng OR đầu vào.

Hình sau cho thấy symbol của cổng NOR, có hai đầu vào A, B và một đầu ra, Y.

Hoạt động của cổng NOR cũng giống như hoạt động của cổng OR theo sau bởi một biến tần. Đó là lý do tại sao biểu tượng cổng NOR được biểu diễn như vậy.

Cổng đặc biệt

Cổng Ex-OR & Ex-NOR được gọi là cổng đặc biệt. Bởi vì, hai cửa này là trường hợp đặc biệt của cửa OR & NOR.

Cổng Ex-OR

Dạng đầy đủ của cổng Ex-OR là Exclusive-ORcánh cổng. Chức năng của nó giống như chức năng của cổng OR ngoại trừ một số trường hợp, khi các đầu vào có số lượng chẵn.

Bảng sau đây cho thấy truth table cổng Ex-OR 2 đầu vào.

| A | B | Y = A⊕B |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

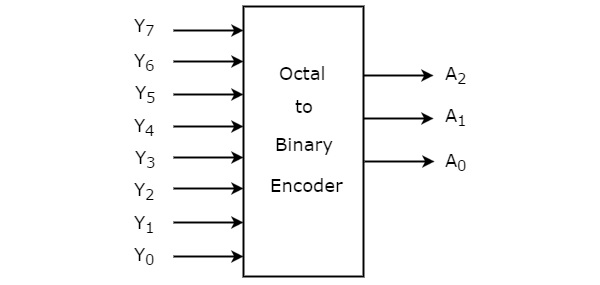

| 1 | 1 | 0 |