Przetworniki ADC typu bezpośredniego

Przetwornik analogowo-cyfrowy (ADC)konwertuje sygnał analogowy na sygnał cyfrowy. Sygnał cyfrowy jest reprezentowany za pomocą kodu binarnego, który jest kombinacją bitów 0 i 1.

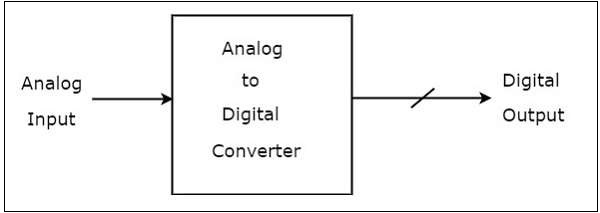

Plik block diagram ADC pokazano na poniższym rysunku -

Zauważ, że na powyższym rysunku jest konwerter analogowo-cyfrowy (ADC)składa się z jednego wejścia analogowego i wielu wyjść binarnych. Ogólnie rzecz biorąc, liczba wyjść binarnych ADC będzie potęgą dwóch.

Tam są two typesADC: ADC typu bezpośredniego i ADC typu pośredniego. W tym rozdziale szczegółowo omówiono przetworniki ADC typu bezpośredniego.

Jeśli przetwornik ADC wykonuje konwersję analogowo-cyfrową bezpośrednio, wykorzystując wewnętrznie wygenerowany równoważny kod cyfrowy (binarny) do porównania z wejściem analogowym, wówczas jest nazywany Direct type ADC.

Poniżej znajdują się pliki examples przetworników ADC typu bezpośredniego -

- Licznik typu ADC

- Kolejne przybliżenie ADC

- Flash typu ADC

W tej sekcji szczegółowo omówiono te przetworniki ADC typu bezpośredniego.

Licznik typu ADC

ZA counter type ADC generuje wyjście cyfrowe, które jest w przybliżeniu równe wejściu analogowemu, używając wewnętrznie operacji licznika.

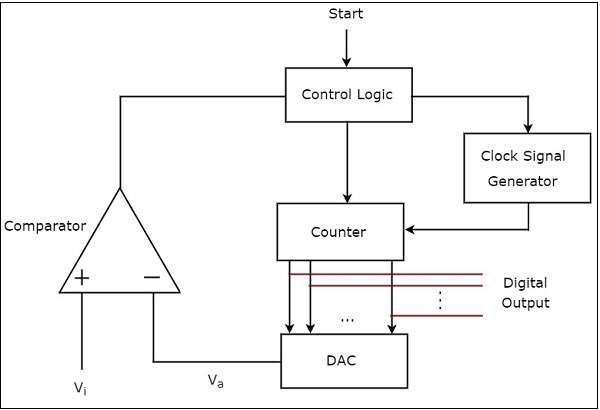

Plik block diagram licznika typu ADC pokazano na poniższym rysunku -

Licznik ADC składa się głównie z 5 bloków: generator sygnału zegarowego, licznik, DAC, komparator i logika sterująca.

Plik working licznika typu ADC jest następująca -

Plik control logic zeruje licznik i włącza generator sygnału zegarowego w celu wysyłania impulsów zegarowych do licznika po otrzymaniu sygnału rozkazu startu.

Plik counterjest zwiększana o jeden dla każdego impulsu zegara, a jego wartość będzie w formacie binarnym (cyfrowym). To wyjście licznika jest stosowane jako wejście DAC.

DACkonwertuje otrzymane wejście binarne (cyfrowe), które jest wyjściem licznika, na wyjście analogowe. Komparator porównuje tę wartość analogową $ V_ {a} $ z wartością zewnętrznego wejścia analogowego $ V_ {i} $.

Plik output of comparator będzie ‘1’tak długo, jak jest większe niż. Operacje wymienione w powyższych dwóch krokach będą kontynuowane tak długo, jak logika sterująca otrzyma „1” z wyjścia komparatora.

Plik output of comparator będzie ‘0’kiedy $ V_ {i} $ jest mniejsze lub równe $ V_ {a} $. Zatem logika sterująca otrzymuje „0” z wyjścia komparatora. Następnie logika sterująca wyłącza generator sygnału zegara, aby nie wysyłał żadnego impulsu zegarowego do licznika.

W tym momencie wyjście licznika zostanie wyświetlone jako digital output. Jest to prawie równoważne odpowiedniej wartości zewnętrznego wejścia analogowego $ V_ {i} $.

Kolejne przybliżenie ADC

ZA successive approximation type ADC generuje wyjście cyfrowe, które jest w przybliżeniu równe wejściu analogowemu dzięki wewnętrznemu zastosowaniu techniki sukcesywnego przybliżania.

Plik block diagram kolejnego przybliżenia ADC pokazano na poniższym rysunku

Kolejny przetwornik ADC z aproksymacją składa się głównie z 5 bloków - generatora sygnału zegarowego, rejestru kolejnych aproksymacji (SAR), przetwornika cyfrowo-analogowego, komparatora i logiki sterującej.

Plik working kolejnego przybliżenia ADC wygląda następująco -

Plik control logic resetuje wszystkie bity SAR i włącza generator sygnału zegarowego w celu wysyłania impulsów zegara do SAR, gdy otrzyma sygnał rozkazujący start.

Dane binarne (cyfrowe) obecne w SARbędzie aktualizowana dla każdego impulsu zegara w oparciu o wyjście komparatora. Wyjście SAR jest stosowane jako wejście DAC.

DAC konwertuje odebrane wejście cyfrowe, które jest wyjściem SAR, na wyjście analogowe. Komparator porównuje tę wartość analogową $ V_ {a} $ z wartością zewnętrznego wejścia analogowego $ V_ {i} $.

Plik output of a comparatorbędzie wynosić „1”, o ile $ V_ {i} $ będzie większe niż $ V_ {a} $. Podobnie, wynikiem komparatora będzie „0”, gdy $ V_ {i} $ jest mniejsze lub równe $ V_ {a} $.

Operacje wymienione w powyższych krokach będą kontynuowane do momentu, gdy wyjście cyfrowe będzie prawidłowe.

Wyjście cyfrowe będzie prawidłowe, gdy jest prawie równoważne odpowiedniej wartości zewnętrznego wejścia analogowego $ V_ {i} $.

Flash typu ADC

ZA flash type ADCw krótkim czasie wytwarza równoważne wyjście cyfrowe dla odpowiedniego wejścia analogowego. Dlatego też ADC typu flash jest najszybszym ADC.

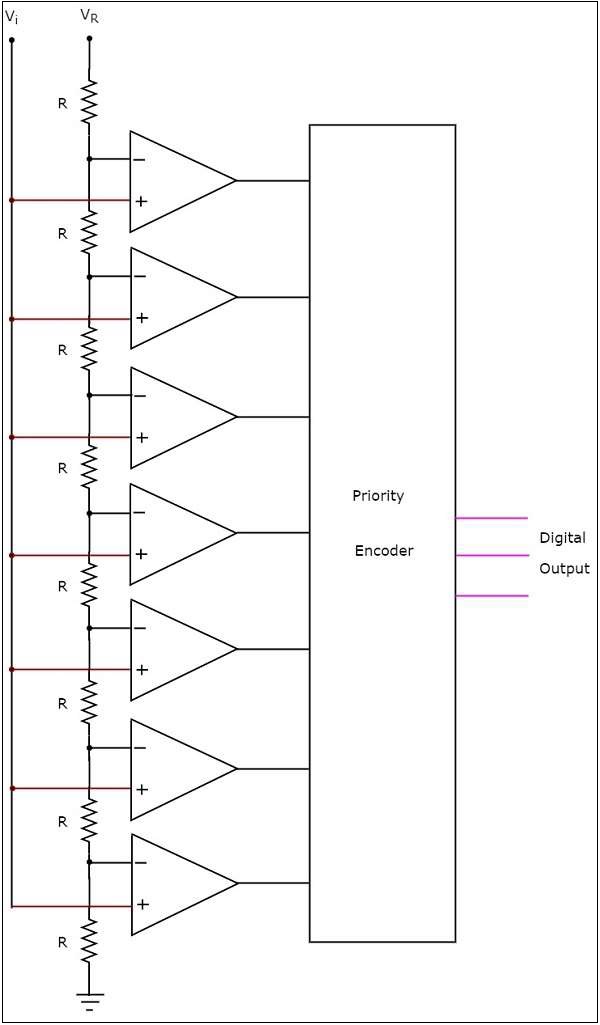

Plik circuit diagram 3-bitowego przetwornika ADC typu flash pokazano na poniższym rysunku -

3-bitowy przetwornik ADC typu flash składa się z sieci dzielnika napięcia, 7 komparatorów i kodera priorytetowego.

Plik working 3-bitowego ADC typu flash jest następująca.

Plik voltage divider networkzawiera 8 równych rezystorów. Napięcie odniesienia $ V_ {R} $ jest przykładane do całej sieci względem ziemi. Spadek napięcia na każdym rezystorze od dołu do góry w stosunku do masy będzie całkowitą wielokrotnością (od 1 do 8) $ \ frac {V_ {R}} {8} $.

Zewnętrzne input voltage$ V_ {i} $ jest stosowane do nieodwracającego zacisku wszystkich komparatorów. Spadek napięcia na każdym rezystorze od dołu do góry w stosunku do masy jest przykładany do zacisku odwracającego komparatorów od dołu do góry.

W danym momencie wszystkie komparatory porównują zewnętrzne napięcie wejściowe ze spadkami napięcia występującymi na odpowiednim innym zacisku wejściowym. Oznacza to, że operacje porównania są wykonywane przez każdy komparatorparallelly.

Plik output of the comparatorbędzie wynosić '1', o ile $ V_ {i} $ będzie większe niż spadek napięcia na odpowiednim innym zacisku wejściowym. Podobnie, wyjście komparatora będzie miało wartość „0”, gdy $ V_ {i} $ jest mniejsze lub równe spadkowi napięcia obecnemu na odpowiednim innym zacisku wejściowym.

Wszystkie wyjścia komparatorów są połączone jako wejścia priority encoderTen enkoder priorytetowy wytwarza kod binarny (wyjście cyfrowe), który odpowiada wejściu o wysokim priorytecie, które ma „1”.

Dlatego wyjście enkodera priorytetowego jest niczym innym jak odpowiednikiem binarnym (digital output) zewnętrznego analogowego napięcia wejściowego, $ V_ {i} $.

Przetwornik ADC typu flash jest używany w aplikacjach, w których szybkość konwersji wejścia analogowego na dane cyfrowe powinna być bardzo wysoka.