Podstawy układów scalonych

Na electronic circuit to grupa elementów elektronicznych połączonych w określonym celu.

Prosty obwód elektroniczny można łatwo zaprojektować, ponieważ wymaga kilku dyskretnych elementów elektronicznych i połączeń. Jednak zaprojektowanie złożonego układu elektronicznego jest trudne, ponieważ wymaga większej liczby dyskretnych elementów elektronicznych i ich połączeń. Zbudowanie tak złożonych obwodów zajmuje również dużo czasu, a ich niezawodność również jest mniejsza. Te trudności można pokonać za pomocą układów scalonych.

Układ scalony (IC)

Jeśli wiele elementów elektronicznych jest połączonych ze sobą na jednym chipie z materiału półprzewodnikowego, wówczas układ ten nazywany jest jako Integrated Circuit (IC). Składa się z elementów aktywnych i pasywnych.

W tym rozdziale omówiono zalety i typy układów scalonych.

Zalety układów scalonych

Układy scalone mają wiele zalet. Omówiono je poniżej -

Compact size - W przypadku danej funkcjonalności można uzyskać obwód o mniejszych rozmiarach za pomocą układów scalonych w porównaniu do obwodu zbudowanego przy użyciu obwodu dyskretnego.

Lesser weight- Obwód zbudowany z układów scalonych waży mniej w porównaniu z wagą obwodu dyskretnego używanego do realizacji tej samej funkcji układu scalonego. przy użyciu układów scalonych, w porównaniu do tego zbudowanego przy użyciu obwodu dyskretnego.

Low power consumption - Układy scalone zużywają mniej energii niż tradycyjne obwody ze względu na ich mniejszy rozmiar i konstrukcję.

Reduced cost - Układy scalone są dostępne po znacznie niższych kosztach niż obwody dyskretne ze względu na technologie ich wytwarzania i użycie mniejszego materiału niż obwody dyskretne.

Increased reliability - Ponieważ wykorzystują mniej połączeń, układy scalone zapewniają większą niezawodność w porównaniu z obwodami cyfrowymi.

Improved operating speeds - Układy scalone działają z większą prędkością ze względu na ich szybkości przełączania i mniejsze zużycie energii.

Rodzaje układów scalonych

Układy scalone są dwojakiego rodzaju − Analog Integrated Circuits and Digital Integrated Circuits.

Analogowe układy scalone

Układy scalone działające w całym zakresie ciągłych wartości amplitudy sygnału nazywane są jako Analog Integrated Circuits. Są one dalej podzielone na dwa typy, jak omówiono tutaj -

Linear Integrated Circuits- O analogowym układzie scalonym mówi się, że jest liniowy, jeśli istnieje liniowa zależność między jego napięciem a prądem. Przykładem liniowego układu scalonego jest IC 741, 8-pinowy podwójny w-liniowy wzmacniacz (DIP).

Radio Frequency Integrated Circuits- O analogowym układzie scalonym mówi się, że jest nieliniowy, jeśli istnieje nieliniowa zależność między jego napięciem a prądem. Nieliniowy układ scalony jest również nazywany układem scalonym częstotliwości radiowej.

Cyfrowe układy scalone

Jeżeli układy scalone działają tylko na kilku z góry określonych poziomach, zamiast pracować dla całego zakresu ciągłych wartości amplitudy sygnału, to nazywane są one jako Digital Integrated Circuits.

W następnych rozdziałach omówimy różne liniowe układy scalone i ich zastosowania.

Wzmacniacz operacyjny, zwany również wzmacniaczem operacyjnym, to układ scalony, który może być używany do wykonywania różnych operacji liniowych, nieliniowych i matematycznych. Wzmacniacz operacyjny todirect coupled high gain amplifier. Możesz obsługiwać wzmacniacz operacyjny zarówno z sygnałami AC, jak i DC. W tym rozdziale omówiono cechy i typy wzmacniaczy operacyjnych.

Budowa wzmacniacza operacyjnego

Wzmacniacz operacyjny składa się ze wzmacniacza (-ów) różnicowego (-ych), translatora poziomów i stopnia wyjściowego. Wzmacniacz różnicowy jest obecny na stopniu wejściowym wzmacniacza operacyjnego, a zatem składa się z wzmacniacza operacyjnegotwo input terminals. Jeden z tych terminali nosi nazwęinverting terminal a drugi nazywa się non-inverting terminal. Terminale są nazwane na podstawie relacji fazowych między ich odpowiednimi wejściami i wyjściami.

Charakterystyka wzmacniacza operacyjnego

Istotne cechy lub parametry wzmacniacza operacyjnego są następujące -

- Wzmocnienie napięcia w otwartej pętli

- Napięcie wyjściowe offsetu

- Współczynnik odrzucenia w trybie wspólnym

- Szybkość opadania

W tej sekcji szczegółowo omówiono te cechy, jak podano poniżej -

Wzmocnienie napięcia w otwartej pętli

Wzmocnienie napięcia w otwartej pętli wzmacniacza operacyjnego to wzmocnienie różnicowe bez ścieżki sprzężenia zwrotnego.

Matematycznie wzmocnienie napięcia w otwartej pętli wzmacniacza operacyjnego jest przedstawiane jako -

$$A_{v}= \frac{v_0}{v_1-v_2}$$

Napięcie wyjściowe offsetu

Napięcie obecne na wyjściu wzmacniacza operacyjnego, gdy jego różnicowe napięcie wejściowe wynosi zero, nazywane jest jako output offset voltage.

Współczynnik odrzucenia w trybie wspólnym

Współczynnik odrzucenia w trybie wspólnym (CMRR) wzmacniacza operacyjnego definiuje się jako stosunek wzmocnienia różnicowego w pętli zamkniętej, $A_{d}$ i wzmocnienie w trybie wspólnym, $A_{c}$.

Matematycznie CMRR można przedstawić jako -

$$CMRR=\frac{A_{d}}{A_{c}}$$

Zwróć uwagę, że wzmocnienie w trybie wspólnym, $A_{c}$ wzmacniacza operacyjnego to stosunek napięcia wyjściowego w trybie wspólnym do napięcia wejściowego w trybie wspólnym.

Szybkość opadania

Szybkość narastania wzmacniacza operacyjnego jest definiowana jako maksymalna szybkość zmian napięcia wyjściowego spowodowana skokowym napięciem wejściowym.

Matematycznie szybkość zmian (SR) można przedstawić jako -

$$SR=Maximum\:of\:\frac{\text{d}V_{0}}{\text{d}t}$$

Gdzie, $V_{0}$to napięcie wyjściowe. Ogólnie szybkość narastania jest mierzona w obu$V/\mu\:Sec$ lub $V/m\:Sec$.

Rodzaje wzmacniaczy operacyjnych

Wzmacniacz operacyjny jest reprezentowany przez symbol trójkąta z dwoma wejściami i jednym wyjściem.

Istnieją dwa typy wzmacniaczy operacyjnych: Ideal Op-Amp i Practical Op-Amp.

Są szczegółowo omówione, jak podano poniżej -

Idealny wzmacniacz operacyjny

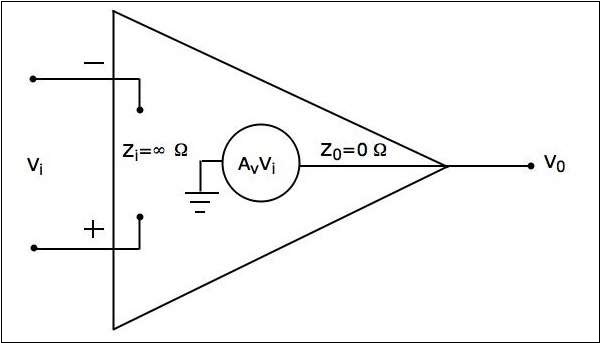

Idealny wzmacniacz operacyjny istnieje tylko w teorii i praktycznie nie istnieje. Plikequivalent circuit idealnego wzmacniacza operacyjnego pokazano na poniższym rysunku -

Na ideal op-amp wykazuje następujące cechy -

Impedancja wejściowa $Z_{i}=\infty\Omega$

Impedancja wyjściowa $Z_{0}=0\Omega$

Wzmocnienie napięcia w otwartej pętli $A_{v}=\infty$

Jeśli (różnicowe) napięcie wejściowe $V_{i}=0V$, wtedy napięcie wyjściowe będzie $V_{0}=0V$

Przepustowość to infinity. Oznacza to, że idealny wzmacniacz operacyjny wzmocni sygnały o dowolnej częstotliwości bez żadnego tłumienia.

Współczynnik odrzucenia w trybie wspólnym (CMRR) jest infinity.

Szybkość opadania (SR) jest infinity. Oznacza to, że idealny wzmacniacz operacyjny spowoduje zmianę na wyjściu natychmiast w odpowiedzi na wejściowe napięcie krokowe.

Praktyczny wzmacniacz operacyjny

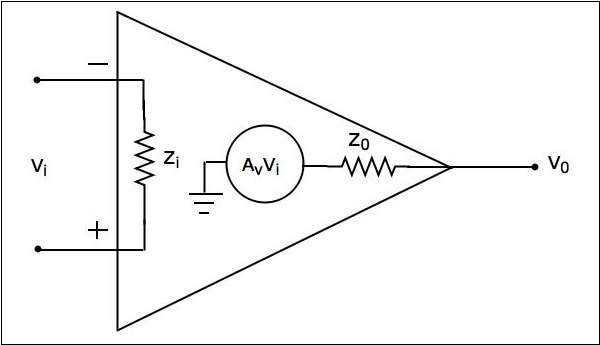

Praktycznie wzmacniacze operacyjne nie są idealne i odbiegają od swoich idealnych cech z powodu pewnych niedoskonałości podczas produkcji. Plikequivalent circuit praktycznego wzmacniacza operacyjnego pokazano na poniższym rysunku -

ZA practical op-amp wykazuje następujące cechy -

Impedancja wejściowa, $Z_{i}$ w kolejności Mega ohms.

Impedancja wyjściowa, $Z_{0}$ w kolejności few ohms..

Wzmocnienie napięcia w otwartej pętli, $A_{v}$ będzie high.

Wybierając praktyczny wzmacniacz operacyjny, należy sprawdzić, czy spełnia on następujące warunki -

Impedancja wejściowa, $Z_{i}$ powinien być jak najwyższy.

Impedancja wyjściowa, $Z_{0}$ powinien być jak najniższy.

Wzmocnienie napięcia w otwartej pętli, $A_{v}$ powinien być jak najwyższy.

Napięcie wyjściowe offsetu powinno być jak najniższe.

Operacyjna przepustowość powinna być jak najwyższa.

CMRR powinien być jak najwyższy.

Szybkość narastania powinna być jak najwyższa.

Note - Wzmacniacz operacyjny IC 741 jest najpopularniejszym i najbardziej praktycznym wzmacniaczem operacyjnym.

Mówi się, że to obwód linear, jeśli istnieje liniowa zależność między jego wejściem a wyjściem. Podobnie mówi się o obwodzienon-linear, jeśli istnieje nieliniowa zależność między wejściem a wyjściem.

Wzmacniacze operacyjne mogą być używane zarówno w zastosowaniach liniowych, jak i nieliniowych. Poniżej przedstawiono podstawowe zastosowania wzmacniacza operacyjnego -

- Wzmacniacz odwracający

- Wzmacniacz nieodwracający

- Popychacz napięcia

W tym rozdziale szczegółowo omówiono te podstawowe aplikacje.

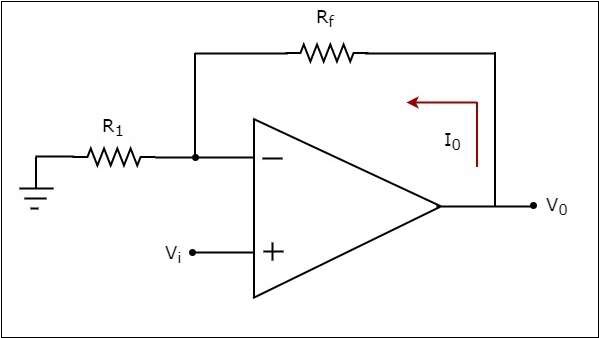

Wzmacniacz odwracający

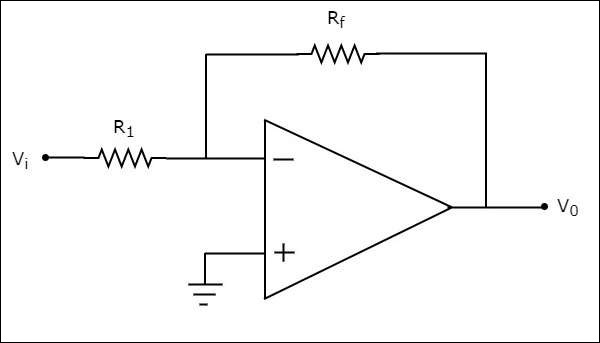

Wzmacniacz odwracający pobiera sygnał wejściowy przez swój zacisk odwracający przez rezystor $R_{1}$i produkuje swoją wzmocnioną wersję jako wyjście. Wzmacniacz ten nie tylko wzmacnia wejście, ale też je odwraca (zmienia jego znak).

Plik circuit diagram wzmacniacza odwracającego pokazano na poniższym rysunku -

Należy zauważyć, że w przypadku wzmacniacza operacyjnego napięcie na odwracającym zacisku wejściowym jest równe napięciu na jego nieodwracającym zacisku wejściowym. Fizycznie nie ma zwarcia między tymi dwoma terminalami, alevirtually, są w short ze sobą.

W pokazanym powyżej obwodzie nieodwracający zacisk wejściowy jest podłączony do masy. Oznacza to, że do nieodwracającego zacisku wejściowego wzmacniacza operacyjnego podawane jest zero woltów.

Według virtual short concept, napięcie na odwracającym zacisku wejściowym wzmacniacza operacyjnego będzie wynosić zero woltów.

Plik nodal equation w węźle tego terminala jest pokazane poniżej -

$$\frac{0-V_i}{R_1}+ \frac{0-V_0}{R_f}=0$$

$$=>\frac{-V_i}{R_1}= \frac{V_0}{R_f}$$

$$=>V_{0}=\left(\frac{-R_f}{R_1}\right)V_{t}$$

$$=>\frac{V_0}{V_i}= \frac{-R_f}{R_1}$$

Stosunek napięcia wyjściowego $V_{0}$ i napięcie wejściowe $V_{i}$oznacza wzmocnienie lub wzmocnienie napięcia wzmacniacza. Dlatego teżgain of inverting amplifier jest równe $-\frac{R_f}{R_1}$.

Zauważ, że wzmocnienie wzmacniacza odwracającego ma negative sign. Wskazuje, że istnieje różnica faz 180 0 między wejściem a wyjściem.

Wzmacniacz nieodwracający

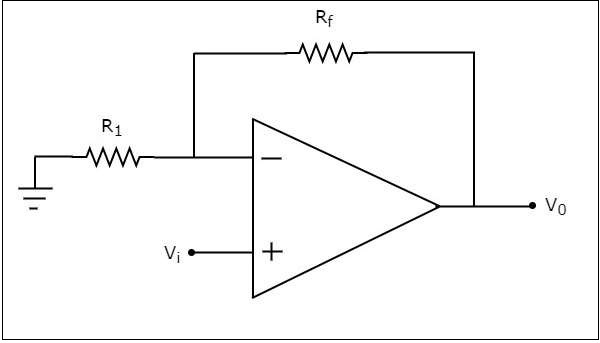

Wzmacniacz nieodwracający pobiera sygnał wejściowy przez swój nieodwracający zacisk i wytwarza wzmocnioną wersję jako wyjście. Jak nazwa sugeruje, wzmacniacz ten po prostu wzmacnia wejście, nie odwracając ani nie zmieniając znaku wyjścia.

Plik circuit diagram Wzmacniacza nieodwracającego pokazano na poniższym rysunku -

W powyższym obwodzie napięcie wejściowe $V_{i}$jest bezpośrednio stosowany do nieodwracającego zacisku wejściowego wzmacniacza operacyjnego. Tak więc napięcie na nieodwracającym zacisku wejściowym wzmacniacza operacyjnego będzie wynosić$V_{i}$.

Używając voltage division principle, możemy obliczyć napięcie na odwracającym zacisku wejściowym wzmacniacza operacyjnego, jak pokazano poniżej -

$$=>V_{1} = V_{0}\left(\frac{R_1}{R_1+R_f}\right)$$

Według virtual short concept, napięcie na odwracającym zacisku wejściowym wzmacniacza operacyjnego jest takie samo, jak napięcie na jego nieodwracającym zacisku wejściowym.

$$=>V_{1} = V_{i}$$

$$=>V_{0}\left(\frac{R_1}{R_1+R_f}\right)=V_{i}$$

$$=>\frac{V_0}{V_i}=\frac{R_1+R_f}{R_1}$$

$$=>\frac{V_0}{V_i}=1+\frac{R_f}{R_1}$$

Teraz stosunek napięcia wyjściowego $V_{0}$ i napięcie wejściowe $V_{i}$ lub wzmocnienie napięcia lub gain of the non-inverting amplifier jest równe $1+\frac{R_f}{R_1}$.

Zauważ, że wzmocnienie nieodwracającego wzmacniacza ma positive sign. Wskazuje, że nie ma różnicy faz między wejściem a wyjściem.

Popychacz napięcia

ZA voltage followerjest obwodem elektronicznym, który wytwarza wyjście zgodne z napięciem wejściowym. Jest to szczególny przypadek wzmacniacza nieodwracającego.

Jeśli weźmiemy pod uwagę wartość rezystora sprzężenia zwrotnego, $R_{f}$jako zero omów i (lub) wartość rezystora, 1 jako nieskończoność omów, wówczas nieodwracający wzmacniacz staje się wtórnikiem napięcia. Plikcircuit diagram wtórnika napięcia pokazano na poniższym rysunku -

W powyższym obwodzie napięcie wejściowe $V_{i}$jest bezpośrednio stosowany do nieodwracającego zacisku wejściowego wzmacniacza operacyjnego. Zatem napięcie na nieodwracającym zacisku wejściowym wzmacniacza operacyjnego jest równe$V_{i}$. Tutaj wyjście jest bezpośrednio podłączone do odwracającego zacisku wejściowego opampa. Stąd napięcie na odwracającym zacisku wejściowym wzmacniacza operacyjnego jest równe$V_{0}$.

Według virtual short concept, napięcie na odwracającym zacisku wejściowym wzmacniacza operacyjnego jest takie samo, jak napięcie na jego nieodwracającym zacisku wejściowym.

$$=>V_{0} = V_{i}$$

Więc napięcie wyjściowe $V_{0}$ wtórnika napięcia jest równe jego napięciu wejściowemu $V_{i}$.

Więc gain of a voltage follower jest równe jeden, ponieważ oba napięcie wyjściowe $V_{0}$ i napięcie wejściowe $V_{i}$ popychacza napięcia są takie same.

W poprzednim rozdziale omówiliśmy podstawowe zastosowania wzmacniacza operacyjnego. Zauważ, że podlegają one liniowym operacjom wzmacniacza operacyjnego. W tym rozdziale omówimy obwody arytmetyczne, które są również liniowymi zastosowaniami wzmacniacza operacyjnego.

Obwody elektroniczne, które wykonują operacje arytmetyczne, nazywane są jako arithmetic circuits. Korzystając ze wzmacniaczy operacyjnych, możesz zbudować podstawowe obwody arytmetyczne, takie jakadder i a subtractor. W tym rozdziale szczegółowo poznasz każdą z nich.

Sumator

Sumator to obwód elektroniczny, który wytwarza wyjście, które jest równe sumie zastosowanych wejść. W tej sekcji omówiono obwód sumatora oparty na wzmacniaczu operacyjnym.

Sumator oparty na wzmacniaczu operacyjnym wytwarza sygnał wyjściowy równy sumie napięć wejściowych przyłożonych do jego zacisku odwracającego. Jest również nazywany jakosumming amplifier, ponieważ wyjście jest wzmocnione.

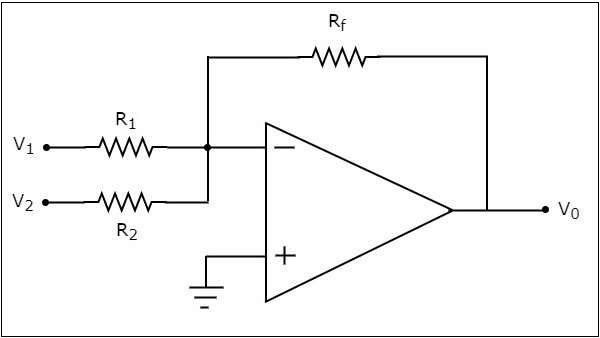

Plik circuit diagram dodatku opartego na wzmacniaczu operacyjnym pokazano na poniższym rysunku -

W powyższym obwodzie nieodwracający zacisk wejściowy wzmacniacza operacyjnego jest podłączony do masy. Oznacza to, że na jego nieodwracającym zacisku wejściowym podawane jest zero woltów.

Według virtual short concept, napięcie na odwracającym zacisku wejściowym wzmacniacza operacyjnego jest takie samo, jak napięcie na jego nieodwracającym zacisku wejściowym. Zatem napięcie na odwracającym zacisku wejściowym wzmacniacza operacyjnego będzie wynosić zero woltów.

Plik nodal equation w węźle odwracającego terminala wejściowego jest

$$\frac{0-V_1}{R_1}+\frac{0-V_2}{R_2}+\frac{0-V_0}{R_f}=0$$

$$=>\frac{V_1}{R_1}-\frac{V_2}{R_2}=\frac{V_0}{R_f}$$

$$=>V_{0}=R_{f}\left(\frac{V_1}{R_1}+\frac{V_2}{R_2}\right)$$

Gdyby $R_{f}=R_{1}=R_{2}=R$, a następnie napięcie wyjściowe $V_{0}$ będzie -

$$V_{0}=-R{}\left(\frac{V_1}{R}+\frac{V_2}{R}\right)$$

$$=>V_{0}=-(V_{1}+V_{2})$$

Dlatego obwód sumatora oparty na wzmacniaczu operacyjnym omówiony powyżej będzie wytwarzał sumę dwóch napięć wejściowych $v_{1}$ i $v_{1}$jako wyjście, gdy wszystkie rezystory obecne w obwodzie mają tę samą wartość. Zauważ, że napięcie wyjściowe$V_{0}$ obwodu sumatora ma negative sign, co wskazuje, że istnieje różnica faz 180 0 między wejściem a wyjściem.

Odejmowanie

Odejmowanie to obwód elektroniczny, który wytwarza sygnał wyjściowy równy różnicy zastosowanych wejść. W tej sekcji omówiono obwód odejmowania oparty na wzmacniaczu operacyjnym.

Odejmowanie oparte na wzmacniaczu operacyjnym wytwarza sygnał wyjściowy równy różnicy napięć wejściowych przyłożonych na jego zaciskach odwracających i nieodwracających. Jest również nazywany jakodifference amplifier, ponieważ wyjście jest wzmocnione.

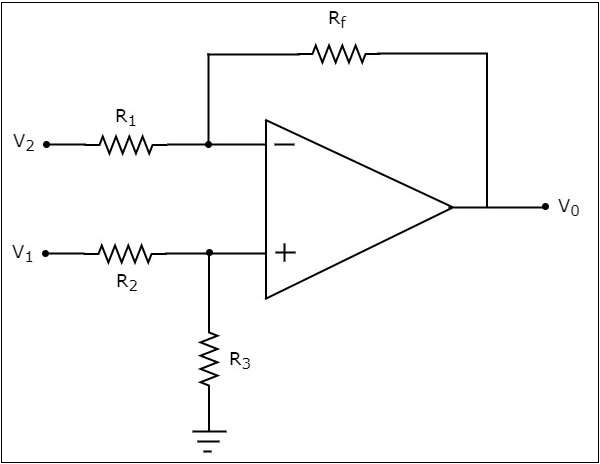

Plik circuit diagram odejmowania opartego na wzmacniaczu operacyjnym pokazano na poniższym rysunku -

Teraz znajdźmy wyrażenie na napięcie wyjściowe $V_{0}$ powyższego obwodu za pomocą superposition theorem wykonując następujące kroki -

Krok 1

Po pierwsze, obliczmy napięcie wyjściowe $V_{01}$ rozważając tylko $V_{1}$.

W tym celu wyeliminuj $V_{2}$powodując zwarcie. Następnie otrzymujemy plikmodified circuit diagram jak pokazano na poniższym rysunku -

Teraz używając voltage division principleobliczyć napięcie na nieodwracającym zacisku wejściowym wzmacniacza operacyjnego.

$$=>V_{p}=V_{1}\left(\frac{R_3}{R_2+R_3}\right)$$

Teraz powyższy obwód wygląda jak nieodwracający wzmacniacz o napięciu wejściowym $V_{p}$. Dlatego napięcie wyjściowe$V_{01}$ powyższego obwodu będzie

$$V_{01}=V_{p}\left(1+\frac{R_f}{R_1}\right)$$

Zastąpienie, wartość $V_{p}$ w powyższym równaniu otrzymujemy napięcie wyjściowe $V_{01}$ rozważając tylko $V_{1}$, ponieważ -

$$V_{01}=V_{1}\left(\frac{R_3}{R_2+R_3}\right)\left(1+\frac{R_f}{R_1}\right)$$

Krok 2

W tym kroku znajdźmy napięcie wyjściowe, $V_{02}$ rozważając tylko $V_{2}$. Podobnie jak w powyższym kroku, wyeliminuj$V_{1}$powodując zwarcie. Plikmodified circuit diagram pokazano na poniższym rysunku.

Można zauważyć, że napięcie na nieodwracającym zacisku wejściowym wzmacniacza operacyjnego będzie wynosić zero woltów. Oznacza to, że powyższy obwód jest po prostu plikieminverting op-amp. Dlatego napięcie wyjściowe$V_{02}$ powyższego obwodu będzie -

$$V_{02}=\left(-\frac{R_f}{R_1}\right)V_{2}$$

Krok 3

W tym kroku uzyskamy napięcie wyjściowe $V_{0}$ obwodu odejmowania wg adding the output voltagesuzyskane w Kroku 1 i Kroku 2. Matematycznie można to zapisać jako

$$V_{0}=V_{01}+V_{02}$$

Podstawiając wartości $V_{01}$ i $V_{02}$ w powyższym równaniu otrzymujemy -

$$V_{0}=V_{1}\left(\frac{R_3}{R_2+R_3}\right)\left(1+\frac{R_f}{R_1}\right)+\left(-\frac{R_f}{R_1}\right)V_{2}$$

$$=>V_{0}=V_{1}\left(\frac{R_3}{R_2+R_3}\right)\left(1+\frac{R_f}{R_1}\right)-\left(\frac{R_f}{R_1}\right)V_{2}$$

Gdyby $R_{f}=R_{1}=R_{2}=R_{3}=R$, a następnie napięcie wyjściowe $V_{0}$ będzie

$$V_{0}=V_{1}\left(\frac{R}{R+R}\right)\left(1+\frac{R}{R}\right)-\left(\frac{R}{R}\right)V_{2}$$

$$=>V_{0}=V_{1}\left(\frac{R}{2R}\right)(2)-(1)V_{2}$$

$$V_{0}=V_{1}-V_{2}$$

Tak więc obwód odejmujący oparty na wzmacniaczu operacyjnym omówiony powyżej będzie generował wyjście, które jest różnicą dwóch napięć wejściowych $V_{1}$ i $V_{2}$, gdy wszystkie rezystory obecne w obwodzie mają tę samą wartość.

Układy elektroniczne, które wykonują operacje matematyczne, takie jak różniczkowanie i całkowanie, nazywane są odpowiednio różniczkownikiem i integratorem.

W tym rozdziale szczegółowo omówiono technologię opartą na wzmacniaczu operacyjnym differentiatori integrator. Należy pamiętać, że są one również objęte liniowymi zastosowaniami wzmacniacza operacyjnego.

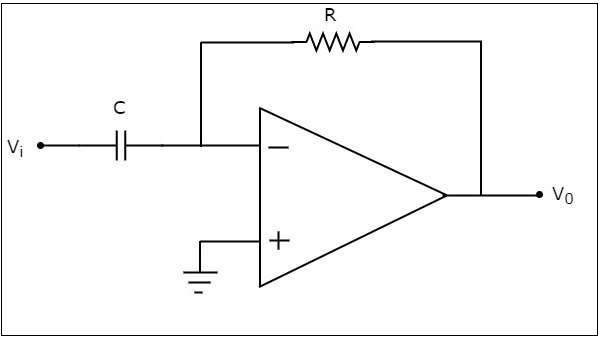

Różnica

ZA differentiatorto obwód elektroniczny, który wytwarza sygnał wyjściowy równy pierwszej pochodnej swojego wejścia. W tej sekcji szczegółowo omówiono różnicę opartą na wzmacniaczu operacyjnym.

Rozróżniacz oparty na wzmacniaczu operacyjnym wytwarza sygnał wyjściowy, który jest równy różnicy napięcia wejściowego, które jest przyłożone do jego zacisku odwracającego. Plikcircuit diagram na poniższym rysunku przedstawiono układ różnicowy oparty na wzmacniaczu operacyjnym -

W powyższym obwodzie nieodwracający zacisk wejściowy wzmacniacza operacyjnego jest podłączony do masy. Oznacza to, że do nieodwracającego zacisku wejściowego podawane jest zero woltów.

Według virtual short concept, napięcie na odwracającym zacisku wejściowym wzmacniacza operacyjnego będzie równe napięciu obecnemu na jego nieodwracającym zacisku wejściowym. Zatem napięcie na odwracającym zacisku wejściowym wzmacniacza operacyjnego będzie wynosić zero woltów.

Równanie węzłowe w odwracającym węźle wejściowym to -

$$C\frac{\text{d}(0-V_{i})}{\text{d}t}+\frac{0-V_0}{R}=0$$

$$=>-C\frac{\text{d}V_{i}}{\text{d}t}=\frac{V_0}{R}$$

$$=>V_{0}=-RC\frac{\text{d}V_{i}}{\text{d}t}$$

Gdyby $RC=1\sec$, a następnie napięcie wyjściowe $V_{0}$ będzie -

$$V_{0}=-\frac{\text{d}V_{i}}{\text{d}t}$$

Zatem pokazany powyżej obwód różnicujący oparty na wzmacniaczu operacyjnym będzie generował wyjście, które jest różnicą napięcia wejściowego $V_{i}$, gdy wielkości impedancji rezystora i kondensatora są wzajemne.

Zauważ, że napięcie wyjściowe $V_{0}$ ma negative sign, co wskazuje, że istnieje różnica faz 180 0 między wejściem a wyjściem.

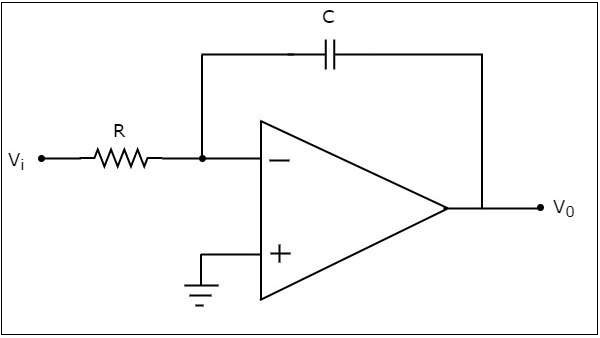

Integrator

Na integratorjest obwodem elektronicznym, który wytwarza sygnał wyjściowy będący integracją zastosowanego wejścia. W tej sekcji omówiono integrator oparty na wzmacniaczu operacyjnym.

Integrator oparty na wzmacniaczu operacyjnym generuje wyjście, które jest całką napięcia wejściowego przyłożonego do jego zacisku odwracającego. Plikcircuit diagram integratora opartego na wzmacniaczu operacyjnym pokazano na poniższym rysunku -

W powyższym obwodzie nieodwracający zacisk wejściowy wzmacniacza operacyjnego jest podłączony do masy. Oznacza to, że do nieodwracającego zacisku wejściowego podawane jest zero woltów.

Według virtual short concept, napięcie na odwracającym zacisku wejściowym wzmacniacza operacyjnego będzie równe napięciu obecnemu na jego nieodwracającym zacisku wejściowym. Zatem napięcie na odwracającym zacisku wejściowym wzmacniacza operacyjnego będzie wynosić zero woltów.

Plik nodal equation na zacisku wejścia odwracającego jest -

$$\frac{0-V_i}{R}+C\frac{\text{d}(0-V_{0})}{\text{d}t}=0$$

$$=>\frac{-V_i}{R}=C\frac{\text{d}V_{0}}{\text{d}t}$$

$$=>\frac{\text{d}V_{0}}{\text{d}t}=-\frac{V_i}{RC}$$

$$=>{d}V_{0}=\left(-\frac{V_i}{RC}\right){\text{d}t}$$

Całkując obie strony powyższego równania, otrzymujemy -

$$\int{d}V_{0}=\int\left(-\frac{V_i}{RC}\right){\text{d}t}$$

$$=>V_{0}=-\frac{1}{RC}\int V_{t}{\text{d}t}$$

Gdyby $RC=1\sec$, następnie napięcie wyjściowe, $V_{0}$ będzie -

$$V_{0}=-\int V_{i}{\text{d}t}$$

Tak więc obwód integratora oparty na wzmacniaczu operacyjnym omówiony powyżej wytworzy wyjście, które jest całką napięcia wejściowego $V_{i}$, gdy wielkości impedancji rezystora i kondensatora są wzajemne.

Note - napięcie wyjściowe, $V_{0}$ ma negative sign, co oznacza, że istnieje 180 0 różnicy faz między wejściem a wyjściem.

Napięcie i prąd to podstawowe wielkości elektryczne. W zależności od wymagań można je łączyć ze sobą.Voltage to Current Converter i Bieżący do Voltage Converterto dwa obwody, które pomagają w takiej konwersji. Są to również liniowe zastosowania wzmacniaczy operacyjnych. W tym rozdziale omówiono je szczegółowo.

Konwerter napięcia na prąd

ZA voltage to current converter lub V to I converter, jest obwodem elektronicznym, który pobiera prąd jako wejście i wytwarza napięcie jako wyjście. W tej sekcji omówiono konwerter napięcia na prąd oparty na wzmacniaczu operacyjnym.

Przetwornik napięcia na prąd oparty na wzmacniaczu operacyjnym wytwarza prąd wyjściowy, gdy napięcie jest przyłożone do jego nieodwracającego zacisku. Plikcircuit diagram konwertera napięcia na prąd na podstawie wzmacniacza operacyjnego pokazano na poniższym rysunku.

W powyższym obwodzie napięcie wejściowe $V_{i}$jest stosowany na nieodwracającym zacisku wejściowym wzmacniacza operacyjnego. Wedługvirtual short concept, napięcie na odwracającym zacisku wejściowym wzmacniacza operacyjnego będzie równe napięciu na jego nieodwracającym zacisku wejściowym. Tak więc napięcie na odwracającym zacisku wejściowym wzmacniacza operacyjnego będzie$V_{i}$.

Plik nodal equation w węźle odwracającego terminala wejściowego jest -

$$\frac{V_i}{R_1}-I_{0}=0$$

$$=>I_{0}=\frac{V_t}{R_1}$$

Więc output current $I_{0}$ konwertera napięcia na prąd to stosunek jego napięcia wejściowego $V_{i}$ i opór $R_{1}$.

Możemy przepisać powyższe równanie jako -

$$\frac{I_0}{V_i}=\frac{1}{R_1}$$

Powyższe równanie przedstawia stosunek prądu wyjściowego $I_{0}$ i napięcie wejściowe $V_{i}$ i jest równa odwrotności oporu $R_{1}$ Stosunek prądu wyjściowego $I_{0}$ i napięcie wejściowe $V_{i}$ nazywa się jako Transconductance.

Wiemy, że stosunek wyjścia i wejścia obwodu nazywa się wzmocnieniem. Zatem wzmocnienie konwertera napięcia na prąd jest transkonduktancją i jest równe odwrotności oporu$R_{1}$.

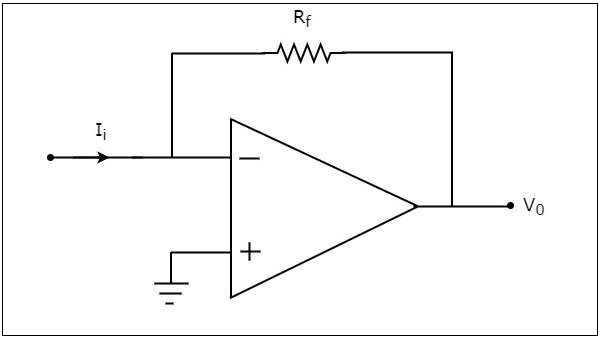

Konwerter prądu na napięcie

ZA current to voltage converter lub I to V converterjest obwodem elektronicznym, który pobiera prąd jako wejście i wytwarza napięcie jako wyjście. W tej sekcji omówiono konwerter prądu na napięcie oparty na wzmacniaczu operacyjnym.

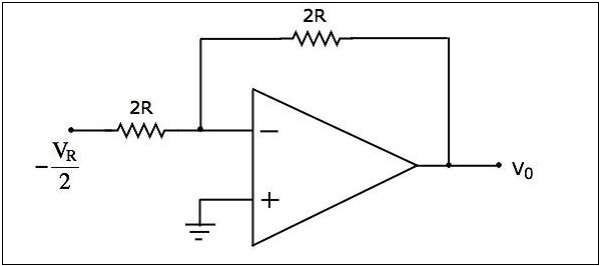

Przetwornik prądu na napięcie oparty na wzmacniaczu operacyjnym wytwarza napięcie wyjściowe, gdy prąd jest doprowadzany do jego zacisku odwracającego. Plikcircuit diagram na poniższym rysunku pokazano konwerter prądu na napięcie oparty na wzmacniaczu operacyjnym.

W powyższym obwodzie nieodwracający zacisk wejściowy wzmacniacza operacyjnego jest podłączony do masy. Oznacza to, że na jego nieodwracającym zacisku wejściowym podawane jest zero woltów.

Według virtual short concept, napięcie na odwracającym zacisku wejściowym wzmacniacza operacyjnego będzie równe napięciu na jego nieodwracającym zacisku wejściowym. Zatem napięcie na odwracającym zacisku wejściowym wzmacniacza operacyjnego będzie wynosić zero woltów.

Plik nodal equation w węźle terminala odwracającego jest -

$$-I_{i}+\frac{0-V_0}{R_f}=0$$

$$-I_{i}=\frac{V_0}{R_f}$$

$$V_{0}=-R_{t}I_{i}$$

Więc output voltage, $V_{0}$ konwertera prądu na napięcie jest (ujemnym) iloczynem rezystancji sprzężenia zwrotnego, $R_{f}$ i prąd wejściowy, $I_{t}$. Zwróć uwagę, że napięcie wyjściowe,$V_{0}$ ma negative sign, co wskazuje, że istnieje różnica faz 180 0 między prądem wejściowym a napięciem wyjściowym.

Możemy przepisać powyższe równanie jako -

$$\frac{V_0}{I_i}=-R_{f}$$

Powyższe równanie przedstawia stosunek napięcia wyjściowego $V_{0}$ i prąd wejściowy $I_{i}$i jest równe ujemnemu oporze sprzężenia zwrotnego, $R_{f}$. Stosunek napięcia wyjściowego$V_{0}$ i prąd wejściowy $I_{i}$ nazywa się jako Transresistance.

Wiemy, że stosunek wyjścia i wejścia obwodu nazywa się as gain. Zatem wzmocnienie przetwornika prądu na napięcie jest jego rezystancją trans i jest równe (ujemnej) rezystancji sprzężenia zwrotnego$R_{f}$ .

ZA comparatorjest obwodem elektronicznym, który porównuje dwa wejścia, które są do niego przyłożone, i generuje wyjście. Wartość wyjściowa komparatora wskazuje, które z wejść jest większe lub mniejsze. Należy pamiętać, że komparator podlega nieliniowym zastosowaniom układów scalonych.

Wzmacniacz operacyjny składa się z dwóch zacisków wejściowych, dlatego komparator oparty na wzmacniaczu operacyjnym porównuje dwa wejścia, które są do niego podłączone, i generuje wynik porównania jako wyjście. W tym rozdziale omówiono tematop-amp based comparators.

Typy komparatorów

Komparatory są dwojakiego rodzaju: Inverting i Non-inverting. W tej sekcji szczegółowo omówiono te dwa typy.

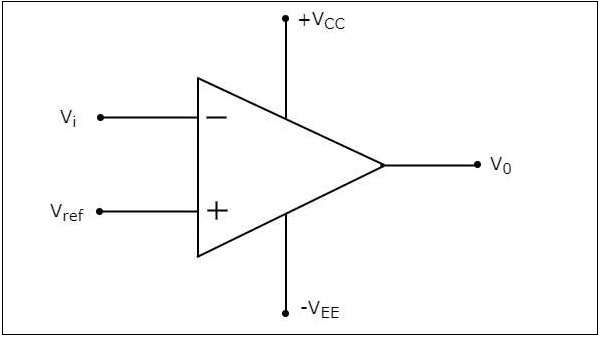

Odwracający komparator

Na inverting comparatorjest komparatorem opartym na wzmacniaczu operacyjnym, dla którego napięcie odniesienia jest przykładane do jego nieodwracającego zacisku, a napięcie wejściowe jest przykładane do jego zacisku odwracającego. Ten komparator nosi nazwęinverting komparatora, ponieważ napięcie wejściowe, które należy porównać, jest przykładane do zacisku odwracającego wzmacniacza operacyjnego.

Plik circuit diagram odwracającego komparatora pokazano na poniższym rysunku.

Plik operationodwracającego komparatora jest bardzo proste. Wytwarza jedną z dwóch wartości,$+V_{sat}$ i $-V_{sat}$ na wyjściu w oparciu o wartości jego napięcia wejściowego $V_{i}$ i napięcie odniesienia $V_{ref}$.

Wartość wyjściowa komparatora odwracającego będzie wynosić $-V_{sat}$, dla którego dane wejściowe $V_{i}$ napięcie jest większe niż napięcie odniesienia $V_{ref}$.

Wartość wyjściowa komparatora odwracającego będzie wynosić $+V_{sat}$, dla którego dane wejściowe $V_{i}$ jest mniejsze niż napięcie odniesienia $V_{ref}$.

Przykład

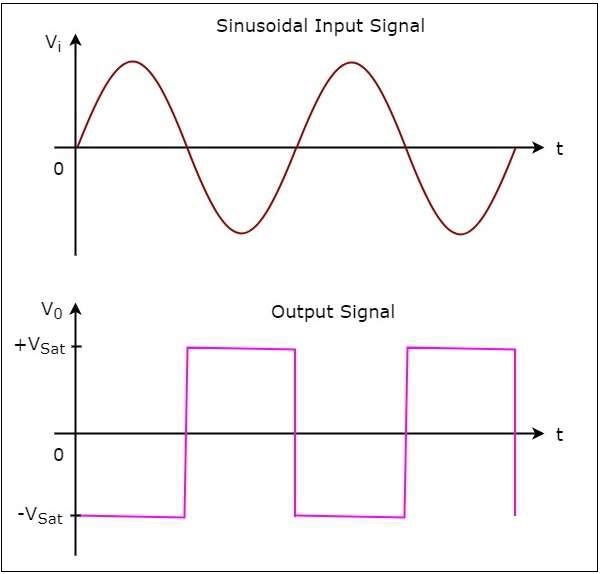

Narysujmy output wave form komparatora odwracającego, gdy sinusoidalny sygnał wejściowy i napięcie odniesienia równe zero woltów są przykładane odpowiednio do jego zacisków odwracających i nieodwracających.

Plik operation komparatora odwracającego pokazanego powyżej omówiono poniżej -

Podczas positive half cyclesinusoidalnego sygnału wejściowego, napięcie obecne na zacisku odwracającym wzmacniacza operacyjnego jest większe od zera woltów. Stąd wartość wyjściowa komparatora odwracającego będzie równa$-V_{sat}$ podczas dodatniego półcyklu sinusoidalnego sygnału wejściowego.

Podobnie podczas negative half cyclesinusoidalnego sygnału wejściowego, napięcie obecne na zacisku odwracającym wzmacniacza operacyjnego jest mniejsze od zera woltów. Stąd wartość wyjściowa komparatora odwracającego będzie równa$+V_{sat}$ podczas ujemnego półcyklu sinusoidalnego sygnału wejściowego.

Poniższy rysunek przedstawia input and output waveforms komparatora odwracającego, gdy napięcie odniesienia wynosi zero woltów.

Na powyższym rysunku możemy zauważyć, że wyjście przechodzi z $-V_{sat}$ do $+V_{sat}$ lub z $+V_{sat}$ do $-V_{sat}$ilekroć sinusoidalny sygnał wejściowy przekracza zero woltów. Innymi słowy, wyjście zmienia swoją wartość, gdy wejście przekracza zero woltów. Stąd powyższy obwód jest również nazywany jakoinverting zero crossing detector.

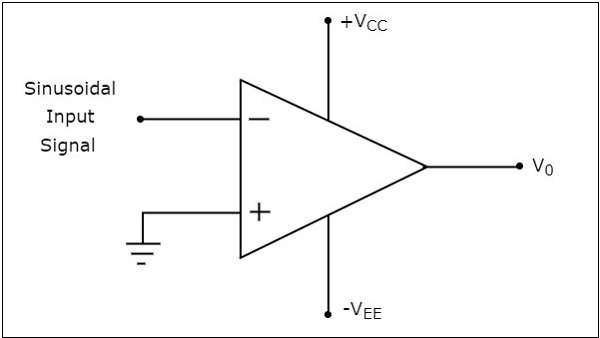

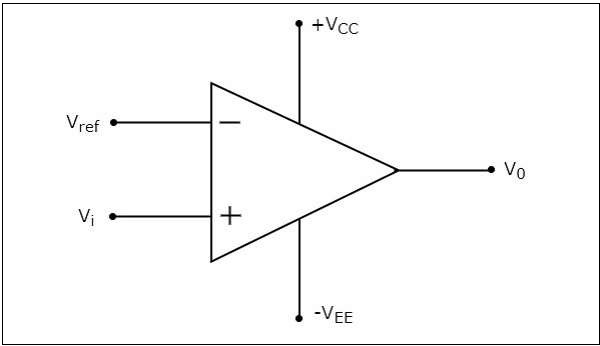

Nieodwracający komparator

Nieodwracający komparator to komparator oparty na wzmacniaczu operacyjnym, dla którego napięcie odniesienia jest przykładane do jego zacisku odwracającego, a napięcie wejściowe jest przykładane do jego nieodwracającego zacisku. Ten komparator oparty na wzmacniaczu operacyjnym nosi nazwęnon-inverting komparatora, ponieważ napięcie wejściowe, które należy porównać, jest doprowadzane do nieodwracającego zacisku wzmacniacza operacyjnego.

Plik circuit diagram komparatora nieodwracającego pokazano na poniższym rysunku

Plik operationkomparatora nieodwracającego jest bardzo proste. Wytwarza jedną z dwóch wartości,$+V_{sat}$ i $-V_{sat}$ na wyjściu w oparciu o wartości napięcia wejściowego $V_{t}$ i napięcie odniesienia $+V_{ref}$.

Wartość wyjściowa komparatora nieodwracającego będzie wynosić $+V_{sat}$, dla którego napięcie wejściowe $V_{i}$ jest większe niż napięcie odniesienia $+V_{ref}$.

Wartość wyjściowa komparatora nieodwracającego będzie bee $-V_{sat}$, dla którego napięcie wejściowe $V_{i}$ jest mniejsze niż napięcie odniesienia $+V_{ref}$.

Przykład

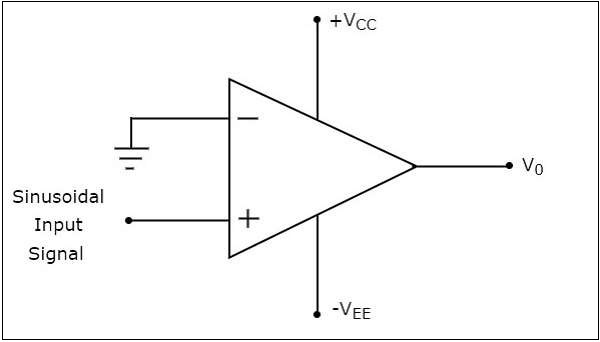

Narysujmy output wave form komparatora nieodwracającego, gdy sinusoidalny sygnał wejściowy i napięcie odniesienia wynoszące zero woltów są przykładane do nieodwracających i odwracających zacisków wzmacniacza operacyjnego.

Plik operation komparatora nieodwracającego wyjaśniono poniżej -

Podczas positive half cyclesinusoidalnego sygnału wejściowego, napięcie obecne na nieodwracającym zacisku wzmacniacza operacyjnego jest większe od zera woltów. W związku z tym wartość wyjściowa nieodwracającego komparatora będzie równa$+V_{sat}$ podczas dodatniego półcyklu sinusoidalnego sygnału wejściowego.

Podobnie podczas negative half cyclesinusoidalnego sygnału wejściowego, napięcie obecne na nieodwracającym zacisku wzmacniacza operacyjnego jest mniejsze od zera woltów. Stąd wartość wyjściowa komparatora nieodwracającego będzie równa$-V_{sat}$ podczas ujemnego półcyklu sinusoidalnego sygnału wejściowego.

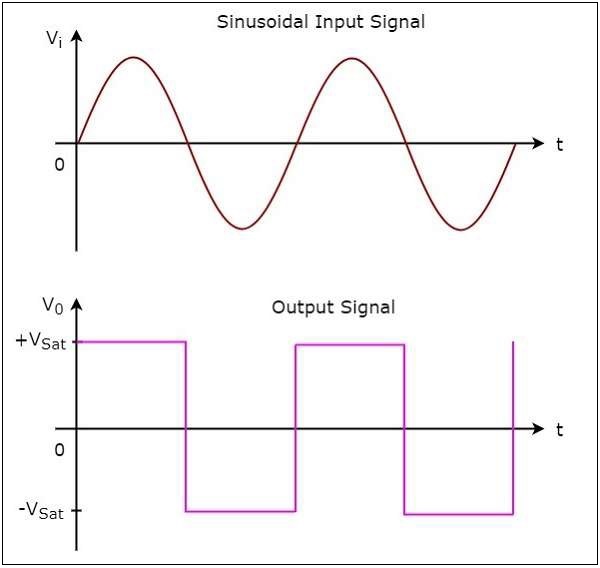

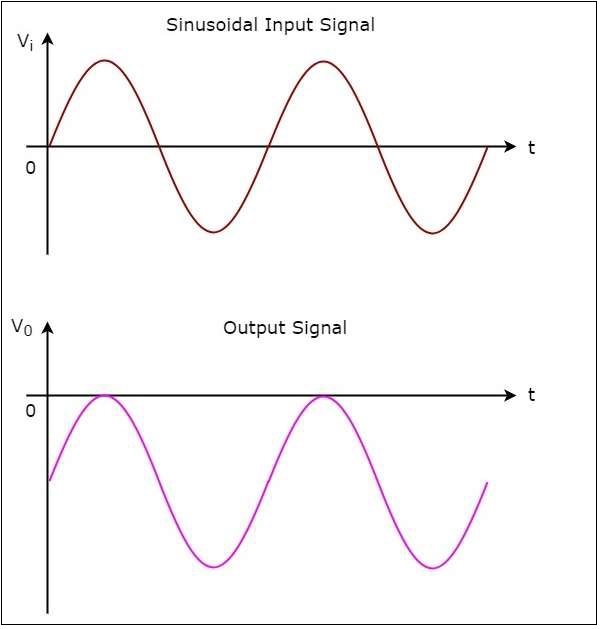

Poniższy rysunek przedstawia input and output waveforms komparatora nieodwracającego, gdy napięcie odniesienia wynosi zero woltów.

Na powyższym rysunku możemy zauważyć, że wyjście przechodzi z $+V_{sat}$ do $-V_{sat}$ lub z $-V_{sat}$ do $+V_{sat}$ilekroć sinusoidalny sygnał wejściowy przekracza zero woltów. Oznacza to, że wyjście zmienia swoją wartość, gdy wejście przekracza zero woltów. Stąd powyższy obwód jest również nazywany jakonon-inverting zero crossing detector.

Obwody elektroniczne, które wykonują operacje matematyczne, takie jak logarytm i antylogarytm (wykładniczy) ze wzmocnieniem, nazywane są Logarithmic amplifier i Anti-Logarithmic amplifier odpowiednio.

W tym rozdziale omówiono temat Logarithmic amplifier i Anti-Logarithmic amplifierszczegółowo. Należy pamiętać, że te wzmacniacze są przeznaczone do zastosowań nieliniowych.

Wzmacniacz logarytmiczny

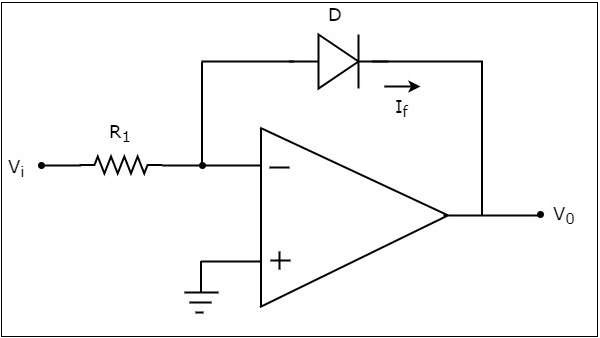

ZA logarithmic amplifierlub a log amplifier, to układ elektroniczny, który generuje sygnał wyjściowy proporcjonalny do logarytmu zastosowanego sygnału wejściowego. W tej sekcji szczegółowo omówiono wzmacniacz logarytmiczny oparty na wzmacniaczu operacyjnym.

Wzmacniacz logarytmiczny oparty na wzmacniaczu operacyjnym wytwarza na wyjściu napięcie, które jest proporcjonalne do logarytmu napięcia przyłożonego do rezystora podłączonego do jego zacisku odwracającego. Plikcircuit diagram wzmacniacza logarytmicznego opartego na wzmacniaczu operacyjnym pokazano na poniższym rysunku -

W powyższym obwodzie nieodwracający zacisk wejściowy wzmacniacza operacyjnego jest podłączony do masy. Oznacza to, że do nieodwracającego zacisku wejściowego wzmacniacza operacyjnego podawane jest zero woltów.

Według virtual short concept, napięcie na odwracającym zacisku wejściowym wzmacniacza operacyjnego będzie równe napięciu na jego nieodwracającym zacisku wejściowym. Zatem napięcie na odwracającym zacisku wejściowym będzie wynosić zero woltów.

Plik nodal equation w węźle odwracającego terminala wejściowego jest -

$$\frac{0-V_i}{R_1}+I_{f}=0$$

$$=>I_{f}=\frac{V_i}{R_1}......Equation 1$$

Poniżej znajduje się plik equation for current przepływa przez diodę, gdy jest przesunięta w przód -

$$I_{f}=I_{s} e^{(\frac{V_f}{nV_T})} ......Equation 2$$

gdzie,

$I_{s}$ jest prądem nasycenia diody,

$V_{f}$ jest spadkiem napięcia na diodzie, gdy jest ona przesunięta w przód,

$V_{T}$ jest termicznym napięciem równoważnym diody.

Plik KVL equation wokół pętli sprzężenia zwrotnego wzmacniacza operacyjnego będzie -

$$0-V_{f}-V_{0}=0$$

$$=>V_{f}=-V_{0}$$

Podstawiając wartość $V_{f}$ w równaniu 2 otrzymujemy -

$$I_{f}=I_{s} e^{\left(\frac{-V_0}{nV_T}\right)} ......Equation 3$$

Zauważ, że wyrazy po lewej stronie zarówno równania 1, jak i równania 3 są takie same. Dlatego zrównaj prawostronny termin tych dwóch równań, jak pokazano poniżej -

$$\frac{V_i}{R_1}=I_{s}e^{\left(\frac{-V_0}{nV_T}\right)}$$

$$\frac{V_i}{R_1I_s}= e^{\left(\frac{-V_0}{nV_T}\right)}$$

Stosowanie natural logarithm po obu stronach otrzymujemy -

$$In\left(\frac{V_i}{R_1I_s}\right)= \frac{-V_0}{nV_T}$$

$$V_{0}=-{nV_T}In\left(\frac{V_i}{R_1I_s}\right)$$

Zauważ, że w powyższym równaniu parametry n, ${V_T}$ i $I_{s}$są stałymi. Więc napięcie wyjściowe$V_{0}$ będzie proporcjonalna do natural logarithm napięcia wejściowego $V_{i}$ dla stałej wartości oporu $R_{1}$.

Dlatego obwód wzmacniacza logarytmicznego oparty na wzmacniaczu operacyjnym omówiony powyżej będzie generował wyjście, które jest proporcjonalne do logarytmu naturalnego napięcia wejściowego. ${V_T}$, gdy ${R_1I_s}=1V$.

Zwróć uwagę na napięcie wyjściowe $V_{0}$ ma negative sign, co wskazuje, że istnieje różnica faz 180 0 między wejściem a wyjściem.

Wzmacniacz antylogarytmiczny

Na anti-logarithmic amplifierlub anti-log amplifier, to układ elektroniczny, który generuje sygnał wyjściowy proporcjonalny do antylogarytmu zastosowanego wejścia. W tej sekcji szczegółowo omówiono wzmacniacz antylogarytmiczny oparty na wzmacniaczu operacyjnym.

Wzmacniacz antylogarytmiczny oparty na wzmacniaczu operacyjnym wytwarza na wyjściu napięcie, które jest proporcjonalne do antylogarytmu napięcia przykładanego do diody podłączonej do jej zacisku odwracającego.

Plik circuit diagram na poniższym rysunku przedstawiono wzmacniacz antylogarytmiczny oparty na wzmacniaczu operacyjnym -

W powyższym obwodzie nieodwracający zacisk wejściowy wzmacniacza operacyjnego jest podłączony do masy. Oznacza to, że do nieodwracającego zacisku wejściowego podawane jest zero woltów.

Według virtual short concept, napięcie na odwracającym zacisku wejściowym wzmacniacza operacyjnego będzie równe napięciu obecnemu na jego nieodwracającym zacisku wejściowym. Zatem napięcie na jego odwracającym zacisku wejściowym będzie wynosić zero woltów.

Plik nodal equation w węźle odwracającego terminala wejściowego jest -

$$-I_{f}+\frac{0-V_0}{R_f}=0$$

$$=>-\frac{V_0}{R_f}=I_{f}$$

$$=>V_{0}=-R_{f}I_{f}.........Equation 4$$

Wiemy, że równanie dla prądu przepływającego przez diodę, gdy jest odchylona do przodu, jest takie, jak podano poniżej -

$$I_{f}=I_{s} e^{\left(\frac{V_f}{nV_T}\right)}$$

Podstawiając wartość $I_{f}$ w równaniu 4 otrzymujemy

$$V_{0}=-R_{f}\left \{{I_{s} e^{\left(\frac{V_f}{nV_T}\right)}}\right \}$$

$$V_{0}=-R_{f}{I_{s} e^{\left(\frac{V_f}{nV_T}\right)}}......Equation 5$$

Równanie KVL po stronie wejściowej zacisku odwracającego wzmacniacza operacyjnego będzie

$$V_{i}-V_{f}=0$$

$$V_{f}=V_{i}$$

Zastępując, wartość w równaniu 5, otrzymujemy -

$$V_{0}=-R_{f}{I_{s} e^{\left(\frac{V_i}{nV_T}\right)}}$$

Zauważ, że w powyższym równaniu parametry n, ${V_T}$ i $I_{s}$są stałymi. Więc napięcie wyjściowe${V_0}$ będzie proporcjonalna do anti-natural logarithm (wykładniczy) napięcia wejściowego ${V_i}$dla stałej wartości rezystancji sprzężenia zwrotnego ${R_f}$.

Dlatego obwód wzmacniacza antylogarytmicznego oparty na wzmacniaczu operacyjnym omówiony powyżej będzie generował wyjście, które jest proporcjonalne do logarytmu antynaturalnego (wykładniczego) napięcia wejściowego. ${V_i}$ gdy, ${R_fI_s}= 1V$. Zwróć uwagę na napięcie wyjściowe${V_0}$ ma negative sign, co wskazuje, że istnieje różnica faz 180 0 między wejściem a wyjściem.

AC i DC to dwa terminy, które często napotykasz podczas badania przepływu ładunku elektrycznego. Alternating Current (AC)ma właściwość do ciągłej zmiany swojego stanu. Na przykład, jeśli weźmiemy pod uwagę falę sinusoidalną, prąd płynie w jednym kierunku dla dodatniego półcyklu i w przeciwnym kierunku dla ujemnego półcyklu. Z drugiej strony,Direct Current (DC) płynie tylko w jednym kierunku.

Obwód elektroniczny, który wytwarza sygnał prądu stałego lub impulsowy sygnał prądu stałego, po przyłożeniu do niego sygnału prądu przemiennego nazywa się rectifier. W tym rozdziale szczegółowo omówiono prostowniki oparte na wzmacniaczach operacyjnych.

Rodzaje prostowników

Prostowniki są podzielone na dwa typy: Half wave rectifier i Full wave rectifier. W tej sekcji szczegółowo omówiono te dwa typy.

Prostownik półfalowy

ZA half wave rectifier jest prostownikiem, który wytwarza dodatnie półcykle na wyjściu przez pół cyklu wejścia i zerowe wyjście dla drugiego półcyklu wejścia.

Plik circuit diagram prostownika półokresowego pokazano na poniższym rysunku.

Zwróć uwagę, że schemat obwodu prostownika półokresowego pokazanego powyżej wygląda jak wzmacniacz odwracający, z dodatkowymi dwiema diodami D 1 i D 2 .

Plik working obwodu prostownika półokresowego pokazanego powyżej wyjaśniono poniżej

Dla positive half cyclez wejścia sinusoidalnego, wyjście wzmacniacza operacyjnego będzie ujemne. Stąd dioda D 1 będzie spolaryzowana do przodu.

Gdy dioda D 1 jest spolaryzowana do przodu, napięcie wyjściowe wzmacniacza operacyjnego wyniesie -0,7 V. Zatem dioda D 2 będzie spolaryzowana odwrotnie. Stądoutput voltage powyższego obwodu jest zero woltów.

Dlatego jest no (zero) output prostownika półfalowego dla dodatniego półokresu wejścia sinusoidalnego.

Dla negative half cyclewejścia sinusoidalnego wyjście wzmacniacza operacyjnego będzie dodatnie. Stąd, diody D 1 i D 2 zostanie spolaryzowana zaporowo spolaryzowana w kierunku przewodzenia i odpowiednio. Tak więc napięcie wyjściowe powyższego obwodu będzie wynosić -

$$V_0=-\left(\frac{R_f}{R_1}\right)V_1$$

Dlatego wyjście prostownika półfalowego będzie wynosić positive half cycle dla ujemnego półcyklu sygnału sinusoidalnego.

Formy falowe

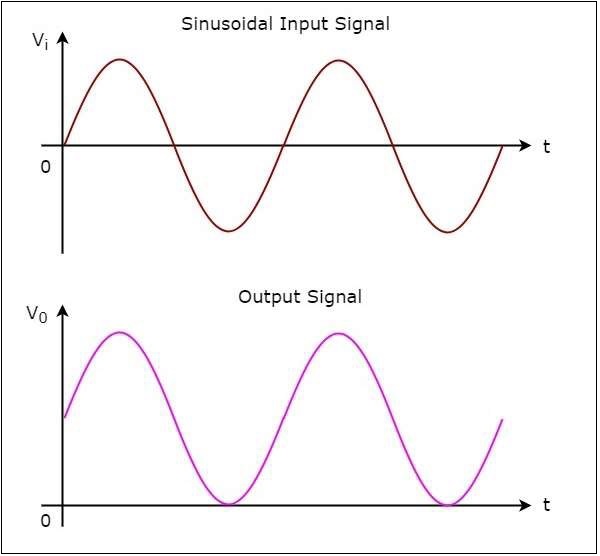

Plik input i output waveforms prostownika półokresowego pokazano na poniższym rysunku

Jak widać na powyższym wykresie, omówiony przez nas schemat obwodu prostownika półokresowego zostanie utworzony positive half cycles dla ujemnych półcykli sinusoidalnego wejścia i zerowego wyjścia dla dodatnich półcykli sinusoidalnego wejścia

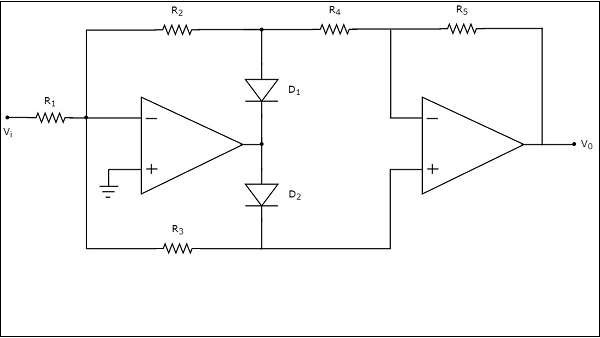

Prostownik pełnookresowy

ZA full wave rectifier generuje dodatnie półcykle na wyjściu dla obu półcyklów wejścia.

Plik circuit diagram prostownika pełnookresowego pokazano na poniższym rysunku -

Powyższy schemat obwodu składa się z dwóch wzmacniaczy operacyjnych, dwóch diod, D 1 i D 2 oraz pięciu rezystorów, od R 1 do R 5 . Plikworking pokazanego powyżej obwodu prostownika pełnookresowego wyjaśniono poniżej -

Dla positive half cyclesinusoidalnego wejścia sygnał wyjściowy pierwszego wzmacniacza operacyjnego będzie ujemny. Stąd, diody D 1 i D 2 będzie spolaryzowana w kierunku przewodzenia i odpowiednio spolaryzowane zaporowo.

Wtedy napięcie wyjściowe pierwszego wzmacniacza operacyjnego będzie wynosić -

$$V_{01}=-\left(\frac{R_2}{R_1}\right)V_i$$

Zauważ, że wyjście pierwszego wzmacniacza operacyjnego jest podłączone do rezystora R 4 , który jest podłączony do zacisku odwracającego drugiego wzmacniacza operacyjnego. Napięcie obecne na nieodwracającym zacisku drugiego wzmacniacza operacyjnego wynosi 0 V. Zatem drugi wzmacniacz operacyjny z rezystorami, R 4 i R 4, działa jakoinverting amplifier.

Napięcie wyjściowe drugiego wzmacniacza operacyjnego będzie wynosić

$$V_0=-\left(\frac{R_5}{R_4}\right)V_{01}$$

Substituting wartość $V_{01}$ w powyższym równaniu otrzymujemy -

$$=>V_{0}=-\left(\frac{R_5}{R_4}\right)\left \{ -\left(\frac{R_2}{R_1}\right)V_{i} \right \}$$

$$=>V_{0}=\left(\frac{R_2R_5}{R_1R_4}\right)V_{i}$$

Dlatego wyjście prostownika pełnookresowego będzie dodatnim półokresem dla positive half cyclewejścia sinusoidalnego. W tym przypadku wzmocnienie wyjścia wynosi$\frac{R_2R_5}{R_1R_4}$. Jeśli weźmiemy pod uwagę$R_{1}=R_{2}=R_{4}=R_{5}=R$, wtedy zysk na wyjściu będzie jeden.

Dla negative half cyclesinusoidalnego wejścia sygnał wyjściowy pierwszego wzmacniacza operacyjnego będzie dodatni. Stąd, diody D 1 i D 2 zostanie spolaryzowana zaporowo spolaryzowana w kierunku przewodzenia i odpowiednio.

Napięcie wyjściowe pierwszego wzmacniacza operacyjnego będzie wynosić -

$$V_{01}=-\left(\frac{R_3}{R_1}\right)V_{i}$$

Wyjście pierwszego wzmacniacza operacyjnego jest bezpośrednio podłączone do nieodwracającego zacisku drugiego wzmacniacza operacyjnego. Teraz drugi wzmacniacz operacyjny z rezystorami, R 4 i R 5, działa jakonon-inverting amplifier.

Napięcie wyjściowe drugiego wzmacniacza operacyjnego będzie wynosić -

$$V_{0}=\left(1+\frac{R_5}{R_4}\right)V_{01}$$

Substituting wartość $V_{01}$ w powyższym równaniu otrzymujemy

$$=>V_{0}=\left(1+\frac{R_5}{R_4}\right) \left\{-\left(\frac{R_3}{R_1}\right)V_{i}\right \} $$

$$=>V_{0}=-\left(\frac{R_3}{R_1}\right)\left(1+\frac{R_5}{R_4}\right)V_{i}$$

Dlatego wyjście prostownika pełnookresowego będzie wynosić positive half cyclerównież dla ujemnego półcyklu wejścia sinusoidalnego. W tym przypadku wielkość wzmocnienia na wyjściu wynosi$\left(\frac{R_3}{R_1}\right)\left(1+\frac{R_5}{R_4}\right)$. Jeśli weźmiemy pod uwagę$R_{1}=2R_{3}=R_{4}=R_{5}=R$ wtedy zysk na wyjściu będzie one.

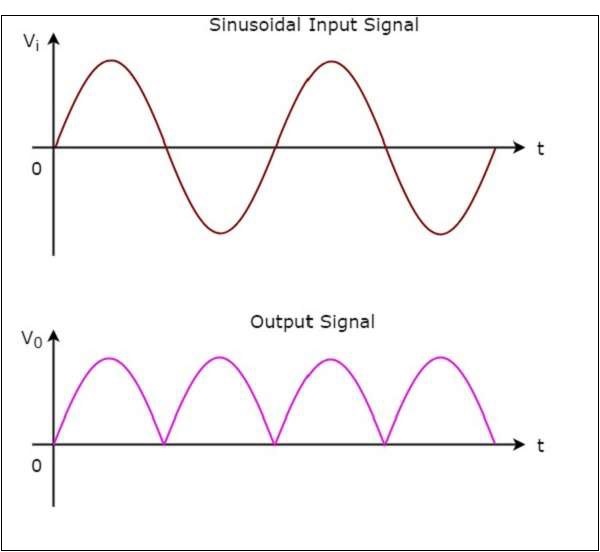

Plik input i output waveforms prostownika pełnookresowego pokazano na poniższym rysunku

Jak widać na powyższym rysunku, schemat obwodu prostownika pełnookresowego, który rozważaliśmy, będzie wytwarzał tylko positive half cycles zarówno dla dodatnich, jak i ujemnych półcyklów wejścia sinusoidalnego.

Wave shaping circuitsto obwody elektroniczne, które na wyjściu z zastosowanego przebiegu wejściowego wytwarzają pożądany kształt. Te obwody pełnią dwie funkcje -

- Osłab zastosowaną falę

- Zmień poziom prądu stałego zastosowanej fali.

Istnieją dwa rodzaje obwodów kształtujących fale: Clippers i Clampers. W tym rozdziale dowiesz się szczegółowo o maszynkach do strzyżenia.

Clippers na bazie wzmacniacza operacyjnego

ZA clipperto obwód elektroniczny, który wytwarza sygnał wyjściowy poprzez usunięcie części wejścia powyżej lub poniżej wartości odniesienia. Oznacza to, że wyjście maszynki do strzyżenia będzie takie samo, jak wejście dla części innej niż przycięta. Z tego powodu amplituda międzyszczytowa na wyjściu obcinacza będzie zawsze mniejsza niż na wejściu.

Główną zaletą maszynek do strzyżenia jest to, że eliminują niepożądane szumy obecne w amplitudzie sygnału AC.

Clippers można podzielić na następujące dwa typy w oparciu o wycinaną część wejścia.

- Pozytywny Clipper

- Negative Clipper

Są one szczegółowo omówione, jak podano poniżej -

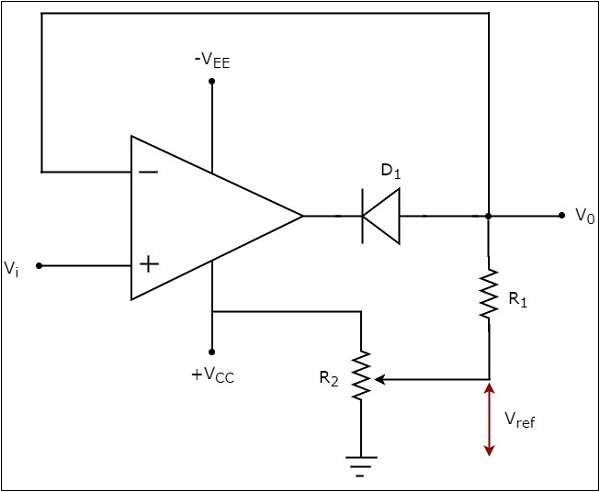

Pozytywny Clipper

ZA positive clipper to maszynka do strzyżenia, która obcina tylko dodatnią część (y) sygnału wejściowego.

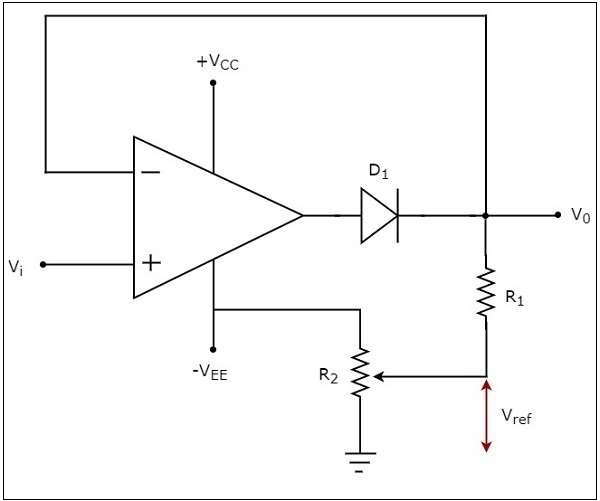

Plik circuit diagrampozytywnej strzyżarki pokazano na poniższym rysunku -

Na powyższym obwodzie sinusoidalny sygnał napięciowy $V_{t}$jest stosowany do nieodwracającego zacisku wzmacniacza operacyjnego. Wartość napięcia odniesienia$V_{ref}$ można wybrać, zmieniając rezystor $R_{2}$.

Plik operation obwodu pokazanego powyżej jest wyjaśnione poniżej -

Jeśli wartość napięcia wejściowego $V_i$ jest mniejsza niż wartość napięcia odniesienia $V_{ref}$, to dioda D 1 przewodzi. Wówczas obwód podany powyżej zachowuje się jakvoltage follower. Dlatego napięcie wyjściowe$V_{0}$ powyższego obwodu będzie takie samo jak napięcie wejściowe $V_{i}$, dla $V_{i}$ < $V_{ref}$.

Jeśli wartość napięcia wejściowego $V_{i}$ jest większa niż wartość napięcia odniesienia $V_{ref}$to dioda D 1 zgaśnie. Teraz wzmacniacz operacyjny działa w otwartej pętli, ponieważ ścieżka sprzężenia zwrotnego była otwarta. Dlatego napięcie wyjściowe$V_{0}$ powyższego obwodu będzie równa wartości napięcia odniesienia $V_{ref}$, dla $V_{i}$ > $V_{ref}$.

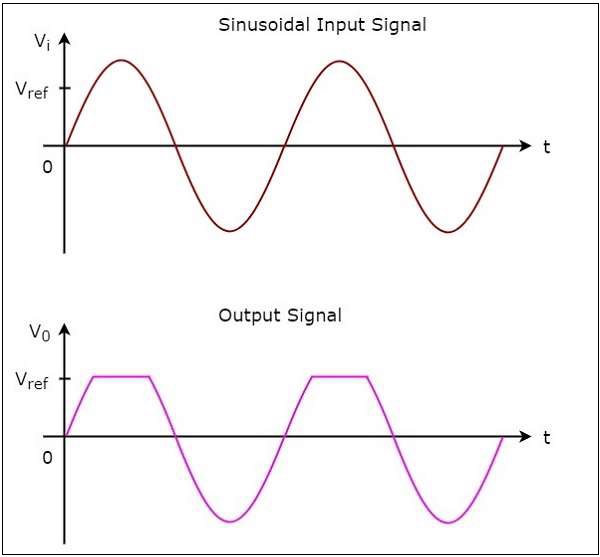

Plik input wave form i odpowiednie output wave form dodatniego obcinacza dla dodatniego napięcia odniesienia $V_{ref}$pokazano na poniższym rysunku -

Negative Clipper

ZA negative clipperto maszynka do strzyżenia, która przycina tylko ujemne części sygnału wejściowego. Możesz uzyskać obwód ujemnego obcinacza po prostu odwracając diodę i biorąc odwrotną polaryzację napięcia odniesienia, w obwodzie, który widziałeś dla dodatniego obcinacza.

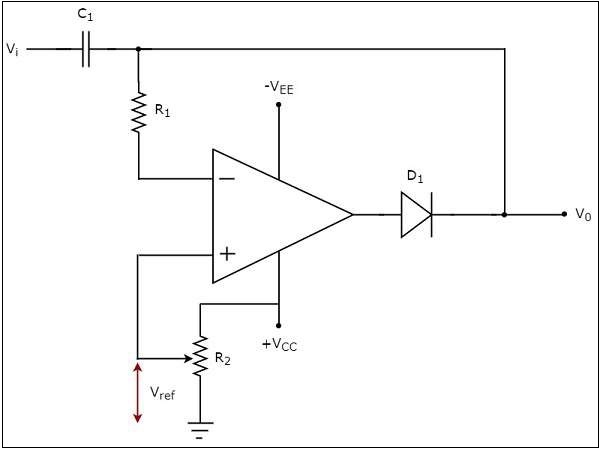

Plik circuit diagram negatywnej strzyżarki pokazano na poniższym rysunku -

W powyższym obwodzie sinusoidalny sygnał napięciowy $V_{i}$jest stosowany do nieodwracającego zacisku wzmacniacza operacyjnego. Wartość napięcia odniesienia$V_{ref}$ można wybrać, zmieniając rezystor $R_{2}$.

Plik operation ujemnego obwodu obcinacza opisano poniżej -

Jeśli wartość napięcia wejściowego $V_{t}$ jest większa niż wartość napięcia odniesienia $V_{ref}$, to dioda D 1 przewodzi. Następnie powyższy obwód zachowuje się jakvoltage follower. Dlatego napięcie wyjściowe$V_{0}$ powyższego obwodu będzie takie samo jak napięcie wejściowe $V_{i}$ dla $V_{i}$> $V_{ref}$.

Jeśli wartość napięcia wejściowego $V_{i}$jest mniejsza niż wartość napięcia odniesienia, to dioda D 1 zgaśnie. Teraz wzmacniacz operacyjny działa w otwartej pętli, ponieważ ścieżka sprzężenia zwrotnego jest otwarta. Dlatego napięcie wyjściowe$V_{0}$ powyższego obwodu będzie równa wartości napięcia odniesienia,$V_{ref}$ dla $V_{i}$ < $V_{ref}$.

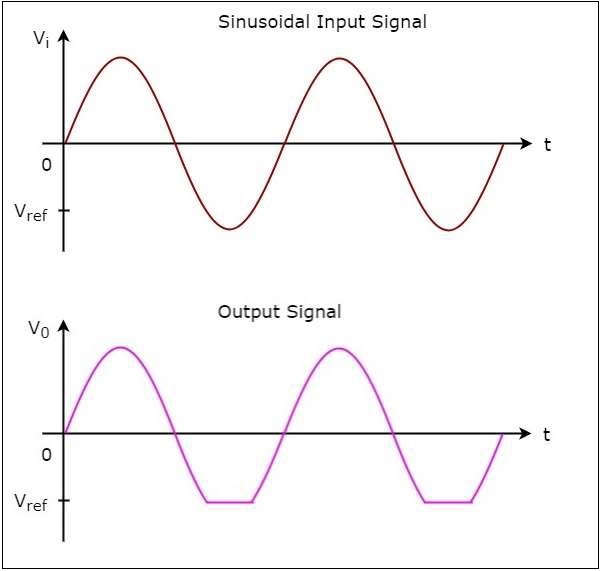

Plik input wave form i odpowiednie output wave form ujemnego obcinacza, dla ujemnego napięcia odniesienia $V_{ref}$pokazano na poniższym rysunku -

W poprzednim rozdziale omówiliśmy maszynki do strzyżenia. Porozmawiajmy teraz o innym typie obwodów kształtowania fali, a mianowicie o zaciskarkach.

Zaciski oparte na wzmacniaczu operacyjnym

ZA clamperjest obwodem elektronicznym, który wytwarza sygnał wyjściowy podobny do wejścia, ale z przesunięciem poziomu prądu stałego. Innymi słowy, wyjście zacisku jest dokładną repliką wejścia. W związku z tym amplituda od szczytu do szczytu na wyjściu zacisku będzie zawsze równa amplitudzie na wejściu.

Cęgi służą do wprowadzania lub przywracania poziomu DC sygnału wejściowego na wyjściu. Tam sątwo types cęgów opartych na wzmacniaczu operacyjnym w oparciu o przesunięcie DC na wejściu.

- Pozytywny Clamper

- Zacisk ujemny

W tej sekcji szczegółowo omówiono te dwa typy zacisków.

Pozytywny Clamper

Zacisk dodatni to obwód zaciskowy, który wytwarza wyjście w taki sposób, że sygnał wejściowy jest przesuwany w pionie o dodatnią wartość prądu stałego.

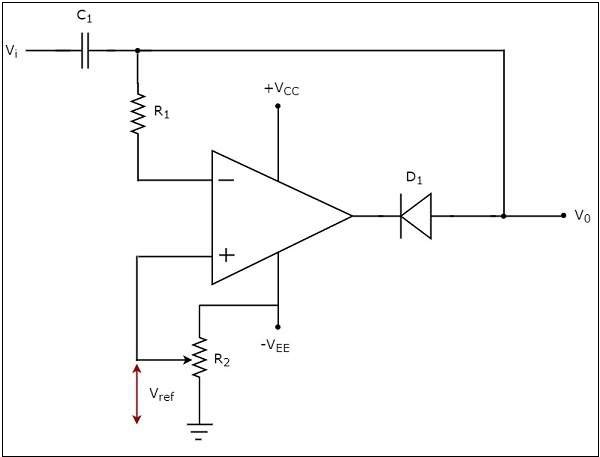

Plik circuit diagram zacisku dodatniego pokazano na poniższym rysunku -

W powyższym obwodzie a sinusoidal voltage signal, $V_{i}$ jest stosowany do odwracającego zacisku wzmacniacza operacyjnego przez sieć składającą się z kondensatora $C_{1}$ i rezystor $R_{1}$. Oznacza to, że sygnał napięcia przemiennego jest podawany na zacisk odwracający wzmacniacza operacyjnego.

Plik DC reference voltage $V_{ref}$ jest stosowany do nieodwracającego zacisku wzmacniacza operacyjnego. Wartość napięcia odniesienia$V_{ref}$ można wybrać, zmieniając rezystor $R_{2}$. W takim przypadku otrzymamy napięcie odniesienia$V_{ref}$ o wartości dodatniej.

Powyższy obwód wytwarza output, który is the combination (resultant sum) sinusoidalnego sygnału napięciowego $V_{i}$ i napięcie odniesienia $V_{ref}$. Oznacza to, że obwód zaciskowy wytwarza wyjście w taki sposób, że sinusoidalny sygnał napięciowy$V_{i}$ zostaje przesunięty pionowo w górę o wartość napięcia odniesienia $V_{ref}$.

Kształt fali wejściowej i odpowiadający jej kształt fali wyjściowej dodatniego zacisku pokazano na powyższym rysunku -

Z powyższego rysunku można zauważyć, że zacisk dodatni przesuwa zastosowany przebieg wejściowy vertically upwardna wyjściu. Wielkość przesunięcia będzie zależeć od wartości napięcia odniesienia DC.

Zacisk ujemny

ZA negative clamper to obwód zaciskowy, który wytwarza sygnał wyjściowy w taki sposób, że sygnał wejściowy jest przesuwany w pionie o ujemną wartość prądu stałego.

Plik circuit diagram zacisku ujemnego pokazano na poniższym rysunku -

W powyższym obwodzie a sinusoidal voltage signal $V_{i}$ stosowany jest do zacisku odwracającego op-amp z sieci, która składa się z kondensatora C 1 i rezystor$R_{1}$. Oznacza to, że sygnał napięcia przemiennego jest podawany na zacisk odwracający wzmacniacza operacyjnego.

Plik DC reference voltage $V_{ref}$ jest przyłożona do nieodwracającego zacisku wzmacniacza operacyjnego Wartość napięcia odniesienia $V_{ref}$ można wybrać, zmieniając rezystor $R_{2}$. W takim przypadku uzyskamy napięcie odniesienia$V_{ref}$ o wartości ujemnej.

Powyższy obwód wytwarza wyjście, które jest połączeniem (sumą wypadkową) sinusoidalnego sygnału napięciowego $V_{i}$ i napięcie odniesienia $V_{ref}$. Oznacza to, że obwód zaciskowy wytwarza wyjście w taki sposób, że sinusoidalny sygnał napięciowy$V_{i}$ zostaje przesunięty pionowo w dół o wartość napięcia odniesienia $V_{ref}$.

Kształt fali wejściowej i odpowiadający mu kształt fali wyjściowej zacisku ujemnego pokazano na poniższym rysunku -

Na wyjściu widać, że zacisk ujemny przesuwa zastosowany przebieg wejściowy vertically downwardna wyjściu. Wielkość przesunięcia będzie zależeć od wartości napięcia odniesienia DC.

Filtersto obwody elektroniczne, które dopuszczają pewne składowe częstotliwości i / lub odrzucają inne. Być może natrafiłeś na filtry w samouczku teorii sieci. Są pasywne i są to obwody lub sieci elektryczne, które składają się z elementów pasywnych, takich jak rezystor, kondensator i (lub) cewka indukcyjna.

W tym rozdziale omówiono temat active filters szczegółowo.

Rodzaje aktywnych filtrów

Filtry aktywne to obwody elektroniczne, które składają się z elementu aktywnego, takiego jak wzmacniacz operacyjny, wraz z elementami biernymi, takimi jak rezystor (i) i kondensator (i).

Filtry aktywne dzielą się głównie na następujące four types w oparciu o pasmo częstotliwości, na które zezwalają i / lub odrzucają -

- Aktywny filtr dolnoprzepustowy

- Aktywny filtr górnoprzepustowy

- Aktywny filtr pasmowy

- Filtr aktywnego pasma zatrzymania

Aktywny filtr dolnoprzepustowy

Jeśli aktywny filtr zezwala (przechodzi) tylko low frequency komponenty i odrzuca (blokuje) wszystkie inne komponenty o wysokiej częstotliwości, wtedy nazywa się to jako active low pass filter.

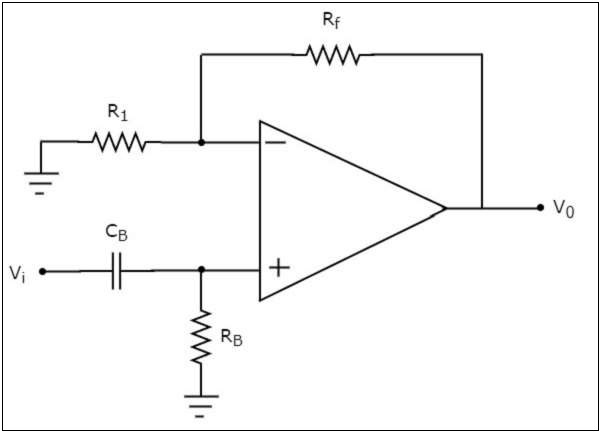

Plik circuit diagram aktywnego filtra dolnoprzepustowego pokazano na poniższym rysunku -

Wiemy, że sieć elektryczna, która jest podłączona do nieodwracającego zacisku wzmacniacza operacyjnego, to passive low pass filter. Tak więc wejście nieodwracającego zacisku wzmacniacza operacyjnego jest wyjściem pasywnego filtra dolnoprzepustowego.

Zauważ, że powyższy obwód przypomina a non-inverting amplifier. Ma wyjście pasywnego filtra dolnoprzepustowego jako wejście do nieodwracającego zacisku wzmacniacza operacyjnego. W związku z tym wytwarza wynik, którym jest$\left(1+\frac{R_f}{R_1}\right)$ razy wejście obecne na nieodwracającym zacisku.

Możemy wybrać wartości $R_{f}$ i $R_{1}$ odpowiednio w celu uzyskania desired gainna wyjściu. Załóżmy, że jeśli weźmiemy pod uwagę wartości oporu$R_{f}$ i $R_{1}$ jako zero omów i nieskończoność omów, powyższy obwód wygeneruje unity gain wyjście filtra dolnoprzepustowego.

Aktywny filtr górnoprzepustowy

Jeśli aktywny filtr zezwala (przechodzi) tylko high frequency komponenty i odrzuca (blokuje) wszystkie inne komponenty o niskiej częstotliwości, wtedy nazywa się to active high pass filter.

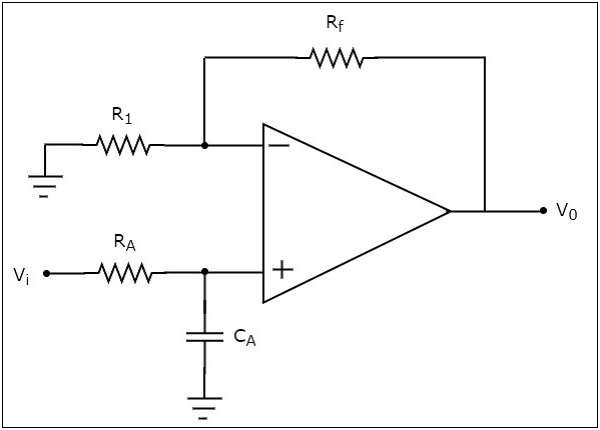

Plik circuit diagram aktywnego filtra górnoprzepustowego pokazano na poniższym rysunku -

Wiemy, że sieć elektryczna, która jest podłączona do nieodwracającego zacisku wzmacniacza operacyjnego, to passive high pass filter. Tak więc wejście nieodwracającego terminala opamp jest wyjściem pasywnego filtra górnoprzepustowego.

Teraz powyższy obwód przypomina a non-inverting amplifier. Ma wyjście pasywnego filtra górnoprzepustowego jako wejście do nieodwracającego zacisku wzmacniacza operacyjnego. W związku z tym wytwarza wynik, którym jest$\left(1+\frac{R_f}{R_1}\right)$ razy wejście obecne na jego nieodwracającym zacisku.

Możemy wybrać wartości $R_f$ i $R_1$ odpowiednio w celu uzyskania desired gainna wyjściu. Załóżmy, że jeśli weźmiemy pod uwagę wartości oporu$R_{f}$ i $R_{1}$ jako zero omów i nieskończoność omów, powyższy obwód wygeneruje unity gain wyjście filtra górnoprzepustowego.

Aktywny filtr pasmowy

Jeśli filtr aktywny przepuszcza (przepuszcza) tylko jedno pasmo częstotliwości, wówczas nazywa się go active band pass filter. Ogólnie rzecz biorąc, to pasmo częstotliwości znajduje się pomiędzy niskimi i wysokimi częstotliwościami. Tak więc aktywny filtr pasmowy odrzuca (blokuje) zarówno składowe o niskiej, jak i wysokiej częstotliwości.

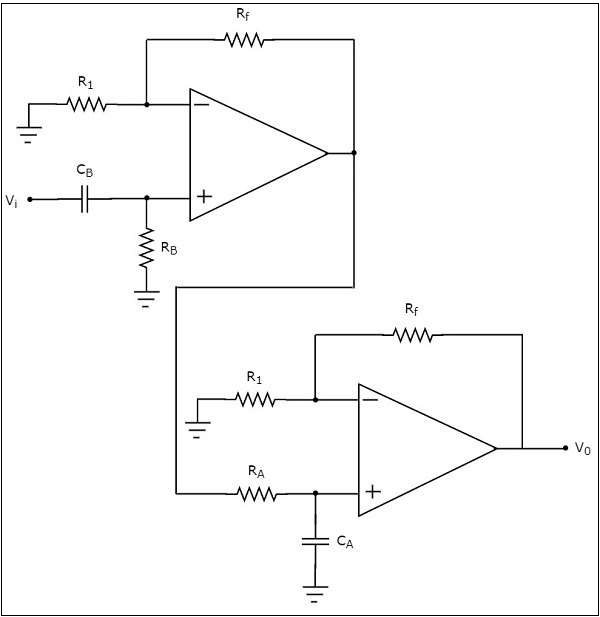

Plik circuit diagram aktywnego filtra pasmowego pokazano na poniższym rysunku

Zauważ, że są two parts na schemacie obwodu aktywnego filtra pasmowego: Pierwsza część to aktywny filtr górnoprzepustowy, natomiast druga część to aktywny filtr dolnoprzepustowy.

Wyjście aktywnego filtra górnoprzepustowego jest stosowane jako wejście aktywnego filtra dolnoprzepustowego, co oznacza, że zarówno aktywny filtr górnoprzepustowy, jak i aktywny filtr dolnoprzepustowy są cascaded w celu uzyskania takiego wyjścia, które zawiera tylko określone pasmo częstotliwości.

Plik active high pass filter, który jest obecny na pierwszym etapie, dopuszcza częstotliwości większe niż lower cut-off frequencyaktywnego filtra pasmowego. Musimy więc wybrać wartości$R_{B}$ i $C_{B}$ odpowiednio, aby uzyskać pożądane lower cut-off frequency aktywnego filtra pasmowego.

Podobnie active low pass filter, który jest obecny na drugim etapie, dopuszcza częstotliwości mniejsze niż wyższa częstotliwość odcięcia aktywnego filtra pasmowego. Musimy więc wybrać wartości$R_{A}$ i $C_{A}$ odpowiednio w celu uzyskania pożądanego higher cut-off frequency aktywnego filtra pasmowego.

W związku z tym obwód na schemacie omówionym powyżej będzie generował wyjście aktywnego filtra pasmowego.

Filtr aktywnego pasma zatrzymania

Jeśli aktywny filtr odrzuca (blokuje) określone pasmo częstotliwości, wówczas jest nazywany active band stop filter. Ogólnie rzecz biorąc, to pasmo częstotliwości znajduje się pomiędzy niskimi i wysokimi częstotliwościami. Tak więc aktywny filtr pasmowy pozwala (przepuszcza) zarówno składowe o niskiej, jak i wysokiej częstotliwości.

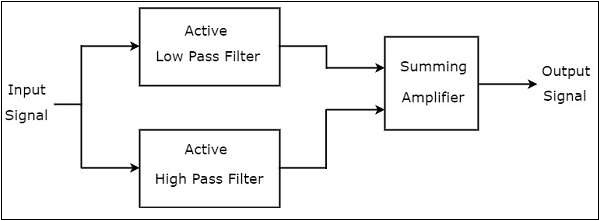

Plik block diagram aktywnego filtru pasmowego pokazano na poniższym rysunku -

Zauważ, że schemat blokowy aktywnego filtru pasmowego składa się z dwóch bloków w pierwszym stopniu: aktywnego filtru dolnoprzepustowego i aktywnego filtru górnoprzepustowego. Wyjścia tych dwóch bloków są stosowane jako wejścia do bloku, który jest obecny w drugim etapie. Więcsumming amplifier generuje wyjście, które jest wzmocnioną wersją sumy sygnałów wyjściowych aktywnego filtra dolnoprzepustowego i aktywnego filtra górnoprzepustowego.

Dlatego wynikiem powyższego schematu blokowego będzie plik output of an active band stop , gdy wybierzemy częstotliwość odcięcia filtra dolnoprzepustowego, aby była mniejsza niż częstotliwość odcięcia filtra górnoprzepustowego.

Plik circuit diagram aktywnego filtru pasmowego pokazano na poniższym rysunku -

Widzieliśmy już schematy obwodów aktywnego filtra dolnoprzepustowego, aktywnego filtra górnoprzepustowego i wzmacniacza sumującego. Zwróć uwagę, że mamy powyższecircuit diagram aktywnego pasmowego filtru odcinającego poprzez zastąpienie bloków odpowiednimi schematami obwodów na schemacie blokowym aktywnego pasmowego filtru odcinającego.

Oscylator to obwód elektroniczny, który wytwarza okresowy sygnał. Jeśli oscylator wytwarza oscylacje sinusoidalne, nazywa się go asinusoidal oscillator. Konwertuje energię wejściową ze źródła prądu stałego na energię wyjściową prądu przemiennego okresowego sygnału. Ten okresowy sygnał będzie miał określoną częstotliwość i amplitudę.

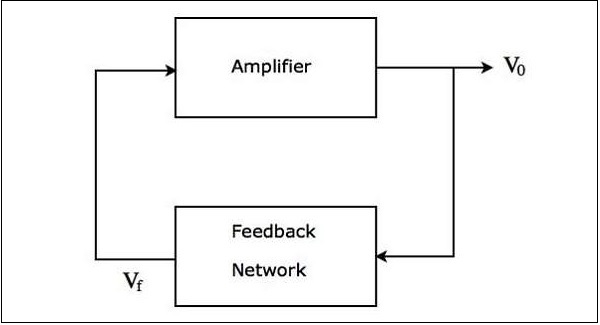

Plik block diagram oscylatora sinusoidalnego pokazano na poniższym rysunku -

Powyższy rysunek składa się głównie z plików two blocks: wzmacniacz i sieć sprzężenia zwrotnego. Sieć sprzężenia zwrotnego bierze część wyjścia wzmacniacza jako wejście do niego i wytwarza sygnał napięciowy. Ten sygnał napięciowy jest podawany jako wejście do wzmacniacza.

Schemat blokowy oscylatora sinusoidalnego pokazany powyżej wytwarza oscylacje sinusoidalne, gdy następujące two conditions są zadowoleni -

Plik loop gain $A_{v}\beta$ powyższego schematu blokowego oscylatora sinusoidalnego musi być większe lub równe unity. Tutaj,$A_{v}$ i $\beta$ są odpowiednio wzmocnieniem wzmacniacza i wzmocnieniem sieci sprzężenia zwrotnego.

Suma phase shift wokół pętli powyższego schematu blokowego oscylatora sinusoidalnego musi być albo 00 lub 3600.

Powyższe dwa warunki razem nazywane są jako Barkhausen criteria.

Oscylatory oparte na wzmacniaczu operacyjnym

Tam są two typy oscylatorów opartych na wzmacniaczach operacyjnych.

- Oscylator przesunięcia fazowego RC

- Oscylator mostu Wien

W tej sekcji szczegółowo omówiono każdy z nich.

Oscylator przesunięcia fazowego RC

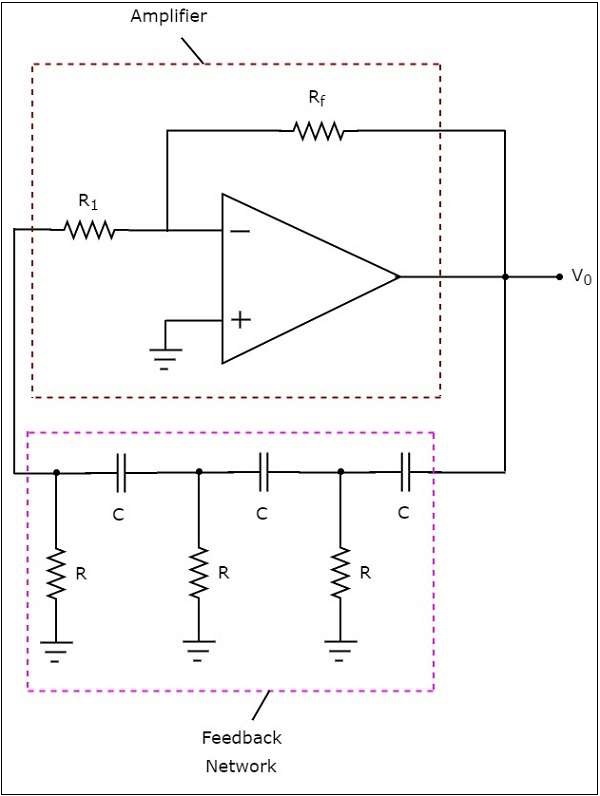

Oscylator oparty na wzmacniaczu operacyjnym, który wytwarza sinusoidalny sygnał napięciowy na wyjściu za pomocą wzmacniacza odwracającego i sieci sprzężenia zwrotnego, jest znany jako RC phase shift oscillator. Ta sieć sprzężenia zwrotnego składa się z trzech połączonych kaskadowo sekcji żelbetowych.

Plik circuit diagram oscylatora przesunięcia fazowego RC pokazano na poniższym rysunku -

W powyższym obwodzie działa wzmacniacz operacyjny inverting mode. W związku z tym zapewnia przesunięcie fazowe o 180 0 . Sieć sprzężenia zwrotnego obecna w powyższym obwodzie zapewnia również przesunięcie fazowe 180 0 , ponieważ każda sekcja RC zapewnia przesunięcie fazowe 60 0 . Dlatego powyższy obwód zapewnia całkowite przesunięcie fazowe o 360 0 przy pewnej częstotliwości.

Plik output frequency oscylatora przesunięcia fazowego RC wynosi -

$$f=\frac{1}{2\Pi RC\sqrt[]{6}}$$

Plik gain $A_{v}$ wzmacniacza odwracającego powinno być większe lub równe -29,

$$i.e.,-\frac{R_f}{R_1}\geq-29$$

$$=>\frac{R_f}{R_1}\geq-29$$

$$=>R_{f}\geq29R_{1}$$

Powinniśmy więc wziąć pod uwagę wartość rezystora sprzężenia zwrotnego $R_{f}$co najmniej 29-krotność wartości rezystora $R_{1}$, w celu wytworzenia trwałych oscylacji na wyjściu oscylatora przesunięcia fazowego RC.

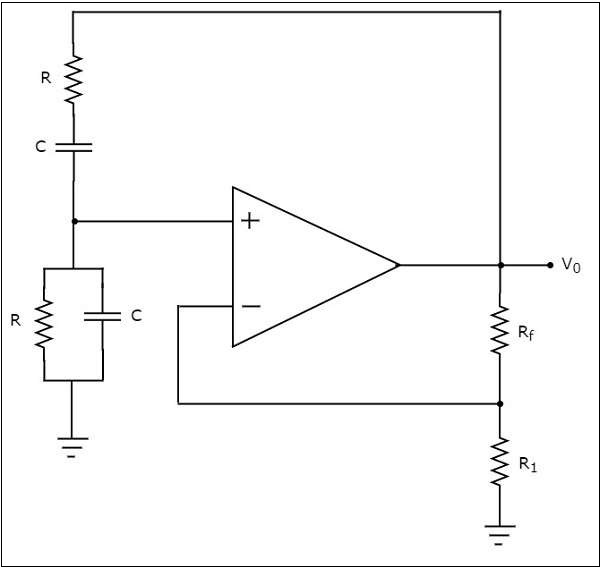

Oscylator Wien Bridge

Oscylator oparty na wzmacniaczu operacyjnym, który wytwarza sinusoidalny sygnał napięciowy na wyjściu za pomocą nieodwracającego wzmacniacza i sieci sprzężenia zwrotnego, jest znany jako Wien bridge oscillator.

Plik circuit diagram oscylatora mostu wiedeńskiego pokazano na poniższym rysunku -

W obwodzie pokazanym powyżej dla oscylatora mostka Weina działa wzmacniacz operacyjny non inverting mode. W związku z tym zapewnia przesunięcie fazowe o wartości 00. Zatem sieć sprzężenia zwrotnego obecna w powyższym obwodzie nie powinna zapewniać żadnego przesunięcia fazowego.

Jeśli sieć sprzężenia zwrotnego zapewnia pewne przesunięcie fazowe, musimy to zrobić balance the bridgew taki sposób, aby nie było żadnego przesunięcia fazowego. Tak więc powyższy obwód zapewnia całkowite przesunięcie fazowe 0 0 przy pewnej częstotliwości.

Plik output frequency oscylatora mostu w Wiedniu jest

$$f=\frac{1}{2\Pi RC}$$

Plik gain $A_{v}$ wzmacniacza nieodwracającego powinno być większe lub równe 3

$$i.e.,1+\frac{R_f}{R_1}\geq3$$

$$=>\frac{R_f}{R_1}\geq2$$

$$=>R_{f}\geq2R_{1}$$

Powinniśmy więc wziąć pod uwagę wartość rezystora sprzężenia zwrotnego $R_{f}$ co najmniej dwukrotność wartości rezystora, $R_{1}$ w celu wytworzenia trwałych oscylacji na wyjściu oscylatora mostu wiedeńskiego.

ZA waveform generatorto układ elektroniczny, który generuje standardową falę. Istnieją dwa typy generatorów przebiegów opartych na wzmacniaczach operacyjnych -

- Generator fal prostokątnych

- Generator fal trójkątnych

W tym rozdziale szczegółowo omówiono każdy z tych generatorów przebiegów opartych na wzmacniaczach operacyjnych.

Generator fal kwadratowych

ZA square wave generatorjest układem elektronicznym generującym falę prostokątną. W tej sekcji omówiono generatory fal prostokątnych oparte na wzmacniaczach operacyjnych.

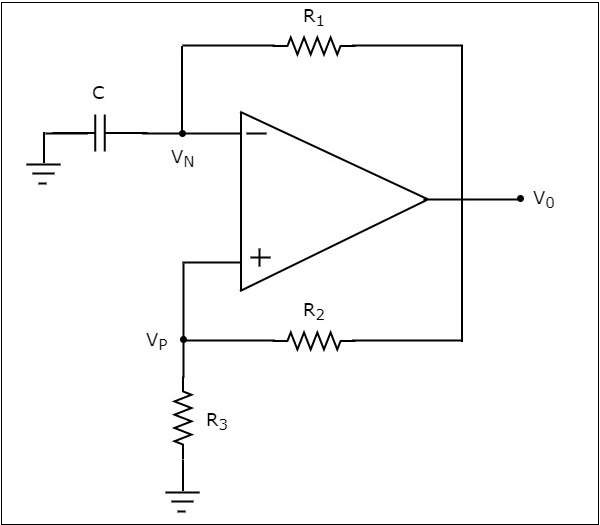

Plik circuit diagram na poniższym rysunku przedstawiono generator fal prostokątnych oparty na wzmacniaczu operacyjnym

Zauważ, że na schemacie obwodu pokazanym powyżej rezystor $R_{1}$jest podłączony między odwracającym zaciskiem wejściowym wzmacniacza operacyjnego a jego wyjściem wzmacniacza operacyjnego. Więc rezystor$R_{1}$ jest używany w negative feedback. Podobnie rezystor$R_{2}$jest podłączony między nieodwracającym zaciskiem wejściowym wzmacniacza operacyjnego a jego wyjściem. Więc rezystor$R_{2}$ jest używany w positive feedback ścieżka.

Kondensator C jest podłączony między odwracającym zaciskiem wejściowym wzmacniacza operacyjnego a masą. Więcvoltage across capacitor Cbędzie napięciem wejściowym na tym odwracającym zacisku wzmacniacza operacyjnego. Podobnie rezystor$R_{3}$jest podłączony między nieodwracającym zaciskiem wejściowym wzmacniacza operacyjnego a masą. Więcvoltage across resistor $R_{3}$ będzie napięciem wejściowym na tym nieodwracającym zacisku wzmacniacza operacyjnego.

Plik operation generatora fal prostokątnych wyjaśniono poniżej -

Załóżmy, że jest no chargepoczątkowo przechowywany w kondensatorze. Następnie napięcie obecne na zacisku odwracającym wzmacniacza operacyjnego wynosi zero woltów. Ale na nieodwracającym zacisku wzmacniacza operacyjnego występuje pewne napięcie przesunięcia. Z tego powodu wartość obecna na wyjściu powyższego obwodu będzie wynosić$+V_{sat}$.

Teraz zaczyna się kondensator C. charging przez rezystor $R_{1}$. Wartość obecna na wyjściu powyższego obwodu zmieni się na$-V_{sat}$, gdy napięcie na kondensatorze C osiągnie wartość nieco większą niż napięcie (wartość dodatnia) na rezystorze $R_{3}$.

Kondensator C uruchamia się discharging przez rezystor $R_{1}$, gdy wyjście powyższego obwodu jest $-V_{sat}$. Wartość obecna na wyjściu powyższego obwodu zmieni się na$+V_{sat}$, gdy napięcie na kondensatorze C osiąga niewiele mniej niż (bardziej ujemne) napięcie (wartość ujemna) na rezystorze $R_{3}$.

Tak więc obwód pokazany na powyższym schemacie wygeneruje square wave na wyjściu, jak pokazano na poniższym rysunku -

Z powyższego rysunku możemy zauważyć, że wyjście generatora fali prostokątnej będzie miało jedną z dwóch wartości: $+V_{sat}$ i $-V_{sat}$. Zatem wyjście pozostaje przy jednej wartości przez pewien czas, a następnie przechodzi do innej wartości i pozostaje tam przez pewien czas. W ten sposób to trwa.

Generator fal trójkątnych

Generator fal trójkątnych to obwód elektroniczny, który generuje falę trójkątną. Plikblock diagram generatora fal trójkątnych pokazano na poniższym rysunku -

Schemat blokowy generatora fal trójkątnych składa się głównie z dwóch bloków: generatora fali prostokątnej i integratora. Te dwa bloki sącascaded. Oznacza to, że wyjście generatora fali prostokątnej jest stosowane jako wejście integratora. Zauważ, że całkowanie fali prostokątnej to nic innego jak fala trójkątna.

Plik circuit diagram generatora fal trójkątnych opartego na wzmacniaczu operacyjnym pokazano na poniższym rysunku -

Widzieliśmy już schematy obwodów generatora fali prostokątnej i integratora. Zwróć uwagę, że mamy powyższecircuit diagram generatora fal trójkątnych opartego na wzmacniaczu operacyjnym poprzez zastąpienie bloków odpowiednimi schematami obwodów na schemacie blokowym generatora fal trójkątnych.

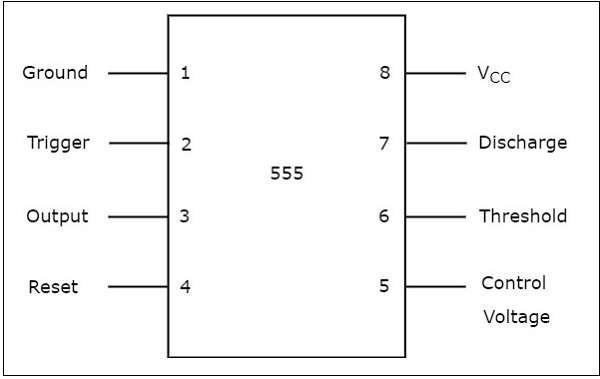

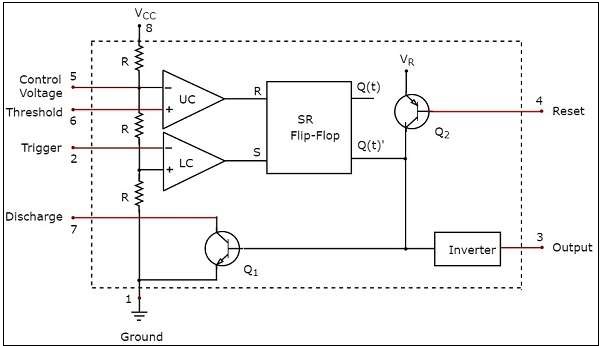

Plik 555 Timer IC ma swoją nazwę od trzech $5K\Omega$rezystory używane w jego sieci dzielnika napięcia. Ten układ scalony jest przydatny do generowania dokładnych opóźnień czasowych i oscylacji. W tym rozdziale szczegółowo opisano programator 555 Timer.

Schemat pinów i schemat funkcjonalny

W tej sekcji najpierw omówimy schemat pinów układu scalonego 555 Timer, a następnie jego schemat funkcjonalny.

Schemat pinów

Układ scalony timera 555 to 8-pinowy mini pakiet Dual-Inline (DIP). Plikpin diagram układu scalonego timera 555 pokazano na poniższym rysunku -

Z powyższego schematu wynika, że znaczenie każdego kołka jest oczywiste. Ten układ scalony timera 555 może być obsługiwany przy zasilaniu prądem stałym od + 5 V do + 18 V. Przydaje się głównie do generowanianon-sinusoidal kształty fal, takie jak kwadrat, rampa, puls itp

Schemat funkcjonalny

Graficzna reprezentacja pokazująca wewnętrzne szczegóły timera 555 jest znana jako schemat funkcjonalny.

Plik functional diagram 555 Timer IC pokazano na poniższym rysunku -

Zwróć uwagę, że schemat funkcjonalny timera 555 zawiera dzielnik napięcia, dwa komparatory, jeden przerzutnik SR, dwa tranzystory i falownik. W tej sekcji szczegółowo omówiono przeznaczenie każdego bloku lub komponentu -

Sieć dzielnika napięcia

Sieć dzielnika napięcia składa się z trzech $5K\Omega$ rezystory połączone szeregowo między napięciem zasilania $V_{cc}$ i ziemi.

Ta sieć zapewnia napięcie $\frac{V_{cc} }{3}$ między punktem a ziemią, jeśli istnieje tylko jeden $5K\Omega$rezystor. Podobnie zapewnia napięcie$\frac{2V_{cc} }{3}$ między punktem a ziemią, jeśli istnieją tylko dwa $5K\Omega$ rezystory.

Komparator

Schemat funkcjonalny układu scalonego timera 555 składa się z dwóch komparatorów: górnego komparatora (UC) i dolnego komparatora (LC).

Przypomnij sobie, że a comparator porównuje dwa dane wejściowe, które są do niego stosowane, i generuje wynik.

Jeśli napięcie obecne na nieodwracającym zacisku wzmacniacza operacyjnego jest większe niż napięcie obecne na jego zacisku odwracającym, to wyjście komparatora będzie $+V_{sat}$. Można to uznać zaLogic High („1”) w postaci cyfrowej.

Jeśli napięcie obecne na nieodwracającym zacisku wzmacniacza operacyjnego jest mniejsze lub równe napięciu na jego zacisku odwracającym, to wyjście komparatora będzie $-V_{sat}$. Można to uznać zaLogic Low („0”) w postaci cyfrowej.

SR Flip-Flop

Przypomnij sobie, że a SR flip-flopdziała z dodatnimi lub ujemnymi przejściami zegara. Posiada dwa wejścia: S i R oraz dwa wyjścia: Q (t) i Q (t) '. Wyjścia Q (t) i Q (t) 'uzupełniają się wzajemnie.

W poniższej tabeli przedstawiono state table przerzutnika SR

| S | R | Q (t + 1) |

|---|---|---|

| 0 | 0 | Q (t) |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | - |

Tutaj Q (t) i Q (t + 1) są odpowiednio stanem obecnym i następnym. Tak więc przerzutnik SR może być używany do jednej z tych trzech funkcji, takich jak Hold, Reset & Set w oparciu o warunki wejściowe, gdy stosowane jest dodatnie (ujemne) przejście sygnału zegarowego.

Wyjścia dolnego komparatora (LC) i górnego komparatora (UC) są stosowane jako inputs of SR flip-flop jak pokazano na schemacie funkcjonalnym układu scalonego 555 Timer.

Tranzystory i falownik

Schemat funkcjonalny układu scalonego timera 555 składa się z jednego tranzystora npn $Q_{1}$ i jeden tranzystor pnp $Q_{2}$. Tranzystor npn$Q_{1}$zostanie WŁĄCZONY, jeśli napięcie podstawy do emitera jest dodatnie i większe niż napięcie włączenia. W przeciwnym razie zostanie WYŁĄCZONY.

Tranzystor pnp $Q_{2}$ jest używany jako buffer w celu odizolowania wejścia resetującego od przerzutnika SR i tranzystora npn $Q_{1}$.

Plik inverter zastosowany w schemacie funkcjonalnym układu scalonego 555 Timer nie tylko wykonuje działanie odwracające, ale także wzmacnia poziom mocy.

Układ scalony timera 555 może być używany w trybie monostabilnym w celu wytworzenia impulsu na wyjściu. Podobnie, może być używany w stabilnym działaniu w celu wytworzenia fali prostokątnej na wyjściu.

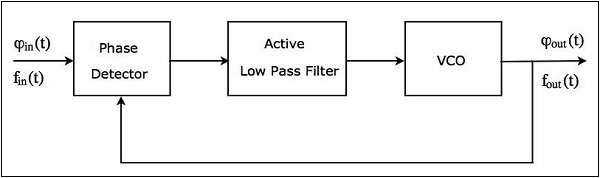

Pętla synchronizacji fazowej (PLL)jest jednym z najważniejszych bloków w systemach liniowych. Jest przydatny w systemach komunikacyjnych, takich jak radary, satelity, FM itp.

W tym rozdziale szczegółowo omówiono schemat blokowy PLL i IC 565.

Schemat blokowy PLL

Pętla z blokadą fazową (PLL) składa się głównie z następujących elementów three blocks -

- Detektor fazy

- Aktywny filtr dolnoprzepustowy

- Oscylator sterowany napięciem (VCO)

Plik block diagram PLL pokazano na poniższym rysunku -

Wyjście detektora fazy jest stosowane jako wejście aktywnego filtra dolnoprzepustowego. Podobnie, wyjście aktywnego filtra dolnoprzepustowego jest stosowane jako wejście VCO.

Plik working PLL wygląda następująco -

Phase detector wytwarza napięcie stałe, które jest proporcjonalne do różnicy faz między sygnałem wejściowym o częstotliwości $f_{in}$ oraz sygnał zwrotny (wyjściowy) o częstotliwości $f_{out}$.

ZA Phase detector jest mnożnikiem i wytwarza na wyjściu dwie składowe częstotliwości - sumę częstotliwości $f_{in}$ i $f_{out}$ i różnica częstotliwości $f_{in}$ & $f_{out}$.

Na active low pass filterwytwarza na wyjściu napięcie stałe po wyeliminowaniu składowej o wysokiej częstotliwości obecnej na wyjściu detektora fazy. Wzmacnia również sygnał.

ZA VCOwytwarza sygnał o określonej częstotliwości, gdy nie ma do niego żadnego sygnału wejściowego. Częstotliwość tę można przesunąć w dowolną stronę, przykładając do niej napięcie prądu stałego. Dlatego odchylenie częstotliwości jest wprost proporcjonalne do napięcia prądu stałego obecnego na wyjściu filtra dolnoprzepustowego.

Powyższe operacje mają miejsce do momentu, gdy częstotliwość VCO zrówna się z częstotliwością sygnału wejściowego. W zależności od typu aplikacji, możemy użyć wyjścia aktywnego filtra dolnoprzepustowego lub wyjścia VCO. PLL są używane w wieluapplications takie jak demodulator FM, generator zegara itp.

PLL działa w jednym z following three modes -

- Swobodny tryb pracy

- Tryb przechwytywania

- Tryb blokady

Początkowo PLL działa w free running modegdy żadne dane wejściowe nie są do niego stosowane. Gdy do PLL zostanie przyłożony sygnał wejściowy o określonej częstotliwości, częstotliwość sygnału wyjściowego VCO zacznie się zmieniać. Na tym etapie mówi się, że PLL działa wcapture mode. Częstotliwość sygnału wyjściowego VCO będzie się zmieniać w sposób ciągły, aż zrówna się z częstotliwością sygnału wejściowego. Teraz mówi się, że PLL działa wlock mode.

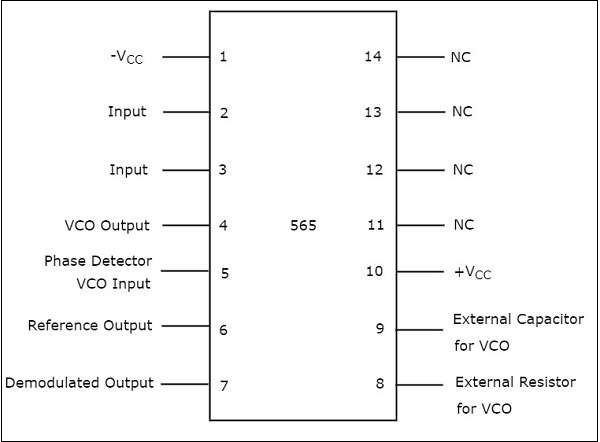

IC 565

IC 565 jest najczęściej używanym układem scalonym z zamkniętą fazą. Jest to 14-pinowy pakiet Dual-Inline (DIP). Plikpin diagram IC 565 pokazano na poniższym rysunku -

Z powyższego schematu wynika, że cel każdego pinu jest oczywisty. Z 14 pinów tylko 10 pinów (numer pinów od 1 do 10) jest używanych do działania PLL. Zatem pozostałe 4 piny (numer styku od 11 do 14) są oznaczone jako NC (brak połączenia).

Plik VCOgeneruje sygnał wyjściowy na pinie numer 4 układu IC 565, gdy styki o numerach 2 i 3 są uziemione. Matematycznie możemy zapisać częstotliwość wyjściową,$f_{out}$ VCO as.

$$f_{out}=\frac{0.25}{R_VC_V}$$

gdzie,

$R_{V}$ to zewnętrzny rezystor podłączony do styku numer 8

$C_{V}$ to zewnętrzny kondensator podłączony do styku numer 9

Wybierając odpowiednie wartości $R_{V}$ i $C_{V}$możemy ustalić (określić) częstotliwość wyjściową, $f_{out}$ VCO.

Pin numbers 4 and 5należy zewrzeć przewodem zewnętrznym, aby wyjście VCO mogło być użyte jako jedno z wejść detektora fazy.

IC 565 ma opór wewnętrzny wynoszący $3.6K\Omega$. Kondensator C musi być podłączony między pinami 7 i 10, aby uzyskaćlow pass filter z tym wewnętrznym oporem.

Zauważ, że zgodnie z wymaganiem musimy odpowiednio skonfigurować szpilki IC 565.

Funkcja a voltage regulatorma na celu utrzymanie stałego napięcia prądu stałego na wyjściu niezależnie od wahań napięcia na wejściu i (lub) wahań prądu obciążenia. Innymi słowy, regulator napięcia wytwarza regulowane napięcie wyjściowe DC.

Regulatory napięcia są również dostępne w postaci układów scalonych (IC). Nazywa się je asvoltage regulator ICs.

Rodzaje regulatorów napięcia

Tam są two types regulatorów napięcia -

- Stały regulator napięcia

- Regulowany regulator napięcia

W tym rozdziale omówiono kolejno te dwa typy regulatorów napięcia.

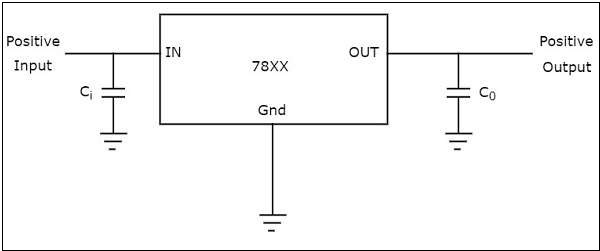

Stały regulator napięcia

ZA fixed voltage regulatorwytwarza stałe napięcie wyjściowe DC, które jest dodatnie lub ujemne. Innymi słowy, niektóre regulatory stałego napięcia wytwarzają dodatnie stałe wartości napięcia DC, podczas gdy inne wytwarzają ujemne stałe wartości napięcia DC.

78xx Układy scalone regulatorów napięcia wytwarzają dodatnie stałe wartości napięcia stałego, podczas gdy układy scalone regulatorów napięcia 79xx wytwarzają ujemne stałe wartości napięcia stałego.

Podczas pracy należy zwrócić uwagę na następujące punkty 78xx i 79xx układy scalone regulatorów napięcia -

„Xx” odpowiada dwucyfrowej liczbie i przedstawia ilość (wielkość) napięcia wytwarzanego przez układ scalony regulatora napięcia.

Oba układy scalone regulatorów napięcia 78xx i 79xx mają 3 pins każdy i trzeci pin służy do zbierania danych wyjściowych z nich.

Cel pierwszego i drugiego pinu tych dwóch typów układów scalonych jest inny -

Pierwsze i drugie piny 78xx Układy scalone regulatorów napięcia służą do podłączenia odpowiednio wejścia i masy.

Pierwsze i drugie piny 79xx Układy scalone regulatorów napięcia są używane odpowiednio do podłączenia masy i wejścia.

Przykłady

- Układ scalony regulatora napięcia 7805 wytwarza napięcie stałe o wartości +5 woltów.

- 7905 regulator napięcia IC wytwarza napięcie prądu stałego o wartości -5 woltów.

Poniższy rysunek pokazuje, jak utworzyć plik fixed positive voltage na wyjściu za pomocą stałego dodatniego regulatora napięcia z niezbędnymi połączeniami.

W powyższym rysunku, który wykazuje stałą regulacji dodatnie napięcie, kondensator C wejściowych i służy do zapobiegania niepożądane drgania i kondensator wyjściowy, C 0 działa jako filtr sieciowy do poprawy transjentów.

Note - zdobądź fixed negative voltage na wyjściu za pomocą stałego regulatora napięcia ujemnego z odpowiednimi połączeniami.

Regulowany regulator napięcia

Regulowany regulator napięcia wytwarza napięcie wyjściowe DC, które można dostosować do dowolnej innej wartości określonego zakresu napięcia. Stąd regulowany regulator napięcia jest również nazywany avariable voltage regulator.

Wartość napięcia wyjściowego DC regulowanego regulatora napięcia może być dodatnia lub ujemna.

Układ scalony regulatora napięcia LM317

LM317 IC stabilizatora napięcia może być użyty do wytworzenia pożądanej dodatniej stałej wartości napięcia stałego z dostępnego zakresu napięcia.

Układ scalony regulatora napięcia LM317 ma 3 styki. Pierwszy pin służy do regulacji napięcia wyjściowego, drugi pin służy do zbierania sygnału wyjściowego, a trzeci pin służy do podłączenia wejścia.

Regulowany pin (zacisk) jest wyposażony w rezystor zmienny, który umożliwia zmianę sygnału wyjściowego w szerokim zakresie.

Powyższy rysunek przedstawia nieregulowany zasilacz napędzający układ scalony regulatora napięcia LM 317, który jest powszechnie stosowany. Ten układ scalony może dostarczać prąd obciążenia 1,5 A w regulowanym zakresie wyjściowym od 1,25 V do 37 V.

Wszystkie wielkości świata rzeczywistego mają naturę analogową. Możemy przedstawić te wielkości elektrycznie jako sygnały analogowe. Naanalog signal jest sygnałem zmieniającym się w czasie, który ma dowolną liczbę wartości (odchyleń) dla danego przedziału czasu.

W przeciwieństwie do tego, a digital signal zmienia się nagle z jednego poziomu na inny i będzie miał tylko skończoną liczbę wartości (wariacji) dla danego przedziału czasowego.

W tym rozdziale omówiono typy konwerterów danych i ich specyfikacje.

Rodzaje konwerterów danych

Obwody elektroniczne, które mogą obsługiwać sygnały analogowe, nazywane są obwodami analogowymi. Podobnie obwody elektroniczne, które mogą być obsługiwane za pomocą sygnałów cyfrowych, nazywane są obwodami cyfrowymi. Konwerter danych to obwód elektroniczny, który konwertuje dane z jednej postaci na inną.

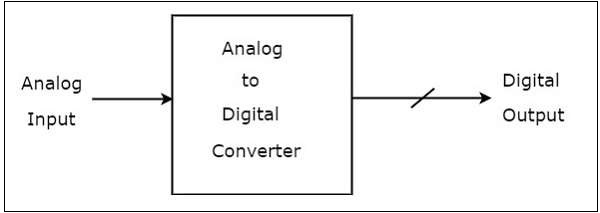

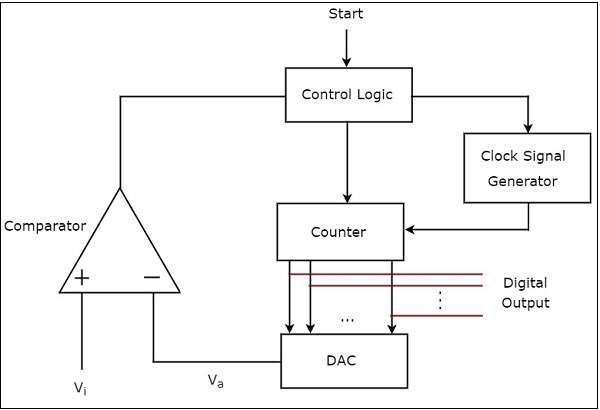

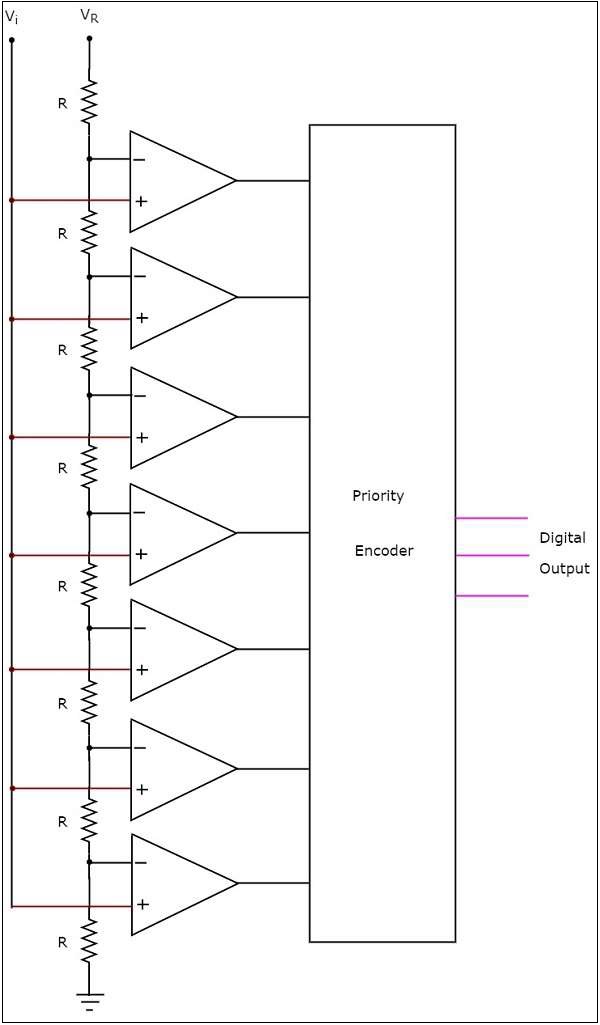

Istnieją dwa types of data converters -

- Analogowy do cyfrowego konwertera

- Przetwornik cyfrowo-analogowy

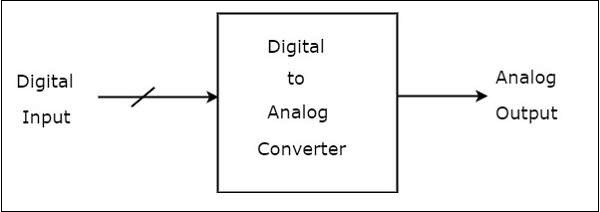

Jeśli chcemy podłączyć wyjście obwodu analogowego jako wejście obwodu cyfrowego, musimy umieścić między nimi obwód interfejsowy. Ten obwód interfejsu, który przekształca sygnał analogowy na sygnał cyfrowy, nazywa sięAnalog to Digital Converter.

Podobnie, jeśli chcemy podłączyć wyjście obwodu cyfrowego jako wejście obwodu analogowego, musimy umieścić między nimi obwód interfejsowy. Ten obwód interfejsu, który przekształca sygnał cyfrowy na sygnał analogowy, nosi nazwęDigital to Analog Converter.