Pośredni typ ADC

W poprzednim rozdziale omówiliśmy, czym jest ADC i przykłady ADC typu bezpośredniego. W tym rozdziale omówiono przetwornik ADC typu pośredniego.

Jeśli przetwornik ADC przeprowadza konwersję analogowo-cyfrową metodą pośrednią, wówczas nazywa się to plikiem Indirect type ADC. Ogólnie rzecz biorąc, najpierw konwertuje wejście analogowe na liniową funkcję czasu (lub częstotliwości), a następnie wytwarza cyfrowe (binarne) wyjście.

Najlepszy jest ADC z podwójnym nachyleniem examplepośredniego typu ADC. W tym rozdziale szczegółowo omówiono to zagadnienie.

ADC z podwójnym nachyleniem

Jak sama nazwa wskazuje, a dual slope ADC wytwarza równoważne wyjście cyfrowe dla odpowiedniego wejścia analogowego przy użyciu techniki dwóch (podwójnych) zboczy.

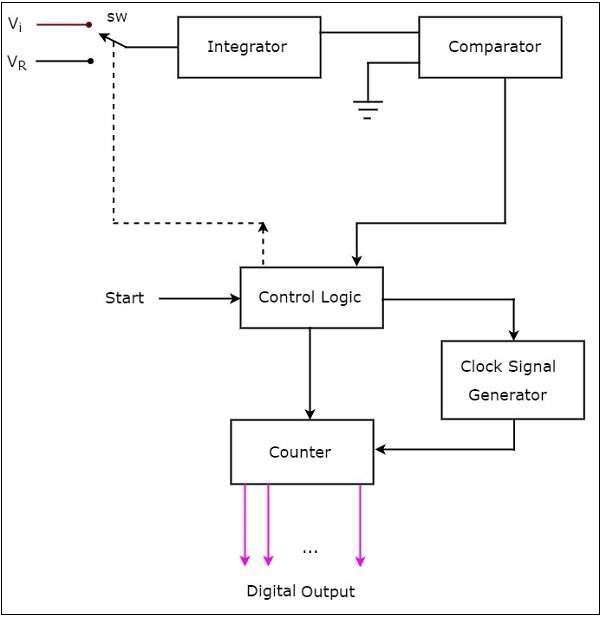

Plik block diagram ADC o podwójnym nachyleniu pokazano na poniższym rysunku -

ADC o podwójnym nachyleniu składa się głównie z 5 bloków: integratora, komparatora, generatora sygnału zegarowego, logiki sterującej i licznika.

Plik working ADC o podwójnym nachyleniu wygląda następująco -

Plik control logic resetuje licznik i włącza generator sygnału zegarowego w celu wysyłania impulsów zegarowych do licznika po otrzymaniu sygnału rozkazu startu.

Logika sterowania naciska przełącznik sw połączyć się z external analog input voltage $V_{i}$, gdy otrzyma sygnał startu. To napięcie wejściowe jest doprowadzane do integratora.

Dane wyjściowe integrator jest podłączony do jednego z dwóch wejść komparatora, a drugie wejście komparatora jest połączone z masą.

Comparator porównuje wyjście integratora z zerowymi woltami (masa) i generuje wyjście, które jest stosowane w logice sterującej.

Plik counterjest zwiększana o jeden dla każdego impulsu zegara, a jego wartość będzie w formacie binarnym (cyfrowym). Wytwarza sygnał przepełnienia do logiki sterowania, gdy jest zwiększany po osiągnięciu maksymalnej wartości zliczania. W tym momencie wszystkie bity licznika będą miały tylko zera.

Teraz logika sterująca naciska przełącznik sw połączyć się z negative referencenapięcie $ -V_ {ref} $. To ujemne napięcie odniesienia jest przykładane do integratora. Usuwa ładunek przechowywany w kondensatorze, aż osiągnie zero.

W tym momencie oba wejścia komparatora mają zero woltów. Zatem komparator wysyła sygnał do logiki sterowania. Teraz logika sterująca wyłącza generator sygnału zegara i zachowuje (utrzymuje) wartość licznika. Plikcounter value jest proporcjonalne do zewnętrznego analogowego napięcia wejściowego.

W tym momencie wyjście licznika zostanie wyświetlone jako digital output. Jest to prawie równoważne odpowiedniej wartości zewnętrznego wejścia analogowego $ V_ {i} $.

ADC z podwójnym nachyleniem jest używany w aplikacjach, w których accuracy jest ważniejszy podczas konwersji wejścia analogowego na jego równoważne dane cyfrowe (binarne).