Краткое руководство

В современном мире электроники термин Digital обычно ассоциируется с компьютером, потому что термин Digitalвыводится из того, как компьютеры выполняют операции, путем подсчета цифр. В течение многих лет цифровая электроника применялась только в компьютерных системах. Но в наши дни цифровая электроника используется во многих других приложениях. Ниже приведены некоторые примеры, в которыхDigital electronics активно используется.

- Управление производственными процессами

- Военная система

- Television

- Система связи

- Медицинское оборудование

- Radar

- Navigation

Сигнал

Signalможно определить как физическую величину, которая содержит некоторую информацию. Это функция одной или нескольких независимых переменных. Сигналы бывают двух типов.

- Аналоговый сигнал

- Цифровой сигнал

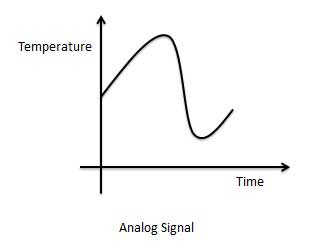

Аналоговый сигнал

An analog signalопределяется как сигнал, имеющий непрерывные значения. Аналоговый сигнал может иметь бесконечное количество различных значений. В реальном мире большинство вещей, наблюдаемых в природе, являются аналогами. Ниже приведены примеры аналоговых сигналов.

- Temperature

- Pressure

- Distance

- Sound

- Voltage

- Current

- Power

Графическое представление аналогового сигнала (температуры)

Цепи, обрабатывающие аналоговые сигналы, называются аналоговыми цепями или системами. Примеры аналоговой системы следующие.

- Filter

- Amplifiers

- Телевизионный приемник

- Регулятор скорости двигателя

Недостаток аналоговых систем

- Меньшая точность

- Меньшая универсальность

- Больше шумового эффекта

- Больше искажений

- Больше влияние погоды

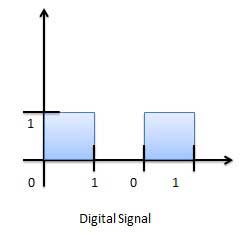

Цифровой сигнал

А digital signalопределяется как сигнал, который имеет только конечное число различных значений. Цифровые сигналы не являются непрерывными сигналами. В цифровом электронном калькуляторе ввод осуществляется с помощью переключателей. Этот вход преобразуется в электрический сигнал, который имеет два дискретных значения или уровня. Один из них можно назвать низким уровнем, а другой - высоким уровнем. Сигнал всегда будет одним из двух уровней. Этот тип сигнала называется цифровым сигналом. Ниже приведены примеры цифрового сигнала.

- Двоичный сигнал

- Восьмеричный сигнал

- Шестнадцатеричный сигнал

Графическое представление цифрового сигнала (двоичного)

Цепи, обрабатывающие цифровые сигналы, называются цифровыми системами или цифровыми цепями. Примеры цифровых систем следующие.

- Registers

- Flip-flop

- Counters

- Microprocessors

Преимущество цифровых систем

- Больше точности

- Больше универсальности

- Меньше искажений

- Легко общаться

- Возможное хранение информации

Сравнение аналогового и цифрового сигнала

| SN | Аналоговый сигнал | Цифровой сигнал |

|---|---|---|

| 1 | Аналоговый сигнал имеет бесконечные значения. | Цифровой сигнал имеет конечное количество значений. |

| 2 | Аналоговый сигнал имеет непрерывный характер. | Цифровой сигнал имеет дискретный характер. |

| 3 | Аналоговый сигнал генерируется преобразователями и генераторами сигналов. | Цифровой сигнал генерируется аналого-цифровым преобразователем. |

| 4 | Пример аналогового сигнала - синусоида, треугольные волны. | Пример цифрового сигнала - двоичный сигнал. |

Цифровая система может понимать позиционную систему счисления только там, где есть несколько символов, называемых цифрами, и эти символы представляют разные значения в зависимости от позиции, которую они занимают в номере.

Значение каждой цифры в числе можно определить с помощью

Цифра

Положение цифры в номере

Основание системы счисления (где основание определяется как общее количество цифр, доступных в системе счисления).

Десятичная система счисления

Система счисления, которую мы используем в повседневной жизни, - это десятичная система счисления. Десятичная система счисления имеет основание 10, поскольку в ней используются 10 цифр от 0 до 9. В десятичной системе счисления последовательные позиции слева от десятичной точки представляют единицы, десятки, сотни, тысячи и так далее.

Каждая позиция представляет собой определенную мощность основания (10). Например, десятичное число 1234 состоит из цифры 4 в позиции единиц, 3 в позиции десятков, 2 в позиции сотен и 1 в позиции тысяч, и его значение может быть записано как

(1×1000) + (2×100) + (3×10) + (4×l)

(1×103) + (2×102) + (3×101) + (4×l00)

1000 + 200 + 30 + 1

1234Как программист или ИТ-специалист, вы должны понимать следующие системы счисления, которые часто используются в компьютерах.

| SN | Система номеров и описание |

|---|---|

| 1 | Binary Number System База 2. Используемые цифры: 0, 1 |

| 2 | Octal Number System База 8. Используемые цифры: от 0 до 7. |

| 3 | Hexa Decimal Number System База 16. Используемые цифры: от 0 до 9, используемые буквы: A- F |

Двоичная система счисления

Характеристики

Использует две цифры: 0 и 1.

Также называется системой счисления с основанием 2

Каждая позиция в двоичном числе представляет собой степень 0 основания (2). Пример: 2 0

Последняя позиция в двоичном числе представляет собой степень x основания (2). Пример: 2 x, где x представляет последнюю позицию - 1.

пример

Двоичное число: 10101 2

Расчет десятичного эквивалента -

| Шаг | Двоичное число | Десятичное число |

|---|---|---|

| Шаг 1 | 10101 2 | ((1 × 2 4 ) + (0 × 2 3 ) + (1 × 2 2 ) + (0 × 2 1 ) + (1 × 2 0 )) 10 |

| Шаг 2 | 10101 2 | (16 + 0 + 4 + 0 + 1) 10 |

| Шаг 3 | 10101 2 | 21 10 |

Note:10101 2 обычно записывается как 10101.

Восьмеричная система счисления

Характеристики

Использует восемь цифр, 0,1,2,3,4,5,6,7.

Также называется системой счисления с основанием 8

Каждая позиция восьмеричного числа представляет собой 0 степень основания (8). Пример: 8 0

Последняя позиция в восьмеричном числе представляет собой степень x основания (8). Пример: 8 x, где x представляет последнюю позицию - 1.

пример

Восьмеричное число - 12570 8

Расчет десятичного эквивалента -

| Шаг | Восьмеричное число | Десятичное число |

|---|---|---|

| Шаг 1 | 12570 8 | ((1 × 8 4 ) + (2 × 8 3 ) + (5 × 8 2 ) + (7 × 8 1 ) + (0 × 8 0 )) 10 |

| Шаг 2 | 12570 8 | (4096 + 1024 + 320 + 56 + 0) 10 |

| Шаг 3 | 12570 8 | 5496 10 |

Note:12570 8 обычно записывается как 12570.

Шестнадцатеричная система счисления

Характеристики

Использует 10 цифр и 6 букв, 0,1,2,3,4,5,6,7,8,9, A, B, C, D, E, F.

Буквы обозначают числа, начинающиеся с 10. A = 10, B = 11, C = 12, D = 13, E = 14, F = 15.

Также называется системой счисления с основанием 16.

Каждая позиция в шестнадцатеричном числе представляет собой степень 0 основания (16). Пример 16 0 .

Последняя позиция в шестнадцатеричном числе представляет собой степень x основания (16). Пример 16 x, где x представляет последнюю позицию - 1.

Пример -

Шестнадцатеричное число: 19FDE 16

Расчет десятичного эквивалента -

| Шаг | Шестнадцатеричное число | Десятичное число |

|---|---|---|

| Шаг 1 | 19FDE 16 | ((1 × 16 4 ) + (9 × 16 3 ) + (F × 16 2 ) + (D × 16 1 ) + (E × 16 0 )) 10 |

| Шаг 2 | 19FDE 16 | ((1 × 16 4 ) + (9 × 16 3 ) + (15 × 16 2 ) + (13 × 16 1 ) + (14 × 16 0 )) 10 |

| Шаг 3 | 19FDE 16 | (65536 + 36864 + 3840 + 208 + 14) 10 |

| Шаг 4 | 19FDE 16 | 106462 10 |

Note −19FDE 16 обычно записывается как 19FDE.

Есть много методов или приемов, которые можно использовать для преобразования чисел из одной системы в другую. Мы продемонстрируем здесь следующее -

- От десятичной к другой системе счисления

- Из другой базовой системы в десятичную

- Из другой базовой системы в недесятичную

- Метод быстрого доступа - двоичный в восьмеричный

- Быстрый метод - от восьмеричного до двоичного

- Быстрый метод - двоичный в шестнадцатеричный

- Быстрый метод - из шестнадцатеричного в двоичный

От десятичной к другой системе счисления

Шаги

Step 1 - Разделите десятичное число, которое нужно преобразовать, на значение нового основания.

Step 2 - Получите остаток от шага 1 как крайнюю правую цифру (младшую значащую цифру) нового основного числа.

Step 3 - Разделите частное предыдущего деления на новое основание.

Step 4 - Запишите остаток от шага 3 как следующую цифру (слева) нового базового числа.

Повторите шаги 3 и 4, получая остатки справа налево, пока на шаге 3 частное не станет равным нулю.

Полученный таким образом последний остаток будет старшей значащей цифрой (MSD) нового основного числа.

Пример -

Десятичное число: 29 10

Расчет двоичного эквивалента -

| Шаг | Операция | Результат | Остаток |

|---|---|---|---|

| Шаг 1 | 29/2 | 14 | 1 |

| Шаг 2 | 14/2 | 7 | 0 |

| Шаг 3 | 7/2 | 3 | 1 |

| Шаг 4 | 3/2 | 1 | 1 |

| Шаг 5 | 1/2 | 0 | 1 |

Как упоминалось в шагах 2 и 4, остатки должны быть расположены в обратном порядке, чтобы первый остаток стал наименьшей значащей цифрой (LSD), а последний остаток стал наиболее значимой цифрой (MSD).

Десятичное число - 29 10 = двоичное число - 11101 2 .

Из другой базовой системы в десятичную

Шаги

Step 1 - Определите столбец (позиционное) значение каждой цифры (это зависит от положения цифры и основания системы счисления).

Step 2 - Умножьте полученные значения столбца (на шаге 1) на цифры в соответствующих столбцах.

Step 3 - Суммируйте продукты, рассчитанные на шаге 2. Итог - это эквивалентное десятичное значение.

пример

Двоичное число - 11101 2

Расчет десятичного эквивалента -

| Шаг | Двоичное число | Десятичное число |

|---|---|---|

| Шаг 1 | 11101 2 | ((1 × 2 4 ) + (1 × 2 3 ) + (1 × 2 2 ) + (0 × 2 1 ) + (1 × 2 0 )) 10 |

| Шаг 2 | 11101 2 | (16 + 8 + 4 + 0 + 1) 10 |

| Шаг 3 | 11101 2 | 29 10 |

Двоичное число - 11101 2 = Десятичное число - 29 10

Из другой базовой системы в недесятичную систему

Шаги

Step 1 - Преобразуйте исходное число в десятичное число (основание 10).

Step 2 - Преобразуйте полученное десятичное число в новое базовое число.

пример

Восьмеричное число - 25 8

Расчет двоичного эквивалента -

Шаг 1 - преобразовать в десятичный формат

| Шаг | Восьмеричное число | Десятичное число |

|---|---|---|

| Шаг 1 | 25 8 | ((2 × 8 1 ) + (5 × 8 0 )) 10 |

| Шаг 2 | 25 8 | (16 + 5) 10 |

| Шаг 3 | 25 8 | 21 10 |

Восьмеричное число - 25 8 = десятичное число - 21 10

Шаг 2 - преобразование десятичного числа в двоичное

| Шаг | Операция | Результат | Остаток |

|---|---|---|---|

| Шаг 1 | 21/2 | 10 | 1 |

| Шаг 2 | 10/2 | 5 | 0 |

| Шаг 3 | 5/2 | 2 | 1 |

| Шаг 4 | 2/2 | 1 | 0 |

| Шаг 5 | 1/2 | 0 | 1 |

Десятичное число - 21 10 = двоичное число - 10101 2

Восьмеричное число - 25 8 = двоичное число - 10101 2

Метод быстрого доступа - двоичный в восьмеричный

Шаги

Step 1 - Разделите двоичные цифры на группы по три (начиная справа).

Step 2 - Преобразуйте каждую группу из трех двоичных цифр в одну восьмеричную цифру.

пример

Двоичное число - 10101 2

Расчет восьмеричного эквивалента -

| Шаг | Двоичное число | Восьмеричное число |

|---|---|---|

| Шаг 1 | 10101 2 | 010 101 |

| Шаг 2 | 10101 2 | 2 8 5 8 |

| Шаг 3 | 10101 2 | 25 8 |

Двоичное число - 10101 2 = восьмеричное число - 25 8

Быстрый метод - от восьмеричного до двоичного

Шаги

Step 1 - Преобразуйте каждую восьмеричную цифру в трехзначное двоичное число (восьмеричные цифры можно рассматривать как десятичные для этого преобразования).

Step 2 - Объедините все полученные двоичные группы (по 3 цифры каждая) в одно двоичное число.

пример

Восьмеричное число - 25 8

Расчет двоичного эквивалента -

| Шаг | Восьмеричное число | Двоичное число |

|---|---|---|

| Шаг 1 | 25 8 | 2 10 5 10 |

| Шаг 2 | 25 8 | 010 2 101 2 |

| Шаг 3 | 25 8 | 010101 2 |

Восьмеричное число - 25 8 = двоичное число - 10101 2

Быстрый метод - двоичный в шестнадцатеричный

Шаги

Step 1 - Разделите двоичные цифры на группы по четыре (начиная справа).

Step 2 - Преобразуйте каждую группу из четырех двоичных цифр в один шестнадцатеричный символ.

пример

Двоичное число - 10101 2

Расчет шестнадцатеричного эквивалента -

| Шаг | Двоичное число | Шестнадцатеричное число |

|---|---|---|

| Шаг 1 | 10101 2 | 0001 0101 |

| Шаг 2 | 10101 2 | 1 10 5 10 |

| Step 3 | 101012 | 1516 |

Binary Number − 101012 = Hexadecimal Number − 1516

Shortcut method - Hexadecimal to Binary

Steps

Step 1 − Convert each hexadecimal digit to a 4 digit binary number (the hexadecimal digits may be treated as decimal for this conversion).

Step 2 − Combine all the resulting binary groups (of 4 digits each) into a single binary number.

Example

Hexadecimal Number − 1516

Calculating Binary Equivalent −

| Step | Hexadecimal Number | Binary Number |

|---|---|---|

| Step 1 | 1516 | 110 510 |

| Step 2 | 1516 | 00012 01012 |

| Step 3 | 1516 | 000101012 |

Hexadecimal Number − 1516 = Binary Number − 101012

In the coding, when numbers, letters or words are represented by a specific group of symbols, it is said that the number, letter or word is being encoded. The group of symbols is called as a code. The digital data is represented, stored and transmitted as group of binary bits. This group is also called as binary code. The binary code is represented by the number as well as alphanumeric letter.

Advantages of Binary Code

Following is the list of advantages that binary code offers.

Binary codes are suitable for the computer applications.

Binary codes are suitable for the digital communications.

Binary codes make the analysis and designing of digital circuits if we use the binary codes.

Since only 0 & 1 are being used, implementation becomes easy.

Classification of binary codes

The codes are broadly categorized into following four categories.

- Weighted Codes

- Non-Weighted Codes

- Binary Coded Decimal Code

- Alphanumeric Codes

- Error Detecting Codes

- Error Correcting Codes

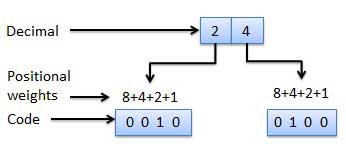

Weighted Codes

Weighted binary codes are those binary codes which obey the positional weight principle. Each position of the number represents a specific weight. Several systems of the codes are used to express the decimal digits 0 through 9. In these codes each decimal digit is represented by a group of four bits.

Non-Weighted Codes

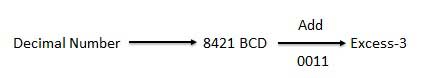

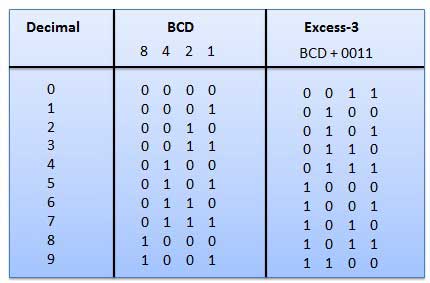

In this type of binary codes, the positional weights are not assigned. The examples of non-weighted codes are Excess-3 code and Gray code.

Excess-3 code

The Excess-3 code is also called as XS-3 code. It is non-weighted code used to express decimal numbers. The Excess-3 code words are derived from the 8421 BCD code words adding (0011)2 or (3)10 to each code word in 8421. The excess-3 codes are obtained as follows −

Example

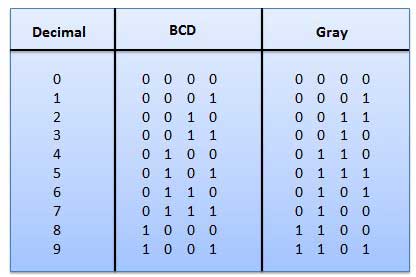

Gray Code

It is the non-weighted code and it is not arithmetic codes. That means there are no specific weights assigned to the bit position. It has a very special feature that, only one bit will change each time the decimal number is incremented as shown in fig. As only one bit changes at a time, the gray code is called as a unit distance code. The gray code is a cyclic code. Gray code cannot be used for arithmetic operation.

Application of Gray code

Gray code is popularly used in the shaft position encoders.

A shaft position encoder produces a code word which represents the angular position of the shaft.

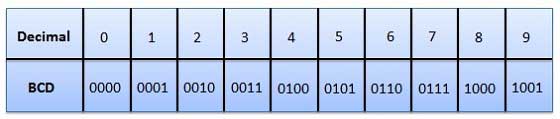

Binary Coded Decimal (BCD) code

In this code each decimal digit is represented by a 4-bit binary number. BCD is a way to express each of the decimal digits with a binary code. In the BCD, with four bits we can represent sixteen numbers (0000 to 1111). But in BCD code only first ten of these are used (0000 to 1001). The remaining six code combinations i.e. 1010 to 1111 are invalid in BCD.

Advantages of BCD Codes

- It is very similar to decimal system.

- We need to remember binary equivalent of decimal numbers 0 to 9 only.

Disadvantages of BCD Codes

The addition and subtraction of BCD have different rules.

The BCD arithmetic is little more complicated.

BCD needs more number of bits than binary to represent the decimal number. So BCD is less efficient than binary.

Alphanumeric codes

A binary digit or bit can represent only two symbols as it has only two states '0' or '1'. But this is not enough for communication between two computers because there we need many more symbols for communication. These symbols are required to represent 26 alphabets with capital and small letters, numbers from 0 to 9, punctuation marks and other symbols.

The alphanumeric codes are the codes that represent numbers and alphabetic characters. Mostly such codes also represent other characters such as symbol and various instructions necessary for conveying information. An alphanumeric code should at least represent 10 digits and 26 letters of alphabet i.e. total 36 items. The following three alphanumeric codes are very commonly used for the data representation.

- American Standard Code for Information Interchange (ASCII).

- Extended Binary Coded Decimal Interchange Code (EBCDIC).

- Five bit Baudot Code.

ASCII code is a 7-bit code whereas EBCDIC is an 8-bit code. ASCII code is more commonly used worldwide while EBCDIC is used primarily in large IBM computers.

Error Codes

There are binary code techniques available to detect and correct data during data transmission.

| Error Code | Description |

|---|---|

Error Detection and Correction |

Error detection and correction code techniques |

There are many methods or techniques which can be used to convert code from one format to another. We'll demonstrate here the following

- Binary to BCD Conversion

- BCD to Binary Conversion

- BCD to Excess-3

- Excess-3 to BCD

Binary to BCD Conversion

Steps

Step 1 -- Convert the binary number to decimal.

Step 2 -- Convert decimal number to BCD.

Example − convert (11101)2 to BCD.

Step 1 − Convert to Decimal

Binary Number − 111012

Calculating Decimal Equivalent −

| Step | Binary Number | Decimal Number |

|---|---|---|

| Step 1 | 111012 | ((1 × 24) + (1 × 23) + (1 × 22) + (0 × 21) + (1 × 20))10 |

| Step 2 | 111012 | (16 + 8 + 4 + 0 + 1)10 |

| Step 3 | 111012 | 2910 |

Binary Number − 111012 = Decimal Number − 2910

Step 2 − Convert to BCD

Decimal Number − 2910

Calculating BCD Equivalent. Convert each digit into groups of four binary digits equivalent.

| Step | Decimal Number | Conversion |

|---|---|---|

| Step 1 | 2910 | 00102 10012 |

| Step 2 | 2910 | 00101001BCD |

Result

(11101)2 = (00101001)BCDBCD to Binary Conversion

Steps

Step 1 -- Convert the BCD number to decimal.

Step 2 -- Convert decimal to binary.

Example − convert (00101001)BCD to Binary.

Step 1 - Convert to BCD

BCD Number − (00101001)BCD

Calculating Decimal Equivalent. Convert each four digit into a group and get decimal equivalent for each group.

| Step | BCD Number | Conversion |

|---|---|---|

| Step 1 | (00101001)BCD | 00102 10012 |

| Step 2 | (00101001)BCD | 210 910 |

| Step 3 | (00101001)BCD | 2910 |

BCD Number − (00101001)BCD = Decimal Number − 2910

Step 2 - Convert to Binary

Used long division method for decimal to binary conversion.

Decimal Number − 2910

Calculating Binary Equivalent −

| Step | Operation | Result | Remainder |

|---|---|---|---|

| Step 1 | 29 / 2 | 14 | 1 |

| Step 2 | 14 / 2 | 7 | 0 |

| Step 3 | 7 / 2 | 3 | 1 |

| Step 4 | 3 / 2 | 1 | 1 |

| Step 5 | 1 / 2 | 0 | 1 |

As mentioned in Steps 2 and 4, the remainders have to be arranged in the reverse order so that the first remainder becomes the least significant digit (LSD) and the last remainder becomes the most significant digit (MSD).

Decimal Number − 2910 = Binary Number − 111012

Result

(00101001)BCD = (11101)2BCD to Excess-3

Steps

Step 1 -- Convert BCD to decimal.

Step 2 -- Add (3)10 to this decimal number.

Step 3 -- Convert into binary to get excess-3 code.

Example − convert (0110)BCD to Excess-3.

Step 1 − Convert to decimal

(0110)BCD = 610

Step 2 − Add 3 to decimal

(6)10 + (3)10 = (9)10

Step 3 − Convert to Excess-3

(9)10 = (1001)2

Result

(0110)BCD = (1001)XS-3Excess-3 to BCD Conversion

Steps

Step 1 -- Subtract (0011)2 from each 4 bit of excess-3 digit to obtain the corresponding BCD code.

Example − convert (10011010)XS-3 to BCD.

Given XS-3 number = 1 0 0 1 1 0 1 0

Subtract (0011)2 = 1 0 0 1 0 1 1 1

--------------------

BCD = 0 1 1 0 0 1 1 1Result

(10011010)XS-3 = (01100111)BCDComplements are used in the digital computers in order to simplify the subtraction operation and for the logical manipulations. For each radix-r system (radix r represents base of number system) there are two types of complements.

| S.N. | Complement | Description |

|---|---|---|

| 1 | Radix Complement | The radix complement is referred to as the r's complement |

| 2 | Diminished Radix Complement | The diminished radix complement is referred to as the (r-1)'s complement |

Binary system complements

As the binary system has base r = 2. So the two types of complements for the binary system are 2's complement and 1's complement.

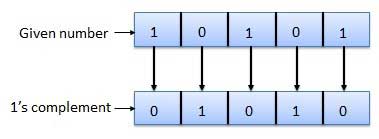

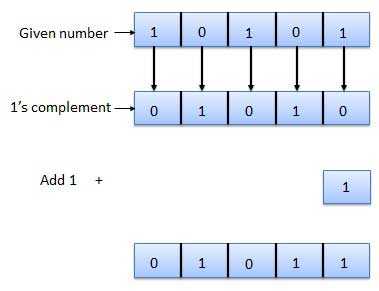

1's complement

The 1's complement of a number is found by changing all 1's to 0's and all 0's to 1's. This is called as taking complement or 1's complement. Example of 1's Complement is as follows.

2's complement

The 2's complement of binary number is obtained by adding 1 to the Least Significant Bit (LSB) of 1's complement of the number.

2's complement = 1's complement + 1

Example of 2's Complement is as follows.

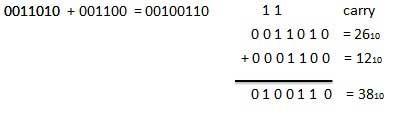

Binary arithmetic is essential part of all the digital computers and many other digital system.

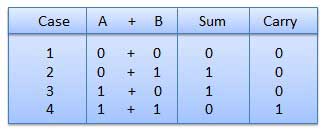

Binary Addition

It is a key for binary subtraction, multiplication, division. There are four rules of binary addition.

In fourth case, a binary addition is creating a sum of (1 + 1 = 10) i.e. 0 is written in the given column and a carry of 1 over to the next column.

Example − Addition

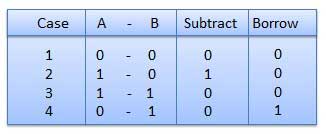

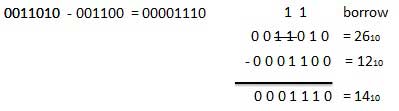

Binary Subtraction

Subtraction and Borrow, these two words will be used very frequently for the binary subtraction. There are four rules of binary subtraction.

Example − Subtraction

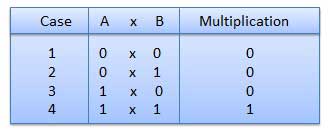

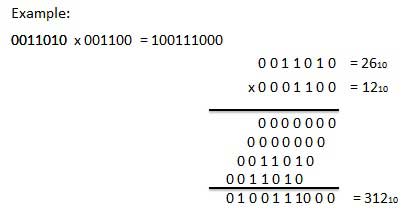

Binary Multiplication

Binary multiplication is similar to decimal multiplication. It is simpler than decimal multiplication because only 0s and 1s are involved. There are four rules of binary multiplication.

Example − Multiplication

Binary Division

Binary division is similar to decimal division. It is called as the long division procedure.

Example − Division

Octal Number System

Following are the characteristics of an octal number system.

Uses eight digits, 0,1,2,3,4,5,6,7.

Also called base 8 number system.

Each position in an octal number represents a 0 power of the base (8). Example: 80

Last position in an octal number represents an x power of the base (8). Example: 8x where x represents the last position - 1.

Example

Octal Number − 125708

Calculating Decimal Equivalent −

| Step | Octal Number | Decimal Number |

|---|---|---|

| Step 1 | 125708 | ((1 × 84) + (2 × 83) + (5 × 82) + (7 × 81) + (0 × 80))10 |

| Step 2 | 125708 | (4096 + 1024 + 320 + 56 + 0)10 |

| Step 3 | 125708 | 549610 |

Note − 125708 is normally written as 12570.

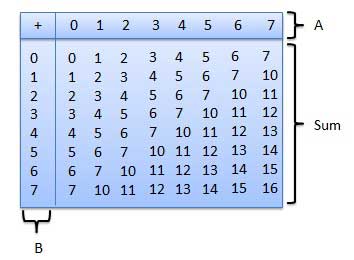

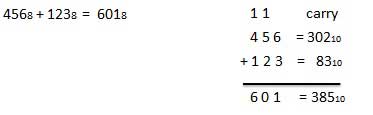

Octal Addition

Following octal addition table will help you to handle octal addition.

To use this table, simply follow the directions used in this example: Add 68 and 58. Locate 6 in the A column then locate the 5 in the B column. The point in 'sum' area where these two columns intersect is the 'sum' of two numbers.

68 + 58 = 138.Example − Addition

Octal Subtraction

The subtraction of octal numbers follows the same rules as the subtraction of numbers in any other number system. The only variation is in borrowed number. In the decimal system, you borrow a group of 1010. In the binary system, you borrow a group of 210. In the octal system you borrow a group of 810.

Example − Subtraction

Hexadecimal Number System

Following are the characteristics of a hexadecimal number system.

Uses 10 digits and 6 letters, 0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F.

Letters represents numbers starting from 10. A = 10, B = 11, C = 12, D = 13, E = 14, F = 15.

Also called base 16 number system.

Each position in a hexadecimal number represents a 0 power of the base (16). Example − 160

Last position in a hexadecimal number represents an x power of the base (16). Example − 16x where x represents the last position - 1.

Example

Hexadecimal Number − 19FDE16

Calculating Decimal Equivalent −

| Step | Hexadecimal Number | Decimal Number |

|---|---|---|

| Step 1 | 19FDE16 | ((1 × 164) + (9 × 163) + (F × 162) + (D × 161) + (E × 160))10 |

| Step 2 | 19FDE16 | ((1 × 164) + (9 × 163) + (15 × 162) + (13 × 161) + (14 × 160))10 |

| Step 3 | 19FDE16 | (65536 + 36864 + 3840 + 208 + 14)10 |

| Step 4 | 19FDE16 | 10646210 |

Note − 19FDE16 is normally written as 19FDE.

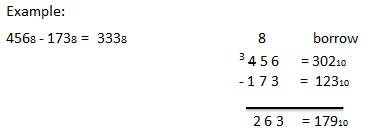

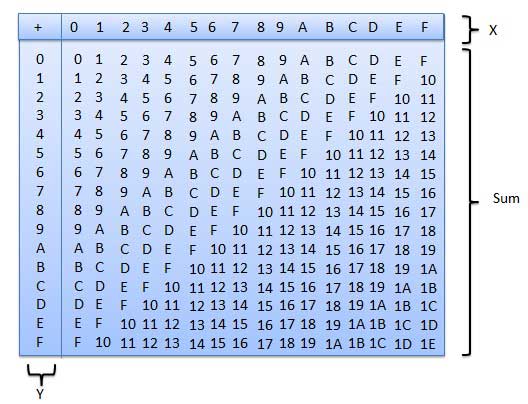

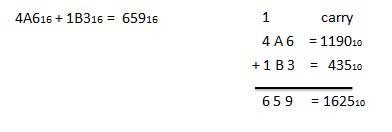

Hexadecimal Addition

Following hexadecimal addition table will help you greatly to handle Hexadecimal addition.

To use this table, simply follow the directions used in this example − Add A16 and 516. Locate A in the X column then locate the 5 in the Y column. The point in 'sum' area where these two columns intersect is the sum of two numbers.

A16 + 516 = F16.Example − Addition

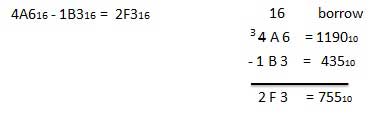

Hexadecimal Subtraction

The subtraction of hexadecimal numbers follow the same rules as the subtraction of numbers in any other number system. The only variation is in borrowed number. In the decimal system, you borrow a group of 1010. In the binary system, you borrow a group of 210. In the hexadecimal system you borrow a group of 1610.

Example - Subtraction

Boolean Algebra is used to analyze and simplify the digital (logic) circuits. It uses only the binary numbers i.e. 0 and 1. It is also called as Binary Algebra or logical Algebra. Boolean algebra was invented by George Boole in 1854.

Rule in Boolean Algebra

Following are the important rules used in Boolean algebra.

Variable used can have only two values. Binary 1 for HIGH and Binary 0 for LOW.

Complement of a variable is represented by an overbar (-). Thus, complement of variable B is represented as

. Thus if B = 0 then = 1 and B = 1 then

= 1 and B = 1 then = 0.

= 0.

ORing of the variables is represented by a plus (+) sign between them. For example ORing of A, B, C is represented as A + B + C.

Logical ANDing of the two or more variable is represented by writing a dot between them such as A.B.C. Sometime the dot may be omitted like ABC.

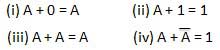

Boolean Laws

There are six types of Boolean Laws.

Commutative law

Any binary operation which satisfies the following expression is referred to as commutative operation.

Commutative law states that changing the sequence of the variables does not have any effect on the output of a logic circuit.

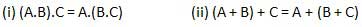

Associative law

This law states that the order in which the logic operations are performed is irrelevant as their effect is the same.

Distributive law

Distributive law states the following condition.

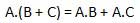

AND law

These laws use the AND operation. Therefore they are called as AND laws.

OR law

These laws use the OR operation. Therefore they are called as OR laws.

INVERSION law

This law uses the NOT operation. The inversion law states that double inversion of a variable results in the original variable itself.

Important Boolean Theorems

Following are few important boolean Theorems.

| Boolean function/theorems | Description |

|---|---|

Boolean Functions |

Boolean Functions and Expressions, K-Map and NAND Gates realization |

De Morgan's Theorems |

De Morgan's Theorem 1 and Theorem 2 |

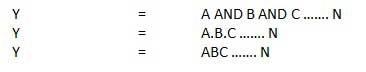

Logic gates are the basic building blocks of any digital system. It is an electronic circuit having one or more than one input and only one output. The relationship between the input and the output is based on a certain logic. Based on this, logic gates are named as AND gate, OR gate, NOT gate etc.

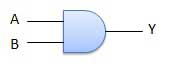

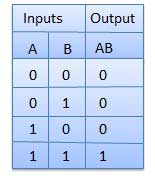

AND Gate

A circuit which performs an AND operation is shown in figure. It has n input (n >= 2) and one output.

Logic diagram

Truth Table

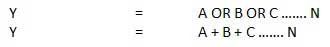

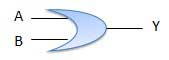

OR Gate

A circuit which performs an OR operation is shown in figure. It has n input (n >= 2) and one output.

Logic diagram

Truth Table

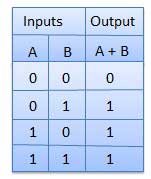

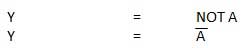

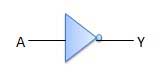

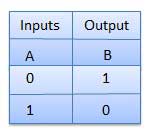

NOT Gate

NOT gate is also known as Inverter. It has one input A and one output Y.

Logic diagram

Truth Table

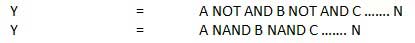

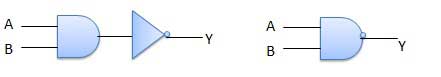

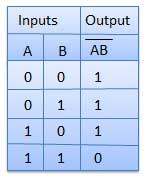

NAND Gate

A NOT-AND operation is known as NAND operation. It has n input (n >= 2) and one output.

Logic diagram

Truth Table

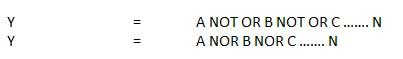

NOR Gate

A NOT-OR operation is known as NOR operation. It has n input (n >= 2) and one output.

Logic diagram

Truth Table

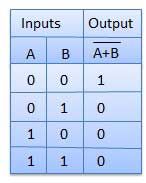

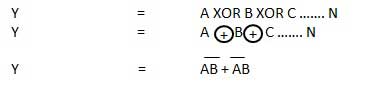

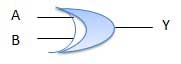

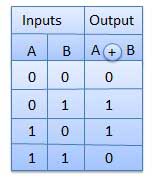

XOR Gate

XOR or Ex-OR gate is a special type of gate. It can be used in the half adder, full adder and subtractor. The exclusive-OR gate is abbreviated as EX-OR gate or sometime as X-OR gate. It has n input (n >= 2) and one output.

Logic diagram

Truth Table

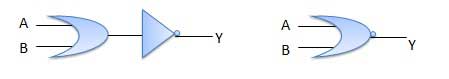

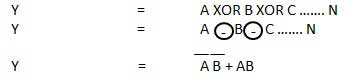

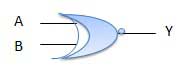

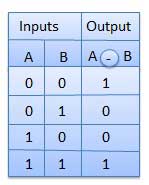

XNOR Gate

XNOR gate is a special type of gate. It can be used in the half adder, full adder and subtractor. The exclusive-NOR gate is abbreviated as EX-NOR gate or sometime as X-NOR gate. It has n input (n >= 2) and one output.

Logic diagram

Truth Table

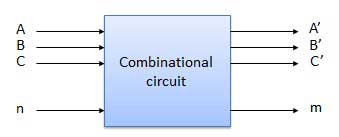

Combinational circuit is a circuit in which we combine the different gates in the circuit, for example encoder, decoder, multiplexer and demultiplexer. Some of the characteristics of combinational circuits are following −

The output of combinational circuit at any instant of time, depends only on the levels present at input terminals.

The combinational circuit do not use any memory. The previous state of input does not have any effect on the present state of the circuit.

A combinational circuit can have an n number of inputs and m number of outputs.

Block diagram

We're going to elaborate few important combinational circuits as follows.

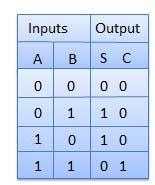

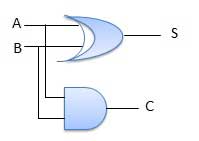

Half Adder

Half adder is a combinational logic circuit with two inputs and two outputs. The half adder circuit is designed to add two single bit binary number A and B. It is the basic building block for addition of two single bit numbers. This circuit has two outputs carry and sum.

Block diagram

Truth Table

Circuit Diagram

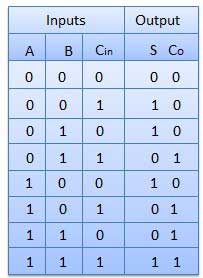

Full Adder

Full adder is developed to overcome the drawback of Half Adder circuit. It can add two one-bit numbers A and B, and carry c. The full adder is a three input and two output combinational circuit.

Block diagram

Truth Table

Circuit Diagram

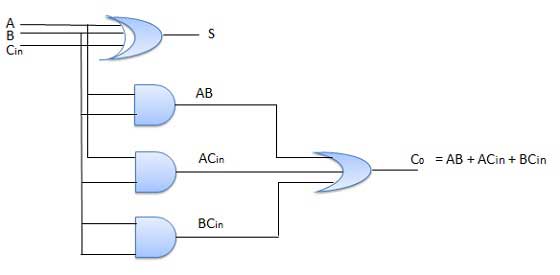

N-Bit Parallel Adder

The Full Adder is capable of adding only two single digit binary number along with a carry input. But in practical we need to add binary numbers which are much longer than just one bit. To add two n-bit binary numbers we need to use the n-bit parallel adder. It uses a number of full adders in cascade. The carry output of the previous full adder is connected to carry input of the next full adder.

4 Bit Parallel Adder

In the block diagram, A0 and B0 represent the LSB of the four bit words A and B. Hence Full Adder-0 is the lowest stage. Hence its Cin has been permanently made 0. The rest of the connections are exactly same as those of n-bit parallel adder is shown in fig. The four bit parallel adder is a very common logic circuit.

Block diagram

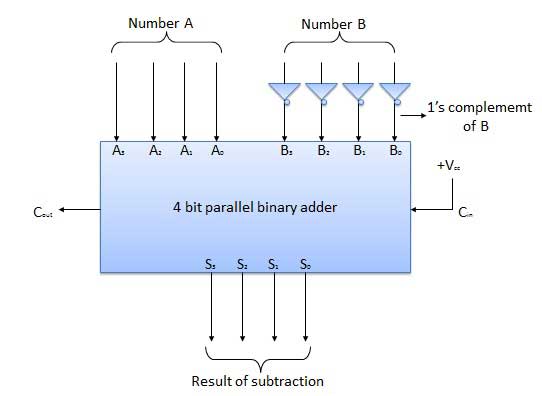

N-Bit Parallel Subtractor

The subtraction can be carried out by taking the 1's or 2's complement of the number to be subtracted. For example we can perform the subtraction (A-B) by adding either 1's or 2's complement of B to A. That means we can use a binary adder to perform the binary subtraction.

4 Bit Parallel Subtractor

The number to be subtracted (B) is first passed through inverters to obtain its 1's complement. The 4-bit adder then adds A and 2's complement of B to produce the subtraction. S3 S2 S1 S0 represents the result of binary subtraction (A-B) and carry output Cout represents the polarity of the result. If A > B then Cout = 0 and the result of binary form (A-B) then Cout = 1 and the result is in the 2's complement form.

Block diagram

Half Subtractors

Half subtractor is a combination circuit with two inputs and two outputs (difference and borrow). It produces the difference between the two binary bits at the input and also produces an output (Borrow) to indicate if a 1 has been borrowed. In the subtraction (A-B), A is called as Minuend bit and B is called as Subtrahend bit.

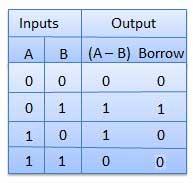

Truth Table

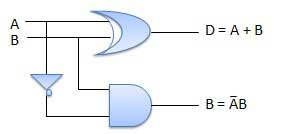

Circuit Diagram

Full Subtractors

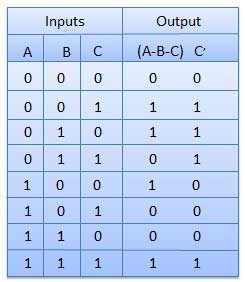

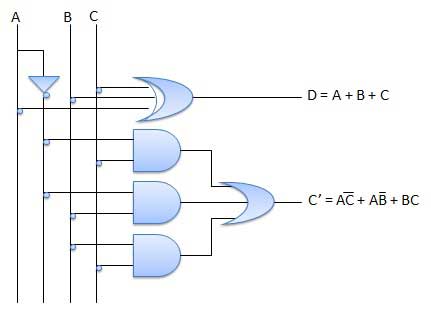

The disadvantage of a half subtractor is overcome by full subtractor. The full subtractor is a combinational circuit with three inputs A,B,C and two output D and C'. A is the 'minuend', B is 'subtrahend', C is the 'borrow' produced by the previous stage, D is the difference output and C' is the borrow output.

Truth Table

Circuit Diagram

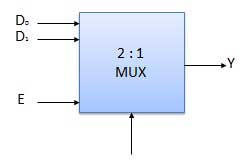

Multiplexers

Multiplexer is a special type of combinational circuit. There are n-data inputs, one output and m select inputs with 2m = n. It is a digital circuit which selects one of the n data inputs and routes it to the output. The selection of one of the n inputs is done by the selected inputs. Depending on the digital code applied at the selected inputs, one out of n data sources is selected and transmitted to the single output Y. E is called the strobe or enable input which is useful for the cascading. It is generally an active low terminal that means it will perform the required operation when it is low.

Block diagram

Multiplexers come in multiple variations

- 2 : 1 multiplexer

- 4 : 1 multiplexer

- 16 : 1 multiplexer

- 32 : 1 multiplexer

Block Diagram

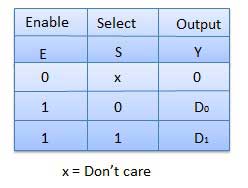

Truth Table

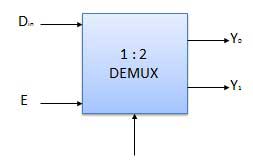

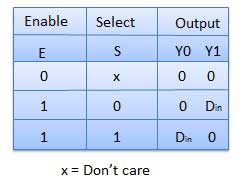

Demultiplexers

A demultiplexer performs the reverse operation of a multiplexer i.e. it receives one input and distributes it over several outputs. It has only one input, n outputs, m select input. At a time only one output line is selected by the select lines and the input is transmitted to the selected output line. A de-multiplexer is equivalent to a single pole multiple way switch as shown in fig.

Demultiplexers comes in multiple variations.

- 1 : 2 demultiplexer

- 1 : 4 demultiplexer

- 1 : 16 demultiplexer

- 1 : 32 demultiplexer

Block diagram

Truth Table

Decoder

A decoder is a combinational circuit. It has n input and to a maximum m = 2n outputs. Decoder is identical to a demultiplexer without any data input. It performs operations which are exactly opposite to those of an encoder.

Block diagram

Examples of Decoders are following.

- Code converters

- BCD to seven segment decoders

- Nixie tube decoders

- Relay actuator

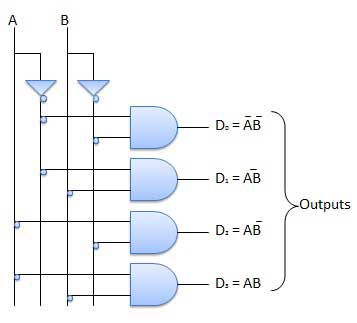

2 to 4 Line Decoder

The block diagram of 2 to 4 line decoder is shown in the fig. A and B are the two inputs where D through D are the four outputs. Truth table explains the operations of a decoder. It shows that each output is 1 for only a specific combination of inputs.

Block diagram

Truth Table

Logic Circuit

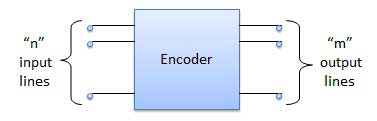

Encoder

Encoder is a combinational circuit which is designed to perform the inverse operation of the decoder. An encoder has n number of input lines and m number of output lines. An encoder produces an m bit binary code corresponding to the digital input number. The encoder accepts an n input digital word and converts it into an m bit another digital word.

Block diagram

Examples of Encoders are following.

- Priority encoders

- Decimal to BCD encoder

- Octal to binary encoder

- Hexadecimal to binary encoder

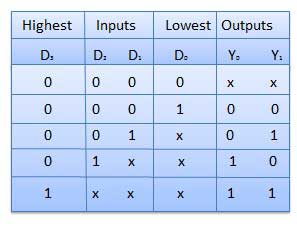

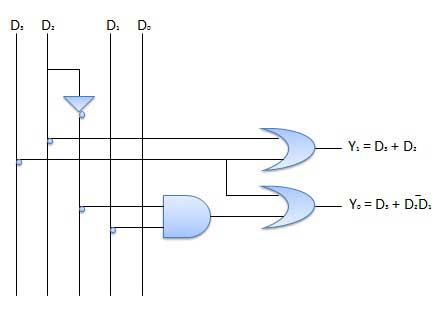

Priority Encoder

This is a special type of encoder. Priority is given to the input lines. If two or more input line are 1 at the same time, then the input line with highest priority will be considered. There are four input D0, D1, D2, D3 and two output Y0, Y1. Out of the four input D3 has the highest priority and D0 has the lowest priority. That means if D3 = 1 then Y1 Y1 = 11 irrespective of the other inputs. Similarly if D3 = 0 and D2 = 1 then Y1 Y0 = 10 irrespective of the other inputs.

Block diagram

Truth Table

Logic Circuit

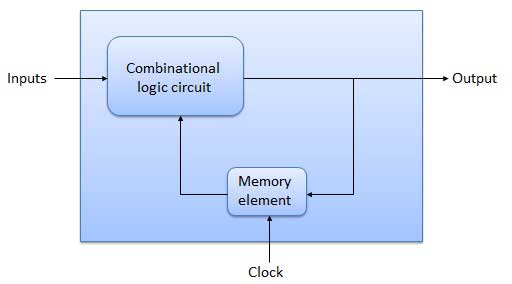

The combinational circuit does not use any memory. Hence the previous state of input does not have any effect on the present state of the circuit. But sequential circuit has memory so output can vary based on input. This type of circuits uses previous input, output, clock and a memory element.

Block diagram

Flip Flop

Flip flop is a sequential circuit which generally samples its inputs and changes its outputs only at particular instants of time and not continuously. Flip flop is said to be edge sensitive or edge triggered rather than being level triggered like latches.

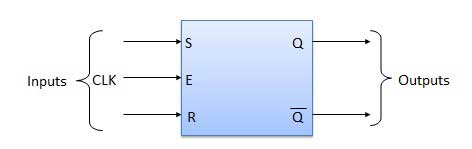

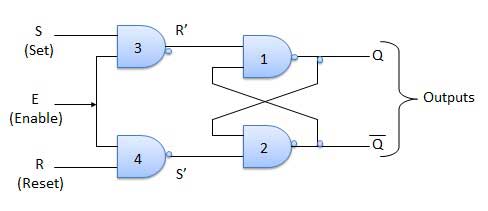

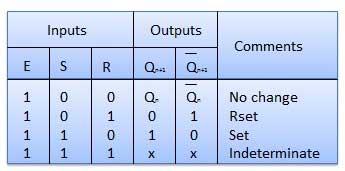

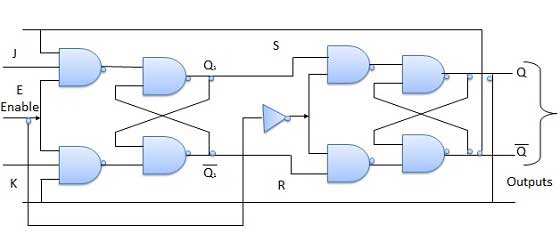

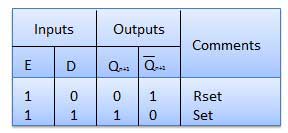

S-R Flip Flop

It is basically S-R latch using NAND gates with an additional enable input. It is also called as level triggered SR-FF. For this, circuit in output will take place if and only if the enable input (E) is made active. In short this circuit will operate as an S-R latch if E = 1 but there is no change in the output if E = 0.

Block Diagram

Circuit Diagram

Truth Table

Operation

| S.N. | Condition | Operation |

|---|---|---|

| 1 | S = R = 0 : No change | If S = R = 0 then output of NAND gates 3 and 4 are forced to become 1. Hence R' and S' both will be equal to 1. Since S' and R' are the input of the basic S-R latch using NAND gates, there will be no change in the state of outputs. |

| 2 | S = 0, R = 1, E = 1 | Since S = 0, output of NAND-3 i.e. R' = 1 and E = 1 the output of NAND-4 i.e. S' = 0. Hence Qn+1 = 0 and Qn+1 bar = 1. This is reset condition. |

| 3 | S = 1, R = 0, E = 1 | Output of NAND-3 i.e. R' = 0 and output of NAND-4 i.e. S' = 1. Hence output of S-R NAND latch is Qn+1 = 1 and Qn+1 bar = 0. This is the reset condition. |

| 4 | S = 1, R = 1, E = 1 | As S = 1, R = 1 and E = 1, the output of NAND gates 3 and 4 both are 0 i.e. S' = R' = 0. Hence the Race condition will occur in the basic NAND latch. |

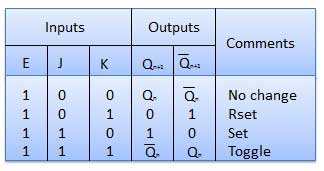

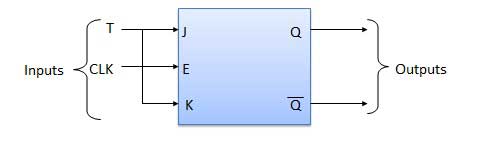

Master Slave JK Flip Flop

Master slave JK FF is a cascade of two S-R FF with feedback from the output of second to input of first. Master is a positive level triggered. But due to the presence of the inverter in the clock line, the slave will respond to the negative level. Hence when the clock = 1 (positive level) the master is active and the slave is inactive. Whereas when clock = 0 (low level) the slave is active and master is inactive.

Circuit Diagram

Truth Table

Operation

| S.N. | Condition | Operation |

|---|---|---|

| 1 | J = K = 0 (No change) | When clock = 0, the slave becomes active and master is inactive. But since the S and R inputs have not changed, the slave outputs will also remain unchanged. Therefore outputs will not change if J = K =0. |

| 2 | J = 0 and K = 1 (Reset) | Clock = 1 − Master active, slave inactive. Therefore outputs of the master become Q1 = 0 and Q1 bar = 1. That means S = 0 and R =1. Clock = 0 − Slave active, master inactive. Therefore outputs of the slave become Q = 0 and Q bar = 1. Again clock = 1 − Master active, slave inactive. Therefore even with the changed outputs Q = 0 and Q bar = 1 fed back to master, its output will be Q1 = 0 and Q1 bar = 1. That means S = 0 and R = 1. Hence with clock = 0 and slave becoming active the outputs of slave will remain Q = 0 and Q bar = 1. Thus we get a stable output from the Master slave. |

| 3 | J = 1 and K = 0 (Set) | Clock = 1 − Master active, slave inactive. Therefore outputs of the master become Q1 = 1 and Q1 bar = 0. That means S = 1 and R =0. Clock = 0 − Slave active, master inactive. Therefore outputs of the slave become Q = 1 and Q bar = 0. Again clock = 1 − then it can be shown that the outputs of the slave are stabilized to Q = 1 and Q bar = 0. |

| 4 | J = K = 1 (Toggle) | Clock = 1 − Master active, slave inactive. Outputs of master will toggle. So S and R also will be inverted. Clock = 0 − Slave active, master inactive. Outputs of slave will toggle. These changed output are returned back to the master inputs. But since clock = 0, the master is still inactive. So it does not respond to these changed outputs. This avoids the multiple toggling which leads to the race around condition. The master slave flip flop will avoid the race around condition. |

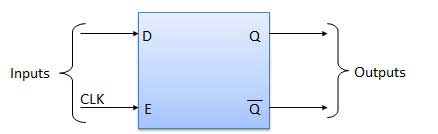

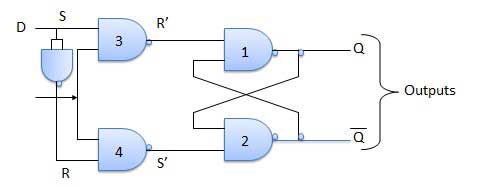

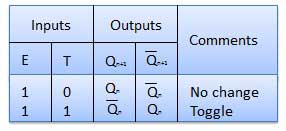

Delay Flip Flop / D Flip Flop

Delay Flip Flop or D Flip Flop is the simple gated S-R latch with a NAND inverter connected between S and R inputs. It has only one input. The input data is appearing at the output after some time. Due to this data delay between i/p and o/p, it is called delay flip flop. S and R will be the complements of each other due to NAND inverter. Hence S = R = 0 or S = R = 1, these input condition will never appear. This problem is avoid by SR = 00 and SR = 1 conditions.

Block Diagram

Circuit Diagram

Truth Table

Operation

| S.N. | Condition | Operation |

|---|---|---|

| 1 | E = 0 | Latch is disabled. Hence no change in output. |

| 2 | E = 1 and D = 0 | If E = 1 and D = 0 then S = 0 and R = 1. Hence irrespective of the present state, the next state is Qn+1 = 0 and Qn+1 bar = 1. This is the reset condition. |

| 3 | E = 1 and D = 1 | If E = 1 and D = 1, then S = 1 and R = 0. This will set the latch and Qn+1 = 1 and Qn+1 bar = 0 irrespective of the present state. |

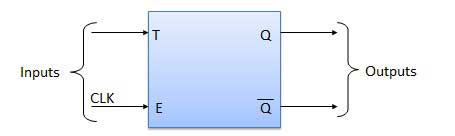

Toggle Flip Flop / T Flip Flop

Toggle flip flop is basically a JK flip flop with J and K terminals permanently connected together. It has only input denoted by T as shown in the Symbol Diagram. The symbol for positive edge triggered T flip flop is shown in the Block Diagram.

Symbol Diagram

Block Diagram

Truth Table

Operation

| S.N. | Condition | Operation |

|---|---|---|

| 1 | T = 0, J = K = 0 | The output Q and Q bar won't change |

| 2 | T = 1, J = K = 1 | Output will toggle corresponding to every leading edge of clock signal. |

Flip-flop is a 1 bit memory cell which can be used for storing the digital data. To increase the storage capacity in terms of number of bits, we have to use a group of flip-flop. Such a group of flip-flop is known as a Register. The n-bit register will consist of n number of flip-flop and it is capable of storing an n-bit word.

The binary data in a register can be moved within the register from one flip-flop to another. The registers that allow such data transfers are called as shift registers. There are four mode of operations of a shift register.

- Последовательный вход Последовательный выход

- Последовательный вход Параллельный выход

- Параллельный вход Последовательный выход

- Параллельный вход Параллельный выход

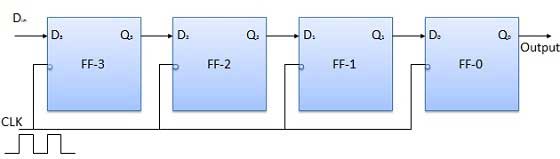

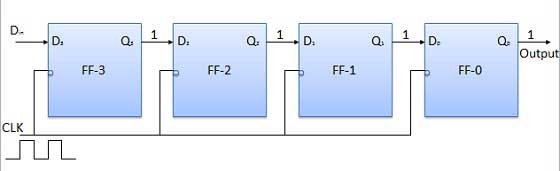

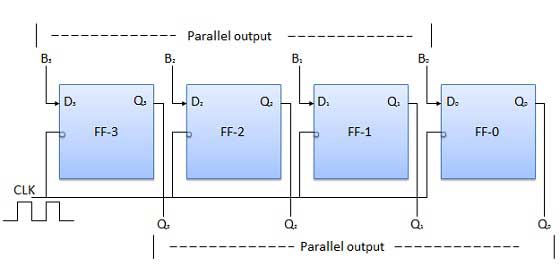

Последовательный вход Последовательный выход

Пусть все триггеры изначально находятся в состоянии сброса, т.е. Q 3 = Q 2 = Q 1 = Q 0 = 0. Если в регистр вносится запись четырехбитного двоичного числа 1 1 1 1, это число должно быть применительно кDinбит с первым примененным битом LSB. Вход D FF-3, т.е. D 3 подключен к последовательному входу данных.Din. Выход FF-3, т.е. Q 3 , подключен к входу следующего триггера, то есть D 2 и так далее.

Блок-схема

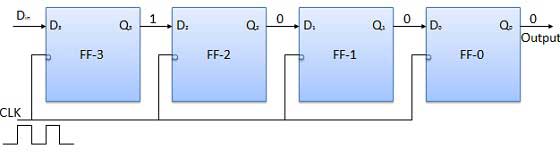

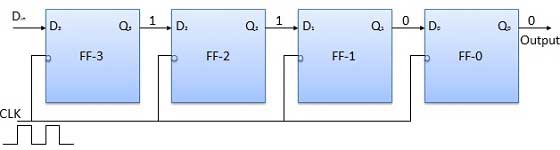

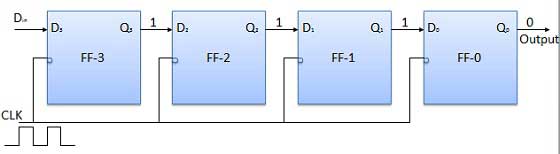

Операция

Перед применением синхросигнала, пусть Q 3 Q 2 Q 1 Q 0 = 0000 и примените бит LSB числа, которое нужно ввести, к D in . Итак, D in = D 3 = 1. Примените часы. На первом заднем фронте тактового сигнала устанавливается FF-3, и сохраненное слово в регистре - Q 3 Q 2 Q 1 Q 0 = 1000.

Примените следующий бит к D в . Итак, D in = 1. Как только наступит следующий отрицательный фронт тактового сигнала, FF-2 установится, и сохраненное слово изменится на Q 3 Q 2 Q 1 Q 0 = 1100.

Примените следующий бит, который нужно сохранить, то есть от 1 до D в . Подайте тактовый импульс. Как только наступит третий отрицательный фронт тактовой частоты, будет установлен FF-1, и выходной сигнал будет изменен на Q 3 Q 2 Q 1 Q 0 = 1110.

Аналогично, при D in = 1 и приходе четвертого отрицательного фронта тактового сигнала, сохраненное слово в регистре - Q 3 Q 2 Q 1 Q 0 = 1111.

Таблица правды

Формы волны

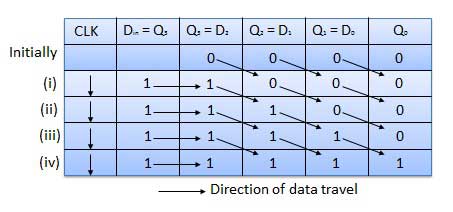

Последовательный вход Параллельный выход

В таких типах операций данные вводятся последовательно и выводятся параллельно.

Данные загружаются бит за битом. Выходы отключены, пока данные загружаются.

Как только загрузка данных завершается, все триггеры содержат свои требуемые данные, выходы активируются, так что все загруженные данные становятся доступными по всем линиям вывода одновременно.

Для загрузки четырехбитового слова требуется 4 тактовых цикла. Следовательно, скорость работы режима SIPO такая же, как и у режима SISO.

Блок-схема

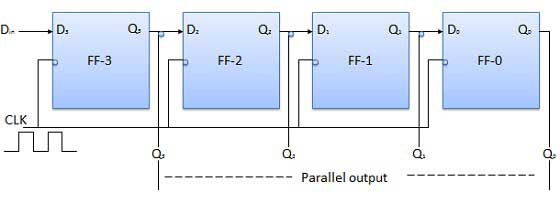

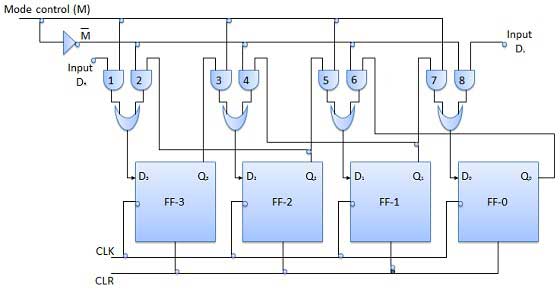

Параллельный вход и последовательный выход (PISO)

Биты данных вводятся параллельно.

Схема, показанная ниже, представляет собой четырехразрядный регистр последовательного вывода с параллельным входом.

Выход предыдущего триггера через комбинационную схему соединен со входом следующего.

Двоичное входное слово B 0 , B 1 , B 2 , B 3 подается через ту же комбинационную схему.

Есть два режима, в которых может работать эта схема, а именно - режим смены или режим нагрузки.

Режим загрузки

Когда линия шкалы сдвига / нагрузки имеет низкий уровень (0), элементы И 2, 4 и 6 становятся активными, они передают биты B 1 , B 2 , B 3 в соответствующие триггеры. На нижнем фронте тактового сигнала двоичный вход B 0 , B 1 , B 2 , B 3 будет загружен в соответствующие триггеры. Таким образом происходит параллельная загрузка.

Режим переключения

Когда линия шкалы сдвига / нагрузки является низкой (1), логические элементы И 2, 4 и 6 становятся неактивными. Следовательно, параллельная загрузка данных становится невозможной. Но активируются логические элементы И 1,3 и 5. Следовательно, сдвиг данных слева направо бит за битом при применении тактовых импульсов. Таким образом, имеет место параллельная последовательная операция вывода.

Блок-схема

Параллельный вход Параллельный выход (PIPO)

В этом режиме 4-битный двоичный вход B 0 , B 1 , B 2 , B 3 подается на входы данных D 0 , D 1 , D 2 , D 3 соответственно четырех триггеров. Как только будет применен отрицательный фронт тактовой частоты, входные двоичные биты будут загружены в триггеры одновременно. Загруженные биты появятся одновременно на выходной стороне. Только тактовый импульс необходим для загрузки всех битов.

Блок-схема

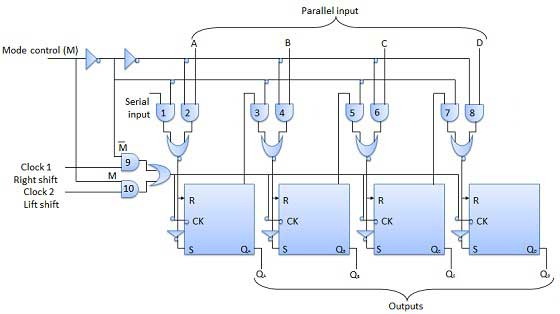

Двунаправленный регистр сдвига

Если двоичное число сдвигается влево на одну позицию, то это эквивалентно умножению исходного числа на 2. Аналогично, если двоичное число сдвигается вправо на одну позицию, это эквивалентно делению исходного числа на 2.

Следовательно, если мы хотим использовать регистр сдвига для умножения и деления заданного двоичного числа, тогда мы должны иметь возможность перемещать данные влево или вправо.

Такой регистр называется двунаправленным регистром. Четырехбитный двунаправленный регистр сдвига показан на рис.

Имеются два последовательных входа, а именно последовательный вход DR данных сдвига вправо и последовательный вход DL данных сдвига влево вместе с входом выбора режима (M).

Блок-схема

Операция

| SN | Состояние | Операция |

|---|---|---|

| 1 | With M = 1 − Shift right operation | Если M = 1, то логические элементы И 1, 3, 5 и 7 включены, тогда как остальные элементы И 2, 4, 6 и 8 будут отключены. Данные в D R сдвигаются вправо побитно от FF-3 до FF-0 при применении тактовых импульсов. Таким образом, при M = 1 мы получаем последовательную операцию сдвига вправо. |

| 2 | With M = 0 − Shift left operation | Когда элемент управления режимом M подключен к 0, тогда логические элементы И 2, 4, 6 и 8 включены, а 1, 3, 5 и 7 отключены. Данные в D L сдвигаются влево побитно от FF-0 до FF-3 при применении тактовых импульсов. Таким образом, при M = 0 мы получаем последовательную операцию сдвига вправо. |

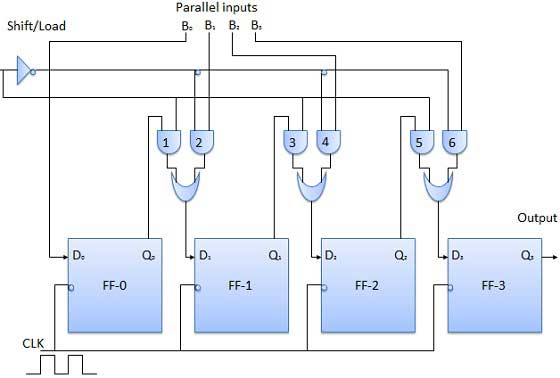

Универсальный регистр сдвига

Регистр сдвига, который может сдвигать данные только в одном направлении, называется регистром однонаправленного сдвига. Регистр сдвига, который может сдвигать данные в обоих направлениях, называется двунаправленным регистром сдвига. Используя ту же логику, регистр сдвига, который может сдвигать данные в обоих направлениях, а также загружать их параллельно, известен как универсальный регистр сдвига. Сдвиговый регистр может выполнять следующую операцию -

- Параллельная загрузка

- Левый сдвиг

- Правое переключение

Вход управления режимом подключен к логической 1 для параллельной операции загрузки, тогда как он подключен к 0 для последовательного переключения. Когда вывод управления режимом подключен к земле, универсальный сдвиговый регистр действует как двунаправленный регистр. Для последовательной левой операции вход применяется к последовательному входу, который идет к логическому элементу И-1, показанному на рисунке. В то время как для операции сдвига вправо последовательный вход применяется ко входу D.

Блок-схема

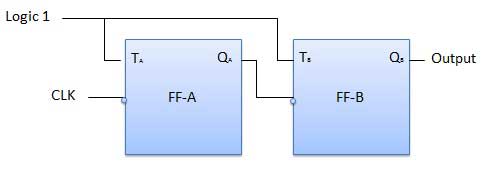

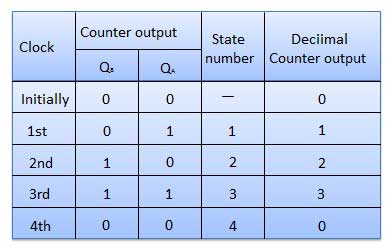

Счетчик - это последовательный контур. Цифровая схема, которая используется для подсчета импульсов, известна как счетчик. Счетчик - это самое широкое применение шлепанцев. Это группа триггеров с тактовым сигналом. Счетчики бывают двух типов.

- Асинхронные счетчики или счетчики пульсаций.

- Синхронные счетчики.

Асинхронные счетчики или счетчики пульсаций

Логическая схема 2-битного счетчика пульсаций показана на рисунке. Используется тумблер (T) триггер. Но мы можем использовать триггер JK также с J и K, постоянно подключенными к логике 1. Внешние часы применяются к тактовому входу триггера A, а выход Q A применяется к тактовому входу следующего триггера, т.е. FF-B.

Логическая диаграмма

Операция

| SN | Состояние | Операция |

|---|---|---|

| 1 | Initially let both the FFs be in the reset state | Q B Q A = 00 изначально |

| 2 | After 1st negative clock edge | Как только будет применен первый отрицательный фронт тактовой частоты, FF-A переключится, и Q A будет равно 1. Q A подключен к тактовому входу FF-B. Поскольку Q A изменился с 0 на 1, он обрабатывается FF-B как положительный фронт тактовой частоты. В Q B нет изменений, потому что FF-B является FF, запускаемым отрицательным фронтом. Q B Q A = 01 после первого тактового импульса. |

| 3 | After 2nd negative clock edge | По прибытии второго отрицательного фронта тактового сигнала FF-A снова переключается и Q A = 0. Изменение Q A действует как отрицательный фронт тактовой частоты для FF-B. Таким образом, он также будет переключаться, и Q B будет 1. Q B Q A = 10 после второго тактового импульса. |

| 4 | After 3rd negative clock edge | По прибытии 3-го отрицательного фронта тактового сигнала FF-A снова переключается, и Q A становится 1 из 0. Поскольку это положительное изменение, FF-B не реагирует на него и остается неактивным. Таким образом, Q B не меняется и продолжает оставаться равным 1. Q B Q A = 11 после третьего тактового импульса. |

| 5 | After 4th negative clock edge | По достижении 4-го отрицательного фронта тактового сигнала FF-A снова переключается, и Q A становится 1 из 0. Это отрицательное изменение Q A действует как тактовый импульс для FF-B. Следовательно, он переключает Q B с 1 на 0. Q B Q A = 00 после четвертого тактового импульса. |

Таблица правды

Синхронные счетчики

Если «тактовые» импульсы подаются на все триггеры счетчика одновременно, то такой счетчик называется синхронным счетчиком.

2-битный синхронный восходящий счетчик

Входы J A и K A FF-A связаны с логикой 1. Таким образом, FF-A будет работать как триггер. В J B и K B входы подключены к Q A .

Логическая диаграмма

Операция

| SN | Состояние | Операция |

|---|---|---|

| 1 | Initially let both the FFs be in the reset state | Q B Q A = 00 изначально. |

| 2 | After 1st negative clock edge | Как только будет применен первый отрицательный фронт тактовой частоты, FF-A переключится, а Q A изменится с 0 на 1. Но в момент применения отрицательного фронта тактовой частоты Q A , J B = K B = 0. Следовательно, FF-B не изменит свое состояние. Таким образом, Q B останется 0. Q B Q A = 01 после первого тактового импульса. |

| 3 | After 2nd negative clock edge | По прибытии второго отрицательного фронта тактового сигнала FF-A снова переключается, и Q A изменяется с 1 на 0. Но в этот момент Q A было 1. Итак, J B = K B = 1, и FF-B будет переключаться. Следовательно, Q B изменяется с 0 на 1. Q B Q A = 10 после второго тактового импульса. |

| 4 | After 3rd negative clock edge | При применении третьего спадающего фронта тактового сигнала FF-A переключится с 0 на 1, но состояние FF-B не изменится. Q B Q A = 11 после третьего тактового импульса. |

| 5 | After 4th negative clock edge | При применении следующего тактового импульса Q A изменится с 1 на 0, так как Q B также изменится с 1 на 0. Q B Q A = 00 после четвертого тактового импульса. |

Классификация счетчиков

В зависимости от того, как идет подсчет, синхронные или асинхронные счетчики классифицируются следующим образом:

- Вверх счетчики

- Счетчики

- Счетчики вверх / вниз

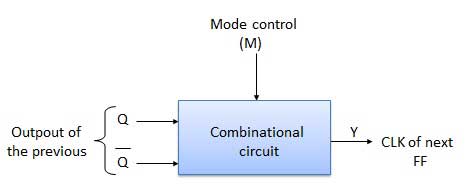

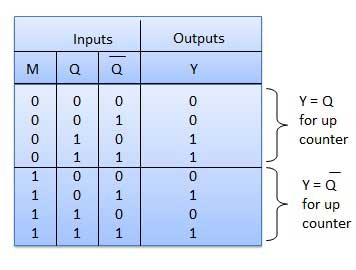

Счетчик ВВЕРХ / ВНИЗ

Повышающий и обратный счетчики объединяются вместе, чтобы получить счетчик ВВЕРХ / ВНИЗ. Также предусмотрен вход управления режимом (M) для выбора режима вверх или вниз. Комбинационная схема должна быть спроектирована и использована между каждой парой триггеров для достижения операции увеличения / уменьшения.

- Тип счетчиков вверх / вниз

- Счетчики пульсаций UP / DOWN

- Синхронный счетчик ВВЕРХ / ВНИЗ

Счетчики пульсаций UP / DOWN

В счетчике пульсаций UP / DOWN все FF работают в режиме переключения. Таким образом, следует использовать либо T-образные, либо JK-шлепанцы. Триггер LSB принимает часы напрямую. Но тактовая частота для каждого другого FF получается из (Q = Q bar) выходных данных предыдущего FF.

UP counting mode (M=0)- Выход Q предыдущего FF соединен с часами следующего каскада, если должен быть достигнут обратный счет. Для этого режима вход выбора режима M находится на логическом 0 (M = 0).

DOWN counting mode (M=1)- Если M = 1, то выход Q-бара предыдущего FF подключается к следующему FF. Это приведет к работе счетчика в режиме счета.

пример

3-битный двоичный счетчик пульсаций вверх / вниз.

3-битный - следовательно, требуются три FF.

ВВЕРХ / ВНИЗ - Значит, необходим вход управления режимом.

Для счетчика пульсаций выход Q предыдущего FF подключен к тактовому входу следующего.

Для счетчика пульсаций выход Q предыдущего FF подключен к тактовому входу следующего.

Для счетчика с уменьшением пульсаций выход Q-линейки предыдущего FF соединяется с тактовым входом следующего.

Пусть выбор выходных полос Q и Q предыдущего FF контролируется входом управления режимом M так, что, если M = 0, подсчет ВВЕРХ. Итак, подключите Q к CLK. Если M = 1, отсчет ВНИЗ. Итак, подключите панель Q к CLK.

Блок-схема

Таблица правды

Операция

| SN | Состояние | Операция |

|---|---|---|

| 1 | Case 1 − With M = 0 (Up counting mode) | Если M = 0 и M bar = 1, то логические элементы И 1 и 3 на рис. будет включен, тогда как логические элементы И 2 и 4 будут отключены. Следовательно, Q A подключается к тактовому входу FF-B, а Q B подключается к тактовому входу FF-C. Эти подключения такие же, как и для обычного счетчика вверх. Таким образом, при M = 0 схема работает как счетчик. |

| 2 | Case 2: With M = 1 (Down counting mode) | Если M = 1, то элементы AND 2 и 4 на рис. включены, тогда как элементы И 1 и 3 отключены. Следовательно, полоса Q A подключается к тактовому входу FF-B, а полоса Q B подключается к тактовому входу FF-C. Эти соединения будут производить обратный счетчик. Таким образом, при M = 1 схема работает как обратный счетчик. |

Счетчик модуля (счетчик MOD-N)

2-битный счетчик пульсаций называется счетчиком MOD-4, а 3-битный счетчик пульсаций называется счетчиком MOD-8. В общем, n-битный счетчик пульсаций называется счетчиком по модулю N. Где, номер MOD = 2 n .

Тип модуля

- 2 бита вверх или вниз (MOD-4)

- 3 бита вверх или вниз (MOD-8)

- 4 бита вверх или вниз (MOD-16)

Применение счетчиков

- Частотомеры

- Цифровые часы

- Измерение времени

- АЦП преобразователь

- Схемы делителя частоты

- Цифровой генератор треугольных волн.

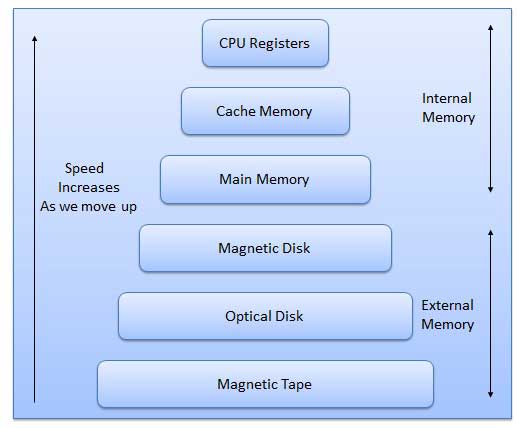

Память похожа на человеческий мозг. Он используется для хранения данных и инструкций. Компьютерная память - это место для хранения данных в компьютере, где данные должны обрабатываться и хранятся инструкции, необходимые для обработки.

Память разделена на большое количество мелких частей. Каждая часть называется ячейкой. Каждое место или ячейка имеет уникальный адрес, который варьируется от нуля до размера памяти минус один.

Например, если в компьютере 64k слов, то этот блок памяти имеет 64 * 1024 = 65536 ячеек памяти. Адрес этих мест варьируется от 0 до 65535.

Память в основном бывает двух типов

Internal Memory - кэш-память и первичная / основная память

External Memory - магнитный диск / оптический диск и т. Д.

Характеристики Иерархии Памяти следуют, когда мы идем сверху вниз.

- Емкость с точки зрения хранения увеличивается.

- Стоимость одного бита хранилища уменьшается.

- Частота доступа ЦП к памяти снижается.

- Время доступа ЦП увеличивается.

баран

RAM представляет собой внутреннюю память CPU для хранения данных, программы и результатов программы. Это память для чтения / записи. Это называется оперативной памятью (RAM).

Поскольку время доступа в ОЗУ не зависит от адреса слова, то есть до каждого места хранения внутри памяти так же легко добраться, как и до другого места, и требуется такое же количество времени. Мы можем обращаться к памяти случайным образом и очень быстро, но это также может быть довольно дорогостоящим.

ОЗУ является энергозависимым, т.е. данные, хранящиеся в нем, теряются при выключении компьютера или при сбое питания. Следовательно, с компьютерами часто используется резервная система бесперебойного питания (ИБП). ОЗУ имеет небольшой размер как с точки зрения физического размера, так и с точки зрения объема данных, которые он может хранить.

RAM бывает двух типов

- Статическая RAM (SRAM)

- Динамическое ОЗУ (DRAM)

Статическая RAM (SRAM)

Слово staticуказывает, что память сохраняет свое содержимое, пока остается поданным питание. Однако данные теряются при отключении питания из-за нестабильности. В микросхемах SRAM используется матрица из 6 транзисторов без конденсаторов. Транзисторам не требуется питание для предотвращения утечки, поэтому SRAM не нужно регулярно обновлять.

Из-за дополнительного места в матрице SRAM использует больше микросхем, чем DRAM, для того же объема памяти, что увеличивает производственные затраты.

Используется статическая оперативная память, поскольку кеш-память должна быть очень быстрой и небольшой.

Динамическое ОЗУ (DRAM)

DRAM, в отличие от SRAM, необходимо постоянно refreshedдля того, чтобы поддерживать данные. Это делается путем помещения памяти в схему обновления, которая перезаписывает данные несколько сотен раз в секунду. DRAM используется для большинства системной памяти, потому что она дешевая и маленькая. Все DRAM состоят из ячеек памяти. Эти ячейки состоят из одного конденсатора и одного транзистора.

ПЗУ

ROM означает постоянное запоминающее устройство. Память, из которой мы можем только читать, но не можем писать. Этот тип памяти энергонезависимый. Информация постоянно сохраняется в такой памяти во время производства.

В ПЗУ хранятся инструкции, необходимые для запуска компьютера при первом включении электричества. Эта операция называется начальной загрузкой. Чип ПЗУ используется не только в компьютере, но и в других электронных устройствах, таких как стиральная машина и микроволновая печь.

Ниже приведены различные типы ПЗУ -

MROM (маскированное ПЗУ)

Самые первые ПЗУ были жестко зашитыми устройствами, которые содержали заранее запрограммированный набор данных или инструкций. Такие ПЗУ известны как ПЗУ с масками. Стоит недорого ПЗУ.

PROM (программируемая постоянная память)

PROM - это постоянная память, которая может быть изменена пользователем только один раз. Пользователь покупает пустой PROM и вводит желаемое содержимое с помощью программатора PROM. Внутри микросхемы PROM есть небольшие предохранители, которые сгорают во время программирования. Его можно запрограммировать только один раз, и его нельзя стереть.

EPROM (стираемая и программируемая постоянная память)

EPROM можно стереть, подвергнув его воздействию ультрафиолетового света в течение до 40 минут. Обычно эту функцию выполняет ластик СППЗУ. Во время программирования электрический заряд задерживается в изолированной области затвора. Заряд сохраняется более десяти лет, поскольку в заряде нет пути утечки. Для стирания этого заряда ультрафиолетовый свет пропускается через кварцевое окно (крышку). Воздействие ультрафиолетового света рассеивает заряд. При нормальном использовании кварцевая крышка закрывается наклейкой.

EEPROM (электрически стираемая и программируемая постоянная память)

EEPROM программируется и стирается электрически. Его можно стереть и перепрограммировать около десяти тысяч раз. И стирание, и программирование занимают от 4 до 10 мс (миллисекунды). В EEPROM любое место можно выборочно стереть и запрограммировать. EEPROM можно стирать по одному байту, вместо того, чтобы стирать весь чип. Следовательно, процесс перепрограммирования гибкий, но медленный.

Память с последовательным доступом

Последовательный доступ означает, что система должна искать устройство хранения с начала адреса памяти, пока не найдет требуемый фрагмент данных. Устройство памяти, которое поддерживает такой доступ, называется памятью с последовательным доступом или памятью с последовательным доступом. Магнитная лента является примером памяти с последовательным доступом.

Память прямого доступа

Память с прямым доступом или память с произвольным доступом относится к условиям, при которых система может напрямую обращаться к информации, которую хочет пользователь. Устройство памяти, которое поддерживает такой доступ, называется памятью прямого доступа. Магнитные диски, оптические диски являются примерами памяти прямого доступа.

Кэш-память

Кэш-память - это высокоскоростная полупроводниковая память, которая может увеличить скорость процессора. Он действует как буфер между ЦП и основной памятью. Он используется для хранения тех частей данных и программы, которые наиболее часто используются ЦП. Части данных и программ передаются с диска в кэш-память операционной системой, откуда ЦП может получить к ним доступ.

Преимущества

- Кэш-память работает быстрее, чем основная память.

- Он потребляет меньше времени доступа по сравнению с основной памятью.

- В нем хранится программа, которую можно выполнить за короткий промежуток времени.

- В нем хранятся данные для временного использования.

Недостатки

- Объем кэш-памяти ограничен.

- Это очень дорого.

Виртуальная память - это метод, позволяющий выполнять процессы, которые не полностью доступны в памяти. Основное видимое преимущество этой схемы состоит в том, что программы могут быть больше, чем физическая память. Виртуальная память - это отделение логической памяти пользователя от физической памяти.

Это разделение позволяет предоставить программистам очень большую виртуальную память, когда доступна только меньшая физическая память. Ниже приведены ситуации, когда не требуется полностью загружать всю программу в основную память.

Написанные пользователем подпрограммы обработки ошибок используются только в случае возникновения ошибки в данных или вычислениях.

Некоторые опции и функции программы могут использоваться редко.

Многим таблицам назначается фиксированный объем адресного пространства, даже если фактически используется лишь небольшой объем таблицы.

Возможность выполнять программу, которая находится в памяти лишь частично, противоречит многим преимуществам.

Для загрузки или перестановки каждой пользовательской программы в память потребуется меньшее количество операций ввода-вывода.

Программа больше не будет ограничена объемом доступной физической памяти.

Каждая пользовательская программа может занимать меньше физической памяти, больше программ может быть запущено за одно и то же время с соответствующим увеличением использования ЦП и пропускной способности.

Вспомогательная память

Вспомогательная память намного больше по размеру, чем основная память, но работает медленнее. Обычно в нем хранятся системные программы, инструкции и файлы данных. Это также известно как вторичная память. Его также можно использовать как переполнение / виртуальную память в случае превышения объема основной памяти. Процессор не может получить доступ к вторичной памяти напрямую. Сначала данные / информация из вспомогательной памяти передаются в основную память, а затем к этой информации может получить доступ ЦП. Характеристики вспомогательной памяти следующие -

Non-volatile memory - Данные не теряются при отключении питания.

Reusable - Данные остаются во вторичном хранилище на постоянной основе, пока они не будут перезаписаны или удалены пользователем.

Reliable - Данные во вторичном хранилище безопасны благодаря высокой физической стабильности вторичного устройства хранения.

Convenience - С помощью компьютерного программного обеспечения уполномоченные люди могут быстро находить данные и получать к ним доступ.

Capacity - Вторичное хранилище может хранить большие объемы данных в наборах из нескольких дисков.

Cost - Хранить данные на ленте или диске намного дешевле, чем в первичной памяти.

Блок микропроцессора является синонимом центрального процессора, центрального процессора, используемого в традиционном компьютере. Микропроцессор (MPU) действует как устройство или группа устройств, которые выполняют следующие задачи.

- общаться с периферийными устройствами

- обеспечить сигнал синхронизации

- прямой поток данных

- выполнять компьютерные задачи в соответствии с инструкциями в памяти

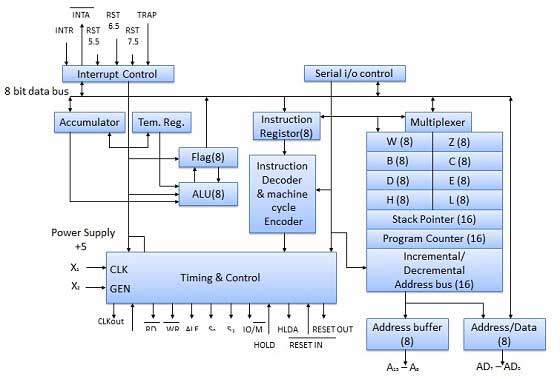

8085 Микропроцессор

Микропроцессор 8085 - это 8-разрядный микропроцессор общего назначения, способный адресовать 64 КБ памяти. Этот процессор имеет сорок контактов, требует одиночного источника питания +5 В и однофазной тактовой частоты 3 МГц.

Блок-схема

ALU

АЛУ выполняет вычислительную функцию микропроцессора. Он включает аккумулятор, временный регистр, арифметическую и логическую схему и пять флагов. Результат сохраняется в аккумуляторе и флагах.

Блок-схема

Аккумулятор

Это 8-битный регистр, который является частью ALU. Этот регистр используется для хранения 8-битных данных и выполнения арифметических и логических операций. Результат операции сохраняется в аккумуляторе.

Диаграмма

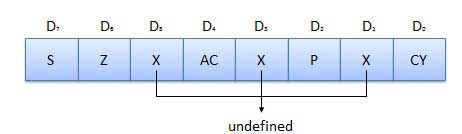

Флаги

Флаги программируемые. Их можно использовать для хранения и передачи данных из регистров с помощью инструкций. ALU включает пять триггеров, которые устанавливаются и сбрасываются в соответствии с состоянием данных в аккумуляторе и других регистрах.

S (Sign) flag- После выполнения арифметической операции, если бит D 7 результата равен 1, устанавливается флаг знака. Используется для числа со знаком. В данном байте, если D 7 равно 1, означает отрицательное число. Если он равен нулю, значит, это положительное число.

Z (Zero) flag - Нулевой флаг устанавливается, если результат операции ALU равен 0.

AC (Auxiliary Carry) flag- В арифметических операциях, когда перенос генерируется цифрой D3 и передается на цифру D 4 , устанавливается флаг AC. Этот флаг используется только для внутренней операции BCD.

P (Parity) flag- После арифметической или логической операции, если результат имеет четное число единиц, флаг устанавливается. Если он имеет нечетное количество единиц, флаг сбрасывается.

C (Carry) flag - Если результатом арифметической операции является перенос, флаг переноса устанавливается, в противном случае он сбрасывается.

Раздел регистрации

По сути, это запоминающее устройство, которое передает данные из регистров с помощью инструкций.

Stack Pointer (SP)- Указатель стека также является 16-битным регистром, который используется как указатель памяти. Он указывает на область памяти в памяти чтения / записи, известную как стек. В промежутках между выполнением программы данные иногда хранятся в стеке. Начало стека определяется загрузкой 16-битного адреса в указатель стека.

Program Counter (PC) − This 16-bit register deals with fourth operation to sequence the execution of instruction. This register is also a memory pointer. Memory location have 16-bit address. It is used to store the execution address. The function of the program counter is to point to memory address from which next byte is to be fetched.

Storage registers − These registers store 8-bit data during a program execution. These registers are identified as B, C, D, E, H, L. They can be combined as register pair BC, DE and HL to perform some 16 bit operations.

Time and Control Section

This unit is responsible to synchronize Microprocessor operation as per the clock pulse and to generate the control signals which are necessary for smooth communication between Microprocessor and peripherals devices. The RD bar and WR bar signals are synchronous pulses which indicates whether data is available on the data bus or not. The control unit is responsible to control the flow of data between microprocessor, memory and peripheral devices.

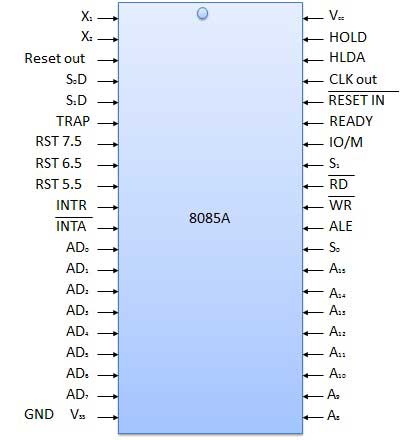

PIN diagram

All the signal can be classified into six groups

| S.N. | Group | Description |

|---|---|---|

| 1 | Address bus | The 8085 microprocessor has 8 signal line, A15 - A8 which are uni directional and used as a high order address bus. |

| 2 | Data bus | The signal line AD7 - AD0 are bi-directional for dual purpose. They are used as low order address bus as well as data bus. |

| 3 | Control signal and Status signal | Control Signal RD bar − It is a read control signal (active low). If it is active then memory read the data. WR bar − It is write control signal (active low). It is active when written into selected memory. Status signal ALU (Address Latch Enable) − When ALU is high. 8085 microprocessor use address bus. When ALU is low. 8085 microprocessor is use data bus. IO/M bar − This is a status signal used to differentiate between i/o and memory operations. When it is high, it indicate an i/o operation and when it is low, it indicate memory operation. S1 and S0 − These status signals, similar to i/o and memory bar, can identify various operations, but they are rarely used in small system. |

| 4 | Power supply and frequency signal | Vcc − +5v power supply. Vss − ground reference. X, X − A crystal is connected at these two pins. The frequency is internally divided by two operate system at 3-MHz, the crystal should have a frequency of 6-MHz. CLK out − This signal can be used as the system clock for other devices. |

| 5 | Externally initiated signal | INTR (i/p) − Interrupt request. INTA bar (o/p) − It is used as acknowledge interrupt. TRAP (i/p) − This is non maskable interrupt and has highest priority. HOLD (i/p) − It is used to hold the executing program. HLDA (o/p) − Hold acknowledge. READY (i/p) − This signal is used to delay the microprocessor read or write cycle until a slow responding peripheral is ready to accept or send data. RESET IN bar − When the signal on this pin goes low, the program counter is set to zero, the bus are tri-stated, & MPU is reset. RESET OUT − This signal indicate that MPU is being reset. The signal can be used to reset other devices. RST 7.5, RST 6.5, RST 5.5 (Request interrupt) − It is used to transfer the program control to specific memory location. They have higher priority than INTR interrupt. |

| 6 | Serial I/O ports | The 8085 microprocessor has two signals to implement the serial transmission serial input data and serial output data. |

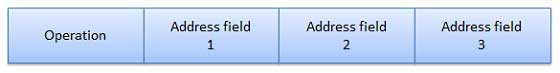

Instruction Format

Each instruction is represented by a sequence of bits within the computer. The instruction is divided into group of bits called field. The way instruction is expressed is known as instruction format. It is usually represented in the form of rectangular box. The instruction format may be of the following types.

Variable Instruction Formats

These are the instruction formats in which the instruction length varies on the basis of opcode & address specifiers. For Example, VAX instruction vary between 1 and 53 bytes while X86 instruction vary between 1 and 17 bytes.

Format

Advantage

These formats have good code density.

Drawback

These instruction formats are very difficult to decode and pipeline.

Fixed Instruction Formats

In this type of instruction format, all instructions are of same size. For Example, MIPS, Power PC, Alpha, ARM.

Format

Advantage

They are easy to decode & pipeline.

Drawback

They don't have good code density.

Hybrid Instruction Formats

In this type of instruction formats, we have multiple format length specified by opcode. For example, IBM 360/70, MIPS 16, Thumb.

Format

Advantage

These compromise between code density & instruction of these type are very easy to decode.

Addressing Modes

Addressing mode provides different ways for accessing an address to given data to a processor. Operated data is stored in the memory location, each instruction required certain data on which it has to operate. There are various techniques to specify address of data. These techniques are called Addressing Modes.

Direct addressing mode − In the direct addressing mode, address of the operand is given in the instruction and data is available in the memory location which is provided in instruction. We will move this data in desired location.

Indirect addressing mode − In the indirect addressing mode, the instruction specifies a register which contain the address of the operand. Both internal RAM and external RAM can be accessed via indirect addressing mode.

Immediate addressing mode − In the immediate addressing mode, direct data is given in the operand which move the data in accumulator. It is very fast.

Relative addressing mode − In the relative address mode, the effective address is determined by the index mode by using the program counter in stead of general purpose processor register. This mode is called relative address mode.

Index addressing mode − In the index address mode, the effective address of the operand is generated by adding a content value to the contents of the register. This mode is called index address mode.