Цифровые регистры

Триггер - это 1-битная ячейка памяти, которая может использоваться для хранения цифровых данных. Чтобы увеличить емкость запоминающего устройства с точки зрения количества битов, мы должны использовать группу триггеров. Такая группа триггеров известна какRegister. Вn-bit register будет состоять из n количество триггеров, и он способен хранить n-bit слово.

Двоичные данные в регистре можно перемещать внутри регистра с одного триггера на другой. Регистры, которые позволяют такую передачу данных, называютсяshift registers. Есть четыре режима работы сдвигового регистра.

- Последовательный вход Последовательный выход

- Последовательный вход Параллельный выход

- Параллельный вход Последовательный выход

- Параллельный вход Параллельный выход

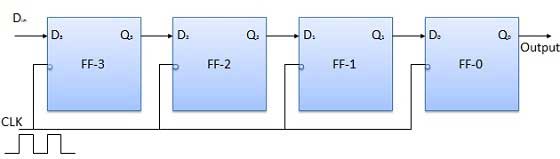

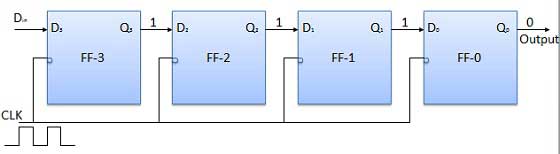

Последовательный вход Последовательный выход

Пусть все триггеры изначально находятся в состоянии сброса, т.е. Q 3 = Q 2 = Q 1 = Q 0 = 0. Если в регистр вносится запись четырехбитного двоичного числа 1 1 1 1, это число должно быть применительно кDinбит с первым примененным битом LSB. Вход D FF-3, т.е. D 3 подключен к последовательному входу данных.Din. Выход FF-3, т.е. Q 3 , соединен со входом следующего триггера, то есть D 2 и так далее.

Блок-схема

Операция

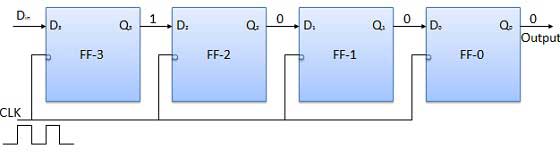

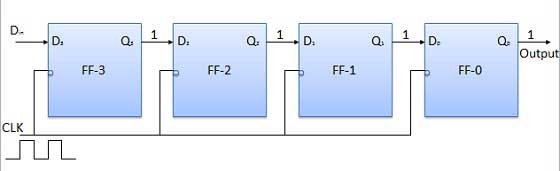

Перед подачей тактового сигнала, пусть Q 3 Q 2 Q 1 Q 0 = 0000 и примените бит LSB числа, которое нужно ввести, к D in . Итак, D in = D 3 = 1. Примените часы. На первом заднем фронте тактового сигнала устанавливается FF-3, и сохраненное слово в регистре - Q 3 Q 2 Q 1 Q 0 = 1000.

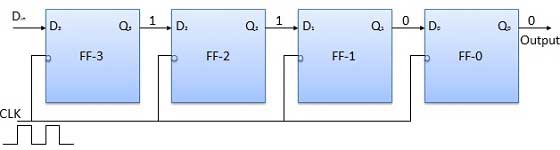

Примените следующий бит к D в . Итак, D in = 1. Как только наступит следующий отрицательный фронт тактового сигнала, FF-2 установится, и сохраненное слово изменится на Q 3 Q 2 Q 1 Q 0 = 1100.

Примените следующий бит, который нужно сохранить, то есть от 1 до D in . Подайте тактовый импульс. Как только наступит третий отрицательный фронт тактовой частоты, будет установлен FF-1, и выходной сигнал будет изменен на Q 3 Q 2 Q 1 Q 0 = 1110.

Аналогично с D in = 1 и приходом четвертого отрицательного фронта тактового сигнала, сохраненное слово в регистре будет Q 3 Q 2 Q 1 Q 0 = 1111.

Таблица правды

Формы волны

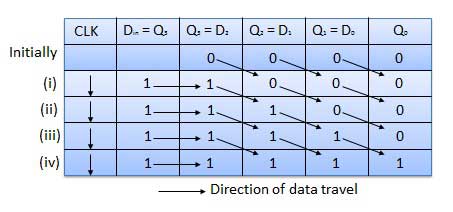

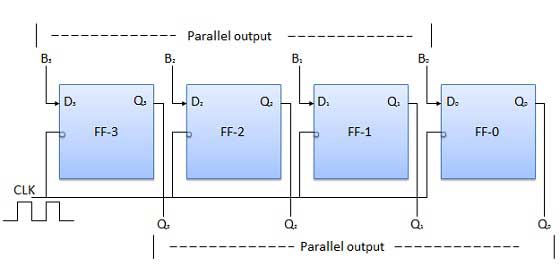

Последовательный вход Параллельный выход

В таких типах операций данные вводятся последовательно и выводятся параллельно.

Данные загружаются бит за битом. Выходы отключены, пока данные загружаются.

Как только загрузка данных завершается, все триггеры содержат свои требуемые данные, выходы активируются, так что все загруженные данные становятся доступными по всем линиям вывода одновременно.

Для загрузки четырехбитового слова требуется 4 тактовых цикла. Следовательно, скорость работы режима SIPO такая же, как и у режима SISO.

Блок-схема

Параллельный вход и последовательный выход (PISO)

Биты данных вводятся параллельно.

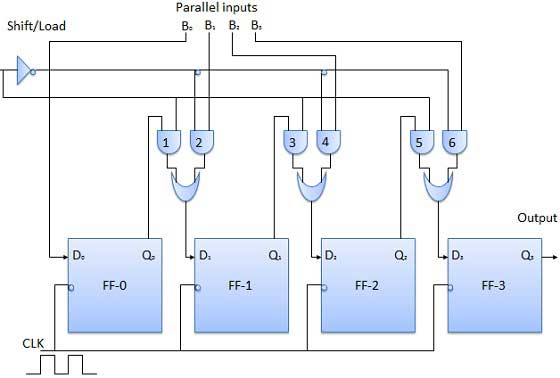

Схема, показанная ниже, представляет собой четырехразрядный регистр последовательного вывода с параллельным входом.

Выход предыдущего триггера соединен с входом следующего через комбинационную схему.

Бинарное входное слово B 0 , B 1 , B 2 , B 3 подается через ту же комбинационную схему.

Есть два режима, в которых может работать эта схема, а именно - режим смены или режим нагрузки.

Режим загрузки

Когда линия шкалы сдвига / нагрузки имеет низкий уровень (0), логические элементы И 2, 4 и 6 становятся активными, они передают биты B 1 , B 2 , B 3 в соответствующие триггеры. На нижнем фронте тактового сигнала двоичный вход B 0 , B 1 , B 2 , B 3 будет загружен в соответствующие триггеры. Таким образом происходит параллельная загрузка.

Режим переключения

Когда линия шкалы сдвига / нагрузки низкая (1), логические элементы И 2, 4 и 6 становятся неактивными. Следовательно, параллельная загрузка данных становится невозможной. Но элементы И 1,3 и 5 становятся активными. Следовательно, сдвиг данных слева направо бит за битом при применении тактовых импульсов. Таким образом, имеет место параллельная последовательная операция вывода.

Блок-схема

Параллельный вход Параллельный выход (PIPO)

В этом режиме 4-битный двоичный вход B 0 , B 1 , B 2 , B 3 подается на входы данных D 0 , D 1 , D 2 , D 3 соответственно четырех триггеров. Как только будет применен отрицательный фронт тактовой частоты, входные двоичные биты будут загружены в триггеры одновременно. Загруженные биты появятся одновременно на выходной стороне. Только тактовый импульс необходим для загрузки всех битов.

Блок-схема

Двунаправленный регистр сдвига

Если двоичное число сдвигается влево на одну позицию, то это эквивалентно умножению исходного числа на 2. Аналогично, если двоичное число сдвигается вправо на одну позицию, это эквивалентно делению исходного числа на 2.

Следовательно, если мы хотим использовать регистр сдвига для умножения и деления данного двоичного числа, тогда мы должны иметь возможность перемещать данные влево или вправо.

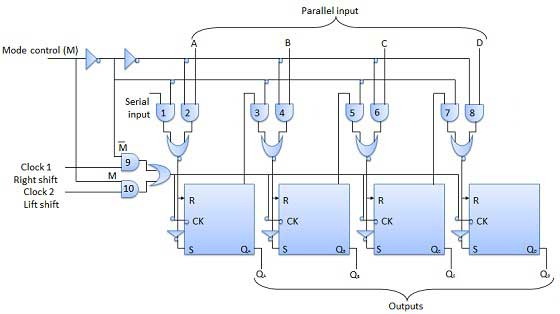

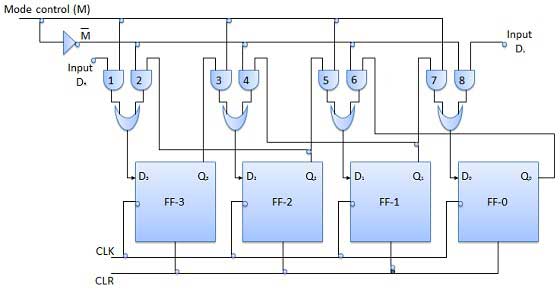

Такой регистр называется двунаправленным регистром. Четырехбитный двунаправленный регистр сдвига показан на рис.

Имеются два последовательных входа, а именно последовательный вход DR данных сдвига вправо и последовательный вход DL данных сдвига влево вместе с входом выбора режима (M).

Блок-схема

Операция

| SN | Состояние | Операция |

|---|---|---|

| 1 | With M = 1 − Shift right operation | Если M = 1, то элементы И 1, 3, 5 и 7 включены, тогда как остальные элементы И 2, 4, 6 и 8 будут отключены. Данные в D R сдвигаются вправо побитно от FF-3 до FF-0 при применении тактовых импульсов. Таким образом, при M = 1 мы получаем последовательную операцию сдвига вправо. |

| 2 | With M = 0 − Shift left operation | Когда элемент управления режимом M подключен к 0, тогда логические элементы И 2, 4, 6 и 8 включены, а 1, 3, 5 и 7 отключены. Данные в D L сдвигаются влево побитно от FF-0 до FF-3 при применении тактовых импульсов. Таким образом, при M = 0 мы получаем последовательную операцию сдвига вправо. |

Универсальный регистр сдвига

Регистр сдвига, который может сдвигать данные только в одном направлении, называется однонаправленным регистром сдвига. Регистр сдвига, который может сдвигать данные в обоих направлениях, называется двунаправленным регистром сдвига. Применяя ту же логику, регистр сдвига, который может сдвигать данные в обоих направлениях, а также загружать их параллельно, известен как универсальный регистр сдвига. Сдвиговый регистр может выполнять следующие операции -

- Параллельная загрузка

- Левый сдвиг

- Правое переключение

Вход управления режимом подключен к логической 1 для параллельной операции загрузки, тогда как он подключен к 0 для последовательного переключения. Когда вывод управления режимом подключен к земле, универсальный сдвиговый регистр действует как двунаправленный регистр. Для последовательной левой операции вход применяется к последовательному входу, который идет к логическому элементу И-1, показанному на рисунке. В то время как для операции сдвига вправо последовательный вход применяется ко входу D.

Блок-схема