Последовательные схемы

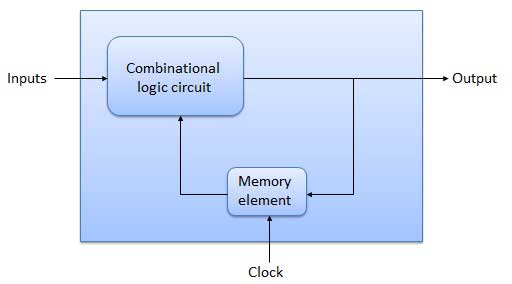

Комбинационная схема не использует память. Следовательно, предыдущее состояние входа не влияет на текущее состояние схемы. Но последовательная схема имеет память, поэтому вывод может варьироваться в зависимости от ввода. Этот тип схем использует предыдущий ввод, вывод, часы и элемент памяти.

Блок-схема

Резкий поворот

Триггер - это последовательная схема, которая обычно выбирает свои входы и изменяет свои выходы только в определенные моменты времени, а не постоянно. Считается, что триггер чувствителен к фронту или срабатывает по фронту, а не по уровню, как защелки.

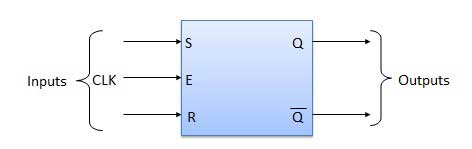

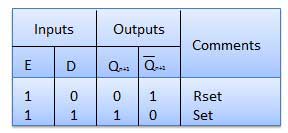

SR Вьетнамки

По сути, это защелка SR с использованием логических элементов NAND с дополнительным enableввод. Его также называют SR-FF с запуском по уровню. Для этого схема на выходе будет иметь место тогда и только тогда, когда разрешающий вход (E) станет активным. Короче говоря, эта схема будет работать как защелка SR, если E = 1, но нет изменений на выходе, если E = 0.

Блок-схема

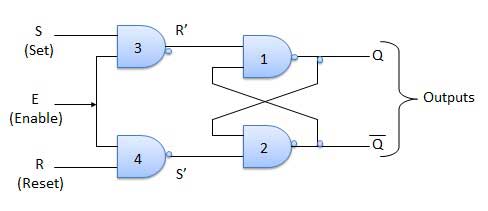

Принципиальная электрическая схема

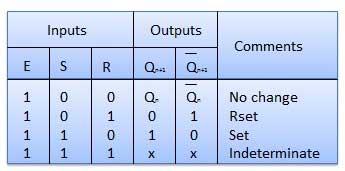

Таблица правды

Операция

| SN | Состояние | Операция |

|---|---|---|

| 1 | S = R = 0 : No change | Если S = R = 0, то выход логических элементов И-НЕ 3 и 4 принудительно принимает значение 1. Следовательно, R 'и S' будут равны 1. Поскольку S 'и R' являются входами базовой защелки SR, использующей вентили NAND, состояние выходов не изменится. |

| 2 | S = 0, R = 1, E = 1 | Поскольку S = 0, выход И-НЕ-3, т.е. R '= 1 и E = 1, выход И-НЕ-4, то есть S' = 0. Следовательно, Q n + 1 = 0 и Q n + 1 полоса = 1. Это условие сброса. |

| 3 | S = 1, R = 0, E = 1 | Выход И-НЕ-3, т.е. R '= 0, и выход И-НЕ-4, т.е. S' = 1. Следовательно, выход защелки SR NAND равен Q n + 1 = 1 и Q n + 1 bar = 0. Это условие сброса. |

| 4 | S = 1, R = 1, E = 1 | Поскольку S = 1, R = 1 и E = 1, оба выхода логических элементов И-НЕ 3 и 4 равны 0, то есть S '= R' = 0. Следовательно Race состояние произойдет в базовой защелке NAND. |

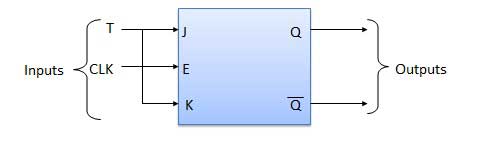

Мастер-раб JK Вьетнамки

Ведущее ведомое устройство JK FF представляет собой каскад из двух SR FF с обратной связью от выхода второго к входу первого. Мастер - это сработавший положительный уровень. Но из-за наличия инвертора в линии синхронизации ведомый ответит на отрицательный уровень. Следовательно, когда часы = 1 (положительный уровень), ведущий активен, а ведомый неактивен. Тогда как, когда clock = 0 (низкий уровень), ведомое устройство активно, а ведущее неактивно.

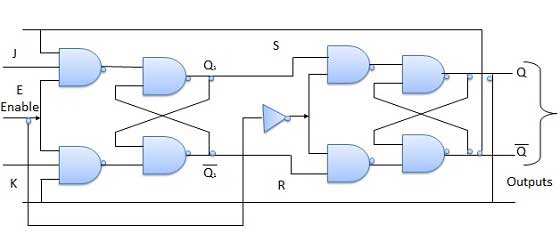

Принципиальная электрическая схема

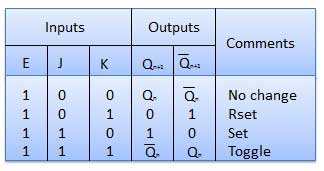

Таблица правды

Операция

| SN | Состояние | Операция |

|---|---|---|

| 1 | J = K = 0 (No change) | Когда clock = 0, ведомое устройство становится активным, а ведущее устройство неактивным. Но поскольку входы S и R не изменились, выходы ведомых также останутся неизменными. Следовательно, выходы не изменятся, если J = K = 0. |

| 2 | J = 0 and K = 1 (Reset) | Clock = 1 - ведущий активен, ведомый неактивен. Следовательно, выходы мастера становятся Q 1 = 0 и Q 1 bar = 1. Это означает, что S = 0 и R = 1. Clock = 0 - ведомый активен, ведущий неактивен. Следовательно, выходы ведомого становятся Q = 0 и Q bar = 1. Снова часы = 1 - ведущий активен, ведомый неактивен. Следовательно, даже с измененными выходами Q = 0 и Q bar = 1, возвращаемыми в мастер, его выход будет Q1 = 0 и Q1 bar = 1. Это означает, что S = 0 и R = 1. Следовательно, когда часы = 0 и ведомое устройство становится активным, выходы ведомого останутся Q = 0 и Q bar = 1. Таким образом, мы получаем стабильный выход от ведущего ведомого. |

| 3 | J = 1 and K = 0 (Set) | Clock = 1 - ведущий активен, ведомый неактивен. Следовательно, выходы мастера становятся Q 1 = 1 и Q 1 bar = 0. Это означает, что S = 1 и R = 0. Clock = 0 - ведомый активен, ведущий неактивен. Следовательно, выходы ведомого становятся Q = 1 и Q bar = 0. Снова clock = 1 - тогда можно показать, что выходы ведомого стабилизированы на Q = 1 и Q bar = 0. |

| 4 | J = K = 1 (Toggle) | Clock = 1 - ведущий активен, ведомый неактивен. Выходы мастера будут переключаться. Таким образом, S и R также будут перевернуты. Clock = 0 - ведомый активен, ведущий неактивен. Выходы ведомого будут переключаться. Эти измененные выходные данные возвращаются на главные входы. Но поскольку clock = 0, мастер по-прежнему неактивен. Таким образом, он не реагирует на эти измененные выходные данные. Это позволяет избежать многократного переключения, которое приводит к гонке вокруг состояния. Триггер ведущего ведомого избегает состояния гонки вокруг. |

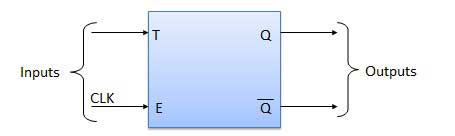

Флип-флоп с задержкой / D-флип-флоп

Delay Flip Flop или D Flip Flop - это простой стробируемый SR-триггер с инвертором NAND, подключенным между входами S и R. У него только один вход. Входные данные появляются на выходе через некоторое время. Из-за этой задержки данных между i / p и o / p это называется триггером задержки. S и R будут дополнять друг друга благодаря инвертору NAND. Следовательно, S = R = 0 или S = R = 1, эти входные условия никогда не появятся. Этой проблемы можно избежать с помощью условий SR = 00 и SR = 1.

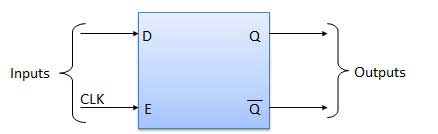

Блок-схема

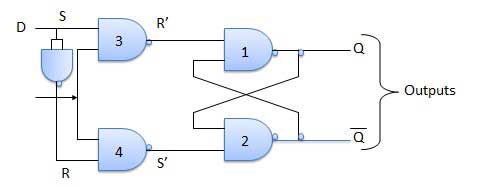

Принципиальная электрическая схема

Таблица правды

Операция

| SN | Состояние | Операция |

|---|---|---|

| 1 | E = 0 | Защелка отключена. Следовательно, никаких изменений в выпуске. |

| 2 | E = 1 and D = 0 | Если E = 1 и D = 0, тогда S = 0 и R = 1. Следовательно, независимо от текущего состояния, следующее состояние будет Q n + 1 = 0 и Q n + 1 bar = 1. Это условие сброса. |

| 3 | E = 1 and D = 1 | Если E = 1 и D = 1, тогда S = 1 и R = 0. Это установит защелку и Q n + 1 = 1 и Q n + 1 bar = 0 независимо от текущего состояния. |

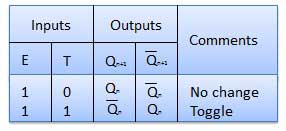

Toggle Flip Flop / T Flip Flop

Перекидной триггер - это, по сути, триггер JK с клеммами J и K, постоянно соединенными вместе. Он имеет только ввод, обозначенныйTкак показано на схеме символов. Символ T-триггера, запускаемого положительным фронтом, показан на блок-схеме.

Диаграмма символов

Блок-схема

Таблица правды

Операция

| SN | Состояние | Операция |

|---|---|---|

| 1 | T = 0, J = K = 0 | Полосы Q и Q на выходе не изменятся |

| 2 | T = 1, J = K = 1 | Выход будет переключаться в соответствии с каждым передним фронтом тактового сигнала. |