การออกแบบ VLSI - ระบบดิจิทัล

การรวมขนาดใหญ่มาก (VLSI) เป็นกระบวนการสร้างไฟล์ integrated circuit (IC) โดยรวมหลายพัน transistorsเป็นชิปตัวเดียว VLSI เริ่มขึ้นในปี 1970 เมื่อมีความซับซ้อนsemiconductor และ communicationมีการพัฒนาเทคโนโลยี microprocessor เป็นอุปกรณ์ VLSI

ก่อนการเปิดตัวเทคโนโลยี VLSI IC ส่วนใหญ่มีชุดฟังก์ชันที่ จำกัด ที่สามารถใช้งานได้ อันelectronic circuit อาจประกอบด้วยไฟล์ CPU, ROM, RAM และอื่น ๆ glue logic. VLSI ช่วยให้นักออกแบบ IC สามารถเพิ่มสิ่งเหล่านี้ทั้งหมดลงในชิปเดียว

อุตสาหกรรมอิเล็กทรอนิกส์มีการเติบโตอย่างก้าวกระโดดในช่วงไม่กี่ทศวรรษที่ผ่านมาส่วนใหญ่เกิดจากความก้าวหน้าอย่างรวดเร็วในเทคโนโลยีการผสานรวมขนาดใหญ่และแอพพลิเคชั่นการออกแบบระบบ ด้วยการถือกำเนิดของการออกแบบการผสานรวมขนาดใหญ่ (VLSI) จำนวนการใช้งานวงจรรวม (ICs) ในการประมวลผลประสิทธิภาพสูงการควบคุมการสื่อสารโทรคมนาคมการประมวลผลภาพและวิดีโอและอุปกรณ์อิเล็กทรอนิกส์สำหรับผู้บริโภคได้เพิ่มขึ้นอย่างรวดเร็ว

เทคโนโลยีล้ำสมัยในปัจจุบันเช่นวิดีโอความละเอียดสูงและอัตราบิตต่ำและการสื่อสารแบบเซลลูลาร์ทำให้ผู้ใช้ปลายทางได้รับแอพพลิเคชั่นพลังการประมวลผลและการพกพาจำนวนมาก แนวโน้มนี้คาดว่าจะเติบโตอย่างรวดเร็วโดยมีผลกระทบที่สำคัญมากในการออกแบบ VLSI และการออกแบบระบบ

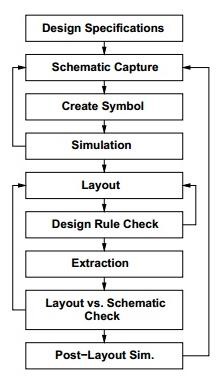

ขั้นตอนการออกแบบ VLSI

ขั้นตอนการออกแบบวงจร VLSI IC แสดงในรูปด้านล่าง ระดับต่างๆของการออกแบบจะถูกกำหนดหมายเลขและบล็อกจะแสดงกระบวนการในขั้นตอนการออกแบบ

ข้อมูลจำเพาะมาก่อนอธิบายในเชิงนามธรรมฟังก์ชันการทำงานส่วนต่อประสานและสถาปัตยกรรมของวงจร IC ดิจิตอลที่จะออกแบบ

จากนั้นคำอธิบายพฤติกรรมจะถูกสร้างขึ้นเพื่อวิเคราะห์การออกแบบในแง่ของฟังก์ชันการทำงานประสิทธิภาพการปฏิบัติตามมาตรฐานที่กำหนดและข้อกำหนดอื่น ๆ

คำอธิบาย RTL ทำได้โดยใช้ HDL คำอธิบาย RTL นี้จำลองขึ้นเพื่อทดสอบการทำงาน จากที่นี่เป็นต้นไปเราต้องการความช่วยเหลือจากเครื่องมือ EDA

จากนั้นคำอธิบาย RTL จะถูกแปลงเป็น netlist ระดับประตูโดยใช้เครื่องมือสังเคราะห์ตรรกะ netlist ระดับประตูคือคำอธิบายของวงจรในแง่ของประตูและการเชื่อมต่อระหว่างพวกเขาซึ่งทำในลักษณะที่ตรงตามข้อกำหนดของเวลากำลังและพื้นที่

ในที่สุดก็มีการจัดทำโครงร่างทางกายภาพซึ่งจะได้รับการตรวจสอบและส่งไปยังการประดิษฐ์

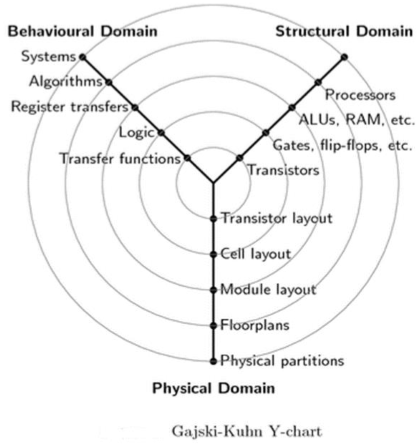

Y แผนภูมิ

กราฟ Gajski-Kuhn Y เป็นแบบจำลองที่รวบรวมข้อควรพิจารณาในการออกแบบอุปกรณ์เซมิคอนดักเตอร์

ทั้งสามโดเมนของแผนภูมิ Gajski-Kuhn Y อยู่บนแกนเรเดียล แต่ละโดเมนสามารถแบ่งออกเป็นระดับของนามธรรมโดยใช้วงแหวนศูนย์กลาง

ที่ระดับบนสุด (วงแหวนรอบนอก) เราจะพิจารณาสถาปัตยกรรมของชิป ที่ระดับล่าง (วงใน) เราปรับแต่งการออกแบบอย่างต่อเนื่องไปสู่การใช้งานที่ละเอียดขึ้น -

การสร้างคำอธิบายเชิงโครงสร้างจากพฤติกรรมนั้นทำได้โดยกระบวนการสังเคราะห์ระดับสูงหรือการสังเคราะห์เชิงตรรกะ

การสร้างคำอธิบายทางกายภาพจากโครงสร้างสามารถทำได้โดยการสังเคราะห์เค้าโครง

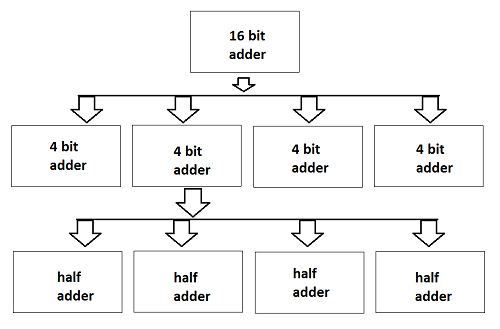

ลำดับชั้นการออกแบบ - โครงสร้าง

ลำดับชั้นของการออกแบบเกี่ยวข้องกับหลักการของ "Divide and Conquer" ไม่มีอะไรนอกจากแบ่งงานออกเป็นงานเล็ก ๆ จนกว่าจะถึงระดับที่ง่ายที่สุด กระบวนการนี้เหมาะสมที่สุดเนื่องจากวิวัฒนาการสุดท้ายของการออกแบบกลายเป็นเรื่องง่ายจนการผลิตง่ายขึ้น

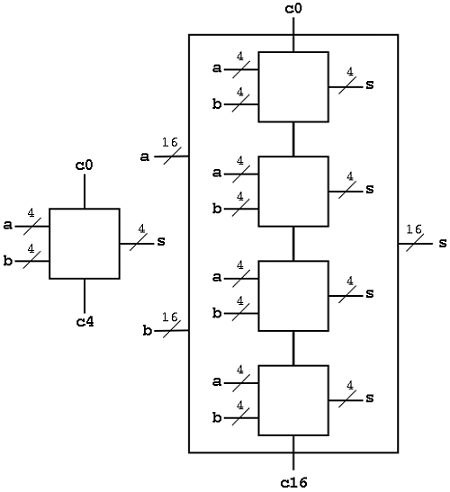

เราสามารถออกแบบงานที่กำหนดให้เป็นโดเมนของกระบวนการออกแบบ (Behavioral, Structural และ Geometrical) เพื่อให้เข้าใจสิ่งนี้เรามาดูตัวอย่างการออกแบบ Adder 16 บิตดังแสดงในรูปด้านล่าง

ที่นี่ชิปทั้งหมดของแอดเดอร์ 16 บิตแบ่งออกเป็นสี่โมดูลของแอดเดอร์ 4 บิต นอกจากนี้การแบ่ง adder 4 บิตเป็น 1-bit adder หรือ half adder การเพิ่ม 1 บิตเป็นกระบวนการออกแบบที่ง่ายที่สุดและวงจรภายในยังง่ายต่อการประดิษฐ์บนชิป ตอนนี้การเชื่อมต่อแอดเดอร์ทั้งสี่ตัวสุดท้ายเราสามารถออกแบบแอดเดอร์ 4 บิตและต่อไปเราสามารถออกแบบแอดเดอร์ 16 บิตได้