การออกแบบ VLSI - บทนำ VHDL

VHDL ย่อมาจากภาษาอธิบายฮาร์ดแวร์วงจรรวมความเร็วสูงมาก เป็นภาษาโปรแกรมที่ใช้ในการสร้างแบบจำลองระบบดิจิทัลโดยกระแสข้อมูลรูปแบบพฤติกรรมและโครงสร้างของการสร้างแบบจำลอง ภาษานี้เปิดตัวครั้งแรกในปี 1981 สำหรับกระทรวงกลาโหม (DoD) ภายใต้โครงการ VHSIC

อธิบายการออกแบบ

ใน VHDL เอนทิตีถูกใช้เพื่ออธิบายโมดูลฮาร์ดแวร์ สามารถอธิบายเอนทิตีได้โดยใช้

- การประกาศเอนทิตี

- Architecture

- Configuration

- การประกาศแพ็กเกจ

- ตัวบรรจุภัณฑ์

มาดูกันว่ามีอะไรบ้าง?

การประกาศเอนทิตี

กำหนดชื่อสัญญาณอินพุตเอาต์พุตและโหมดของโมดูลฮาร์ดแวร์

Syntax -

entity entity_name is

Port declaration;

end entity_name;การประกาศเอนทิตีควรเริ่มต้นด้วย "เอนทิตี" และลงท้ายด้วยคีย์เวิร์ด "end" ทิศทางจะเป็นอินพุตเอาต์พุตหรืออินพุต

| ใน | พอร์ตสามารถอ่านได้ |

| ออก | สามารถเขียนพอร์ตได้ |

| Inout | พอร์ตสามารถอ่านและเขียนได้ |

| กันชน | พอร์ตสามารถอ่านและเขียนได้เพียงแหล่งเดียว |

Architecture -

สถาปัตยกรรมสามารถอธิบายได้โดยใช้รูปแบบโครงสร้างกระแสข้อมูลพฤติกรรมหรือแบบผสม

Syntax -

architecture architecture_name of entity_name

architecture_declarative_part;

begin

Statements;

end architecture_name;ที่นี่เราควรระบุชื่อเอนทิตีที่เรากำลังเขียนเนื้อหาสถาปัตยกรรม คำสั่งสถาปัตยกรรมควรอยู่ในคีย์เวิร์ด "begin" และ "énd" ส่วนประกาศสถาปัตยกรรมอาจมีตัวแปรค่าคงที่หรือการประกาศส่วนประกอบ

การสร้างแบบจำลองกระแสข้อมูล

ในรูปแบบการสร้างแบบจำลองนี้การไหลของข้อมูลผ่านเอนทิตีจะแสดงโดยใช้สัญญาณพร้อมกัน (ขนาน) คำสั่งพร้อมกันใน VHDL คือ WHEN และ GENERATE

นอกจากนี้ยังสามารถใช้การกำหนดโดยใช้ตัวดำเนินการเท่านั้น (AND, NOT, +, *, sll และอื่น ๆ ) เพื่อสร้างโค้ด

สุดท้ายการมอบหมายแบบพิเศษที่เรียกว่า BLOCK สามารถใช้ในรหัสประเภทนี้ได้เช่นกัน

ในรหัสพร้อมกันสามารถใช้สิ่งต่อไปนี้ได้ -

- Operators

- คำสั่ง WHEN (WHEN / ELSE หรือ WITH / SELECT / WHEN);

- สร้างคำสั่ง;

- คำสั่ง BLOCK

การสร้างแบบจำลองพฤติกรรม

ในรูปแบบการสร้างแบบจำลองนี้ลักษณะการทำงานของเอนทิตีเป็นชุดคำสั่งจะดำเนินการตามลำดับตามลำดับที่ระบุ เฉพาะคำสั่งที่อยู่ใน PROCESS, FUNCTION หรือ PROCEDURE เท่านั้นที่เป็นลำดับ

กระบวนการฟังก์ชั่นและกระบวนการเป็นส่วนเดียวของโค้ดที่ดำเนินการตามลำดับ

อย่างไรก็ตามโดยรวมแล้วบล็อกใด ๆ เหล่านี้ยังคงเกิดขึ้นพร้อมกับข้อความอื่น ๆ ที่วางไว้ภายนอก

สิ่งสำคัญอย่างหนึ่งของรหัสพฤติกรรมคือไม่ จำกัด เฉพาะตรรกะแบบลำดับ อันที่จริงด้วยมันเราสามารถสร้างวงจรต่อเนื่องและวงจรรวมได้

ข้อความแสดงพฤติกรรมคือ IF, WAIT, CASE และ LOOP VARIABLES ถูก จำกัด ด้วยและควรใช้ในโค้ดต่อเนื่องเท่านั้น VARIABLE ไม่สามารถเป็น global ได้ดังนั้นจึงไม่สามารถส่งผ่านค่าได้โดยตรง

การสร้างแบบจำลองโครงสร้าง

ในการสร้างแบบจำลองนี้เอนทิตีถูกอธิบายว่าเป็นชุดของส่วนประกอบที่เชื่อมต่อกัน คำสั่งสร้างอินสแตนซ์คอมโพเนนต์เป็นคำสั่งที่เกิดขึ้นพร้อมกัน ดังนั้นลำดับของข้อความเหล่านี้จึงไม่สำคัญ รูปแบบโครงสร้างของการสร้างแบบจำลองอธิบายเฉพาะการเชื่อมต่อโครงข่ายของส่วนประกอบ (ดูเป็นกล่องดำ) โดยไม่ได้หมายความถึงพฤติกรรมใด ๆ ของส่วนประกอบเองหรือของเอนทิตีที่รวมกันเป็นตัวแทน

ในการสร้างแบบจำลองโครงสร้างเนื้อหาของสถาปัตยกรรมประกอบด้วยสองส่วนคือส่วนที่ประกาศ (ก่อนที่คำหลักจะเริ่มต้น) และส่วนของคำสั่ง (หลังจากคำหลักเริ่มต้น)

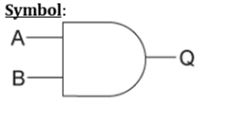

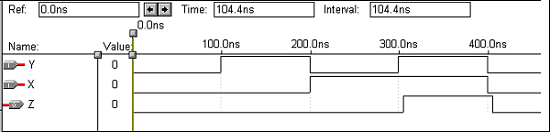

การดำเนินการลอจิก - และประตู

| X | ย | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity and1 is

port(x,y:in bit ; z:out bit);

end and1;

architecture virat of and1 is

begin

z<=x and y;

end virat;รูปคลื่น

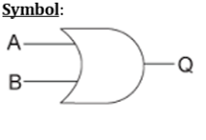

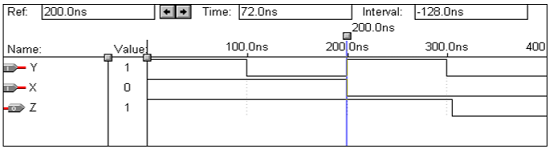

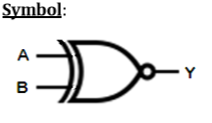

Logic Operation - หรือ Gate

| X | ย | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity or1 is

port(x,y:in bit ; z:out bit);

end or1;

architecture virat of or1 is

begin

z<=x or y;

end virat;รูปคลื่น

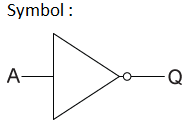

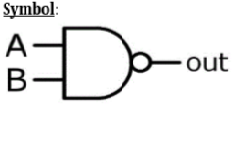

Logic Operation - ไม่ใช่ประตู

| X | ย |

|---|---|

| 0 | 1 |

| 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity not1 is

port(x:in bit ; y:out bit);

end not1;

architecture virat of not1 is

begin

y<=not x;

end virat;รูปคลื่น

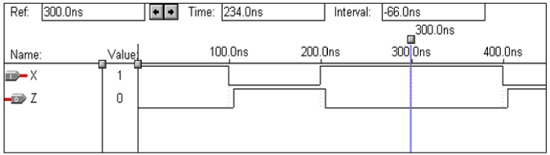

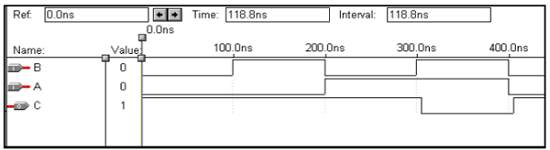

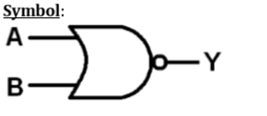

Logic Operation - NAND Gate

| X | ย | z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity nand1 is

port(a,b:in bit ; c:out bit);

end nand1;

architecture virat of nand1 is

begin

c<=a nand b;

end virat;รูปคลื่น

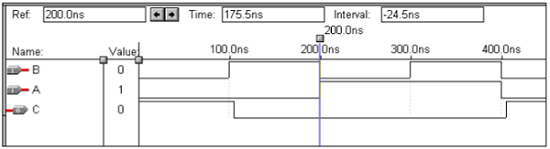

Logic Operation - NOR Gate

| X | ย | z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity nor1 is

port(a,b:in bit ; c:out bit);

end nor1;

architecture virat of nor1 is

begin

c<=a nor b;

end virat;รูปคลื่น

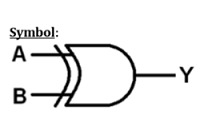

Logic Operation - XOR Gate

| X | ย | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity xor1 is

port(a,b:in bit ; c:out bit);

end xor1;

architecture virat of xor1 is

begin

c<=a xor b;

end virat;รูปคลื่น

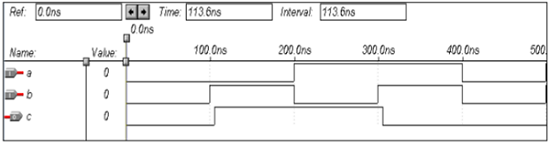

การทำงานลอจิก - ประตู X-NOR

| X | ย | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity xnor1 is

port(a,b:in bit ; c:out bit);

end xnor1;

architecture virat of xnor1 is

begin

c<=not(a xor b);

end virat;รูปคลื่น