การออกแบบ VLSI - อินเวอร์เตอร์ MOS

อินเวอร์เตอร์ถือเป็นหัวใจสำคัญของการออกแบบดิจิทัลทั้งหมด เมื่อเข้าใจการทำงานและคุณสมบัติอย่างชัดเจนแล้วการออกแบบโครงสร้างที่ซับซ้อนมากขึ้นเช่นประตู NAND, แอดเดอร์, ตัวคูณและไมโครโปรเซสเซอร์จะง่ายขึ้นมาก พฤติกรรมทางไฟฟ้าของวงจรที่ซับซ้อนเหล่านี้สามารถหาได้เกือบทั้งหมดโดยการคาดคะเนผลลัพธ์ที่ได้รับสำหรับอินเวอร์เตอร์

การวิเคราะห์อินเวอร์เตอร์สามารถขยายได้เพื่ออธิบายพฤติกรรมของเกตที่ซับซ้อนมากขึ้นเช่น NAND, NOR หรือ XOR ซึ่งจะสร้างบล็อคส่วนประกอบสำหรับโมดูลเช่นตัวคูณและตัวประมวลผล ในบทนี้เรามุ่งเน้นไปที่การเกิดใหม่เพียงครั้งเดียวของประตูอินเวอร์เตอร์คืออินเวอร์เตอร์ CMOS แบบคงที่หรือเรียกสั้น ๆ ว่าอินเวอร์เตอร์ CMOS ซึ่งเป็นที่นิยมมากที่สุดในปัจจุบันดังนั้นจึงสมควรได้รับความสนใจเป็นพิเศษ

หลักการทำงาน

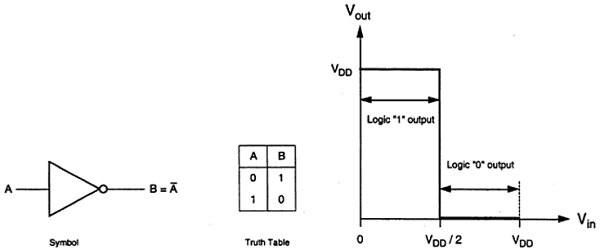

สัญลักษณ์ลอจิกและตารางความจริงของอินเวอร์เตอร์ในอุดมคติแสดงไว้ในรูปด้านล่าง นี่คืออินพุตและ B คือเอาต์พุตแบบกลับหัวที่แสดงโดยแรงดันไฟฟ้าของโหนด การใช้ลอจิกเชิงบวกค่าบูลีนของลอจิก 1 จะแสดงด้วย V ddและตรรกะ 0 แสดงด้วย 0 V thคือแรงดันไฟฟ้าเกณฑ์อินเวอร์เตอร์ซึ่งก็คือ V dd / 2 โดยที่ V ddคือแรงดันเอาต์พุต

เอาท์พุทจะเปลี่ยนจาก 0 ถึง V DDเมื่อป้อนข้อมูลน้อยกว่า V TH ดังนั้นสำหรับ 0 <V ในเอาต์พุต<V thเท่ากับอินพุตลอจิก 0 และ V th <V ใน <V ddเท่ากับอินพุตลอจิก 1 สำหรับอินเวอร์เตอร์

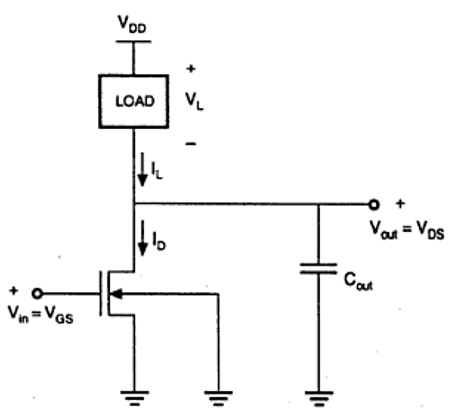

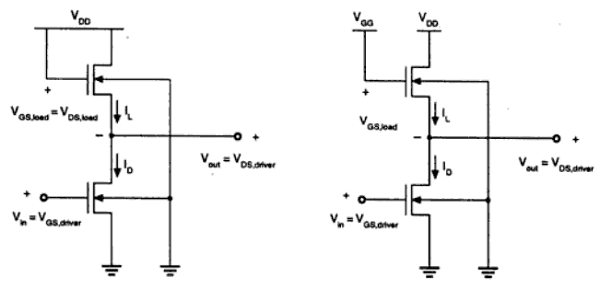

ลักษณะที่แสดงในรูปเหมาะอย่างยิ่ง โครงสร้างวงจรทั่วไปของอินเวอร์เตอร์ nMOS แสดงในรูปด้านล่าง

จากรูปที่กำหนดเราจะเห็นว่าแรงดันไฟฟ้าขาเข้าของอินเวอร์เตอร์เท่ากับแรงดันเกตไปยังต้นทางของทรานซิสเตอร์ nMOS และแรงดันขาออกของอินเวอร์เตอร์เท่ากับการระบายไปยังแรงดันต้นทางของทรานซิสเตอร์ nMOS แหล่งที่มาของแรงดันไฟฟ้าพื้นผิวของ nMOS เรียกอีกอย่างว่าไดรเวอร์สำหรับทรานซิสเตอร์ที่ต่อสายดิน ดังนั้น V SS = 0 โหนดเอาต์พุตเชื่อมต่อกับความจุแบบก้อนที่ใช้สำหรับ VTC

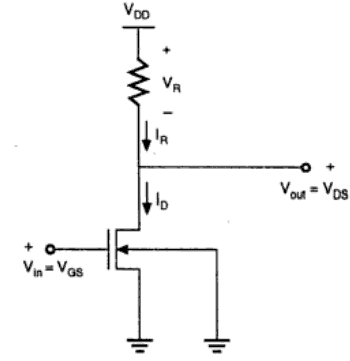

อินเวอร์เตอร์โหลดแบบ Resistive

โครงสร้างพื้นฐานของอินเวอร์เตอร์โหลดตัวต้านทานแสดงในรูปด้านล่าง ที่นี่ประเภทการเพิ่มประสิทธิภาพ nMOS ทำหน้าที่เป็นทรานซิสเตอร์ของไดรเวอร์ โหลดประกอบด้วยง่ายต้านทานเชิงเส้น R L แหล่งจ่ายไฟของวงจรคือ V DDและท่อระบายน้ำในปัจจุบันผมDเท่ากับภาระปัจจุบันฉันR

การทำงานของวงจร

เมื่ออินพุทของทรานซิสเตอร์ไดรเวอร์มีค่าน้อยกว่าแรงดันไฟฟ้า V TH (V ใน <V TH ) ทรานซิสเตอร์ของไดรเวอร์จะอยู่ในพื้นที่ตัดและไม่นำกระแสใด ๆ ดังนั้นแรงดันไฟฟ้าตกคร่อมตัวต้านทานโหลดเป็นศูนย์และแรงดันเอาท์พุทจะเท่ากับ V DD ตอนนี้เมื่อแรงดันไฟฟ้าขาเข้าเพิ่มขึ้นอีกทรานซิสเตอร์ของไดรเวอร์จะเริ่มทำกระแสที่ไม่เป็นศูนย์และ nMOS จะไปในบริเวณอิ่มตัว

ในทางคณิตศาสตร์

$$ I_ {D} = \ frac {K_ {n}} {2} \ left [V_ {GS} -V_ {TO} \ right] ^ {2} $$

การเพิ่มแรงดันไฟฟ้าขาเข้าให้มากขึ้นทรานซิสเตอร์ของไดรเวอร์จะเข้าสู่พื้นที่เชิงเส้นและเอาต์พุตของทรานซิสเตอร์ไดรเวอร์จะลดลง

$$ I_ {D} = \ frac {K_ {n}} {2} 2 \ left [V_ {GS} -V_ {TO} \ right] V_ {DS} -V_ {DS} ^ {2} $$

VTC ของอินเวอร์เตอร์โหลดตัวต้านทานที่แสดงด้านล่างแสดงโหมดการทำงานของทรานซิสเตอร์ไดรเวอร์และจุดแรงดันไฟฟ้า

อินเวอร์เตอร์พร้อมโหลด MOSFET ชนิด N

ข้อได้เปรียบหลักของการใช้ MOSFET เป็นอุปกรณ์โหลดคือพื้นที่ซิลิกอนที่ครอบครองโดยทรานซิสเตอร์มีขนาดเล็กกว่าพื้นที่ที่โหลดโดยตัวต้านทาน ที่นี่ MOSFET เป็นโหลดที่ใช้งานอยู่และอินเวอร์เตอร์ที่มีโหลดแบบแอคทีฟให้ประสิทธิภาพที่ดีกว่าอินเวอร์เตอร์ที่มีโหลดตัวต้านทาน

การปรับปรุงโหลด NMOS

อินเวอร์เตอร์สองตัวพร้อมอุปกรณ์โหลดประเภทการเพิ่มประสิทธิภาพแสดงอยู่ในรูป โหลดทรานซิสเตอร์สามารถใช้งานได้ทั้งในบริเวณอิ่มตัวหรือในพื้นที่เชิงเส้นขึ้นอยู่กับแรงดันไบอัสที่ใช้กับเทอร์มินัลเกต อินเวอร์เตอร์โหลดการเพิ่มประสิทธิภาพอิ่มตัวแสดงในรูป (ก). มันต้องมีแรงดันไฟฟ้าเดียวและกระบวนการผลิตที่ง่ายและเพื่อให้ V OHถูก จำกัด V DD - V T

อินเวอร์เตอร์โหลดการเพิ่มประสิทธิภาพเชิงเส้นแสดงในรูป (ข). มันทำงานในพื้นที่เชิงเส้นเสมอ ดังนั้น V OHระดับเท่ากับ V DD

อินเวอร์เตอร์โหลดเชิงเส้นมีขอบเสียงที่สูงกว่าเมื่อเทียบกับอินเวอร์เตอร์ที่เพิ่มประสิทธิภาพอิ่มตัว แต่ข้อเสียของอินเวอร์เตอร์การเพิ่มประสิทธิภาพเชิงเส้นคือต้องใช้แหล่งจ่ายไฟแยกกันสองตัวและทั้งสองวงจรต้องทนทุกข์ทรมานจากการกระจายพลังงานสูง ดังนั้นจึงไม่ใช้อินเวอร์เตอร์สำหรับการเพิ่มประสิทธิภาพในแอปพลิเคชันดิจิทัลขนาดใหญ่ใด ๆ

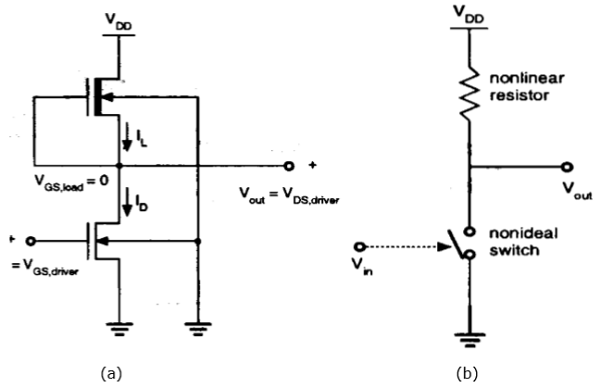

โหลดพร่อง NMOS

ข้อเสียของอินเวอร์เตอร์โหลดการเพิ่มประสิทธิภาพสามารถเอาชนะได้โดยใช้อินเวอร์เตอร์โหลดพร่อง เมื่อเทียบกับอินเวอร์เตอร์ที่มีการเพิ่มประสิทธิภาพอินเวอร์เตอร์โหลดพร่องต้องใช้ขั้นตอนการผลิตเพิ่มขึ้นอีกสองสามขั้นสำหรับการฝังช่องสัญญาณเพื่อปรับแรงดันไฟฟ้าเกณฑ์ของโหลด

ข้อดีของอินเวอร์เตอร์โหลดพร่องคือ - การเปลี่ยน VTC ที่คมชัดขอบเสียงที่ดีขึ้นแหล่งจ่ายไฟเดี่ยวและพื้นที่รูปแบบโดยรวมที่เล็กลง

ดังแสดงในรูปเกตและเทอร์มินัลต้นทางของโหลดเชื่อมต่ออยู่ ดังนั้น V GS = 0 ดังนั้นแรงดันไฟฟ้าเกณฑ์ของโหลดจึงเป็นลบ ดังนั้น

$$ V_ {GS, load}> V_ {T, load} $$ พอใจแล้ว

ดังนั้นอุปกรณ์โหลดจึงมีช่องการนำไฟฟ้าเสมอโดยไม่คำนึงถึงระดับแรงดันไฟฟ้าขาเข้าและขาออก

เมื่อทรานซิสเตอร์โหลดอยู่ในบริเวณอิ่มตัวกระแสโหลดจะถูกกำหนดโดย

$$ I_ {D, load} = \ frac {K_ {n, load}} {2} \ left [-V_ {T, load} \ left (V_ {out} \ right) \ right] ^ {2} $ $

เมื่อทรานซิสเตอร์โหลดอยู่ในพื้นที่เชิงเส้นกระแสโหลดจะถูกกำหนดโดย

$$ I_ {D, load} = \ frac {K_ {n, load}} {2} \ left [2 \ left | V_ {T โหลด} \ left (V_ {out} \ right) \ right |. \ left (V_ {DD} -V_ {out} \ right) - \ left (V_ {DD} -V_ {out} \ right ) ^ {2} \ right] $$

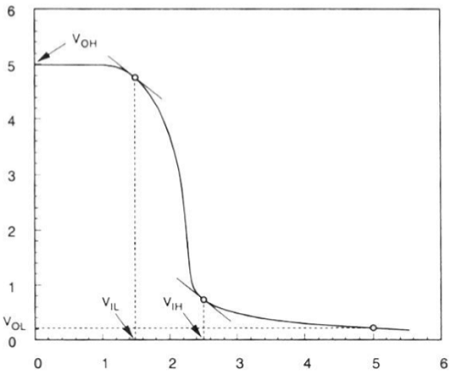

ลักษณะการถ่ายโอนแรงดันไฟฟ้าของอินเวอร์เตอร์โหลดพร่องแสดงในรูปด้านล่าง -

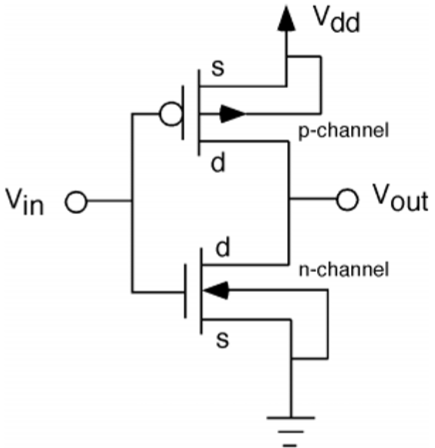

CMOS Inverter - วงจรการทำงานและคำอธิบาย

วงจรอินเวอร์เตอร์ CMOS แสดงดังรูป ที่นี่ทรานซิสเตอร์ nMOS และ pMOS ทำงานเป็นทรานซิสเตอร์ไดรเวอร์ เมื่อทรานซิสเตอร์ตัวหนึ่งเปิดอยู่อีกตัวหนึ่งปิด

การกำหนดค่านี้เรียกว่า complementary MOS (CMOS). อินพุตเชื่อมต่อกับเทอร์มินัลประตูของทรานซิสเตอร์ทั้งสองเพื่อให้ทั้งสองสามารถขับเคลื่อนโดยตรงด้วยแรงดันไฟฟ้าอินพุต พื้นผิวของ NMOS เชื่อมต่อกับพื้นดินและพื้นผิวของพีมอสที่เชื่อมต่อกับแหล่งจ่ายไฟ, V DD

ดังนั้น V SB = 0 สำหรับทรานซิสเตอร์ทั้งสองตัว

$$ V_ {GS, n} = V_ {in} $$

$$ V_ {DS, n} = V_ {out} $$

และ,

$$ V_ {GS, p} = V_ {in} -V_ {DD} $$

$$ V_ {DS, p} = V_ {out} -V_ {DD} $$

เมื่ออินพุตของ nMOS มีขนาดเล็กกว่าแรงดันไฟฟ้าเกณฑ์ (V ใน <V TO, n ) nMOS จะถูกตัดออกและ pMOS อยู่ในพื้นที่เชิงเส้น ดังนั้นกระแสระบายของทรานซิสเตอร์ทั้งสองจึงเป็นศูนย์

$$ I_ {D, n} = I_ {D, p} = 0 $$

ดังนั้นแรงดันเอาต์พุต V OHจึงเท่ากับแรงดันไฟฟ้า

$$ V_ {out} = V_ {OH} = V_ {DD} $$

เมื่อแรงดันไฟฟ้าขาเข้ามากกว่า V DD + V TO, pทรานซิสเตอร์ pMOS อยู่ในพื้นที่ตัดและ nMOS อยู่ในพื้นที่เชิงเส้นดังนั้นกระแสระบายของทรานซิสเตอร์ทั้งสองจึงเป็นศูนย์

$$ I_ {D, n} = I_ {D, p} = 0 $$

ดังนั้นแรงดันเอาต์พุต V OLจึงเท่ากับศูนย์

$$ V_ {out} = V_ {OL} = 0 $$

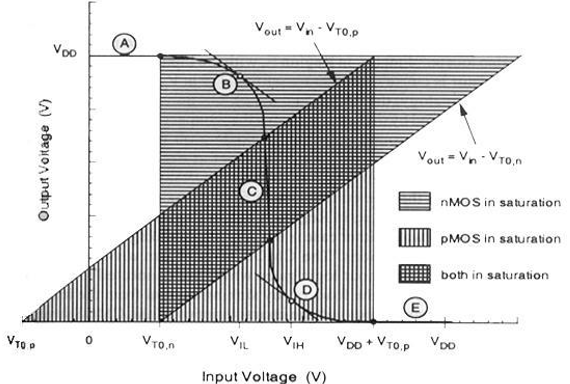

nMOS ทำงานในพื้นที่อิ่มตัวถ้า V in > V TOและหากเป็นไปตามเงื่อนไขต่อไปนี้

$$ V_ {DS, n} \ geq V_ {GS, n} -V_ {TO, n} $$

$$ V_ {out} \ geq V_ {in} -V_ {TO, n} $$

pMOS ทำงานในพื้นที่อิ่มตัวถ้า V ใน <V DD + V TO, pและหากเป็นไปตามเงื่อนไขต่อไปนี้

$$ V_ {DS, p} \ leq V_ {GS, p} -V_ {TO, p} $$

$$ V_ {out} \ leq V_ {in} -V_ {TO, p} $$

สำหรับค่าแรงดันไฟฟ้าขาเข้าที่แตกต่างกันพื้นที่การทำงานจะแสดงรายการด้านล่างสำหรับทรานซิสเตอร์ทั้งสองตัว

| ภูมิภาค | V ใน | V ออก | nMOS | pMOS |

|---|---|---|---|---|

| ก | <V TO, n | V OH | ตัด - ปิด | เชิงเส้น |

| ข | V IL | สูง≈ V OH | ความอิ่มตัว | เชิงเส้น |

| ค | V ธ | V ธ | ความอิ่มตัว | ความอิ่มตัว |

| ง | V IH | ต่ำ≈ V OL | เชิงเส้น | ความอิ่มตัว |

| จ | > (V DD + V TO, p ) | V OL | เชิงเส้น | ตัด - ปิด |

VTC ของ CMOS แสดงในรูปด้านล่าง -