การออกแบบ VLSI - วงจรลอจิก MOS แบบต่อเนื่อง

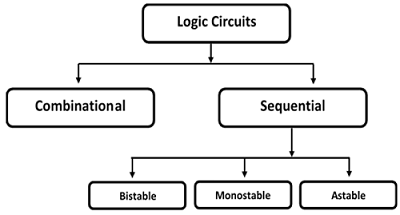

วงจรลอจิกแบ่งออกเป็นสองประเภท - (a) วงจรผสมและ (b) วงจรลำดับ

ในวงจร Combinational เอาต์พุตจะขึ้นอยู่กับเงื่อนไขของอินพุตล่าสุดเท่านั้น

ในวงจรลำดับผลลัพธ์ไม่เพียงขึ้นอยู่กับอินพุตล่าสุดเท่านั้น แต่ยังขึ้นอยู่กับเงื่อนไขของอินพุตก่อนหน้านี้ด้วย วงจรลำดับประกอบด้วยองค์ประกอบหน่วยความจำ

วงจรลำดับมีสามประเภท -

Bistable- วงจร Bistable มีจุดปฏิบัติการที่มั่นคงสองจุดและจะอยู่ในสถานะใดสถานะหนึ่ง ตัวอย่าง - เซลล์หน่วยความจำสลักฟลิปฟล็อปและรีจิสเตอร์

Monostable- วงจรโมโนสเตเบิลมีจุดปฏิบัติการที่เสถียรเพียงจุดเดียวและแม้ว่าจะถูกรบกวนชั่วคราวไปยังสถานะตรงกันข้าม แต่ก็จะกลับไปยังจุดปฏิบัติการที่เสถียร ตัวอย่าง: ตัวจับเวลาเครื่องกำเนิดพัลส์

Astable- วงจรไม่มีจุดปฏิบัติการที่มั่นคงและสั่นระหว่างหลายสถานะ ตัวอย่าง - Ring oscillator

วงจรลอจิก CMOS

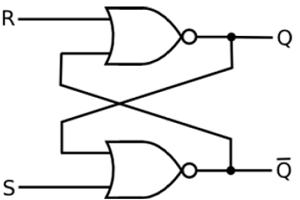

SR Latch ขึ้นอยู่กับ NOR Gate

หากอินพุตที่ตั้งไว้ (S) เท่ากับลอจิก "1" และอินพุตรีเซ็ตเท่ากับลอจิก "0." จากนั้นเอาต์พุต Q จะถูกบังคับให้ใช้ตรรกะ "1". แม้ว่า $ \ overline {Q} $ จะถูกบังคับให้ใช้ตรรกะ"0". ซึ่งหมายความว่าสลัก SR จะถูกตั้งค่าโดยไม่คำนึงถึงสถานะก่อนหน้า

ในทำนองเดียวกันถ้า S เท่ากับ "0" และ R เท่ากับ "1" จากนั้นเอาต์พุต Q จะถูกบังคับให้ "0" ในขณะที่ $ \ overline {Q} $ ถูกบังคับให้ "1". ซึ่งหมายความว่าสลักจะถูกรีเซ็ตโดยไม่คำนึงถึงสถานะที่ยึดไว้ก่อนหน้านี้ สุดท้ายถ้าอินพุตทั้งสอง S และ R เท่ากับลอจิก"1" จากนั้นเอาต์พุตทั้งสองจะถูกบังคับให้ใช้ตรรกะ "0" ซึ่งขัดแย้งกับความสมบูรณ์ของ Q และ $ \ overline {Q} $

ดังนั้นจึงไม่อนุญาตให้ใช้ชุดอินพุตนี้ในระหว่างการทำงานปกติ ตารางความจริงของ SR Latch ตาม NOR แสดงไว้ในตาราง

| ส | ร | ถาม | $ \ overline {Q} $ | การดำเนินการ |

|---|---|---|---|---|

| 0 | 0 | ถาม | $ \ overline {Q} $ | ถือ |

| 1 | 0 | 1 | 0 | ชุด |

| 0 | 1 | 0 | 1 | รีเซ็ต |

| 1 | 1 | 0 | 0 | ไม่ได้รับอนุญาต |

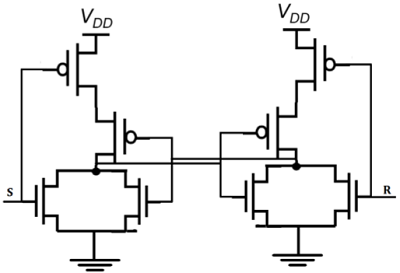

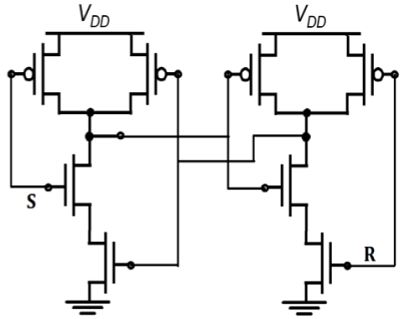

สลัก CMOS SR ขึ้นอยู่กับประตู NOR แสดงในรูปด้านล่าง

ถ้า S เท่ากับ V OHและ R เท่ากับ V OLทรานซิสเตอร์ที่เชื่อมต่อแบบขนาน M1 และ M2 ทั้งสองจะเปิดอยู่ แรงดันไฟฟ้าบนโหนด $ \ overline {Q} $ จะถือว่าระดับลอจิกต่ำของ V OL = 0

ในเวลาเดียวกันทั้ง M3 และ M4 ถูกปิดซึ่งจะส่งผลให้แรงดันไฟฟ้าตรรกะสูง V OHที่โหนด Q. ถ้า R เท่ากับ V OHและ S มีค่าเท่ากับ V OL , M1 และ M2 ปิดและ M3 และ M4 เปิดอยู่

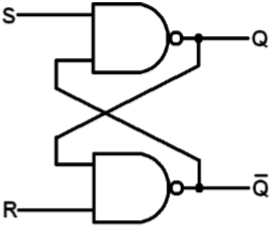

SR Latch ขึ้นอยู่กับ NAND Gate

แผนภาพบล็อกและแผนผังระดับประตูของสลัก SR ที่ใช้ NAND แสดงในรูป วงกลมขนาดเล็กที่ขั้วอินพุต S และ R แสดงว่าวงจรตอบสนองต่อสัญญาณอินพุตต่ำที่ใช้งานอยู่ ตารางความจริงของสลัก SR ที่ใช้ NAND แสดงไว้ในตาราง

| ส | ร | ถาม | Q ′ | |

| 0 | 0 | NC | NC | ไม่มีการเปลี่ยนแปลง. สลักยังคงอยู่ในสถานะปัจจุบัน |

| 1 | 0 | 1 | 0 | ชุดสลัก |

| 0 | 1 | 0 | 1 | รีเซ็ตสลัก |

| 1 | 1 | 0 | 0 | เงื่อนไขไม่ถูกต้อง |

ถ้า S ไปที่ 0 (ในขณะที่ R = 1) Q จะสูงดึง $ \ overline {Q} $ ต่ำและสลักจะเข้าสู่ Set state

S = 0 แล้ว Q = 1 (ถ้า R = 1)

ถ้า R ไปที่ 0 (ในขณะที่ S = 1) Q จะสูงดึง $ \ overline {Q} $ ต่ำและสลักจะรีเซ็ต

R = 0 แล้ว Q = 1 (ถ้า S = 1)

สถานะการระงับต้องการให้ทั้ง S และ R สูง ถ้า S = R = 0 แสดงว่าเอาต์พุตไม่ได้รับอนุญาตเนื่องจากจะส่งผลให้อยู่ในสถานะที่ไม่แน่นอน CMOS SR Latch ตาม NAND Gate แสดงดังรูป

Depletion-load nMOS SR Latch ตาม NAND Gate แสดงในรูป การทำงานคล้ายกับสลัก CMOS NAND SR การใช้งานวงจร CMOS มีการกระจายพลังงานคงที่ต่ำและมีอัตราสัญญาณรบกวนสูง

วงจรลอจิก CMOS

สลัก SR แบบนาฬิกา

รูปแสดงสลัก SR ที่ใช้ NOR พร้อมกับนาฬิกาที่เพิ่มเข้ามา สลักตอบสนองต่ออินพุต S และ R เฉพาะเมื่อ CLK สูง

เมื่อ CLK ต่ำสลักจะยังคงอยู่ในสถานะปัจจุบัน สังเกตว่า Q เปลี่ยนสถานะ -

- เมื่อ S ไปสูงระหว่าง CLK ที่เป็นบวก

- บนขอบ CLK ชั้นนำหลังจากมีการเปลี่ยนแปลงใน S & R ในช่วงเวลาที่ต่ำของ CLK

- ความผิดพลาดในเชิงบวกใน S ขณะที่ CLK สูง

- เมื่อ R ไปสูงระหว่าง CLK ที่เป็นบวก

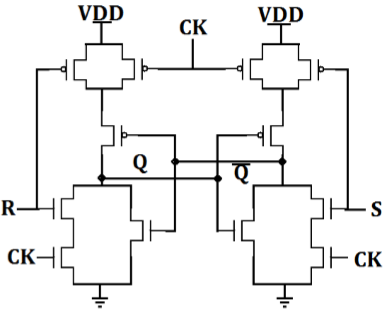

การใช้งาน CMOS AOI ของสลัก SR แบบโอเวอร์คล็อกแบบ NOR แสดงในรูป โปรดทราบว่าต้องใช้ทรานซิสเตอร์เพียง 12 ตัว

เมื่อ CLK อยู่ในระดับต่ำเทอร์มินัลสองชุดใน N ทรี N จะเปิดและทรานซิสเตอร์แบบขนานสองตัวในทรี P เปิดอยู่ดังนั้นจึงคงสถานะไว้ในเซลล์หน่วยความจำ

เมื่อสัญญาณนาฬิกาสูงวงจรจะกลายเป็นเพียงสลัก CMOS ที่ใช้ NOR ซึ่งจะตอบสนองต่ออินพุต S และ R

Clocked SR Latch based on NAND Gate

วงจรใช้กับประตู NAND สี่ประตู หากใช้วงจรนี้กับ CMOS ก็ต้องใช้ทรานซิสเตอร์ 16 ตัว

- สลักตอบสนองต่อ S หรือ R เฉพาะในกรณีที่ CLK สูง

- หากสัญญาณอินพุตทั้งสองและสัญญาณ CLK แอ็คทีฟสูงนั่นคือเอาต์พุตสลัก Q จะถูกตั้งค่าเมื่อ CLK = "1" S = "1" และ R = "0"

- ในทำนองเดียวกันสลักจะถูกรีเซ็ตเมื่อ CLK = "1," S = "0," และ

เมื่อ CLK ต่ำสลักจะยังคงอยู่ในสถานะปัจจุบัน

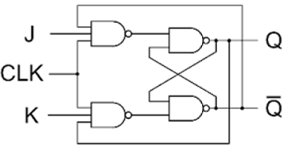

นาฬิกา JK Latch

รูปด้านบนแสดงสลัก JK แบบโอเวอร์คล็อกตามประตู NAND ข้อเสียของสลัก SR คือเมื่อทั้ง S และ R สูงสถานะเอาต์พุตจะไม่แน่นอน สลัก JK ช่วยขจัดปัญหานี้โดยใช้การป้อนกลับจากเอาต์พุตไปยังอินพุตเพื่อให้สามารถใช้สถานะอินพุตทั้งหมดของตารางความจริงได้ ถ้า J = K = 0 สลักจะคงสถานะปัจจุบันไว้

ถ้า J = 1 และ K = 0 สลักจะตั้งอยู่บนขอบนาฬิกาที่เป็นบวกถัดไปนั่นคือ Q = 1, $ \ overline {Q} $ = 0

ถ้า J = 0 และ K = 1 สลักจะรีเซ็ตบนขอบนาฬิกาที่เป็นบวกถัดไปนั่นคือ Q = 1 และ $ \ overline {Q} $ = 0

ถ้า J = K = 1 สลักจะสลับที่ขอบนาฬิกาที่เป็นบวกถัดไป

การทำงานของสลัก JK แบบตอกบัตรสรุปไว้ในตารางความจริงที่ระบุไว้ในตาราง

J |

K |

Q |

$ \ overline {Q} $ | S |

R |

Q |

$ \ overline {Q} $ | Operation |

| 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | ถือ |

| 1 | 0 | 1 | 1 | 1 | 0 | |||

| 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | รีเซ็ต |

| 1 | 0 | 1 | 0 | 0 | 1 | |||

| 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | ชุด |

| 1 | 0 | 1 | 1 | 1 | 0 | |||

| 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | สลับ |

| 1 | 0 | 1 | 0 | 0 | 1 |

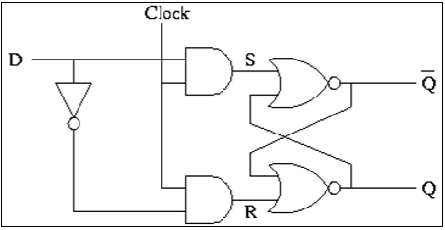

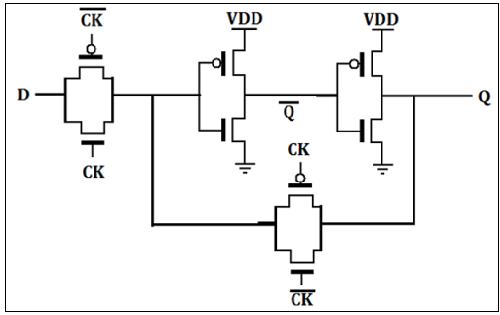

การติดตั้ง CMOS D Latch

โดยปกติสลัก D จะใช้กับสวิตช์เกียร์ (TG) ตามที่แสดงในรูป อินพุต TG เปิดใช้งานด้วย CLK ในขณะที่ลูปป้อนกลับสลัก TG เปิดใช้งานด้วย CLK อินพุต D ได้รับการยอมรับเมื่อ CLK สูง เมื่อ CLK ลดลงอินพุตจะถูกเปิดและสลักถูกตั้งค่าด้วยข้อมูลก่อนหน้า D