การออกแบบ VLSI - เทคโนโลยี FPGA

FPGA - บทนำ

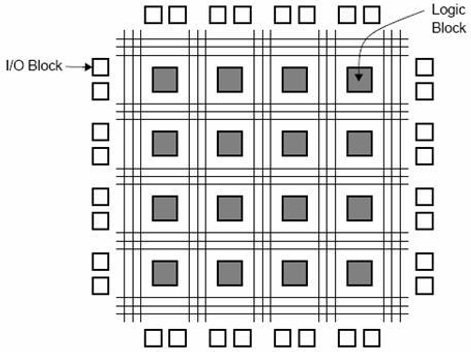

รูปแบบเต็มของ FPGA คือ "Field Programmable Gate Array”. ประกอบด้วยประตูลอจิกหนึ่งหมื่นถึงมากกว่าหนึ่งล้านประตูพร้อมการเชื่อมต่อโครงข่ายที่ตั้งโปรแกรมได้ การเชื่อมต่อระหว่างกันที่ตั้งโปรแกรมได้มีให้สำหรับผู้ใช้หรือนักออกแบบเพื่อทำหน้าที่ต่างๆ ชิป FPGA รุ่นทั่วไปจะแสดงในรูปที่กำหนด มีบล็อก I / O ซึ่งได้รับการออกแบบและกำหนดหมายเลขตามฟังก์ชัน สำหรับแต่ละโมดูลขององค์ประกอบระดับลอจิกมีCLB’s (Configurable Logic Blocks).

CLB ดำเนินการตามตรรกะที่กำหนดให้กับโมดูล การเชื่อมต่อระหว่างบล็อก CLB และ I / O ทำโดยใช้ช่องทางแนวนอนช่องเส้นทางแนวตั้งและ PSM (Multiplexers ที่ตั้งโปรแกรมได้)

จำนวน CLB ที่มีเฉพาะในการตัดสินความซับซ้อนของ FPGA ฟังก์ชันการทำงานของ CLB และ PSM ได้รับการออกแบบโดย VHDL หรือภาษาอธิบายฮาร์ดแวร์อื่น ๆ หลังจากการเขียนโปรแกรม CLB และ PSM จะถูกวางไว้บนชิปและเชื่อมต่อกันด้วยช่องทางกำหนดเส้นทาง

ข้อดี

- ต้องใช้เวลาน้อยมาก เริ่มตั้งแต่กระบวนการออกแบบไปจนถึงชิปที่ใช้งานได้

- ไม่มีขั้นตอนการผลิตทางกายภาพที่เกี่ยวข้อง

- ข้อเสียเพียงอย่างเดียวคือมีราคาแพงกว่ารูปแบบอื่น ๆ

การออกแบบประตูอาร์เรย์

gate array (GA)เป็นอันดับสองรองจาก FPGA ในแง่ของความสามารถในการสร้างต้นแบบที่รวดเร็ว แม้ว่าการเขียนโปรแกรมของผู้ใช้จะมีความสำคัญต่อการใช้งานการออกแบบของชิป FPGA แต่การออกแบบและการประมวลผลหน้ากากโลหะจะใช้สำหรับ GA การใช้งาน Gate Array ต้องใช้กระบวนการผลิตสองขั้นตอน

ระยะแรกส่งผลให้อาร์เรย์ของทรานซิสเตอร์ที่ไม่ได้ผูกมัดบนชิป GA แต่ละตัว ชิปที่ไม่ได้ผูกมัดเหล่านี้สามารถเก็บไว้สำหรับการปรับแต่งในภายหลังซึ่งทำได้โดยการกำหนดส่วนเชื่อมต่อระหว่างโลหะระหว่างทรานซิสเตอร์ของอาร์เรย์ การสร้างลวดลายของการเชื่อมต่อระหว่างโลหะจะทำในตอนท้ายของกระบวนการผลิตชิปดังนั้นเวลาหมุนเวียนจึงยังคงสั้นอยู่ 2-3 วันถึงสองสามสัปดาห์ รูปด้านล่างแสดงขั้นตอนการประมวลผลพื้นฐานสำหรับการใช้งานเกตอาร์เรย์

แพลตฟอร์มอาร์เรย์ประตูทั่วไปใช้พื้นที่เฉพาะที่เรียกว่าช่องสัญญาณสำหรับการกำหนดเส้นทางระหว่างเซลล์ระหว่างแถวหรือคอลัมน์ของทรานซิสเตอร์ MOS ทำให้การเชื่อมต่อระหว่างกันง่ายขึ้น รูปแบบการเชื่อมต่อที่ทำหน้าที่ลอจิกเกตพื้นฐานจะถูกเก็บไว้ในไลบรารีซึ่งสามารถใช้เพื่อปรับแต่งแถวของทรานซิสเตอร์ที่ไม่ได้กำหนดตามรายการเน็ต

ใน GAs สมัยใหม่ส่วนใหญ่จะใช้ชั้นโลหะหลายชั้นสำหรับการกำหนดเส้นทางช่องสัญญาณ ด้วยการใช้เลเยอร์ที่เชื่อมต่อกันหลายชั้นการกำหนดเส้นทางสามารถทำได้บนพื้นที่เซลล์ที่ใช้งานอยู่ เพื่อให้สามารถลบช่องเส้นทางได้เช่นเดียวกับชิป Sea-of-Gates (SOG) ที่นี่พื้นผิวชิปทั้งหมดถูกปกคลุมด้วยทรานซิสเตอร์ nMOS และ pMOS ที่ไม่ได้ผูกมัด ทรานซิสเตอร์ที่อยู่ใกล้เคียงสามารถปรับแต่งได้โดยใช้หน้ากากโลหะเพื่อสร้างลอจิกเกตพื้นฐาน

สำหรับการกำหนดเส้นทางระหว่างเซลล์จะต้องเสียสละทรานซิสเตอร์ที่ไม่ได้ผูกมัดบางตัว รูปแบบการออกแบบนี้ส่งผลให้มีความยืดหยุ่นมากขึ้นสำหรับการเชื่อมต่อระหว่างกันและโดยปกติจะมีความหนาแน่นสูงกว่า ปัจจัยการใช้ชิป GA วัดโดยพื้นที่ชิปที่ใช้หารด้วยพื้นที่ชิปทั้งหมด มันสูงกว่า FPGA และความเร็วชิปก็เช่นกัน

การออกแบบตามเซลล์มาตรฐาน

การออกแบบตามเซลล์มาตรฐานต้องการการพัฒนาชุดมาสก์แบบกำหนดเองแบบเต็ม เซลล์มาตรฐานเรียกอีกอย่างว่าโพลีเซลล์ ด้วยวิธีนี้เซลล์ลอจิกที่ใช้กันทั่วไปทั้งหมดได้รับการพัฒนามีลักษณะและจัดเก็บไว้ในไลบรารีเซลล์มาตรฐาน

ไลบรารีอาจมีเซลล์ไม่กี่ร้อยเซลล์รวมทั้งอินเวอร์เตอร์ประตู NAND ประตู NOR ประตู AOI ที่ซับซ้อนประตู OAI สลัก D และรองเท้าแตะ ประตูแต่ละประเภทสามารถใช้งานได้หลายรุ่นเพื่อให้มีความสามารถในการขับขี่ที่เพียงพอสำหรับพัดลมที่แตกต่างกัน ประตูอินเวอร์เตอร์สามารถมีขนาดมาตรฐานขนาดสองเท่าและขนาดสี่เท่าเพื่อให้ผู้ออกแบบชิปสามารถเลือกขนาดที่เหมาะสมเพื่อให้ได้ความเร็ววงจรสูงและความหนาแน่นของโครงร่าง

แต่ละเซลล์มีลักษณะตามหมวดหมู่ลักษณะที่แตกต่างกันเช่น

- เวลาหน่วงเมื่อเทียบกับความจุโหลด

- แบบจำลองวงจร

- โมเดลจำลองเวลา

- แบบจำลองความผิดพลาด

- ข้อมูลเซลล์สำหรับสถานที่และเส้นทาง

- ข้อมูลมาสก์

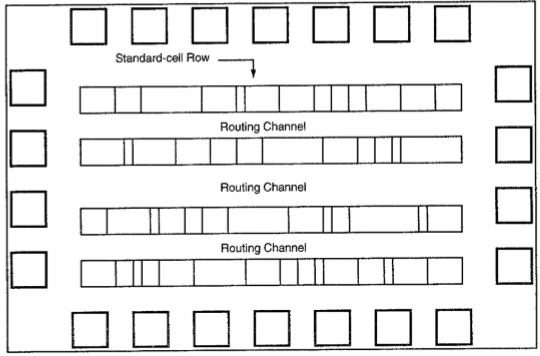

สำหรับการจัดวางเซลล์และการกำหนดเส้นทางโดยอัตโนมัติเค้าโครงเซลล์แต่ละแบบได้รับการออกแบบให้มีความสูงคงที่เพื่อให้เซลล์จำนวนหนึ่งสามารถถูกล้อมรอบข้างกันเพื่อสร้างแถวได้ รางกำลังและกราวด์วิ่งขนานกับขอบเขตบนและล่างของเซลล์ ดังนั้นเซลล์ข้างเคียงจึงแบ่งปันบัสพลังงานร่วมและบัสพื้นดินทั่วไป รูปที่แสดงด้านล่างเป็นแผนผังสำหรับการออกแบบตามเซลล์มาตรฐาน

การออกแบบที่กำหนดเองเต็มรูปแบบ

ในการออกแบบที่กำหนดเองทั้งหมดการออกแบบมาสก์ทั้งหมดถูกสร้างขึ้นใหม่โดยไม่ต้องใช้ไลบรารีใด ๆ ต้นทุนการพัฒนารูปแบบการออกแบบนี้สูงขึ้น ดังนั้นแนวคิดของการนำการออกแบบกลับมาใช้ใหม่จึงมีชื่อเสียงในการลดเวลาของวงจรการออกแบบและต้นทุนการพัฒนา

การออกแบบแบบกำหนดเองแบบเต็มที่ยากที่สุดอาจเป็นการออกแบบเซลล์หน่วยความจำไม่ว่าจะเป็นแบบคงที่หรือแบบไดนามิก สำหรับการออกแบบชิปลอจิกการต่อรองที่ดีสามารถหาได้โดยใช้การผสมผสานของสไตล์การออกแบบที่แตกต่างกันบนชิปเดียวกันเช่นเซลล์มาตรฐานเซลล์เส้นทางข้อมูลและprogrammable logic arrays (PLAs).

ในทางปฏิบัตินักออกแบบจะสร้างเค้าโครงที่กำหนดเองทั้งหมดเช่นรูปทรงเรขาคณิตการวางแนวและการจัดวางทรานซิสเตอร์ทุกตัว ผลผลิตการออกแบบมักจะต่ำมาก โดยทั่วไปทรานซิสเตอร์ไม่กี่สิบตัวต่อวันต่อผู้ออกแบบ ใน Digital CMOS VLSI การออกแบบแบบกำหนดเองทั้งหมดแทบจะไม่ถูกนำมาใช้เนื่องจากต้นทุนแรงงานสูง รูปแบบการออกแบบเหล่านี้รวมถึงการออกแบบผลิตภัณฑ์ปริมาณมากเช่นชิปหน่วยความจำไมโครโปรเซสเซอร์ประสิทธิภาพสูงและ FPGA