การออกแบบ VLSI - คู่มือฉบับย่อ

การรวมขนาดใหญ่มาก (VLSI) เป็นกระบวนการสร้างไฟล์ integrated circuit (IC) โดยรวมหลายพัน transistorsเป็นชิปตัวเดียว VLSI เริ่มขึ้นในปี 1970 เมื่อมีความซับซ้อนsemiconductor และ communicationมีการพัฒนาเทคโนโลยี microprocessor เป็นอุปกรณ์ VLSI

ก่อนการเปิดตัวเทคโนโลยี VLSI IC ส่วนใหญ่มีชุดฟังก์ชันที่ จำกัด ที่สามารถทำได้ อันelectronic circuit อาจประกอบด้วยไฟล์ CPU, ROM, RAM และอื่น ๆ glue logic. VLSI ช่วยให้นักออกแบบ IC สามารถเพิ่มสิ่งเหล่านี้ทั้งหมดลงในชิปเดียว

อุตสาหกรรมอิเล็กทรอนิกส์มีการเติบโตอย่างรวดเร็วในช่วงไม่กี่ทศวรรษที่ผ่านมาโดยส่วนใหญ่เกิดจากความก้าวหน้าอย่างรวดเร็วในเทคโนโลยีการผสานรวมขนาดใหญ่และแอพพลิเคชั่นการออกแบบระบบ ด้วยการถือกำเนิดของการออกแบบการผสานรวมขนาดใหญ่ (VLSI) จำนวนการใช้งานวงจรรวม (ICs) ในการประมวลผลประสิทธิภาพสูงการควบคุมการสื่อสารโทรคมนาคมการประมวลผลภาพและวิดีโอและอุปกรณ์อิเล็กทรอนิกส์สำหรับผู้บริโภคได้เพิ่มขึ้นอย่างรวดเร็ว

เทคโนโลยีล้ำสมัยในปัจจุบันเช่นวิดีโอความละเอียดสูงและอัตราบิตต่ำและการสื่อสารแบบเซลลูลาร์ทำให้ผู้ใช้ปลายทางได้รับแอปพลิเคชันจำนวนมหาศาลพลังการประมวลผลและการพกพา แนวโน้มนี้คาดว่าจะเติบโตอย่างรวดเร็วโดยมีผลกระทบที่สำคัญมากในการออกแบบ VLSI และการออกแบบระบบ

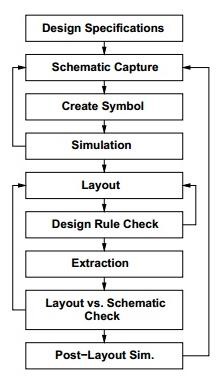

ขั้นตอนการออกแบบ VLSI

ขั้นตอนการออกแบบวงจร VLSI IC แสดงในรูปด้านล่าง ระดับต่างๆของการออกแบบจะถูกกำหนดหมายเลขและบล็อกจะแสดงกระบวนการในขั้นตอนการออกแบบ

ข้อมูลจำเพาะมาก่อนอธิบายในเชิงนามธรรมฟังก์ชันการทำงานส่วนต่อประสานและสถาปัตยกรรมของวงจร IC ดิจิทัลที่จะออกแบบ

จากนั้นคำอธิบายพฤติกรรมจะถูกสร้างขึ้นเพื่อวิเคราะห์การออกแบบในแง่ของฟังก์ชันการทำงานประสิทธิภาพการปฏิบัติตามมาตรฐานที่กำหนดและข้อกำหนดอื่น ๆ

คำอธิบาย RTL ทำได้โดยใช้ HDL คำอธิบาย RTL นี้จำลองขึ้นเพื่อทดสอบการทำงาน จากที่นี่เป็นต้นไปเราต้องการความช่วยเหลือจากเครื่องมือ EDA

จากนั้นคำอธิบาย RTL จะถูกแปลงเป็น netlist ระดับประตูโดยใช้เครื่องมือสังเคราะห์ตรรกะ netlist ระดับประตูเป็นคำอธิบายของวงจรในแง่ของประตูและการเชื่อมต่อระหว่างพวกเขาซึ่งทำในลักษณะที่ตรงตามข้อกำหนดเวลากำลังและพื้นที่

ในที่สุดก็มีการสร้างเค้าโครงจริงซึ่งจะได้รับการตรวจสอบและส่งไปยังการประดิษฐ์

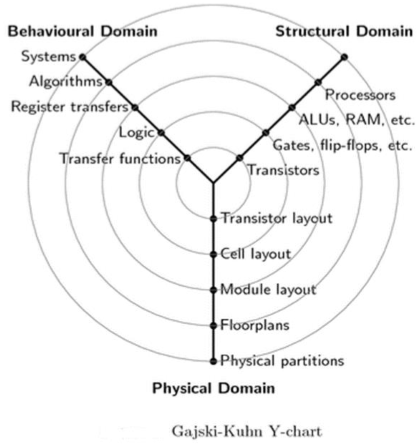

Y แผนภูมิ

กราฟ Gajski-Kuhn Y เป็นแบบจำลองที่รวบรวมข้อควรพิจารณาในการออกแบบอุปกรณ์เซมิคอนดักเตอร์

ทั้งสามโดเมนของแผนภูมิ Gajski-Kuhn Y อยู่บนแกนเรเดียล แต่ละโดเมนสามารถแบ่งออกเป็นระดับของนามธรรมโดยใช้วงแหวนศูนย์กลาง

ที่ระดับบนสุด (วงแหวนรอบนอก) เราจะพิจารณาสถาปัตยกรรมของชิป ที่ระดับล่าง (วงใน) เราปรับแต่งการออกแบบอย่างต่อเนื่องไปสู่การใช้งานที่ละเอียดยิ่งขึ้น -

การสร้างคำอธิบายโครงสร้างจากพฤติกรรมหนึ่งทำได้โดยกระบวนการสังเคราะห์ระดับสูงหรือการสังเคราะห์เชิงตรรกะ

การสร้างคำอธิบายทางกายภาพจากโครงสร้างสามารถทำได้โดยการสังเคราะห์เค้าโครง

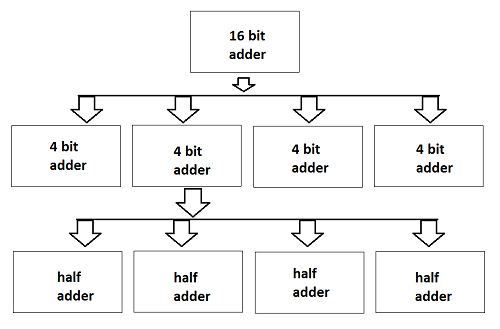

ลำดับชั้นการออกแบบ - โครงสร้าง

ลำดับชั้นของการออกแบบเกี่ยวข้องกับหลักการของ "Divide and Conquer" ไม่มีอะไรนอกจากแบ่งงานออกเป็นงานเล็ก ๆ จนกว่าจะถึงระดับที่ง่ายที่สุด กระบวนการนี้เหมาะสมที่สุดเนื่องจากวิวัฒนาการสุดท้ายของการออกแบบกลายเป็นเรื่องง่ายจนการผลิตง่ายขึ้น

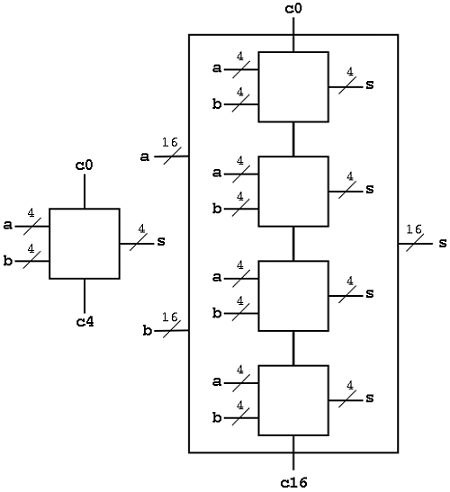

เราสามารถออกแบบงานที่กำหนดให้เป็นโดเมนของกระบวนการออกแบบ (Behavioral, Structural และ Geometrical) เพื่อให้เข้าใจสิ่งนี้เรามาดูตัวอย่างการออกแบบ Adder 16 บิตดังแสดงในรูปด้านล่าง

ที่นี่ชิปทั้งหมดของแอดเดอร์ 16 บิตแบ่งออกเป็นสี่โมดูลของแอดเดอร์ 4 บิต นอกจากนี้การแบ่ง adder 4 บิตออกเป็น adder 1 บิตหรือ half adder การเพิ่ม 1 บิตเป็นกระบวนการออกแบบที่ง่ายที่สุดและวงจรภายในยังง่ายต่อการประดิษฐ์บนชิป ตอนนี้การเชื่อมต่อแอดเดอร์ทั้งสี่ตัวสุดท้ายเราสามารถออกแบบแอดเดอร์ 4 บิตและต่อไปเราสามารถออกแบบแอดเดอร์ 16 บิตได้

FPGA - บทนำ

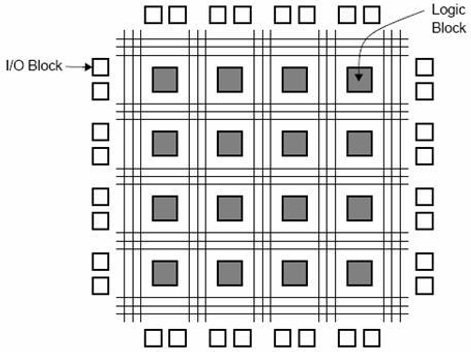

รูปแบบเต็มของ FPGA คือ "Field Programmable Gate Array”. ประกอบด้วยประตูลอจิกหนึ่งหมื่นถึงมากกว่าหนึ่งล้านประตูพร้อมการเชื่อมต่อโครงข่ายที่ตั้งโปรแกรมได้ การเชื่อมต่อระหว่างโปรแกรมมีให้สำหรับผู้ใช้หรือนักออกแบบเพื่อดำเนินการฟังก์ชันต่างๆ ชิป FPGA รุ่นทั่วไปจะแสดงในรูปที่กำหนด มีบล็อก I / O ซึ่งได้รับการออกแบบและกำหนดหมายเลขตามฟังก์ชัน สำหรับแต่ละโมดูลขององค์ประกอบระดับลอจิกมีCLB’s (Configurable Logic Blocks).

CLB ดำเนินการตามตรรกะที่กำหนดให้กับโมดูล การเชื่อมต่อระหว่างบล็อก CLB และ I / O ทำด้วยความช่วยเหลือของช่องเส้นทางแนวนอนช่องเส้นทางแนวตั้งและ PSM (Multiplexers ที่ตั้งโปรแกรมได้)

จำนวน CLB ที่มีเฉพาะในการตัดสินความซับซ้อนของ FPGA ฟังก์ชันการทำงานของ CLB และ PSM ได้รับการออกแบบโดย VHDL หรือภาษาอธิบายฮาร์ดแวร์อื่น ๆ หลังจากการเขียนโปรแกรม CLB และ PSM จะถูกวางไว้บนชิปและเชื่อมต่อกันด้วยช่องทางกำหนดเส้นทาง

ข้อดี

- ต้องใช้เวลาน้อยมาก เริ่มตั้งแต่กระบวนการออกแบบไปจนถึงชิปที่ใช้งานได้

- ไม่มีขั้นตอนการผลิตทางกายภาพที่เกี่ยวข้อง

- ข้อเสียเพียงอย่างเดียวคือมีราคาแพงกว่ารูปแบบอื่น ๆ

การออกแบบประตูอาร์เรย์

gate array (GA)เป็นอันดับสองรองจาก FPGA ในแง่ของความสามารถในการสร้างต้นแบบที่รวดเร็ว ในขณะที่การเขียนโปรแกรมของผู้ใช้มีความสำคัญต่อการใช้งานการออกแบบของชิป FPGA การออกแบบและการประมวลผลหน้ากากโลหะจะใช้สำหรับ GA การใช้งาน Gate Array ต้องใช้กระบวนการผลิตสองขั้นตอน

ระยะแรกส่งผลให้อาร์เรย์ของทรานซิสเตอร์ที่ไม่ได้ผูกมัดบนชิป GA แต่ละตัว ชิปที่ไม่ได้ผูกมัดเหล่านี้สามารถจัดเก็บไว้สำหรับการปรับแต่งในภายหลังซึ่งทำได้โดยการกำหนดส่วนเชื่อมต่อระหว่างโลหะระหว่างทรานซิสเตอร์ของอาร์เรย์ การสร้างลวดลายของการเชื่อมต่อระหว่างโลหะจะทำในตอนท้ายของกระบวนการผลิตชิปดังนั้นเวลาหมุนเวียนจึงยังคงสั้นอยู่ 2-3 วันถึงสองสามสัปดาห์ รูปด้านล่างแสดงขั้นตอนการประมวลผลพื้นฐานสำหรับการใช้งานเกตอาร์เรย์

แพลตฟอร์มอาร์เรย์ประตูทั่วไปใช้พื้นที่เฉพาะที่เรียกว่าช่องสัญญาณสำหรับการกำหนดเส้นทางระหว่างเซลล์ระหว่างแถวหรือคอลัมน์ของทรานซิสเตอร์ MOS ทำให้การเชื่อมต่อระหว่างกันง่ายขึ้น รูปแบบการเชื่อมต่อที่ทำหน้าที่ลอจิกเกตพื้นฐานจะถูกเก็บไว้ในไลบรารีซึ่งสามารถใช้เพื่อปรับแต่งแถวของทรานซิสเตอร์ที่ไม่ได้กำหนดตามรายการเน็ต

ใน GAs สมัยใหม่ส่วนใหญ่จะใช้ชั้นโลหะหลายชั้นสำหรับการกำหนดเส้นทางช่องสัญญาณ ด้วยการใช้เลเยอร์ที่เชื่อมต่อกันหลายชั้นการกำหนดเส้นทางสามารถทำได้บนพื้นที่เซลล์ที่ใช้งานอยู่ เพื่อให้สามารถลบช่องเส้นทางได้เช่นเดียวกับชิป Sea-of-Gates (SOG) ที่นี่พื้นผิวชิปทั้งหมดถูกปกคลุมด้วยทรานซิสเตอร์ nMOS และ pMOS ที่ไม่ได้ผูกมัด ทรานซิสเตอร์ที่อยู่ใกล้เคียงสามารถปรับแต่งได้โดยใช้หน้ากากโลหะเพื่อสร้างลอจิกเกตพื้นฐาน

สำหรับการกำหนดเส้นทางระหว่างเซลล์จะต้องเสียสละทรานซิสเตอร์ที่ไม่ได้ผูกมัดบางตัว รูปแบบการออกแบบนี้ส่งผลให้มีความยืดหยุ่นมากขึ้นสำหรับการเชื่อมต่อระหว่างกันและโดยปกติจะมีความหนาแน่นสูงกว่า ปัจจัยการใช้ชิป GA วัดโดยพื้นที่ชิปที่ใช้หารด้วยพื้นที่ชิปทั้งหมด มันสูงกว่า FPGA และความเร็วชิปก็เช่นกัน

การออกแบบตามเซลล์มาตรฐาน

การออกแบบตามเซลล์มาตรฐานต้องการการพัฒนาชุดมาสก์แบบกำหนดเองแบบเต็ม เซลล์มาตรฐานเรียกอีกอย่างว่าโพลีเซลล์ ด้วยวิธีนี้เซลล์ลอจิกที่ใช้กันทั่วไปทั้งหมดได้รับการพัฒนามีลักษณะเฉพาะและจัดเก็บไว้ในไลบรารีเซลล์มาตรฐาน

ไลบรารีอาจมีเซลล์ไม่กี่ร้อยเซลล์รวมทั้งอินเวอร์เตอร์ประตู NAND ประตู NOR ประตู AOI ที่ซับซ้อนประตู OAI สลัก D และรองเท้าแตะ ประตูแต่ละประเภทสามารถใช้งานได้หลายเวอร์ชันเพื่อให้มีความสามารถในการขับขี่ที่เพียงพอสำหรับพัดลมที่แตกต่างกัน ประตูอินเวอร์เตอร์สามารถมีขนาดมาตรฐานขนาดสองเท่าและขนาดสี่เท่าเพื่อให้ผู้ออกแบบชิปสามารถเลือกขนาดที่เหมาะสมเพื่อให้ได้ความเร็ววงจรสูงและความหนาแน่นของโครงร่าง

แต่ละเซลล์มีลักษณะตามหมวดหมู่ลักษณะที่แตกต่างกันเช่น

- เวลาหน่วงเมื่อเทียบกับความจุโหลด

- แบบจำลองวงจร

- โมเดลจำลองเวลา

- แบบจำลองความผิดพลาด

- ข้อมูลเซลล์สำหรับสถานที่และเส้นทาง

- ข้อมูลมาสก์

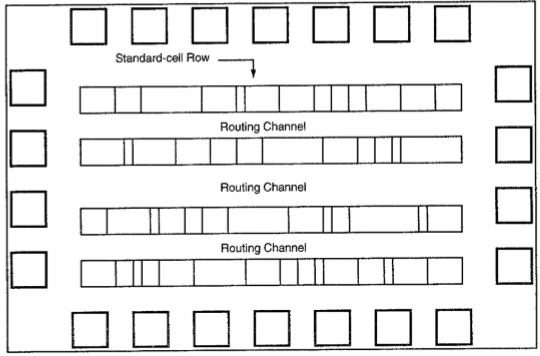

สำหรับการจัดวางเซลล์และการกำหนดเส้นทางโดยอัตโนมัติเค้าโครงเซลล์แต่ละแบบได้รับการออกแบบให้มีความสูงคงที่เพื่อให้เซลล์จำนวนหนึ่งสามารถถูกล้อมรอบข้างกันเพื่อสร้างแถวได้ รางกำลังและกราวด์วิ่งขนานกับขอบเขตบนและล่างของเซลล์ ดังนั้นเซลล์ใกล้เคียงจึงแบ่งปันบัสพลังงานร่วมและบัสพื้นดินทั่วไป รูปที่แสดงด้านล่างเป็นแผนผังสำหรับการออกแบบตามเซลล์มาตรฐาน

การออกแบบที่กำหนดเองเต็มรูปแบบ

ในการออกแบบที่กำหนดเองทั้งหมดการออกแบบมาสก์ทั้งหมดถูกสร้างขึ้นใหม่โดยไม่ต้องใช้ไลบรารีใด ๆ ต้นทุนการพัฒนารูปแบบการออกแบบนี้สูงขึ้น ดังนั้นแนวคิดของการนำการออกแบบกลับมาใช้ใหม่จึงมีชื่อเสียงในการลดเวลาของวงจรการออกแบบและต้นทุนการพัฒนา

การออกแบบที่กำหนดเองเต็มรูปแบบที่ยากที่สุดอาจเป็นการออกแบบเซลล์หน่วยความจำไม่ว่าจะเป็นแบบคงที่หรือแบบไดนามิก สำหรับการออกแบบชิปลอจิกการต่อรองที่ดีสามารถหาได้โดยใช้การผสมผสานของรูปแบบการออกแบบที่แตกต่างกันบนชิปเดียวกันเช่นเซลล์มาตรฐานเซลล์เส้นทางข้อมูลและprogrammable logic arrays (PLAs).

ในทางปฏิบัติผู้ออกแบบจะสร้างเค้าโครงที่กำหนดเองทั้งหมดเช่นรูปทรงเรขาคณิตการวางแนวและตำแหน่งของทรานซิสเตอร์ทุกตัว ผลผลิตการออกแบบมักจะต่ำมาก โดยทั่วไปทรานซิสเตอร์ไม่กี่สิบตัวต่อวันต่อผู้ออกแบบ ใน Digital CMOS VLSI การออกแบบแบบกำหนดเองทั้งหมดแทบจะไม่ได้ใช้เนื่องจากต้นทุนแรงงานที่สูง รูปแบบการออกแบบเหล่านี้รวมถึงการออกแบบผลิตภัณฑ์ปริมาณมากเช่นชิปหน่วยความจำไมโครโปรเซสเซอร์ประสิทธิภาพสูงและ FPGA

เทคโนโลยี MOSFET เสริม (CMOS) ถูกนำมาใช้กันอย่างแพร่หลายในปัจจุบันเพื่อสร้างวงจรในการใช้งานที่หลากหลายและหลากหลาย คอมพิวเตอร์ซีพียูและโทรศัพท์มือถือในปัจจุบันใช้ประโยชน์จาก CMOS เนื่องจากข้อดีหลายประการ CMOS ให้การกระจายพลังงานต่ำความเร็วค่อนข้างสูงขอบสัญญาณรบกวนสูงในทั้งสองสถานะและจะทำงานในแหล่งกำเนิดและแรงดันไฟฟ้าอินพุตที่หลากหลาย (หากแรงดันไฟฟ้าของแหล่งจ่ายคงที่)

สำหรับกระบวนการที่เราจะพูดถึงประเภทของทรานซิสเตอร์ที่มีคือ Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET) ทรานซิสเตอร์เหล่านี้เกิดขึ้นas a ‘sandwich’ประกอบด้วยชั้นเซมิคอนดักเตอร์มักจะเป็นชิ้นหรือเวเฟอร์จากผลึกซิลิกอนเดี่ยว ชั้นของซิลิกอนไดออกไซด์ (ออกไซด์) และชั้นของโลหะ

โครงสร้างของ MOSFET

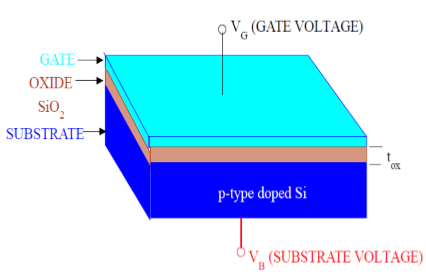

ดังแสดงในรูปโครงสร้าง MOS ประกอบด้วยสามชั้น -

The Metal Gate Electrode

The Insulating Oxide Layer (SiO2)

P – type Semiconductor (Substrate)

โครงสร้าง MOS เป็นตัวเก็บประจุโดยมีประตูและพื้นผิวเป็นแผ่นสองแผ่นและชั้นออกไซด์เป็นวัสดุอิเล็กทริก ความหนาของวัสดุอิเล็กทริก (SiO 2 ) มักอยู่ระหว่าง 10 นาโนเมตรถึง 50 นาโนเมตร ความเข้มข้นและการกระจายตัวของพาหะภายในวัสดุพิมพ์สามารถจัดการได้โดยแรงดันภายนอกที่ใช้กับประตูและขั้วของวัสดุพิมพ์ ตอนนี้เพื่อทำความเข้าใจโครงสร้างของ MOS ก่อนอื่นให้พิจารณาคุณสมบัติทางไฟฟ้าพื้นฐานของสารตั้งต้นเซมิคอนดักเตอร์ชนิด P

ความเข้มข้นของตัวพาในวัสดุเซมิคอนดักเตอร์เป็นไปตาม Mass Action Law. Mass Action Law กำหนดโดย -

$$n.p=n_{i}^{2}$$

ที่ไหน

n คือความเข้มข้นของอิเล็กตรอนแบบพาหะ

p คือผู้ให้บริการความเข้มข้นของรู

ni เป็นความเข้มข้นของผู้ให้บริการภายในของซิลิคอน

ตอนนี้ถือว่าพื้นผิวที่มีการเจืออย่างเท่าเทียมกันกับใบเสร็จ (โบรอน) ความเข้มข้น N ดังนั้นความเข้มข้นของอิเล็กตรอนและโฮลในสารตั้งต้นชนิด p คือ

$$n_{po}=\frac{n_{i}^{2}}{N_{A}}$$

$$p_{po}=N_{A}$$

ที่นี่ความเข้มข้นของยาสลบ NAคือ (10 15ถึง 10 16ซม. −3 ) มากกว่าความเข้มข้นภายใน ni ตอนนี้เพื่อทำความเข้าใจโครงสร้าง MOS ให้พิจารณาแผนภาพระดับพลังงานของสารตั้งต้นซิลิคอนชนิด p

ดังแสดงในรูปช่องว่างของวงดนตรีระหว่างแถบการนำกระแสและแถบคาดเอวคือ 1.1eV ที่นี่ Fermi potential Φ Fคือความแตกต่างระหว่างระดับภายใน Fermi (E i ) และระดับ Fermi (E FP )

โดยที่ Fermi ระดับ E Fขึ้นอยู่กับความเข้มข้นของยาสลบ Fermi potential Φ Fคือความแตกต่างระหว่างระดับภายใน Fermi (E i ) และระดับ Fermi (E FP )

ในทางคณิตศาสตร์

$$\Phi_{Fp}=\frac{E_{F}-E_{i}}{q}$$

ความต่างศักย์ระหว่างแถบการนำไฟฟ้าและพื้นที่ว่างเรียกว่าความสัมพันธ์ของอิเล็กตรอนและแสดงด้วย qx

ดังนั้นพลังงานที่จำเป็นสำหรับอิเล็กตรอนในการเคลื่อนที่จากระดับเฟอร์มิไปยังพื้นที่ว่างเรียกว่าฟังก์ชันการทำงาน (qΦ S ) และได้รับจาก

$$q\Phi _{s}=(E_{c}-E_{F})+qx$$

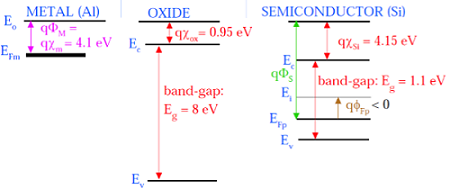

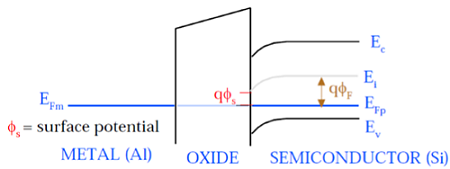

รูปต่อไปนี้แสดงแผนภาพแถบพลังงานของส่วนประกอบที่ประกอบเป็น MOS

ดังแสดงในรูปด้านบนฉนวนชั้นSiO 2มีช่องว่างแถบพลังงานขนาดใหญ่ที่ 8eV และฟังก์ชันการทำงานเท่ากับ 0.95 eV ประตูโลหะมีฟังก์ชันการทำงาน 4.1eV ที่นี่ฟังก์ชั่นการทำงานแตกต่างกันดังนั้นมันจะสร้างแรงดันตกคร่อมระบบ MOS รูปด้านล่างแสดงแผนภาพแถบพลังงานรวมของระบบ MOS

ดังแสดงในรูปนี้ระดับศักย์ไฟฟ้าของประตูโลหะและเซมิคอนดักเตอร์ (Si) มีศักยภาพเท่ากัน ศักยภาพเฟอร์มิที่พื้นผิวเรียกว่าศักย์พื้นผิวΦ Sและมีขนาดเล็กกว่าศักย์เฟอร์มิΦ Fในขนาด

การทำงานของ MOSFET

MOSFET ประกอบด้วยตัวเก็บประจุ MOS ที่มีทางแยก pn สองตัววางปิดกับพื้นที่ช่องสัญญาณและพื้นที่นี้ถูกควบคุมโดยแรงดันเกต ในการทำให้ทางแยก pn ทั้งสองมีความเอนเอียงแบบย้อนกลับศักยภาพของวัสดุพิมพ์จะถูกเก็บไว้ต่ำกว่าศักยภาพของขั้วต่ออีกสามขั้ว

หากแรงดันเกตเพิ่มขึ้นเกินขีด จำกัด แรงดันไฟฟ้า (V GS > V TO ) ชั้นผกผันจะถูกสร้างขึ้นบนพื้นผิวและช่องประเภท n จะเกิดขึ้นระหว่างแหล่งจ่ายและท่อระบายน้ำ นี้ n - ช่องประเภทจะดำเนินการระบายน้ำในปัจจุบันให้เป็นไปตาม V DSคุ้มค่า

สำหรับค่า V DS ที่แตกต่างกันMOSFET สามารถใช้งานได้ในภูมิภาคต่างๆตามที่อธิบายไว้ด้านล่าง

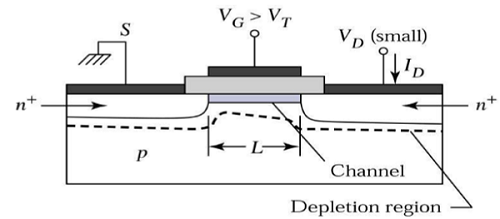

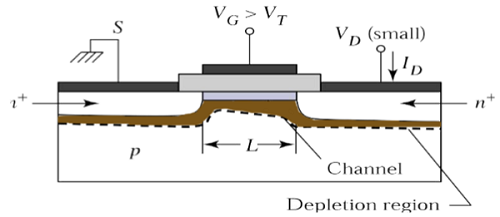

ภูมิภาคเชิงเส้น

ที่ V DS = 0 สมดุลทางความร้อนมีอยู่ในพื้นที่ช่องกลับด้านและระบายกระแส I D = 0 ตอนนี้ถ้าแรงดันท่อระบายน้ำขนาดเล็กใช้ V DS > 0 กระแสระบายที่เป็นสัดส่วนกับ V DSจะเริ่มไหลจากแหล่งที่มาไปยัง ระบายผ่านช่อง

ช่องสัญญาณให้เส้นทางต่อเนื่องสำหรับการไหลของกระแสจากแหล่งที่มาไปยังท่อระบายน้ำ โหมดการทำงานนี้เรียกว่าlinear region. มุมมองหน้าตัดของ MOSFET แบบ n-channel ซึ่งทำงานในพื้นที่เชิงเส้นแสดงไว้ในรูปด้านล่าง

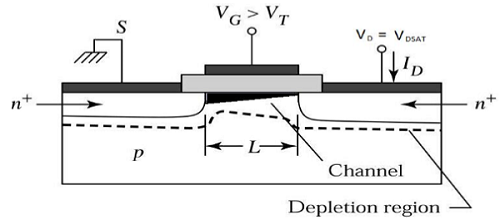

ที่ Edge of Saturation Region

ตอนนี้ถ้า V DSเพิ่มขึ้นประจุในช่องสัญญาณและความลึกของช่องจะลดลงเมื่อสิ้นสุดท่อระบายน้ำ สำหรับ V DS = V DSATประจุในช่องสัญญาณจะลดลงเป็นศูนย์ซึ่งเรียกว่าpinch – off point. มุมมองภาพตัดขวางของ N-channel MOSFET ที่ทำงานที่ขอบของขอบเขตความอิ่มตัวจะแสดงในรูปด้านล่าง

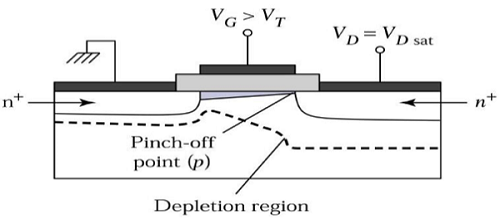

ภาคความอิ่มตัว

สำหรับ V DS > V DSATพื้นผิวที่หมดอยู่ใกล้จะระบายออกและโดยการเพิ่มแรงดันไฟฟ้าของท่อระบายน้ำบริเวณที่หมดลงนี้จะขยายไปยังแหล่งกำเนิด

โหมดการทำงานนี้เรียกว่า Saturation region. อิเล็กตรอนที่มาจากแหล่งกำเนิดไปยังปลายช่องป้อนในบริเวณท่อระบายน้ำ - พื้นที่พร่องและถูกเร่งไปยังท่อระบายน้ำในสนามไฟฟ้าสูง

MOSFET Current - ลักษณะแรงดันไฟฟ้า

เพื่อให้เข้าใจลักษณะกระแส - แรงดันไฟฟ้าของ MOSFET การประมาณสำหรับช่องสัญญาณเสร็จสิ้น หากไม่มีการประมาณนี้การวิเคราะห์สามมิติของระบบ MOS จะซับซ้อน Gradual Channel Approximation (GCA) สำหรับลักษณะแรงดันไฟฟ้าในปัจจุบันจะช่วยลดปัญหาในการวิเคราะห์

การประมาณช่องสัญญาณแบบค่อยเป็นค่อยไป (GCA)

พิจารณามุมมองตัดขวางของ n channel MOSFET ที่ทำงานในโหมดเชิงเส้น ที่นี่แหล่งที่มาและวัสดุพิมพ์เชื่อมต่อกับพื้นดิน V S = V B = 0 ประตู - เพื่อ - แหล่งที่มา (V GS ) และท่อระบายน้ำ - เพื่อ - แรงดันไฟฟ้าที่แหล่งที่มา (V DS ) แรงดันไฟฟ้าที่เป็นพารามิเตอร์ภายนอกที่ควบคุมการระบายน้ำในปัจจุบันผมD

แรงดันไฟฟ้า V GSถูกตั้งค่าเป็นแรงดันไฟฟ้าที่มากกว่าแรงดันไฟฟ้าเกณฑ์ V TOเพื่อสร้างช่องระหว่างแหล่งจ่ายและท่อระบายน้ำ ดังแสดงในรูปทิศทาง x ตั้งฉากกับพื้นผิวและทิศทาง y ขนานกับพื้นผิว

ที่นี่ y = 0 ที่ปลายต้นทางดังแสดงในรูป แรงดันไฟฟ้าของช่องเกี่ยวกับแหล่งที่มาจะแสดงโดยVC(Y). สมมติว่าแรงดันไฟฟ้าเกณฑ์ VTO คงที่ตามพื้นที่ช่องระหว่าง y = 0 ถึง y = L เงื่อนไขขอบเขตสำหรับแรงดันช่อง V Cคือ -

$$V_{c}\left ( y = 0 \right ) = V_{s} = 0 \,and\,V_{c}\left ( y = L \right ) = V_{DS}$$

เรายังสามารถสันนิษฐานได้ว่า

$$V_{GS}\geq V_{TO}$$ และ

$$V_{GD} = V_{GS}-V_{DS}\geq V_{TO}$$

ให้ Q1 (y) เป็นประจุอิเล็กตรอนเคลื่อนที่ทั้งหมดในชั้นผกผันของพื้นผิว ประจุอิเล็กตรอนนี้สามารถแสดงเป็น -

$$Q1(y)=-C_{ox}.[V_{GS}-V_{C(Y)}-V_{TO}]$$

รูปด้านล่างแสดงรูปทรงเรขาคณิตเชิงพื้นที่ของชั้นผกผันพื้นผิวและระบุขนาดของมัน ชั้นผกผันจะเรียวลงเมื่อเราย้ายจากท่อระบายน้ำไปยังแหล่งที่มา ตอนนี้ถ้าเราพิจารณาสีย้อมพื้นที่เล็ก ๆ ของความยาวช่อง L แล้วความต้านทานที่เพิ่มขึ้น dR ที่นำเสนอโดยภูมิภาคนี้สามารถแสดงเป็น -

$$dR=-\frac{dy}{w.\mu _{n}.Q1(y)}$$

ที่นี่เครื่องหมายลบเกิดจากขั้วลบของประจุชั้นผกผัน Q1 และμ nคือความคล่องตัวของพื้นผิวซึ่งคงที่ ตอนนี้แทนที่ค่าของ Q1 (y) ในสมการ dR -

$$dR=-\frac{dy}{w.\mu _{n}.\left \{ -C_{ox}\left [ V_{GS}-V_{C\left ( Y \right )} \right ]-V_{TO} \right \}}$$

$$dR=\frac{dy}{w.\mu _{n}.C_{ox}\left [ V_{GS}-V_{C\left ( Y \right )} \right ]-V_{TO}}$$

ตอนนี้แรงดันตกในพื้นที่ dy ขนาดเล็กสามารถกำหนดได้

$$dV_{c}=I_{D}.dR$$

ใส่ค่าของ dR ในสมการด้านบน

$$dV_{C}=I_{D}.\frac{dy}{w.\mu_{n}.C_{ox}\left [ V_{GS}-V_{C(Y)} \right ]-V_{TO}}$$

$$w.\mu _{n}.C_{ox}\left [ V_{GS}-V_{C(Y)}-V_{TO} \right ].dV_{C}=I_{D}.dy$$

เพื่อให้ได้ ID ปัจจุบันของท่อระบายน้ำในพื้นที่ช่องสัญญาณทั้งหมดสมการข้างต้นสามารถรวมเข้ากับช่องจาก y = 0 ถึง y = L และแรงดันไฟฟ้า V C (y) = 0 ถึง V C (y) = V DS ,

$$C_{ox}.w.\mu _{n}.\int_{V_{c}=0}^{V_{DS}} \left [ V_{GS}-V_{C\left ( Y \right )}-V_{TO} \right ].dV_{C} = \int_{Y=0}^{L}I_{D}.dy$$

$$\frac{C_{ox}.w.\mu _{n}}{2}\left ( 2\left [ V_{GS}-V_{TO} \right ] V_{DS}-V_{DS}^{2}\right ) = I_{D}\left [ L-0 \right ]$$

$$I_{D} = \frac{C_{ox}.\mu _{n}}{2}.\frac{w}{L}\left ( 2\left [ V_{GS}-V_{TO} \right ]V_{DS}-V_{DS}^{2} \right )$$

สำหรับภูมิภาคเชิงเส้น V DS <V GS - V TO สำหรับพื้นที่อิ่มตัวค่าของ V DSจะมากกว่า (V GS - V TO ) ดังนั้นสำหรับพื้นที่อิ่มตัว V DS = (V GS - V TO )

$$I_{D} = C_{ox}.\mu _{n}.\frac{w}{2}\left ( \frac{\left [ 2V_{DS} \right ]V_{DS}-V_{DS}^{2}}{L} \right )$$

$$I_{D} = C_{ox}.\mu _{n}.\frac{w}{2}\left ( \frac{2V_{DS}^{2}-V_{DS}^{2}}{L} \right )$$

$$I_{D} = C_{ox}.\mu _{n}.\frac{w}{2}\left ( \frac{V_{DS}^{2}}{L} \right )$$

$$I_{D} = C_{ox}.\mu _{n}.\frac{w}{2}\left ( \frac{\left [ V_{GS}-V_{TO} \right ]^{2}}{L} \right )$$

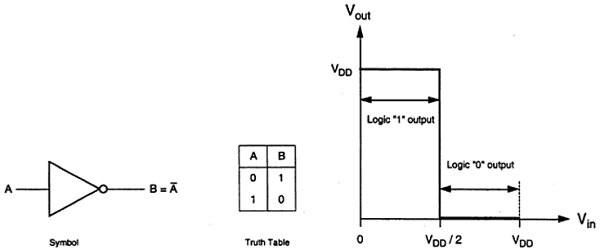

อินเวอร์เตอร์ถือเป็นหัวใจสำคัญของการออกแบบดิจิทัลทั้งหมด เมื่อเข้าใจการทำงานและคุณสมบัติอย่างชัดเจนแล้วการออกแบบโครงสร้างที่ซับซ้อนมากขึ้นเช่นประตู NAND, แอดเดอร์, ตัวคูณและไมโครโปรเซสเซอร์จะง่ายขึ้นมาก พฤติกรรมทางไฟฟ้าของวงจรที่ซับซ้อนเหล่านี้สามารถหาได้เกือบทั้งหมดโดยการประมาณผลลัพธ์ที่ได้รับสำหรับอินเวอร์เตอร์

การวิเคราะห์อินเวอร์เตอร์สามารถขยายได้เพื่ออธิบายพฤติกรรมของเกตที่ซับซ้อนมากขึ้นเช่น NAND, NOR หรือ XOR ซึ่งจะสร้างบล็อคส่วนประกอบสำหรับโมดูลเช่นตัวคูณและตัวประมวลผล ในบทนี้เรามุ่งเน้นไปที่การเกิดใหม่เพียงครั้งเดียวของประตูอินเวอร์เตอร์ซึ่งเป็นอินเวอร์เตอร์ CMOS แบบคงที่หรือเรียกสั้น ๆ ว่าอินเวอร์เตอร์ CMOS ซึ่งเป็นที่นิยมมากที่สุดในปัจจุบันดังนั้นจึงสมควรได้รับความสนใจเป็นพิเศษ

หลักการทำงาน

สัญลักษณ์ลอจิกและตารางความจริงของอินเวอร์เตอร์ในอุดมคติแสดงไว้ในรูปด้านล่าง นี่คืออินพุตและ B คือเอาต์พุตแบบกลับด้านที่แสดงโดยแรงดันไฟฟ้าของโหนด การใช้ลอจิกเชิงบวกค่าบูลีนของลอจิก 1 จะแสดงด้วย V ddและลอจิก 0 แทนด้วย 0 V thคือแรงดันไฟฟ้าเกณฑ์อินเวอร์เตอร์ซึ่งก็คือ V dd / 2 โดยที่ V ddคือแรงดันเอาต์พุต

เอาท์พุทจะเปลี่ยนจาก 0 ถึง V DDเมื่อป้อนข้อมูลน้อยกว่า V TH ดังนั้นสำหรับ 0 <V ในเอาต์พุต<V thเท่ากับอินพุตลอจิก 0 และ V th <V ใน <V ddเท่ากับอินพุตลอจิก 1 สำหรับอินเวอร์เตอร์

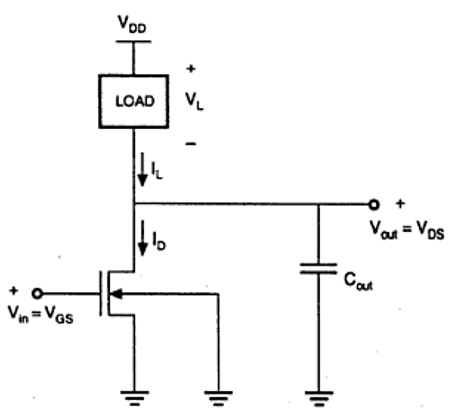

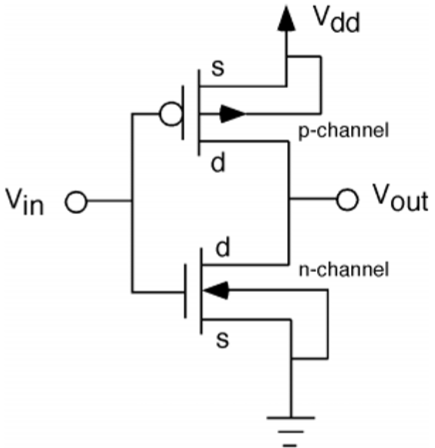

ลักษณะที่แสดงในรูปเหมาะอย่างยิ่ง โครงสร้างวงจรทั่วไปของอินเวอร์เตอร์ nMOS แสดงในรูปด้านล่าง

จากรูปที่กำหนดเราจะเห็นว่าแรงดันไฟฟ้าขาเข้าของอินเวอร์เตอร์เท่ากับแรงดันเกตไปยังต้นทางของทรานซิสเตอร์ nMOS และแรงดันขาออกของอินเวอร์เตอร์เท่ากับการระบายไปยังแรงดันต้นทางของทรานซิสเตอร์ nMOS แหล่งที่มาของแรงดันไฟฟ้าพื้นผิวของ nMOS เรียกอีกอย่างว่าไดรเวอร์สำหรับทรานซิสเตอร์ที่ต่อสายดิน ดังนั้น V SS = 0 โหนดเอาต์พุตเชื่อมต่อกับความจุแบบก้อนที่ใช้สำหรับ VTC

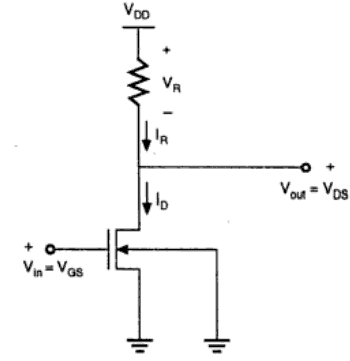

อินเวอร์เตอร์โหลดแบบ Resistive

โครงสร้างพื้นฐานของอินเวอร์เตอร์โหลดตัวต้านทานแสดงในรูปด้านล่าง ที่นี่ประเภทการเพิ่มประสิทธิภาพ nMOS ทำหน้าที่เป็นทรานซิสเตอร์ของไดรเวอร์ โหลดประกอบด้วยง่ายต้านทานเชิงเส้น R L แหล่งจ่ายไฟของวงจรคือ V DDและท่อระบายน้ำในปัจจุบันผมDเท่ากับภาระปัจจุบันฉันR

การทำงานของวงจร

เมื่ออินพุทของทรานซิสเตอร์ไดรเวอร์มีค่าน้อยกว่าแรงดันไฟฟ้า V TH (V ใน <V TH ) ทรานซิสเตอร์ของไดรเวอร์จะอยู่ในพื้นที่ตัดและไม่นำกระแสใด ๆ ดังนั้นแรงดันไฟฟ้าตกคร่อมตัวต้านทานโหลดเป็นศูนย์และแรงดันเอาท์พุทจะเท่ากับ V DD ตอนนี้เมื่อแรงดันไฟฟ้าขาเข้าเพิ่มขึ้นอีกทรานซิสเตอร์ของไดรเวอร์จะเริ่มทำกระแสที่ไม่เป็นศูนย์และ nMOS จะเข้าสู่บริเวณอิ่มตัว

ในทางคณิตศาสตร์

$$I_{D} = \frac{K_{n}}{2}\left [ V_{GS}-V_{TO} \right ]^{2}$$

การเพิ่มแรงดันไฟฟ้าขาเข้าให้มากขึ้นทรานซิสเตอร์ของไดรเวอร์จะเข้าสู่พื้นที่เชิงเส้นและเอาต์พุตของทรานซิสเตอร์ไดรเวอร์จะลดลง

$$I_{D} = \frac{K_{n}}{2}2\left [ V_{GS}-V_{TO} \right ]V_{DS}-V_{DS}^{2}$$

VTC ของอินเวอร์เตอร์โหลดตัวต้านทานที่แสดงด้านล่างแสดงโหมดการทำงานของทรานซิสเตอร์ไดรเวอร์และจุดแรงดันไฟฟ้า

อินเวอร์เตอร์พร้อมโหลด MOSFET ชนิด N

ข้อได้เปรียบหลักของการใช้ MOSFET เป็นอุปกรณ์โหลดคือพื้นที่ซิลิกอนที่ครอบครองโดยทรานซิสเตอร์มีขนาดเล็กกว่าพื้นที่ที่โหลดโดยตัวต้านทาน ที่นี่ MOSFET เป็นโหลดที่ใช้งานอยู่และอินเวอร์เตอร์ที่มีโหลดแบบแอคทีฟให้ประสิทธิภาพที่ดีกว่าอินเวอร์เตอร์ที่มีโหลดตัวต้านทาน

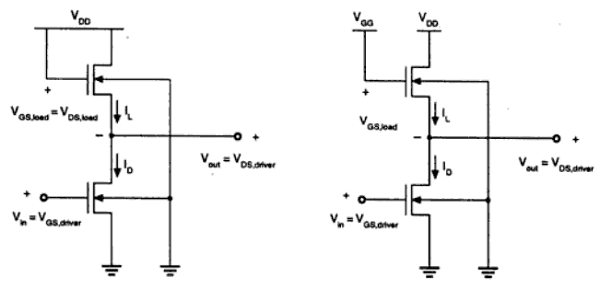

Enhancement Load NMOS

อินเวอร์เตอร์สองตัวพร้อมอุปกรณ์โหลดชนิดเสริมประสิทธิภาพแสดงในรูป โหลดทรานซิสเตอร์สามารถใช้งานได้ทั้งในบริเวณอิ่มตัวหรือในพื้นที่เชิงเส้นขึ้นอยู่กับแรงดันไบอัสที่ใช้กับเทอร์มินัลเกต อินเวอร์เตอร์โหลดการเพิ่มประสิทธิภาพอิ่มตัวแสดงในรูป (ก). มันต้องมีแรงดันไฟฟ้าเดียวและกระบวนการผลิตที่ง่ายและเพื่อให้ V OHถูก จำกัด V DD - V T

อินเวอร์เตอร์โหลดการเพิ่มประสิทธิภาพเชิงเส้นแสดงในรูป (ข). มันทำงานในพื้นที่เชิงเส้นเสมอ ดังนั้น V OHระดับเท่ากับ V DD

อินเวอร์เตอร์โหลดเชิงเส้นมีขอบเสียงที่สูงกว่าเมื่อเทียบกับอินเวอร์เตอร์ที่เพิ่มประสิทธิภาพอิ่มตัว แต่ข้อเสียของอินเวอร์เตอร์การเพิ่มประสิทธิภาพเชิงเส้นคือต้องใช้แหล่งจ่ายไฟสองตัวแยกกันและทั้งสองวงจรต้องทนทุกข์ทรมานจากการกระจายพลังงานสูง ดังนั้นจึงไม่มีการใช้อินเวอร์เตอร์สำหรับการเพิ่มประสิทธิภาพในแอปพลิเคชันดิจิทัลขนาดใหญ่ใด ๆ

โหลดพร่อง NMOS

ข้อเสียของอินเวอร์เตอร์โหลดการเพิ่มประสิทธิภาพสามารถเอาชนะได้โดยใช้อินเวอร์เตอร์โหลดพร่อง เมื่อเทียบกับอินเวอร์เตอร์ที่มีการเพิ่มประสิทธิภาพอินเวอร์เตอร์โหลดพร่องต้องใช้ขั้นตอนการผลิตเพิ่มขึ้นอีกสองสามขั้นสำหรับการฝังช่องสัญญาณเพื่อปรับแรงดันไฟฟ้าเกณฑ์ของโหลด

ข้อดีของอินเวอร์เตอร์โหลดพร่องคือ - การเปลี่ยน VTC ที่คมชัดขอบเสียงที่ดีขึ้นแหล่งจ่ายไฟเดี่ยวและพื้นที่รูปแบบโดยรวมที่เล็กลง

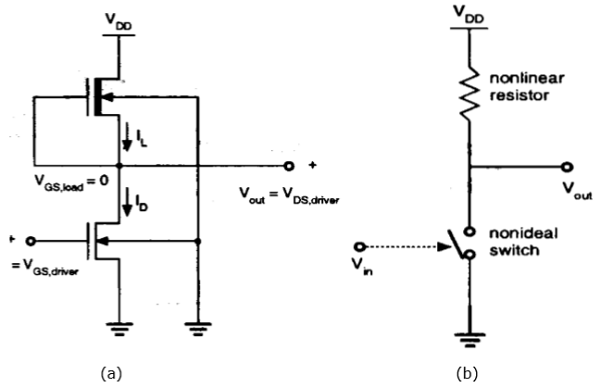

ดังแสดงในรูปเกตและเทอร์มินัลต้นทางของโหลดเชื่อมต่ออยู่ ดังนั้น V GS = 0 ดังนั้นแรงดันไฟฟ้าเกณฑ์ของโหลดจึงเป็นลบ ดังนั้น

$$V_{GS,load}> V_{T,load}$$ พอใจ

ดังนั้นอุปกรณ์โหลดจึงมีช่องการนำไฟฟ้าเสมอโดยไม่คำนึงถึงระดับแรงดันไฟฟ้าขาเข้าและขาออก

เมื่อทรานซิสเตอร์โหลดอยู่ในบริเวณอิ่มตัวกระแสโหลดจะถูกกำหนดโดย

$$I_{D,load} = \frac{K_{n,load}}{2}\left [ -V_{T,load}\left ( V_{out} \right ) \right ]^{2}$$

เมื่อทรานซิสเตอร์โหลดอยู่ในพื้นที่เชิงเส้นกระแสโหลดจะถูกกำหนดโดย

$$I_{D,load} = \frac{K_{n,load}}{2}\left [ 2\left | V_{T,load}\left ( V_{out} \right ) \right |.\left ( V_{DD}-V_{out} \right )-\left ( V_{DD}-V_{out} \right )^{2} \right ]$$

ลักษณะการถ่ายโอนแรงดันไฟฟ้าของอินเวอร์เตอร์โหลดพร่องแสดงในรูปด้านล่าง -

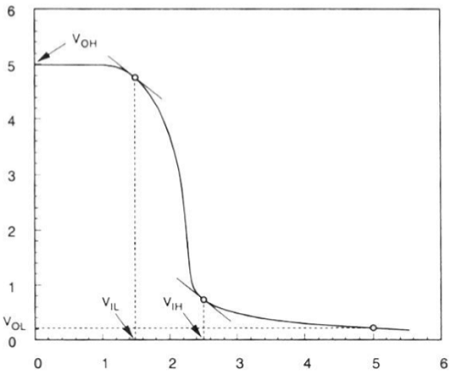

CMOS Inverter - วงจรการทำงานและคำอธิบาย

วงจรอินเวอร์เตอร์ CMOS แสดงดังรูป ที่นี่ทรานซิสเตอร์ nMOS และ pMOS ทำงานเป็นทรานซิสเตอร์ไดรเวอร์ เมื่อทรานซิสเตอร์ตัวหนึ่งเปิดอยู่อีกตัวหนึ่งปิด

การกำหนดค่านี้เรียกว่า complementary MOS (CMOS). อินพุตเชื่อมต่อกับเทอร์มินัลประตูของทรานซิสเตอร์ทั้งสองเพื่อให้ทั้งสองสามารถขับเคลื่อนโดยตรงด้วยแรงดันไฟฟ้าอินพุต พื้นผิวของ NMOS เชื่อมต่อกับพื้นดินและพื้นผิวของพีมอสที่เชื่อมต่อกับแหล่งจ่ายไฟ, V DD

ดังนั้น V SB = 0 สำหรับทรานซิสเตอร์ทั้งสองตัว

$$V_{GS,n}=V_{in}$$

$$V_{DS,n}=V_{out}$$

และ,

$$V_{GS,p}=V_{in}-V_{DD}$$

$$V_{DS,p}=V_{out}-V_{DD}$$

เมื่ออินพุตของ nMOS มีขนาดเล็กกว่าแรงดันไฟฟ้าเกณฑ์ (V ใน <V TO, n ) nMOS จะถูกตัดออกและ pMOS อยู่ในพื้นที่เชิงเส้น ดังนั้นกระแสระบายของทรานซิสเตอร์ทั้งสองจึงเป็นศูนย์

$$I_{D,n}=I_{D,p}=0$$

ดังนั้นแรงดันเอาต์พุต V OHจึงเท่ากับแรงดันไฟฟ้า

$$V_{out}=V_{OH}=V_{DD}$$

เมื่อแรงดันไฟฟ้าขาเข้ามากกว่า V DD + V TO, pทรานซิสเตอร์ pMOS อยู่ในพื้นที่ตัดและ nMOS อยู่ในพื้นที่เชิงเส้นดังนั้นกระแสระบายของทรานซิสเตอร์ทั้งสองจึงเป็นศูนย์

$$I_{D,n}=I_{D,p}=0$$

ดังนั้นแรงดันเอาต์พุต V OLจึงเท่ากับศูนย์

$$V_{out}=V_{OL}=0$$

nMOS ทำงานในพื้นที่อิ่มตัวถ้า V in > V TOและหากเป็นไปตามเงื่อนไขต่อไปนี้

$$V_{DS,n}\geq V_{GS,n}-V_{TO,n} $$

$$V_{out}\geq V_{in}-V_{TO,n} $$

pMOS ทำงานในพื้นที่อิ่มตัวถ้า V ใน <V DD + V TO, pและหากเป็นไปตามเงื่อนไขต่อไปนี้

$$V_{DS,p}\leq V_{GS,p}-V_{TO,p} $$

$$V_{out}\leq V_{in}-V_{TO,p} $$

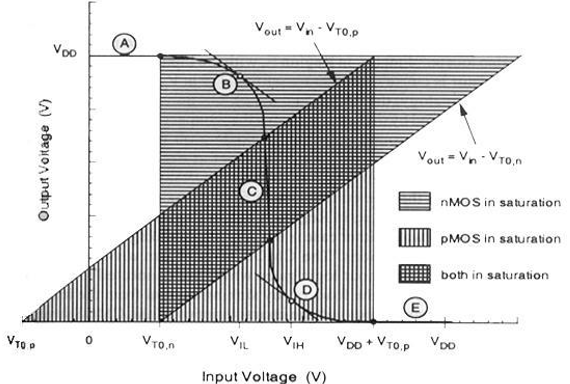

สำหรับค่าแรงดันไฟฟ้าอินพุตที่แตกต่างกันพื้นที่การทำงานจะแสดงรายการด้านล่างสำหรับทรานซิสเตอร์ทั้งสองตัว

| ภูมิภาค | V ใน | V ออก | nMOS | pMOS |

|---|---|---|---|---|

| ก | <V TO, n | V OH | ตัด - ปิด | เชิงเส้น |

| ข | V IL | สูง≈ V OH | ความอิ่มตัว | เชิงเส้น |

| ค | V th | V th | ความอิ่มตัว | ความอิ่มตัว |

| ง | V IH | ต่ำ≈ V OL | เชิงเส้น | ความอิ่มตัว |

| จ | > (V DD + V TO, p ) | V OL | เชิงเส้น | ตัด - ปิด |

VTC ของ CMOS แสดงในรูปด้านล่าง -

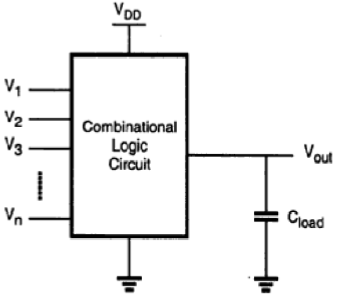

วงจรลอจิกเชิงผสมหรือเกตซึ่งดำเนินการบูลีนกับตัวแปรอินพุตหลายตัวและกำหนดเอาต์พุตเป็นฟังก์ชันบูลีนของอินพุตเป็นส่วนประกอบพื้นฐานของระบบดิจิทัลทั้งหมด เราจะตรวจสอบการกำหนดค่าวงจรอย่างง่ายเช่น NAND สองอินพุตและ NOR ประตูจากนั้นขยายการวิเคราะห์ของเราไปยังกรณีทั่วไปของโครงสร้างวงจรอินพุตหลายตัว

ต่อไปวงจรลอจิก CMOS จะถูกนำเสนอในรูปแบบที่คล้ายคลึงกัน เราจะเน้นย้ำถึงความเหมือนและความแตกต่างระหว่างลอจิกการลดลงของ nMOS และวงจรลอจิก CMOS และชี้ให้เห็นข้อดีของประตู CMOS พร้อมตัวอย่าง ในรูปแบบทั่วไปที่สุดวงจรลอจิกเชิงผสมหรือเกตที่ทำหน้าที่บูลีนสามารถแสดงเป็นระบบอินพุตหลายอินพุตเดียวตามที่แสดงในรูป

แรงดันไฟฟ้าของโหนดที่อ้างถึงศักย์กราวด์แสดงถึงตัวแปรอินพุตทั้งหมด การใช้หลักการตรรกะเชิงบวกค่าบูลีน (หรือลอจิก) ของ "1" สามารถแสดงด้วยแรงดันไฟฟ้าสูงของ VDD และค่าบูลีน (หรือตรรกะ) เป็น "0" สามารถแทนด้วยแรงดันไฟฟ้าต่ำที่ 0 เอาต์พุต โหนดถูกโหลดด้วยความจุ C Lซึ่งแสดงถึงความจุรวมของอุปกรณ์กาฝากในวงจร

วงจรลอจิก CMOS

CMOS สองอินพุต NOR Gate

วงจรประกอบด้วย n-net ที่เชื่อมต่อแบบขนานและ p-net ที่เชื่อมต่อแบบอนุกรม แรงดันไฟฟ้าอินพุต V Xและ V Yใช้กับประตูของหนึ่ง nMOS และทรานซิสเตอร์ pMOS หนึ่งตัว

เมื่ออินพุตหนึ่งหรือทั้งสองมีค่าสูงกล่าวคือเมื่อ n-net สร้างเส้นทางการนำไฟฟ้าระหว่างโหนดเอาต์พุตและกราวด์ p-net จะถูกตัด - ปิด หากแรงดันไฟฟ้าอินพุตทั้งสองต่ำกล่าวคือ n-net ถูกตัดออกดังนั้น p-net จะสร้างเส้นทางการนำไฟฟ้าระหว่างโหนดเอาต์พุตและแรงดันไฟฟ้า

สำหรับชุดอินพุตใด ๆ ที่กำหนดโครงสร้างวงจรเสริมคือเอาท์พุทเชื่อมต่อกับ V DDหรือต่อกราวด์ผ่านทางความต้านทานต่ำและไม่ได้กำหนดเส้นทางกระแส DC ระหว่าง V DDและกราวด์สำหรับชุดอินพุตใด ๆ แรงดันการส่งออกของ CMOS สองอินพุต NOR ประตูจะได้รับแรงดันไฟฟ้าตรรกะต่ำของ V OL = 0 และแรงดันไฟฟ้าตรรกะสูงของ V OH = V DD สมการของแรงดันไฟฟ้าสลับ V thกำหนดโดย

$$V_{th}\left ( NOR2 \right ) = \frac{V_{T,n}+\frac{1}{2}\sqrt{\frac{k_{p}}{k_{n}}\left ( V_{DD}-\left | V_{T,p} \right | \right )}}{1+\frac{1}{2}\sqrt{\frac{k_{p}}{k_{n}}}}$$

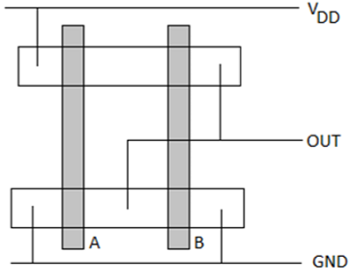

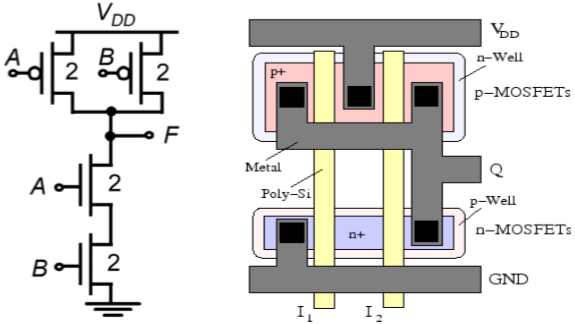

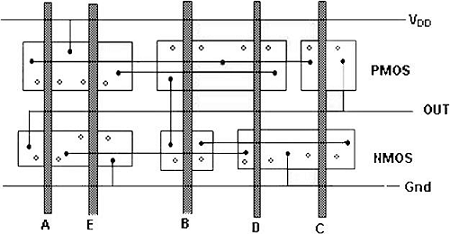

เค้าโครงของประตู NOR Gate 2 อินพุต CMOS

รูปแสดงเค้าโครงตัวอย่างของประตู NOR อินพุต CMOS 2 โดยใช้โลหะชั้นเดียวและโพลีซิลิคอนชั้นเดียว คุณสมบัติของเค้าโครงนี้คือ -

- โพลีลีนแนวตั้งเดี่ยวสำหรับแต่ละอินพุต

- รูปร่างที่ใช้งานเดี่ยวสำหรับอุปกรณ์ N และ P ตามลำดับ

- รถเมล์โลหะวิ่งในแนวนอน

แผนภาพแท่งสำหรับประตู CMOS N0R2 แสดงในรูปด้านล่าง ซึ่งสอดคล้องโดยตรงกับเค้าโครง แต่ไม่มีข้อมูล W และ L พื้นที่การแพร่กระจายจะแสดงเป็นรูปสี่เหลี่ยมการเชื่อมต่อของโลหะและเส้นทึบและวงกลมตามลำดับแสดงถึงหน้าสัมผัสและแถบกากบาทแทนคอลัมน์โพลีซิลิคอน Stick Diagram มีประโยชน์สำหรับการวางแผนโทโพโลยีโครงร่างที่เหมาะสมที่สุด

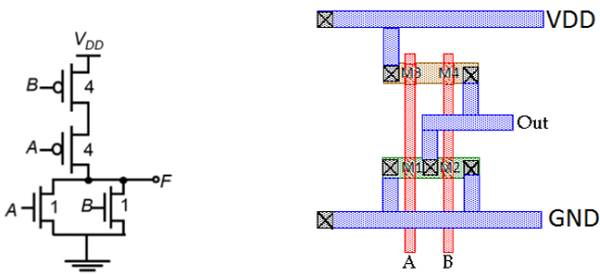

CMOS ประตู NAND สองอินพุต

แผนภาพวงจรของประตู CMOS NAND อินพุตสองตัวแสดงไว้ในรูปด้านล่าง

หลักการทำงานของวงจรเป็นแบบคู่ที่แน่นอนของการดำเนินการอินพุต NOR สอง CMOS n - net ประกอบด้วยทรานซิสเตอร์ nMOS ที่เชื่อมต่อสองชุดสร้างเส้นทางการนำไฟฟ้าระหว่างโหนดเอาต์พุตและกราวด์ถ้าแรงดันไฟฟ้าอินพุตทั้งสองมีลอจิกสูง ทรานซิสเตอร์ pMOS ที่เชื่อมต่อแบบขนานทั้งสองใน p-net จะดับลง

สำหรับชุดอินพุตอื่น ๆ ทั้งหมดทรานซิสเตอร์ pMOS ตัวใดตัวหนึ่งหรือทั้งสองตัวจะถูกเปิดในขณะที่ p - net ถูกตัดออกดังนั้นการสร้างเส้นทางปัจจุบันระหว่างโหนดเอาต์พุตและแรงดันไฟฟ้าของแหล่งจ่ายไฟ เกณฑ์การสลับสำหรับประตูนี้ได้รับเป็น -

$$V_{th}\left ( NAND2 \right ) = \frac{V_{T,n}+2\sqrt{\frac{k_{p}}{k_{n}}\left ( V_{DD}-\left | V_{T,p} \right | \right )}}{1+2\sqrt{\frac{k_{p}}{k_{n}}}}$$

คุณสมบัติของเค้าโครงนี้มีดังต่อไปนี้ -

- เส้นโพลีซิลิคอนเส้นเดียวสำหรับอินพุตจะทำงานในแนวตั้งทั้งบริเวณที่ใช้งาน N และ P

- รูปร่างที่ใช้งานเดี่ยวใช้สำหรับสร้างทั้งอุปกรณ์ nMOS และอุปกรณ์ pMOS ทั้งสอง

- Power bussing กำลังทำงานในแนวนอนที่ด้านบนและด้านล่างของเค้าโครง

- สายเอาท์พุตทำงานในแนวนอนเพื่อให้ง่ายต่อการเชื่อมต่อกับวงจรข้างเคียง

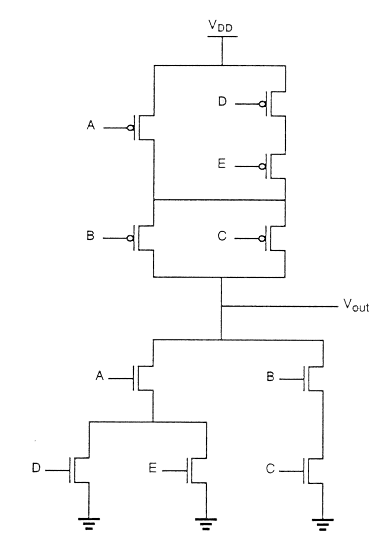

วงจรลอจิกที่ซับซ้อน

NMOS Depletion Load Complex Logic Gate

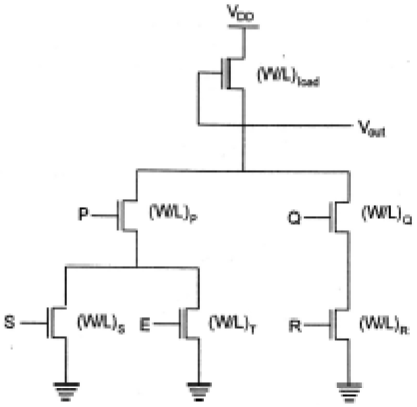

เพื่อให้ทราบถึงฟังก์ชันที่ซับซ้อนของตัวแปรอินพุตหลายตัวโครงสร้างวงจรพื้นฐานและหลักการออกแบบที่พัฒนาขึ้นสำหรับ NOR และ NAND สามารถขยายไปยังลอจิกเกตที่ซับซ้อนได้ ความสามารถในการรับรู้ฟังก์ชันลอจิกที่ซับซ้อนโดยใช้ทรานซิสเตอร์จำนวนน้อยเป็นหนึ่งในคุณสมบัติที่น่าสนใจที่สุดของวงจรลอจิก nMOS และ CMOS พิจารณาฟังก์ชันบูลีนต่อไปนี้เป็นตัวอย่าง

$$\overline{Z=P\left ( S+T \right )+QR}$$

ลอจิกเกตเชิงซ้อนที่โหลดพร่องของ nMOS ที่ใช้ในการรับรู้ฟังก์ชันนี้จะแสดงในรูป ในรูปนี้สาขาไดรเวอร์ nMOS ด้านซ้ายของทรานซิสเตอร์ไดรเวอร์สามตัวใช้เพื่อดำเนินการฟังก์ชันลอจิก P (S + T) ในขณะที่สาขาด้านขวามือทำหน้าที่ QR โดยการเชื่อมต่อสองสาขาแบบขนานและโดยการวางทรานซิสเตอร์โหลดระหว่างโหนดเอาต์พุตและแรงดันไฟฟ้าVDD,เราได้รับฟังก์ชันที่ซับซ้อนที่กำหนด ตัวแปรอินพุตแต่ละตัวถูกกำหนดให้กับไดรเวอร์เพียงตัวเดียว

การตรวจสอบโทโพโลยีของวงจรให้หลักการออกแบบที่เรียบง่ายของเครือข่ายแบบดึงลง -

- การดำเนินการหรือดำเนินการโดยไดรเวอร์ที่เชื่อมต่อแบบขนาน

- การดำเนินการ AND ดำเนินการโดยไดรเวอร์ที่เชื่อมต่อแบบอนุกรม

- การผกผันเกิดจากลักษณะของการทำงานของวงจร MOS

หากตัวแปรอินพุตทั้งหมดมีตรรกะสูงในวงจรที่ตระหนักถึงฟังก์ชันไดรเวอร์ที่เท่ากัน (W/L) อัตราส่วนของเครือข่ายแบบดึงลงที่ประกอบด้วยทรานซิสเตอร์ nMOS ห้าตัวคือ

$$\frac{W}{L}=\frac{1}{\frac{1}{\left ( W/L \right )Q}+\frac{1}{\left ( W/L \right )R}}+\frac{1}{\frac{1}{\left ( W/L \right )P}+\frac{1}{\left ( W/L \right )S+\left ( W/L \right )Q}}$$

คอมเพล็กซ์ CMOS Logic Gates

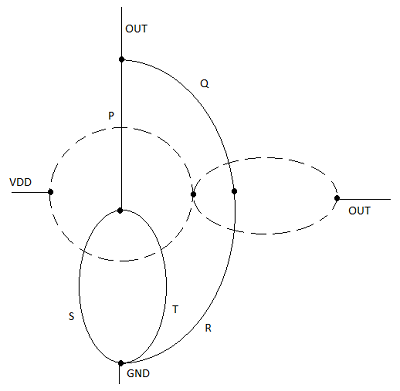

การรับรู้ของ n-net หรือเครือข่ายแบบดึงลงนั้นขึ้นอยู่กับหลักการออกแบบพื้นฐานเดียวกันกับที่ตรวจสอบสำหรับประตูลอจิกเชิงซ้อนที่โหลด nMOS เครือข่ายพูลอัพ pMOS ต้องเป็นเครือข่ายคู่ของ n-net

หมายความว่าการเชื่อมต่อแบบขนานทั้งหมดในเครือข่าย nMOS จะสอดคล้องกับการเชื่อมต่อแบบอนุกรมในเครือข่าย pMOS และการเชื่อมต่อแบบอนุกรมทั้งหมดในเครือข่าย nMOS จะสอดคล้องกับการเชื่อมต่อแบบขนานในเครือข่าย pMOS รูปแสดงโครงสร้างอย่างง่ายของกราฟคู่ p-net (แบบดึงขึ้น) จากกราฟ n-net (แบบดึงลง)

ทรานซิสเตอร์ไดรเวอร์แต่ละตัวในเครือข่ายแบบดึงลงจะแสดงด้วย ai และแต่ละโหนดจะแสดงด้วยจุดยอดในกราฟแบบดึงลง จากนั้นจุดยอดใหม่จะถูกสร้างขึ้นภายในพื้นที่ จำกัด แต่ละจุดในกราฟดึงและจุดยอดใกล้เคียงจะเชื่อมต่อกันด้วยขอบซึ่งข้ามขอบแต่ละด้านในกราฟแบบดึงลงเพียงครั้งเดียว กราฟใหม่นี้แสดงเครือข่ายแบบดึงขึ้น

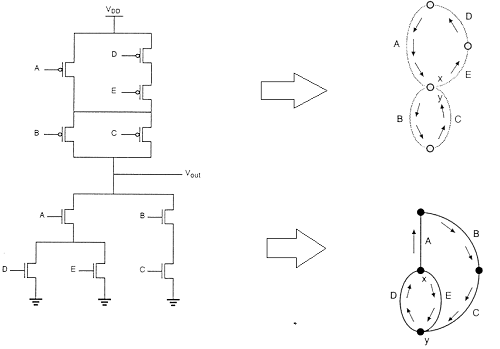

เทคนิคการจัดวางโดยใช้วิธีออยเลอร์กราฟ

ภาพแสดงการใช้งาน CMOS ของฟังก์ชันที่ซับซ้อนและแผนภาพแท่งที่ทำด้วยการสั่งซื้อประตูโดยพลการซึ่งให้รูปแบบที่ไม่เหมาะสมอย่างยิ่งสำหรับประตู CMOS

ในกรณีนี้การแยกระหว่างคอลัมน์โพลีซิลิคอนจะต้องอนุญาตให้มีการแยกการแพร่กระจายไปยังการแพร่กระจายระหว่างกัน สิ่งนี้ใช้พื้นที่ซิลิคอนเป็นจำนวนมากอย่างแน่นอน

ด้วยการใช้เส้นทางออยเลอร์เราจะได้รูปแบบที่เหมาะสมที่สุด เส้นทางออยเลอร์ถูกกำหนดให้เป็นเส้นทางที่ไม่ขาดตอนซึ่งจะลัดเลาะไปตามขอบแต่ละด้าน (กิ่งก้าน) ของกราฟเพียงครั้งเดียว ค้นหาเส้นทางออยเลอร์ทั้งในกราฟต้นไม้แบบดึงลงและกราฟต้นไม้แบบดึงขึ้นโดยมีลำดับอินพุตที่เหมือนกัน

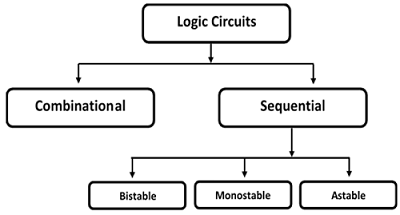

วงจรลอจิกแบ่งออกเป็นสองประเภท - (a) วงจรผสมและ (b) วงจรลำดับ

ในวงจร Combinational เอาต์พุตจะขึ้นอยู่กับเงื่อนไขของอินพุตล่าสุดเท่านั้น

ในวงจรซีเควนเชียลเอาต์พุตไม่เพียงขึ้นอยู่กับอินพุตล่าสุดเท่านั้น แต่ยังขึ้นอยู่กับเงื่อนไขของอินพุตก่อนหน้านี้ด้วย วงจรลำดับประกอบด้วยองค์ประกอบหน่วยความจำ

วงจรลำดับมีสามประเภท -

Bistable- วงจร Bistable มีจุดปฏิบัติการที่มั่นคงสองจุดและจะอยู่ในสถานะใดสถานะหนึ่ง ตัวอย่าง - เซลล์หน่วยความจำสลักฟลิปฟล็อปและรีจิสเตอร์

Monostable- วงจรโมโนสเตเบิลมีจุดปฏิบัติการที่เสถียรเพียงจุดเดียวและแม้ว่าจะถูกรบกวนชั่วคราวไปยังสถานะตรงกันข้าม แต่ก็จะกลับไปยังจุดปฏิบัติการที่เสถียร ตัวอย่าง: ตัวจับเวลาเครื่องกำเนิดพัลส์

Astable- วงจรไม่มีจุดปฏิบัติการที่มั่นคงและสั่นระหว่างหลายสถานะ ตัวอย่าง - Ring oscillator

วงจรลอจิก CMOS

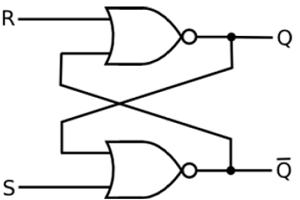

SR Latch ขึ้นอยู่กับ NOR Gate

ถ้าอินพุตที่ตั้งไว้ (S) เท่ากับลอจิก "1" และอินพุตรีเซ็ตเท่ากับลอจิก "0." จากนั้นเอาต์พุต Q จะถูกบังคับให้ใช้ตรรกะ "1". ในขณะที่$\overline{Q}$ ถูกบังคับให้ใช้ตรรกะ "0". ซึ่งหมายความว่าสลัก SR จะถูกตั้งค่าโดยไม่คำนึงถึงสถานะก่อนหน้า

ในทำนองเดียวกันถ้า S เท่ากับ "0" และ R เท่ากับ "1" จากนั้นเอาต์พุต Q จะถูกบังคับให้ "0" ในขณะที่ $\overline{Q}$ ถูกบังคับให้ "1". ซึ่งหมายความว่าสลักจะถูกรีเซ็ตโดยไม่คำนึงถึงสถานะที่ยึดไว้ก่อนหน้านี้ สุดท้ายหากอินพุตทั้งสอง S และ R เท่ากับลอจิก"1" จากนั้นเอาต์พุตทั้งสองจะถูกบังคับให้ใช้ตรรกะ "0" ซึ่งขัดแย้งกับความสมบูรณ์ของ Q และ $\overline{Q}$.

ดังนั้นจึงไม่อนุญาตให้ใช้ชุดอินพุตนี้ในระหว่างการทำงานปกติ ตารางความจริงของ SR Latch ตาม NOR แสดงไว้ในตาราง

| ส | ร | ถาม | $\overline{Q}$ | การดำเนินการ |

|---|---|---|---|---|

| 0 | 0 | ถาม | $\overline{Q}$ | ถือ |

| 1 | 0 | 1 | 0 | ชุด |

| 0 | 1 | 0 | 1 | รีเซ็ต |

| 1 | 1 | 0 | 0 | ไม่ได้รับอนุญาต |

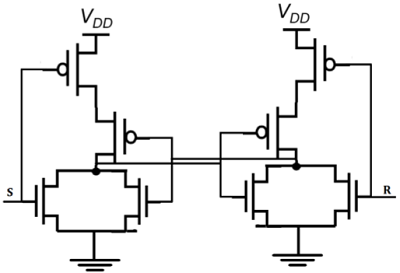

สลัก CMOS SR ที่ยึดตามประตู NOR แสดงในรูปด้านล่าง

ถ้า S เท่ากับ V OHและ R เท่ากับ V OLทรานซิสเตอร์ที่เชื่อมต่อแบบขนาน M1 และ M2 ทั้งสองจะเปิดอยู่ แรงดันไฟฟ้าบนโหนด$\overline{Q}$จะถือว่าระดับตรรกะต่ำของ V OL = 0

ในเวลาเดียวกันทั้ง M3 และ M4 ถูกปิดซึ่งจะส่งผลให้แรงดันไฟฟ้าตรรกะสูง V OHที่โหนด Q. ถ้า R เท่ากับ V OHและ S มีค่าเท่ากับ V OL , M1 และ M2 ปิดและ M3 และ M4 เปิดอยู่

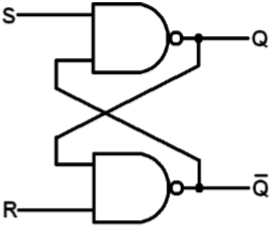

SR Latch ขึ้นอยู่กับ NAND Gate

แผนภาพบล็อกและแผนผังระดับประตูของสลัก SR ที่ใช้ NAND แสดงไว้ในรูป วงกลมเล็ก ๆ ที่ขั้วอินพุต S และ R แสดงว่าวงจรตอบสนองต่อสัญญาณอินพุตต่ำที่ใช้งานอยู่ ตารางความจริงของสลัก SR ที่ใช้ NAND แสดงไว้ในตาราง

| ส | ร | ถาม | Q ′ | |

| 0 | 0 | NC | NC | ไม่มีการเปลี่ยนแปลง. สลักยังคงอยู่ในสถานะปัจจุบัน |

| 1 | 0 | 1 | 0 | ชุดสลัก |

| 0 | 1 | 0 | 1 | รีเซ็ตสลัก |

| 1 | 1 | 0 | 0 | เงื่อนไขไม่ถูกต้อง |

ถ้า S ไปที่ 0 (ในขณะที่ R = 1) Q จะสูงและดึง $\overline{Q}$ ต่ำและสลักเข้าสู่สถานะตั้งค่า

S = 0 แล้ว Q = 1 (ถ้า R = 1)

ถ้า R ไปที่ 0 (ในขณะที่ S = 1) Q จะสูงดึง $\overline{Q}$ ต่ำและสลักถูกรีเซ็ต

R = 0 แล้ว Q = 1 (ถ้า S = 1)

สถานะการระงับต้องการให้ทั้ง S และ R สูง ถ้า S = R = 0 แสดงว่าเอาต์พุตไม่ได้รับอนุญาตเนื่องจากจะส่งผลให้อยู่ในสถานะที่ไม่แน่นอน CMOS SR Latch ตาม NAND Gate แสดงดังรูป

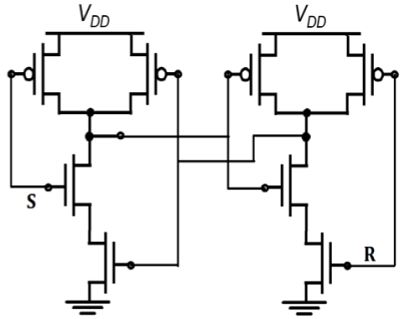

Depletion-load nMOS SR Latch ตาม NAND Gate แสดงในรูป การทำงานคล้ายกับสลัก CMOS NAND SR การใช้งานวงจร CMOS มีการกระจายพลังงานคงที่ต่ำและมีอัตราสัญญาณรบกวนสูง

วงจรลอจิก CMOS

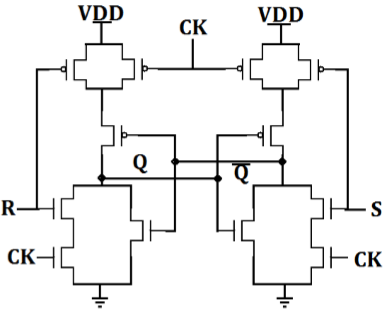

สลัก SR แบบนาฬิกา

รูปแสดงสลัก SR ที่ใช้ NOR พร้อมกับนาฬิกาที่เพิ่มเข้ามา สลักตอบสนองต่ออินพุต S และ R เฉพาะเมื่อ CLK สูง

เมื่อ CLK ต่ำสลักจะยังคงอยู่ในสถานะปัจจุบัน สังเกตว่า Q เปลี่ยนสถานะ -

- เมื่อ S ไปสูงระหว่าง CLK ที่เป็นบวก

- บนขอบ CLK ชั้นนำหลังจากการเปลี่ยนแปลงใน S & R ในช่วงเวลาที่ต่ำของ CLK

- ความผิดพลาดในเชิงบวกใน S ขณะที่ CLK สูง

- เมื่อ R ไปสูงระหว่าง CLK ที่เป็นบวก

การใช้งาน CMOS AOI ของสลัก SR แบบโอเวอร์คล็อกแบบ NOR แสดงในรูป โปรดทราบว่าต้องใช้ทรานซิสเตอร์เพียง 12 ตัว

เมื่อ CLK อยู่ในระดับต่ำเทอร์มินัลสองชุดใน N ทรี N จะเปิดและทรานซิสเตอร์แบบขนานสองตัวในทรี P เปิดอยู่ดังนั้นจึงคงสถานะไว้ในเซลล์หน่วยความจำ

เมื่อสัญญาณนาฬิกาสูงวงจรจะกลายเป็นเพียงสลัก CMOS ที่ใช้ NOR ซึ่งจะตอบสนองต่ออินพุต S และ R

Clocked SR Latch based on NAND Gate

วงจรใช้กับประตู NAND สี่ประตู หากใช้วงจรนี้กับ CMOS ก็ต้องใช้ทรานซิสเตอร์ 16 ตัว

- สลักตอบสนองต่อ S หรือ R เฉพาะในกรณีที่ CLK สูง

- หากสัญญาณอินพุตทั้งสองและสัญญาณ CLK แอ็คทีฟสูงนั่นคือเอาต์พุตสลัก Q จะถูกตั้งค่าเมื่อ CLK = "1" S = "1" และ R = "0"

- ในทำนองเดียวกันสลักจะถูกรีเซ็ตเมื่อ CLK = "1," S = "0," และ

เมื่อ CLK ต่ำสลักจะยังคงอยู่ในสถานะปัจจุบัน

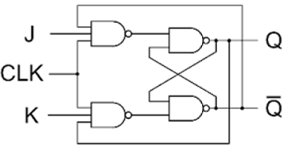

นาฬิกา JK Latch

รูปด้านบนแสดงสลัก JK แบบโอเวอร์คล็อกตามประตู NAND ข้อเสียของสลัก SR คือเมื่อทั้ง S และ R สูงสถานะเอาต์พุตจะไม่แน่นอน สลัก JK ช่วยขจัดปัญหานี้โดยใช้การป้อนกลับจากเอาต์พุตไปยังอินพุตเพื่อให้สามารถใช้สถานะอินพุตทั้งหมดของตารางความจริงได้ ถ้า J = K = 0 สลักจะคงสถานะปัจจุบันไว้

ถ้า J = 1 และ K = 0 สลักจะตั้งอยู่บนขอบนาฬิกาที่เป็นบวกถัดไปเช่น Q = 1 $\overline{Q}$ = 0

ถ้า J = 0 และ K = 1 สลักจะรีเซ็ตบนขอบนาฬิกาที่เป็นบวกถัดไปนั่นคือ Q = 1 และ $\overline{Q}$ = 0.

ถ้า J = K = 1 สลักจะสลับไปที่ขอบนาฬิกาที่เป็นบวกถัดไป

การทำงานของสลัก JK แบบตอกบัตรสรุปไว้ในตารางความจริงที่ระบุไว้ในตาราง

J |

K |

Q |

$\overline{Q}$ | S |

R |

Q |

$\overline{Q}$ | Operation |

| 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | ถือ |

| 1 | 0 | 1 | 1 | 1 | 0 | |||

| 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | รีเซ็ต |

| 1 | 0 | 1 | 0 | 0 | 1 | |||

| 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | ชุด |

| 1 | 0 | 1 | 1 | 1 | 0 | |||

| 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | สลับ |

| 1 | 0 | 1 | 0 | 0 | 1 |

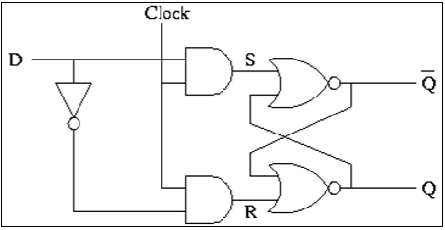

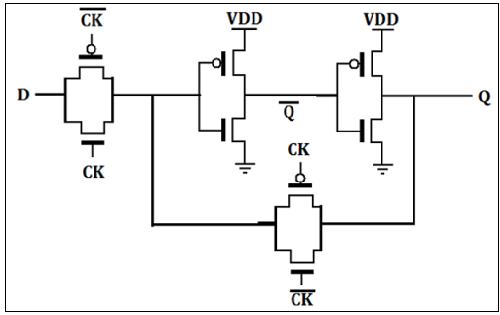

การติดตั้ง CMOS D Latch

โดยปกติสลัก D จะใช้งานร่วมกับสวิตช์ Transmission Gate (TG) ดังแสดงในรูป อินพุต TG เปิดใช้งานด้วย CLK ในขณะที่ลูปป้อนกลับสลัก TG เปิดใช้งานด้วย CLK อินพุต D ได้รับการยอมรับเมื่อ CLK สูง เมื่อ CLK ลดลงอินพุตจะถูกเปิดและสลักถูกตั้งค่าด้วยข้อมูลก่อนหน้า D

VHDL ย่อมาจากภาษาอธิบายฮาร์ดแวร์วงจรรวมความเร็วสูงมาก เป็นภาษาโปรแกรมที่ใช้ในการสร้างแบบจำลองระบบดิจิทัลโดยกระแสข้อมูลรูปแบบพฤติกรรมและโครงสร้างของการสร้างแบบจำลอง ภาษานี้เปิดตัวครั้งแรกในปี 1981 สำหรับกระทรวงกลาโหม (DoD) ภายใต้โครงการ VHSIC

อธิบายการออกแบบ

ใน VHDL เอนทิตีถูกใช้เพื่ออธิบายโมดูลฮาร์ดแวร์ สามารถอธิบายเอนทิตีได้โดยใช้

- การประกาศเอนทิตี

- Architecture

- Configuration

- การประกาศแพ็กเกจ

- ตัวบรรจุภัณฑ์

มาดูกันว่ามีอะไรบ้าง?

การประกาศเอนทิตี

กำหนดชื่อสัญญาณอินพุตเอาต์พุตและโหมดของโมดูลฮาร์ดแวร์

Syntax -

entity entity_name is

Port declaration;

end entity_name;การประกาศเอนทิตีควรเริ่มต้นด้วย "เอนทิตี" และลงท้ายด้วยคีย์เวิร์ด "end" ทิศทางจะเป็นอินพุตเอาต์พุตหรืออินพุต

| ใน | พอร์ตสามารถอ่านได้ |

| ออก | สามารถเขียนพอร์ตได้ |

| Inout | พอร์ตสามารถอ่านและเขียนได้ |

| กันชน | พอร์ตสามารถอ่านและเขียนได้เพียงแหล่งเดียว |

Architecture -

สถาปัตยกรรมสามารถอธิบายได้โดยใช้รูปแบบโครงสร้างกระแสข้อมูลพฤติกรรมหรือแบบผสม

Syntax -

architecture architecture_name of entity_name

architecture_declarative_part;

begin

Statements;

end architecture_name;ที่นี่เราควรระบุชื่อเอนทิตีที่เรากำลังเขียนเนื้อหาสถาปัตยกรรม คำสั่งสถาปัตยกรรมควรอยู่ในคีย์เวิร์ด "begin" และ "énd" ส่วนที่ประกาศสถาปัตยกรรมอาจมีตัวแปรค่าคงที่หรือการประกาศส่วนประกอบ

การสร้างแบบจำลองกระแสข้อมูล

ในรูปแบบการสร้างแบบจำลองนี้การไหลของข้อมูลผ่านเอนทิตีจะแสดงโดยใช้สัญญาณพร้อมกัน (ขนาน) คำสั่งพร้อมกันใน VHDL คือ WHEN และ GENERATE

นอกจากนี้ยังสามารถใช้การกำหนดโดยใช้ตัวดำเนินการเท่านั้น (AND, NOT, +, *, sll และอื่น ๆ ) เพื่อสร้างโค้ด

สุดท้ายการมอบหมายแบบพิเศษที่เรียกว่า BLOCK สามารถใช้ในรหัสประเภทนี้ได้เช่นกัน

ในรหัสพร้อมกันสามารถใช้สิ่งต่อไปนี้ได้ -

- Operators

- คำสั่ง WHEN (WHEN / ELSE หรือ WITH / SELECT / WHEN);

- สร้างคำสั่ง;

- คำสั่ง BLOCK

การสร้างแบบจำลองพฤติกรรม

ในรูปแบบการสร้างแบบจำลองนี้ลักษณะการทำงานของเอนทิตีเป็นชุดคำสั่งจะดำเนินการตามลำดับตามลำดับที่ระบุ เฉพาะข้อความที่อยู่ใน PROCESS, FUNCTION หรือ PROCEDURE เท่านั้นที่เป็นลำดับ

กระบวนการฟังก์ชันและกระบวนการเป็นส่วนเดียวของโค้ดที่ดำเนินการตามลำดับ

อย่างไรก็ตามโดยรวมแล้วบล็อกใด ๆ เหล่านี้ยังคงเกิดขึ้นพร้อมกับข้อความอื่น ๆ ที่วางไว้ภายนอก

สิ่งสำคัญอย่างหนึ่งของรหัสพฤติกรรมคือไม่ จำกัด เฉพาะตรรกะแบบลำดับ อันที่จริงด้วยมันเราสามารถสร้างวงจรต่อเนื่องและวงจรรวมได้

คำสั่งลักษณะการทำงานคือ IF, WAIT, CASE และ LOOP นอกจากนี้ VARIABLES ยังถูก จำกัด และควรใช้ในรหัสต่อเนื่องเท่านั้น VARIABLE ไม่สามารถเป็น global ได้ดังนั้นจึงไม่สามารถส่งผ่านค่าได้โดยตรง

การสร้างแบบจำลองโครงสร้าง

ในการสร้างแบบจำลองนี้เอนทิตีถูกอธิบายว่าเป็นชุดของส่วนประกอบที่เชื่อมต่อกัน คำสั่งสร้างอินสแตนซ์คอมโพเนนต์เป็นคำสั่งที่เกิดขึ้นพร้อมกัน ดังนั้นลำดับของแถลงการณ์เหล่านี้จึงไม่สำคัญ รูปแบบโครงสร้างของการสร้างแบบจำลองอธิบายเฉพาะการเชื่อมต่อโครงข่ายของส่วนประกอบ (ดูเป็นกล่องดำ) โดยไม่ได้หมายความถึงพฤติกรรมใด ๆ ของส่วนประกอบเองหรือของเอนทิตีที่รวมกัน

ในการสร้างแบบจำลองโครงสร้างเนื้อหาของสถาปัตยกรรมประกอบด้วยสองส่วนคือส่วนที่ประกาศ (ก่อนที่คีย์เวิร์ดจะเริ่ม) และส่วนของคำสั่ง (หลังจากคีย์เวิร์ดเริ่มต้น)

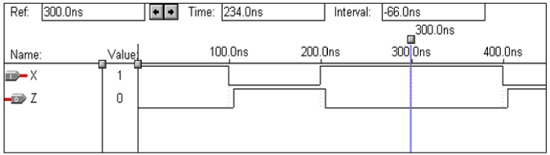

การดำเนินการลอจิก - และประตู

| X | ย | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity and1 is

port(x,y:in bit ; z:out bit);

end and1;

architecture virat of and1 is

begin

z<=x and y;

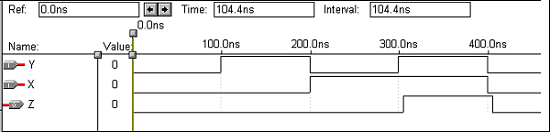

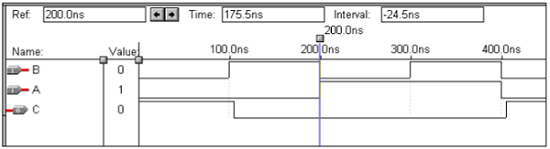

end virat;รูปคลื่น

Logic Operation - หรือ Gate

| X | ย | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity or1 is

port(x,y:in bit ; z:out bit);

end or1;

architecture virat of or1 is

begin

z<=x or y;

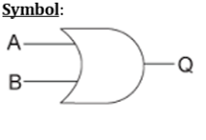

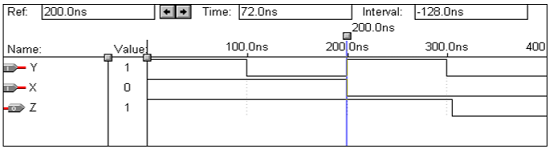

end virat;รูปคลื่น

การดำเนินการลอจิก - ไม่ใช่ประตู

| X | ย |

|---|---|

| 0 | 1 |

| 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity not1 is

port(x:in bit ; y:out bit);

end not1;

architecture virat of not1 is

begin

y<=not x;

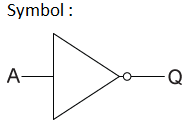

end virat;รูปคลื่น

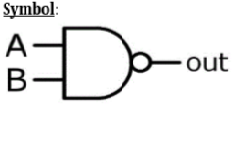

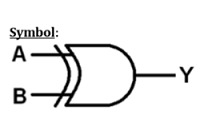

Logic Operation - NAND Gate

| X | ย | z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity nand1 is

port(a,b:in bit ; c:out bit);

end nand1;

architecture virat of nand1 is

begin

c<=a nand b;

end virat;รูปคลื่น

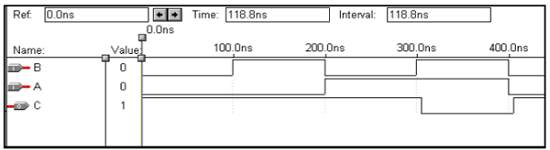

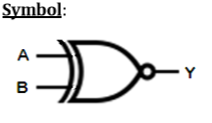

Logic Operation - NOR Gate

| X | ย | z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity nor1 is

port(a,b:in bit ; c:out bit);

end nor1;

architecture virat of nor1 is

begin

c<=a nor b;

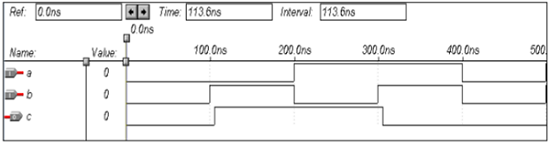

end virat;รูปคลื่น

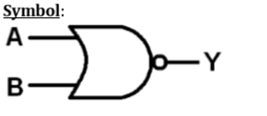

Logic Operation - XOR Gate

| X | ย | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity xor1 is

port(a,b:in bit ; c:out bit);

end xor1;

architecture virat of xor1 is

begin

c<=a xor b;

end virat;รูปคลื่น

การทำงานลอจิก - ประตู X-NOR

| X | ย | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity xnor1 is

port(a,b:in bit ; c:out bit);

end xnor1;

architecture virat of xnor1 is

begin

c<=not(a xor b);

end virat;รูปคลื่น

บทนี้จะอธิบายถึงการเขียนโปรแกรม VHDL สำหรับ Combinational Circuits

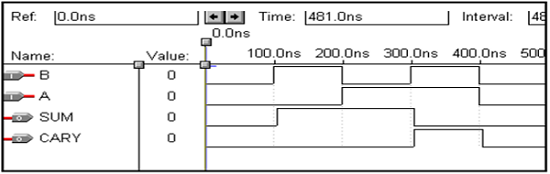

รหัส VHDL สำหรับ Half-Adder

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity half_adder is

port(a,b:in bit; sum,carry:out bit);

end half_adder;

architecture data of half_adder is

begin

sum<= a xor b;

carry <= a and b;

end data;รูปคลื่น

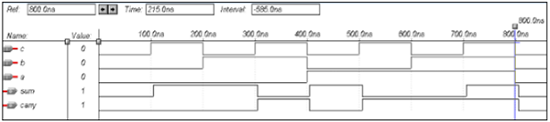

รหัส VHDL สำหรับ Adder แบบเต็ม

Library ieee;

use ieee.std_logic_1164.all;

entity full_adder is port(a,b,c:in bit; sum,carry:out bit);

end full_adder;

architecture data of full_adder is

begin

sum<= a xor b xor c;

carry <= ((a and b) or (b and c) or (a and c));

end data;รูปคลื่น

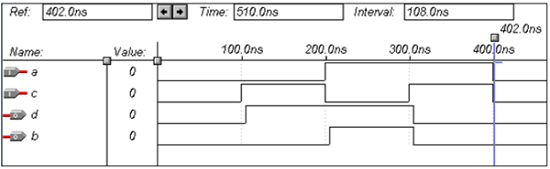

รหัส VHDL สำหรับตัวลบครึ่งหนึ่ง

Library ieee;

use ieee.std_logic_1164.all;

entity half_sub is

port(a,c:in bit; d,b:out bit);

end half_sub;

architecture data of half_sub is

begin

d<= a xor c;

b<= (a and (not c));

end data;รูปคลื่น

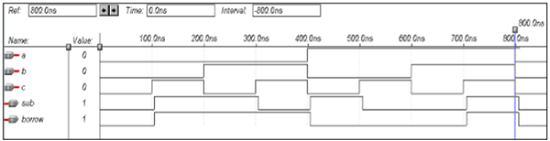

รหัส VHDL สำหรับตัวลบแบบเต็ม

Library ieee;

use ieee.std_logic_1164.all;

entity full_sub is

port(a,b,c:in bit; sub,borrow:out bit);

end full_sub;

architecture data of full_sub is

begin

sub<= a xor b xor c;

borrow <= ((b xor c) and (not a)) or (b and c);

end data;รูปคลื่น

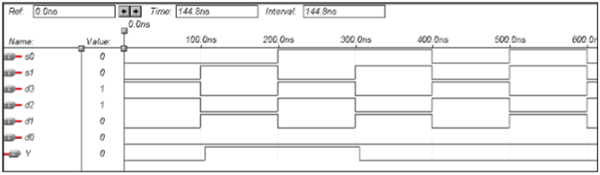

รหัส VHDL สำหรับ Multiplexer

Library ieee;

use ieee.std_logic_1164.all;

entity mux is

port(S1,S0,D0,D1,D2,D3:in bit; Y:out bit);

end mux;

architecture data of mux is

begin

Y<= (not S0 and not S1 and D0) or

(S0 and not S1 and D1) or

(not S0 and S1 and D2) or

(S0 and S1 and D3);

end data;รูปคลื่น

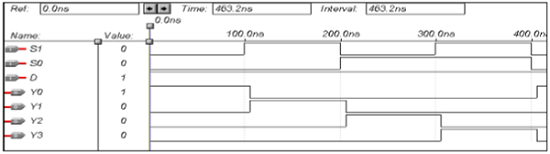

รหัส VHDL สำหรับ Demultiplexer

Library ieee;

use ieee.std_logic_1164.all;

entity demux is

port(S1,S0,D:in bit; Y0,Y1,Y2,Y3:out bit);

end demux;

architecture data of demux is

begin

Y0<= ((Not S0) and (Not S1) and D);

Y1<= ((Not S0) and S1 and D);

Y2<= (S0 and (Not S1) and D);

Y3<= (S0 and S1 and D);

end data;รูปคลื่น

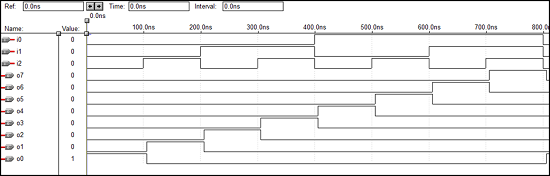

รหัส VHDL สำหรับตัวเข้ารหัส 8 x 3

library ieee;

use ieee.std_logic_1164.all;

entity enc is

port(i0,i1,i2,i3,i4,i5,i6,i7:in bit; o0,o1,o2: out bit);

end enc;

architecture vcgandhi of enc is

begin

o0<=i4 or i5 or i6 or i7;

o1<=i2 or i3 or i6 or i7;

o2<=i1 or i3 or i5 or i7;

end vcgandhi;รูปคลื่น

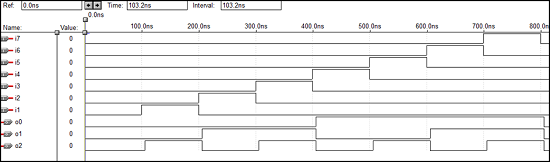

รหัส VHDL สำหรับตัวถอดรหัส 3 x 8

library ieee;

use ieee.std_logic_1164.all;

entity dec is

port(i0,i1,i2:in bit; o0,o1,o2,o3,o4,o5,o6,o7: out bit);

end dec;

architecture vcgandhi of dec is

begin

o0<=(not i0) and (not i1) and (not i2);

o1<=(not i0) and (not i1) and i2;

o2<=(not i0) and i1 and (not i2);

o3<=(not i0) and i1 and i2;

o4<=i0 and (not i1) and (not i2);

o5<=i0 and (not i1) and i2;

o6<=i0 and i1 and (not i2);

o7<=i0 and i1 and i2;

end vcgandhi;รูปคลื่น

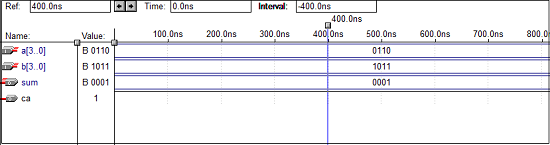

รหัส VHDL - แอดเดอร์ขนาน 4 บิต

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity pa is

port(a : in STD_LOGIC_VECTOR(3 downto 0);

b : in STD_LOGIC_VECTOR(3 downto 0);

ca : out STD_LOGIC;

sum : out STD_LOGIC_VECTOR(3 downto 0)

);

end pa;

architecture vcgandhi of pa is

Component fa is

port (a : in STD_LOGIC;

b : in STD_LOGIC;

c : in STD_LOGIC;

sum : out STD_LOGIC;

ca : out STD_LOGIC

);

end component;

signal s : std_logic_vector (2 downto 0);

signal temp: std_logic;

begin

temp<='0';

u0 : fa port map (a(0),b(0),temp,sum(0),s(0));

u1 : fa port map (a(1),b(1),s(0),sum(1),s(1));

u2 : fa port map (a(2),b(2),s(1),sum(2),s(2));

ue : fa port map (a(3),b(3),s(2),sum(3),ca);

end vcgandhi;รูปคลื่น

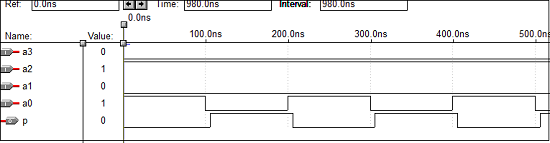

รหัส VHDL - ตัวตรวจสอบความเท่าเทียมกัน 4 บิต

library ieee;

use ieee.std_logic_1164.all;

entity parity_checker is

port (a0,a1,a2,a3 : in std_logic;

p : out std_logic);

end parity_checker;

architecture vcgandhi of parity_checker is

begin

p <= (((a0 xor a1) xor a2) xor a3);

end vcgandhi;รูปคลื่น

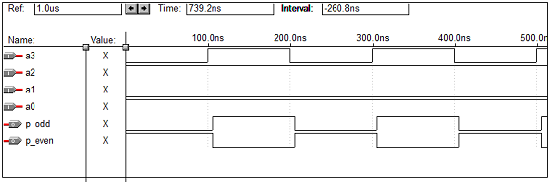

รหัส VHDL - ตัวสร้าง Parity 4 บิต

library ieee;

use ieee.std_logic_1164.all;

entity paritygen is

port (a0, a1, a2, a3: in std_logic; p_odd, p_even: out std_logic);

end paritygen;

architecture vcgandhi of paritygen is

begin

process (a0, a1, a2, a3)

if (a0 ='0' and a1 ='0' and a2 ='0' and a3 =’0’)

then odd_out <= "0";

even_out <= "0";

else

p_odd <= (((a0 xor a1) xor a2) xor a3);

p_even <= not(((a0 xor a1) xor a2) xor a3);

end vcgandhiรูปคลื่น

บทนี้อธิบายวิธีการเขียนโปรแกรม VHDL สำหรับวงจรลำดับ

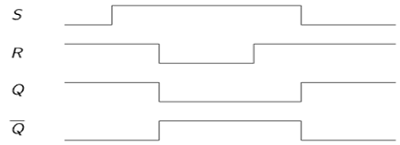

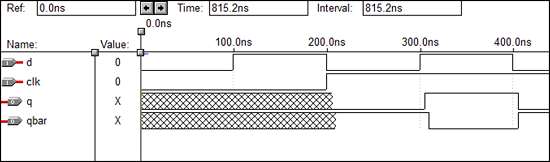

รหัส VHDL สำหรับ SR Latch

library ieee;

use ieee.std_logic_1164.all;

entity srl is

port(r,s:in bit; q,qbar:buffer bit);

end srl;

architecture virat of srl is

signal s1,r1:bit;

begin

q<= s nand qbar;

qbar<= r nand q;

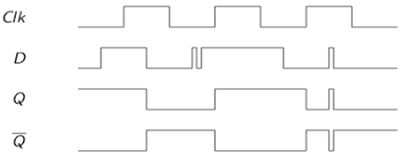

end virat;รูปคลื่น

รหัส VHDL สำหรับ D Latch

library ieee;

use ieee.std_logic_1164.all;

entity Dl is

port(d:in bit; q,qbar:buffer bit);

end Dl;

architecture virat of Dl is

signal s1,r1:bit;

begin

q<= d nand qbar;

qbar<= d nand q;

end virat;รูปคลื่น

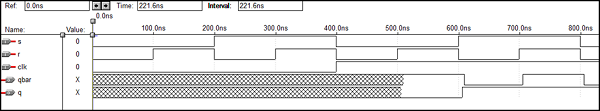

รหัส VHDL สำหรับ SR Flip Flop

library ieee;

use ieee.std_logic_1164.all;

entity srflip is

port(r,s,clk:in bit; q,qbar:buffer bit);

end srflip;

architecture virat of srflip is

signal s1,r1:bit;

begin

s1<=s nand clk;

r1<=r nand clk;

q<= s1 nand qbar;

qbar<= r1 nand q;

end virat;รูปคลื่น

รหัส VHDL สำหรับ JK Flip Flop

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity jk is

port(

j : in STD_LOGIC;

k : in STD_LOGIC;

clk : in STD_LOGIC;

reset : in STD_LOGIC;

q : out STD_LOGIC;

qb : out STD_LOGIC

);

end jk;

architecture virat of jk is

begin

jkff : process (j,k,clk,reset) is

variable m : std_logic := '0';

begin

if (reset = '1') then

m : = '0';

elsif (rising_edge (clk)) then

if (j/ = k) then

m : = j;

elsif (j = '1' and k = '1') then

m : = not m;

end if;

end if;

q <= m;

qb <= not m;

end process jkff;

end virat;รูปคลื่น

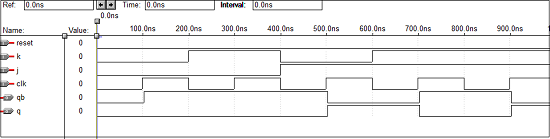

รหัส VHDL สำหรับ D Flip Flop

Library ieee;

use ieee.std_logic_1164.all;

entity dflip is

port(d,clk:in bit; q,qbar:buffer bit);

end dflip;

architecture virat of dflip is

signal d1,d2:bit;

begin

d1<=d nand clk;

d2<=(not d) nand clk;

q<= d1 nand qbar;

qbar<= d2 nand q;

end virat;รูปคลื่น

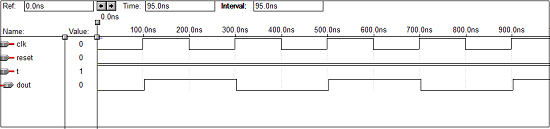

รหัส VHDL สำหรับ T Flip Flop

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity Toggle_flip_flop is

port(

t : in STD_LOGIC;

clk : in STD_LOGIC;

reset : in STD_LOGIC;

dout : out STD_LOGIC

);

end Toggle_flip_flop;

architecture virat of Toggle_flip_flop is

begin

tff : process (t,clk,reset) is

variable m : std_logic : = '0';

begin

if (reset = '1') then

m : = '0';

elsif (rising_edge (clk)) then

if (t = '1') then

m : = not m;

end if;

end if;

dout < = m;

end process tff;

end virat;รูปคลื่น

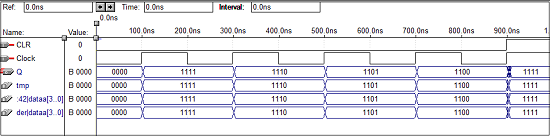

รหัส VHDL สำหรับตัวนับ 4 บิต

library IEEE;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity counter is

port(Clock, CLR : in std_logic;

Q : out std_logic_vector(3 downto 0)

);

end counter;

architecture virat of counter is

signal tmp: std_logic_vector(3 downto 0);

begin

process (Clock, CLR)

begin

if (CLR = '1') then

tmp < = "0000";

elsif (Clock'event and Clock = '1') then

mp <= tmp + 1;

end if;

end process;

Q <= tmp;

end virat;รูปคลื่น

รหัส VHDL สำหรับตัวนับลง 4 บิต

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity dcounter is

port(Clock, CLR : in std_logic;

Q : out std_logic_vector(3 downto 0));

end dcounter;

architecture virat of dcounter is

signal tmp: std_logic_vector(3 downto 0);

begin

process (Clock, CLR)

begin

if (CLR = '1') then

tmp <= "1111";

elsif (Clock'event and Clock = '1') then

tmp <= tmp - 1;

end if;

end process;

Q <= tmp;

end virat;รูปคลื่น

Verilog เป็นภาษาคำอธิบายฮาร์ดแวร์ (HDL) เป็นภาษาที่ใช้ในการอธิบายระบบดิจิทัลเช่นสวิตช์เครือข่ายหรือไมโครโปรเซสเซอร์หรือหน่วยความจำหรือฟลิปฟล็อป หมายความว่าด้วยการใช้ HDL เราสามารถอธิบายฮาร์ดแวร์ดิจิทัลได้ทุกระดับ การออกแบบซึ่งอธิบายไว้ใน HDL นั้นไม่ขึ้นกับเทคโนโลยีง่ายมากสำหรับการออกแบบและการดีบักและโดยปกติจะมีประโยชน์มากกว่าแผนผังโดยเฉพาะอย่างยิ่งสำหรับวงจรขนาดใหญ่

Verilog สนับสนุนการออกแบบในหลายระดับของนามธรรม สามรายใหญ่ ได้แก่ -

- ระดับพฤติกรรม

- ระดับทะเบียน - โอน

- ระดับประตู

ระดับพฤติกรรม

ระดับนี้จะอธิบายระบบโดยอัลกอริทึมที่ทำงานพร้อมกัน (พฤติกรรม) ทุกอัลกอริทึมเป็นลำดับซึ่งหมายความว่าประกอบด้วยชุดคำสั่งที่ดำเนินการทีละคำสั่ง ฟังก์ชั่นงานและบล็อกเป็นองค์ประกอบหลัก ไม่มีการคำนึงถึงโครงสร้างของการออกแบบ

ลงทะเบียน − โอนเลเวล

การออกแบบโดยใช้ Register Register Transfer Level ระบุลักษณะของวงจรที่ใช้การทำงานและการถ่ายโอนข้อมูลระหว่างรีจิสเตอร์ คำจำกัดความสมัยใหม่ของรหัส RTL คือ "รหัสใด ๆ ที่สังเคราะห์ได้เรียกว่ารหัส RTL"

ระดับประตู

ภายในระดับตรรกะลักษณะของระบบจะอธิบายโดยลิงก์ตรรกะและคุณสมบัติของเวลา สัญญาณทั้งหมดเป็นสัญญาณที่ไม่ต่อเนื่อง ค่าเหล่านี้สามารถมีค่าตรรกะที่แน่นอนเท่านั้น (`0 ',` 1', `X ',` Z`) การดำเนินการที่ใช้งานได้เป็นพื้นฐานตรรกะที่กำหนดไว้ล่วงหน้า (ประตูพื้นฐาน) การสร้างแบบจำลองระดับประตูอาจไม่ใช่แนวคิดที่ถูกต้องสำหรับการออกแบบเชิงตรรกะ รหัสระดับประตูถูกสร้างขึ้นโดยใช้เครื่องมือเช่นเครื่องมือสังเคราะห์และ netlist ของเขาใช้สำหรับการจำลองระดับประตูและสำหรับแบ็กเอนด์

โทเค็นคำศัพท์

ไฟล์ข้อความต้นฉบับภาษา Verilog เป็นสตรีมของโทเค็นคำศัพท์ โทเค็นประกอบด้วยอักขระอย่างน้อยหนึ่งตัวและอักขระเดี่ยวแต่ละตัวอยู่ในโทเค็นเดียว

โทเค็นคำศัพท์พื้นฐานที่ใช้โดย Verilog HDL นั้นคล้ายกับโทเค็นในภาษาการเขียนโปรแกรม C Verilog เป็นกรณีที่ละเอียดอ่อน คำสำคัญทั้งหมดเป็นตัวพิมพ์เล็ก

พื้นที่สีขาว

ช่องว่างสีขาวสามารถมีอักขระสำหรับช่องว่างแท็บบรรทัดใหม่และฟีดฟอร์ม อักขระเหล่านี้จะถูกละเว้นยกเว้นเมื่อใช้เพื่อแยกโทเค็น

อักขระช่องว่างคือช่องว่างแท็บการส่งคืนค่าขนส่งขึ้นบรรทัดใหม่และฟีดฟอร์ม

ความคิดเห็น

มีสองรูปแบบเพื่อแสดงความคิดเห็น

- 1) ความคิดเห็นบรรทัดเดียวเริ่มต้นด้วยโทเค็น // และลงท้ายด้วยการคืนค่าขนส่ง

ตัวอย่าง: // นี่คือไวยากรณ์บรรทัดเดียว

- 2) ความคิดเห็นหลายบรรทัดเริ่มต้นด้วยโทเค็น / * และลงท้ายด้วยโทเค็น * /

ตัวอย่าง: / * นี่คือไวยากรณ์หลายบรรทัด * /

ตัวเลข

คุณสามารถระบุตัวเลขในรูปแบบไบนารีฐานแปดทศนิยมหรือฐานสิบหก ตัวเลขเชิงลบจะแสดงเป็นตัวเลขชมเชย 2 Verilog อนุญาตให้ใช้เลขจำนวนเต็มจำนวนจริงและตัวเลขที่ลงชื่อและไม่ได้ลงชื่อ

ไวยากรณ์ถูกกำหนดโดย - <size> <radix> <value>

ขนาดหรือจำนวนที่ไม่ได้กำหนดขนาดสามารถกำหนดได้ใน <Size> และ <radix> กำหนดว่าเป็นเลขฐานสองฐานแปดเลขฐานสิบหกหรือฐานสิบ

ตัวระบุ

Identifier คือชื่อที่ใช้ในการกำหนดวัตถุเช่นฟังก์ชันโมดูลหรือรีจิสเตอร์ ตัวระบุควรขึ้นต้นด้วยอักขระตามตัวอักษรหรืออักขระขีดล่าง เช่น A_Z, a_z, _

Identifiers คือการผสมระหว่างตัวอักษรตัวเลขเครื่องหมายขีดล่างและอักขระ $ มีความยาวได้ถึง 1024 อักขระ

ตัวดำเนินการ

ตัวดำเนินการคืออักขระพิเศษที่ใช้ในการวางเงื่อนไขหรือใช้งานตัวแปร มีหนึ่งสองและบางครั้งสามอักขระที่ใช้ในการดำเนินการกับตัวแปร

เช่น >, +, ~, &! =.

คีย์เวิร์ด Verilog

คำที่มีความหมายพิเศษใน Verilog เรียกว่าคำหลัก Verilog ตัวอย่างเช่นกำหนด case, while, wire, reg และหรือ nand และ module ไม่ควรใช้เป็นตัวระบุ คีย์เวิร์ด Verilog ยังรวมถึงคำสั่งคอมไพเลอร์และงานระบบและฟังก์ชัน

การสร้างแบบจำลองระดับประตู

Verilog มีแบบดั้งเดิมในตัวเช่นลอจิกเกตประตูส่งและสวิตช์ สิ่งเหล่านี้ไม่ค่อยใช้สำหรับงานออกแบบ แต่ใช้ในโลกหลังการสังเคราะห์เพื่อสร้างแบบจำลองของเซลล์ ASIC / FPGA

แบบจำลองระดับประตูแสดงคุณสมบัติสองประการ -

Drive strength- ความแข็งแรงของประตูเอาต์พุตกำหนดโดยความแรงของไดรฟ์ เอาต์พุตจะแข็งแกร่งที่สุดหากมีการเชื่อมต่อโดยตรงกับแหล่งที่มา ความแรงจะลดลงหากการเชื่อมต่อผ่านทรานซิสเตอร์ตัวนำและน้อยที่สุดเมื่อเชื่อมต่อผ่านตัวต้านทานแบบดึงขึ้น / ลง โดยปกติจะไม่ระบุความแรงของไดรฟ์ซึ่งในกรณีนี้จุดแข็งจะมีค่าเริ่มต้นเป็น strong1 และ strong0

Delays- หากไม่ได้ระบุความล่าช้าประตูจะไม่มีความล่าช้าในการขยายพันธุ์ หากมีการระบุความล่าช้าสองรายการรายการแรกหมายถึงความล่าช้าในการเพิ่มขึ้นและความล่าช้าที่สอง หากระบุการหน่วงเวลาเพียงครั้งเดียวการขึ้นและลงทั้งสองจะเท่ากัน ความล่าช้าอาจถูกละเลยในการสังเคราะห์

ประตูดั้งเดิม

ลอจิกเกตพื้นฐานที่ใช้เอาต์พุตเดียวและอินพุตจำนวนมากถูกใช้ใน Verilog GATE ใช้หนึ่งในคีย์เวิร์ด - and, nand หรือ, nor, xor, xnor เพื่อใช้ใน Verilog สำหรับอินพุตจำนวน N และเอาต์พุต 1 เอาต์พุต

Example:

Module gate()

Wire ot0;

Wire ot1;

Wire ot2;

Reg in0,in1,in2,in3;

Not U1(ot0,in0);

Xor U2(ot1,in1,in2,in3);

And U3(ot2, in2,in3,in0)ดั้งเดิมของ Transmission Gate

พื้นฐานของ Transmission gate ประกอบด้วยทั้งบัฟเฟอร์และอินเวอร์เตอร์ มีอินพุตเดียวและเอาต์พุตอย่างน้อยหนึ่งรายการ ในไวยากรณ์เกตอินสแตนซ์ที่แสดงด้านล่าง GATE ย่อมาจากคำหลัก buf หรือ NOT gate

ตัวอย่าง: Not, buf, bufif0, bufif1, notif0, notif1

ไม่ - n outout อินเวอร์เตอร์

บัฟเฟอร์เอาต์พุต Buf - n

Bufifo - บัฟเฟอร์ tristate เปิดใช้งานต่ำ

Bufif1 - บัฟเฟอร์ tristate เปิดใช้งานสูง

Notifo - อินเวอร์เตอร์ tristate เปิดใช้งานต่ำ

Notif1 - อินเวอร์เตอร์ tristate เปิดใช้งานสูง

Example:

Module gate()

Wire out0;

Wire out1;

Reg in0,in1;

Not U1(out0,in0);

Buf U2(out0,in0);ประเภทข้อมูล

ชุดค่า

Verilog ประกอบด้วยค่าพื้นฐานสี่ค่าเป็นหลัก ชนิดข้อมูล Verilog ทั้งหมดซึ่งใช้ใน Verilog เก็บค่าเหล่านี้ -

0 (ศูนย์ลอจิกหรือเงื่อนไขเท็จ)

1 (ลอจิกหนึ่งหรือเงื่อนไขจริง)

x (ค่าตรรกะที่ไม่รู้จัก)

z (สถานะอิมพีแดนซ์สูง)

การใช้ x และ z มีข้อ จำกัด ในการสังเคราะห์

ลวด

ลวดใช้เพื่อแสดงลวดทางกายภาพในวงจรและใช้สำหรับเชื่อมต่อประตูหรือโมดูล ค่าของสายสามารถอ่านได้เท่านั้นและไม่ได้กำหนดในฟังก์ชันหรือบล็อก ลวดไม่สามารถจัดเก็บค่าได้ แต่จะขับเคลื่อนด้วยคำสั่งการกำหนดอย่างต่อเนื่องหรือโดยการเชื่อมต่อสายเข้ากับเอาต์พุตของเกต / โมดูล สายไฟประเภทอื่น ๆ ได้แก่ -

Wand (wired-AND) - ค่า Wand ที่นี่ขึ้นอยู่กับตรรกะ AND ของไดรเวอร์อุปกรณ์ทั้งหมดที่เชื่อมต่ออยู่

Wor (wired-OR) - ค่าของ Wor ขึ้นอยู่กับตรรกะหรือของไดรเวอร์อุปกรณ์ทั้งหมดที่เชื่อมต่ออยู่

Tri (three-state) - ที่นี่ไดรเวอร์ทั้งหมดที่เชื่อมต่อกับไตรต้องเป็น z ยกเว้นเพียงตัวเดียว (ซึ่งกำหนดค่าของไตร)

Example:

Wire [msb:lsb] wire_variable_list;

Wirec // simple wire

Wand d;

Assign d = a; // value of d is the logical AND of

Assign d = b; // a and b

Wire [9:0] A; // a cable (vector) of 10 wires.

Wand [msb:lsb] wand_variable_list;

Wor [msb:lsb] wor_variable_list;

Tri [msb:lsb] tri_variable_list;ลงทะเบียน

reg (register) คืออ็อบเจ็กต์ข้อมูลซึ่งเก็บค่าจากการกำหนดโพรซีเดอร์หนึ่งไปยังขั้นตอนถัดไปและใช้เฉพาะในฟังก์ชันและบล็อกโพรซีเดอร์ที่แตกต่างกัน Reg คือ Verilog แบบธรรมดาซึ่งเป็นรีจิสเตอร์ประเภทตัวแปรและไม่สามารถบ่งบอกถึงการลงทะเบียนทางกายภาพได้ ในการลงทะเบียนแบบหลายบิตข้อมูลจะถูกจัดเก็บในรูปแบบของตัวเลขที่ไม่ได้ลงชื่อและไม่ได้ใช้นามสกุล

ตัวอย่าง -

reg c; // ตัวแปรรีจิสเตอร์ 1 บิตเดียว

reg [5: 0] อัญมณี; // เวกเตอร์ 6 บิต;

reg [6: 0] ง, จ; // สองตัวแปร 7 บิต

อินพุตเอาต์พุต Inout

คำสำคัญเหล่านี้ใช้เพื่อประกาศพอร์ตอินพุตเอาต์พุตและแบบสองทิศทางของงานหรือโมดูล ที่นี่พอร์ตอินพุตและอินเอาต์ซึ่งเป็นประเภทสายไฟและพอร์ตเอาต์พุตได้รับการกำหนดค่าให้เป็นประเภท wire, reg, wand, wor หรือ tri ค่าเริ่มต้นคือประเภทสายเสมอ

Example

Module sample(a, c, b, d);

Input c; // An input where wire is used.

Output a, b; // Two outputs where wire is used.

Output [2:0] d; /* A three-bit output. One must declare type in a separate statement. */

reg [1:0] a; // The above ‘a’ port is for declaration in reg.จำนวนเต็ม

จำนวนเต็มใช้ในตัวแปรวัตถุประสงค์ทั่วไป ส่วนใหญ่จะใช้ในการบ่งชี้ลูปค่าคงที่และพารามิเตอร์ เป็นประเภทข้อมูลประเภท 'reg' พวกเขาจัดเก็บข้อมูลเป็นตัวเลขที่มีการลงนามในขณะที่ประเภท reg ที่ประกาศไว้อย่างชัดเจนจะจัดเก็บเป็นข้อมูลที่ไม่ได้ลงชื่อ หากไม่ได้กำหนดจำนวนเต็มในขณะคอมไพล์ขนาดเริ่มต้นจะเป็น 32 บิต

หากจำนวนเต็มมีค่าคงที่ซินธิไซเซอร์จะปรับให้มีความกว้างต่ำสุดที่จำเป็นในขณะคอมไพล์

Example

Integer c; // single 32-bit integer

Assign a = 63; // 63 defaults to a 7-bit variable.ซัพพลาย 0, ซัพพลาย 1

Supply0 กำหนดสายที่เชื่อมโยงกับลอจิก 0 (กราวด์) และ supply1 กำหนดสายไฟที่เชื่อมโยงกับลอจิก 1 (กำลัง)

Example

supply0 logic_0_wires;

supply0 gnd1; // equivalent to a wire assigned as 0

supply1 logic_1_wires;

supply1 c, s;เวลา

เวลาเป็นปริมาณ 64 บิตที่สามารถใช้ร่วมกับงานระบบ $ time เพื่อเก็บเวลาจำลอง ไม่สนับสนุนเวลาสำหรับการสังเคราะห์ดังนั้นจึงใช้เพื่อวัตถุประสงค์ในการจำลองเท่านั้น

Example

time time_variable_list;

time c;

c = $time; //c = current simulation timeพารามิเตอร์

พารามิเตอร์กำลังกำหนดค่าคงที่ซึ่งสามารถตั้งค่าได้เมื่อคุณใช้โมดูลซึ่งอนุญาตให้ปรับแต่งโมดูลในระหว่างกระบวนการสร้างอินสแตนซ์

Example

Parameter add = 3’b010, sub = 2’b11;

Parameter n = 3;

Parameter [2:0] param2 = 3’b110;

reg [n-1:0] jam; /* A 3-bit register with length of n or above. */

always @(z)

y = {{(add - sub){z}};

if (z)

begin

state = param2[1];

else

state = param2[2];

endตัวดำเนินการ

ตัวดำเนินการเลขคณิต

ตัวดำเนินการเหล่านี้ดำเนินการคำนวณทางคณิตศาสตร์ + และ − ใช้เป็นตัวดำเนินการยูนารี (x) หรือไบนารี (z − y)

ตัวดำเนินการที่รวมอยู่ในการคำนวณทางคณิตศาสตร์ ได้แก่ -

+ (การบวก), - (การลบ), * (การคูณ), / (การหาร),% (โมดูลัส)

Example -

parameter v = 5;

reg[3:0] b, d, h, i, count;

h = b + d;

i = d - v;

cnt = (cnt +1)%16; //Can count 0 thru 15.ตัวดำเนินการเชิงสัมพันธ์

ตัวดำเนินการเหล่านี้เปรียบเทียบตัวถูกดำเนินการสองตัวและส่งคืนผลลัพธ์เป็นบิตเดียว 1 หรือ 0

ตัวแปร Wire และ reg เป็นค่าบวก ดังนั้น (−3'd001) = = 3'd111 และ (−3b001)> 3b110

ตัวดำเนินการที่รวมอยู่ในการดำเนินการเชิงสัมพันธ์ ได้แก่ -

- == (เท่ากับ)

- ! = (ไม่เท่ากับ)

- > (มากกว่า)

- > = (มากกว่าหรือเท่ากับ)

- <(น้อยกว่า)

- <= (น้อยกว่าหรือเท่ากับ)

Example

if (z = = y) c = 1;

else c = 0; // Compare in 2’s compliment; d>b

reg [3:0] d,b;

if (d[3]= = b[3]) d[2:0] > b[2:0];

else b[3];

Equivalent Statement

e = (z == y);ตัวดำเนินการที่ชาญฉลาด

ตัวดำเนินการที่ชาญฉลาดซึ่งกำลังทำการเปรียบเทียบแบบบิตต่อบิตระหว่างตัวถูกดำเนินการสองตัว

ตัวดำเนินการที่รวมอยู่ในการทำงานของ Bit wise ได้แก่ -

- & (บิตตามและ)

- | (bitwiseOR)

- ~ (บิตไม่)

- ^ (XOR แบบบิต)

- ~ ^ หรือ ^ ~ (บิต XNOR)

Example

module and2 (d, b, c);

input [1:0] d, b;

output [1:0] c;

assign c = d & b;

end moduleตัวดำเนินการทางตรรกะ

ตัวดำเนินการทางตรรกะเป็นตัวดำเนินการที่ชาญฉลาดและใช้สำหรับตัวถูกดำเนินการบิตเดียวเท่านั้น พวกเขาส่งคืนค่าบิตเดียว 0 หรือ 1 สามารถทำงานกับจำนวนเต็มหรือกลุ่มของบิตนิพจน์และถือว่าค่าที่ไม่ใช่ศูนย์ทั้งหมดเป็น 1 โดยทั่วไปตัวดำเนินการทางตรรกะจะใช้ในคำสั่งเงื่อนไขเนื่องจากทำงานกับนิพจน์

ตัวดำเนินการที่รวมอยู่ในการดำเนินการทางตรรกะ ได้แก่ -

- ! (ตรรกะไม่)

- && (ตรรกะ AND)

- || (ตรรกะหรือ)

Example

wire[7:0] a, b, c; // a, b and c are multibit variables.

reg x;

if ((a == b) && (c)) x = 1; //x = 1 if a equals b, and c is nonzero.

else x = !a; // x =0 if a is anything but zero.ตัวดำเนินการลด

ตัวดำเนินการลดเป็นรูปแบบเอกพจน์ของตัวดำเนินการบิตและดำเนินการกับบิตทั้งหมดของเวกเตอร์ตัวถูกดำเนินการ สิ่งเหล่านี้ส่งคืนค่าบิตเดียว

ตัวดำเนินการที่รวมอยู่ในการดำเนินการลด ได้แก่ -

- & (ลดและ)

- | (ลดหรือ)

- ~ & (ลด NAND)

- ~ | (ลด NOR)

- ^ (ลด XOR)

- ~ ^ หรือ ^ ~ (ลด XNOR)

Example

Module chk_zero (x, z);

Input [2:0] x;

Output z;

Assign z = & x; // Reduction AND

End moduleตัวดำเนินการกะ

ตัวดำเนินการ Shift ซึ่งขยับตัวถูกดำเนินการตัวแรกตามจำนวนบิตที่ระบุโดยตัวถูกดำเนินการที่สองในไวยากรณ์ ตำแหน่งที่ว่างจะเต็มไปด้วยเลขศูนย์สำหรับทั้งสองทิศทางการเลื่อนซ้ายและขวา (ไม่มีส่วนขยายเครื่องหมายใช้)

ตัวดำเนินการที่รวมอยู่ในการทำงานของ Shift ได้แก่ -

- << (เลื่อนไปทางซ้าย)

- >> (เลื่อนไปทางขวา)

Example

Assign z = c << 3; /* z = c shifted left 3 bits;ตำแหน่งว่างจะเต็มไปด้วย 0's * /

ตัวดำเนินการเชื่อมต่อ

ตัวดำเนินการต่อกันจะรวมตัวถูกดำเนินการสองตัวขึ้นไปเพื่อสร้างเวกเตอร์ที่ใหญ่ขึ้น

ตัวดำเนินการที่รวมอยู่ในการดำเนินการเชื่อมต่อคือ - {} (การเรียงต่อกัน)

Example

wire [1:0] a, h; wire [2:0] x; wire [3;0] y, Z;

assign x = {1’b0, a}; // x[2] = 0, x[1] = a[1], x[0] = a[0]

assign b = {a, h}; /* b[3] = a[1], b[2] = a[0], b[1] = h[1],

b[0] = h[0] */

assign {cout, b} = x + Z; // Concatenation of a resultตัวดำเนินการจำลอง

ตัวดำเนินการจำลองแบบกำลังทำสำเนาหลายรายการ

ตัวดำเนินการที่ใช้ในการจำลองแบบคือ - {n {item}} (การจำลองแบบแบบพับของรายการ)

Example

Wire [1:0] a, f; wire [4:0] x;

Assign x = {2{1’f0}, a}; // Equivalent to x = {0,0,a }

Assign y = {2{a}, 3{f}}; //Equivalent to y = {a,a,f,f}

For synthesis, Synopsis did not like a zero replication.

For example:-

Parameter l = 5, k = 5;

Assign x = {(l-k){a}}ตัวดำเนินการตามเงื่อนไข

ตัวดำเนินการตามเงื่อนไขสังเคราะห์เป็นมัลติเพล็กเซอร์ เป็นชนิดเดียวกับที่ใช้ใน C / C ++ และประเมินหนึ่งในสองนิพจน์ตามเงื่อนไข

ตัวดำเนินการที่ใช้ในการดำเนินการตามเงื่อนไขคือ -

(เงื่อนไข) ? (ผลลัพธ์หากเงื่อนไขเป็นจริง) -

(ผลลัพธ์หากเงื่อนไขเป็นเท็จ)

Example

Assign x = (g) ? a : b;

Assign x = (inc = = 2) ? x+1 : x-1;

/* if (inc), x = x+1, else x = x-1 */โอเปร่า

ตัวอักษร

ตัวอักษรเป็นตัวถูกดำเนินการที่มีค่าคงที่ซึ่งใช้ในนิพจน์ Verilog ตัวอักษร Verilog ที่ใช้กันทั่วไปสองตัวคือ -

String - ตัวดำเนินการตามตัวอักษรสตริงคืออาร์เรย์ของอักขระหนึ่งมิติซึ่งอยู่ในเครื่องหมายคำพูดคู่ ("")

Numeric - ตัวถูกดำเนินการตัวเลขคงที่ระบุเป็นเลขฐานสองฐานแปดฐานสิบหรือเลขฐานสิบหก

Example

n - จำนวนเต็มแทนจำนวนบิต

F - หนึ่งในสี่รูปแบบพื้นฐานที่เป็นไปได้ -

b สำหรับไบนารี o สำหรับฐานแปด d สำหรับทศนิยม h สำหรับเลขฐานสิบหก

“time is” // string literal

267 // 32-bit decimal number

2’b01 // 2-bit binary

20’hB36F // 20-bit hexadecimal number

‘062 // 32-bit octal numberสายไฟ Regs และพารามิเตอร์

สายไฟ regs และพารามิเตอร์คือชนิดข้อมูลที่ใช้เป็นตัวถูกดำเนินการในนิพจน์ Verilog

Bit-Selection“ x [2]” และ Part-Selection“ x [4: 2]”

การเลือกบิตและการเลือกบางส่วนใช้เพื่อเลือกหนึ่งบิตและหลายบิตตามลำดับจากลวดเรกหรือเวกเตอร์พารามิเตอร์โดยใช้วงเล็บเหลี่ยม“ []” Bit-selects และ part-selects ยังใช้เป็นตัวถูกดำเนินการในนิพจน์ในลักษณะเดียวกับที่ใช้อ็อบเจ็กต์ข้อมูลหลัก

Example

reg [7:0] x, y;

reg [3:0] z;

reg a;

a = x[7] & y[7]; // bit-selects

z = x[7:4] + y[3:0]; // part-selectsฟังก์ชั่นการโทร

ในการเรียกใช้ฟังก์ชันค่าส่งกลับของฟังก์ชันจะถูกใช้โดยตรงในนิพจน์โดยไม่จำเป็นต้องกำหนดให้กับรีจิสเตอร์หรือการต่อสายก่อน เพียงแค่วางการเรียกใช้ฟังก์ชันเป็นหนึ่งในประเภทของตัวถูกดำเนินการจำเป็นอย่างยิ่งเพื่อให้แน่ใจว่าคุณทราบความกว้างบิตของค่าส่งกลับของการเรียกฟังก์ชัน

Example

Assign x = y & z & chk_yz(z, y); // chk_yz is a function

. . ./* Definition of the function */

Function chk_yz; // function definition

Input z,y;

chk_yz = y^z;

End functionโมดูล

การประกาศโมดูล

ใน Verilog โมดูลคือเอนทิตีการออกแบบหลัก สิ่งนี้ระบุชื่อและรายการพอร์ต (อาร์กิวเมนต์) ไม่กี่บรรทัดถัดไปซึ่งระบุประเภทอินพุต / เอาต์พุต (อินพุตเอาต์พุตหรืออินพุต) และความกว้างของแต่ละพอร์ต ความกว้างของพอร์ตเริ่มต้นคือ 1 บิตเท่านั้น ต้องประกาศตัวแปรพอร์ตด้วยลวดไม้กายสิทธิ์ . ., reg. ตัวแปรพอร์ตเริ่มต้นคือสาย โดยปกติอินพุตจะเป็นแบบต่อสายเนื่องจากข้อมูลของมันถูกสลักอยู่นอกโมดูล เอาต์พุตเป็นประเภท reg หากสัญญาณถูกเก็บไว้ภายใน

Example

module sub_add(add, in1, in2, out);

input add; // defaults to wire

input [7:0] in1, in2; wire in1, in2;

output [7:0] out; reg out;

... statements ...

End moduleการมอบหมายงานอย่างต่อเนื่อง

การกำหนดแบบต่อเนื่องในโมดูลใช้สำหรับกำหนดค่าบนสายซึ่งเป็นการกำหนดปกติที่ใช้นอกบล็อกเสมอหรือเริ่มต้น การมอบหมายนี้ทำด้วยคำสั่งมอบหมายอย่างชัดเจนหรือเพื่อกำหนดค่าให้กับลวดในระหว่างการประกาศ การมอบหมายงานอย่างต่อเนื่องจะดำเนินการอย่างต่อเนื่องในช่วงเวลาจำลอง ลำดับของการกำหนดงบไม่มีผลกับมัน หากคุณทำการเปลี่ยนแปลงใด ๆ ในสัญญาณอินพุตด้านขวามือสัญญาณจะเปลี่ยนสัญญาณเอาต์พุตด้านซ้ายมือ

Example

Wire [1:0] x = 2’y01; // assigned on declaration

Assign y = c | d; // using assign statement

Assign d = a & b;

/* the order of the assign statements does not matter. */โมดูลอินสแตนซ์

การประกาศโมดูลเป็นเทมเพลตสำหรับการสร้างวัตถุจริง โมดูลถูกสร้างอินสแตนซ์ภายในโมดูลอื่น ๆ และแต่ละอินสแตนซ์กำลังสร้างออบเจ็กต์เดียวจากเทมเพลตนั้น ข้อยกเว้นคือโมดูลระดับบนสุดซึ่งเป็นอินสแตนซ์ของตัวเอง พอร์ตของโมดูลจะต้องตรงกับพอร์ตที่กำหนดไว้ในเทมเพลต มีการระบุ -

By nameโดยใช้จุด“ .template port name (ชื่อสายไฟที่เชื่อมต่อกับพอร์ต)” หรือ

By positionวางพอร์ตไว้ที่เดียวกันในรายการพอร์ตของทั้งเทมเพลตและอินสแตนซ์

Example

MODULE DEFINITION

Module and4 (x, y, z);

Input [3:0] x, y;

Output [3:0] z;

Assign z = x | y;

End moduleแบบจำลองพฤติกรรมใน Verilog ประกอบด้วยคำสั่งขั้นตอนซึ่งควบคุมการจำลองและจัดการตัวแปรของชนิดข้อมูล ข้อความทั้งหมดเหล่านี้มีอยู่ในขั้นตอน แต่ละโพรซีเดอร์มีโฟลว์กิจกรรมที่เกี่ยวข้อง

ในระหว่างการจำลองแบบจำลองพฤติกรรมกระแสทั้งหมดที่กำหนดโดยคำสั่ง "always" และ "initial" จะเริ่มต้นพร้อมกันที่เวลาจำลอง "ศูนย์" คำสั่งเริ่มต้นจะดำเนินการเพียงครั้งเดียวและคำสั่ง always จะถูกดำเนินการซ้ำ ๆ ในโมเดลนี้ตัวแปรรีจิสเตอร์ a และ b จะเริ่มต้นเป็นไบนารี 1 และ 0 ตามลำดับที่เวลาจำลอง 'ศูนย์' จากนั้นคำสั่งเริ่มต้นจะเสร็จสมบูรณ์และจะไม่ดำเนินการอีกในระหว่างการดำเนินการจำลองนั้น คำสั่งเริ่มต้นนี้ประกอบด้วยบล็อกเริ่มต้น (หรือเรียกว่าบล็อกตามลำดับ) ของคำสั่ง ในบล็อกประเภทเริ่มต้นนี้ a จะเริ่มต้นก่อนตามด้วย b

ตัวอย่างการสร้างแบบจำลองพฤติกรรม

module behave;

reg [1:0]a,b;

initial

begin

a = ’b1;

b = ’b0;

end

always

begin

#50 a = ~a;

end

always

begin

#100 b = ~b;

end

End moduleการกำหนดขั้นตอน

การกำหนดขั้นตอนมีไว้สำหรับการอัพเดตตัวแปร reg, integer, time และ memory มีความแตกต่างอย่างมีนัยสำคัญระหว่างการกำหนดขั้นตอนและการมอบหมายงานต่อเนื่องตามที่อธิบายไว้ด้านล่าง -

การกำหนดอย่างต่อเนื่องขับเคลื่อนตัวแปรสุทธิและได้รับการประเมินและอัปเดตเมื่อใดก็ตามที่ตัวถูกดำเนินการอินพุตเปลี่ยนค่า

การกำหนดขั้นตอนจะอัพเดตค่าของตัวแปรรีจิสเตอร์ภายใต้การควบคุมของโครงสร้างโฟลว์โพรซีเดอร์ที่ล้อมรอบ

ด้านขวามือของการกำหนดขั้นตอนอาจเป็นนิพจน์ใด ๆ ที่ประเมินเป็นค่า อย่างไรก็ตามส่วนที่เลือกทางด้านขวามือจะต้องมีดัชนีคงที่ ด้านซ้ายแสดงถึงตัวแปรที่รับงานจากด้านขวามือ ด้านซ้ายมือของการกำหนดขั้นตอนสามารถใช้รูปแบบใดรูปแบบหนึ่งต่อไปนี้ -

register, integer, real หรือ time variable - การกำหนดให้กับการอ้างอิงชื่อของข้อมูลประเภทใดประเภทหนึ่งเหล่านี้

การเลือกบิตของตัวแปร register, จำนวนเต็ม, จริงหรือเวลา - การกำหนดให้กับบิตเดียวที่ทำให้บิตอื่น ๆ ไม่ถูกแตะต้อง

part-select of a register, integer, real หรือ time variable - การเลือกบางส่วนของสองบิตที่ต่อเนื่องกันซึ่งจะทำให้ส่วนที่เหลือไม่ถูกแตะต้อง สำหรับรูปแบบการเลือกชิ้นส่วนนิพจน์คงที่เท่านั้นที่ถูกต้องตามกฎหมาย

องค์ประกอบหน่วยความจำ - คำเดียวของหน่วยความจำ โปรดทราบว่าการเลือกบิตและการเลือกบางส่วนไม่ถูกต้องในการอ้างอิงองค์ประกอบหน่วยความจำ

การเรียงต่อกันของข้อใดข้อหนึ่งข้างต้น - สามารถระบุการเรียงต่อกันของรูปแบบใดก็ได้จากสี่รูปแบบก่อนหน้าซึ่งแบ่งพาร์ติชันผลลัพธ์ของนิพจน์ด้านขวามือได้อย่างมีประสิทธิภาพและกำหนดพาร์ติชันพาร์ติชันตามลำดับไปยังส่วนต่างๆของการเรียงต่อกัน

ความล่าช้าในการมอบหมายงาน (ไม่ใช่สำหรับการสังเคราะห์)

ในการมอบหมายงานล่าช้าหน่วยเวลาจะผ่านไปก่อนที่คำสั่งจะถูกดำเนินการและทำการกำหนดทางซ้าย ด้วยความล่าช้าภายในการมอบหมายงานด้านขวาจะได้รับการประเมินทันที แต่มีความล่าช้าก่อนที่ผลลัพธ์จะถูกวางไว้ในการมอบหมายด้านซ้ายมือ หากขั้นตอนอื่นเปลี่ยนสัญญาณด้านขวามือระหว่างΔtจะไม่มีผลกับเอาต์พุต เครื่องมือสังเคราะห์ไม่รองรับความล่าช้า

ไวยากรณ์

Procedural Assignmentตัวแปร = นิพจน์

Delayed assignment# Δtตัวแปร = นิพจน์;

Intra-assignment delayตัวแปร = # Δtนิพจน์;

ตัวอย่าง

reg [6:0] sum; reg h, ziltch;

sum[7] = b[7] ^ c[7]; // execute now.

ziltch = #15 ckz&h; /* ckz&a evaluated now; ziltch changed

after 15 time units. */

#10 hat = b&c; /* 10 units after ziltch changes, b&c is

evaluated and hat changes. */การบล็อกงาน

คำสั่งกำหนดขั้นตอนการบล็อกต้องดำเนินการก่อนการดำเนินการของคำสั่งที่ตามมาในบล็อกตามลำดับ คำสั่งกำหนดขั้นตอนการบล็อกไม่ได้ป้องกันการดำเนินการของคำสั่งที่ตามมาในบล็อกคู่ขนาน

ไวยากรณ์

ไวยากรณ์สำหรับการกำหนดขั้นตอนการบล็อกมีดังนี้ -

<lvalue> = <timing_control> <expression>โดยที่ lvalue เป็นชนิดข้อมูลที่ถูกต้องสำหรับคำสั่งการกำหนดขั้นตอน = คือตัวดำเนินการกำหนดและการควบคุมเวลาคือความล่าช้าภายในที่เป็นทางเลือก ความล่าช้าในการควบคุมเวลาอาจเป็นได้ทั้งการควบคุมการหน่วงเวลา (เช่น # 6) หรือการควบคุมเหตุการณ์ (ตัวอย่างเช่น @ (posedge clk)) นิพจน์คือค่าด้านขวามือที่เครื่องมือจำลองกำหนดให้ทางด้านซ้ายมือ ตัวดำเนินการ = ที่ใช้โดยการปิดกั้นการกำหนดขั้นตอนยังใช้โดยการกำหนดขั้นตอนต่อเนื่องและการกำหนดต่อเนื่อง

ตัวอย่าง

rega = 0;

rega[3] = 1; // a bit-select

rega[3:5] = 7; // a part-select

mema[address] = 8’hff; // assignment to a memory element

{carry, acc} = rega + regb; // a concatenationการกำหนด Nonblocking (RTL)

การกำหนดขั้นตอนที่ไม่ปิดกั้นช่วยให้คุณกำหนดเวลาการมอบหมายงานได้โดยไม่ต้องปิดกั้นขั้นตอน คุณสามารถใช้คำสั่งขั้นตอนการไม่ปิดกั้นเมื่อใดก็ตามที่คุณต้องการทำการมอบหมายการลงทะเบียนหลายรายการภายในขั้นตอนเวลาเดียวกันโดยไม่คำนึงถึงลำดับหรือการพึ่งพาซึ่งกันและกัน

ไวยากรณ์

ไวยากรณ์สำหรับการกำหนดขั้นตอนที่ไม่ปิดกั้นมีดังนี้ -

<lvalue> <= <timing_control> <expression>โดยที่ lvalue เป็นชนิดข้อมูลที่ถูกต้องสำหรับคำสั่งการกำหนดขั้นตอน <= คือตัวดำเนินการกำหนดที่ไม่ปิดกั้นและการควบคุมเวลาคือการควบคุมเวลาภายในที่กำหนดซึ่งเป็นทางเลือก ความล่าช้าในการควบคุมเวลาอาจเป็นได้ทั้งการควบคุมการหน่วงเวลาหรือการควบคุมเหตุการณ์ (ตัวอย่างเช่น @ (posedge clk)) นิพจน์คือค่าด้านขวามือที่เครื่องมือจำลองกำหนดให้ทางด้านซ้ายมือ ตัวดำเนินการกำหนดแบบไม่ปิดกั้นเป็นตัวดำเนินการเดียวกับที่ตัวจำลองใช้สำหรับตัวดำเนินการเชิงสัมพันธ์ที่มีคุณภาพน้อยกว่า ตัวจำลองตีความตัวดำเนินการ <= เป็นตัวดำเนินการเชิงสัมพันธ์เมื่อคุณใช้ในนิพจน์และตีความว่าตัวดำเนินการ <= เป็นตัวดำเนินการกำหนดเมื่อคุณใช้ในโครงสร้างการกำหนดขั้นตอนที่ไม่ปิดกั้น

วิธีที่ตัวจำลองประเมินการกำหนดขั้นตอนที่ไม่ปิดกั้นเมื่อตัวจำลองพบการกำหนดขั้นตอนที่ไม่ปิดกั้นตัวจำลองจะประเมินและดำเนินการการกำหนดขั้นตอนที่ไม่ปิดกั้นในสองขั้นตอนดังนี้ -

เครื่องจำลองจะประเมินทางด้านขวามือและกำหนดเวลาการกำหนดค่าใหม่ที่จะเกิดขึ้นในเวลาที่กำหนดโดยการควบคุมเวลาตามขั้นตอน เครื่องจำลองจะประเมินทางด้านขวามือและกำหนดเวลาการกำหนดค่าใหม่ที่จะเกิดขึ้นในเวลาที่กำหนดโดยการควบคุมเวลาตามขั้นตอน

ในตอนท้ายของขั้นตอนเวลาซึ่งความล่าช้าที่กำหนดได้หมดลงหรือเหตุการณ์ที่เหมาะสมเกิดขึ้นเครื่องจำลองจะดำเนินการมอบหมายโดยกำหนดค่าให้ทางด้านซ้ายมือ

ตัวอย่าง

module evaluates2(out);

output out;

reg a, b, c;

initial

begin

a = 0;

b = 1;

c = 0;

end

always c = #5 ~c;

always @(posedge c)

begin

a <= b;

b <= a;

end

endmoduleเงื่อนไข

คำสั่งเงื่อนไข (หรือคำสั่ง if-else) ใช้ในการตัดสินใจว่าจะดำเนินการคำสั่งหรือไม่

อย่างเป็นทางการไวยากรณ์มีดังนี้ -

<statement>

::= if ( <expression> ) <statement_or_null>

||= if ( <expression> ) <statement_or_null>

else <statement_or_null>

<statement_or_null>

::= <statement>

||= ;<expression> ได้รับการประเมิน; ถ้าเป็นจริง (นั่นคือมีค่าที่ไม่รู้จักเป็นศูนย์) คำสั่งแรกจะดำเนินการ ถ้าเป็นเท็จ (มีค่าเป็นศูนย์หรือค่า x หรือ z) คำสั่งแรกจะไม่ดำเนินการ หากมีคำสั่ง else และ <expression> เป็นเท็จคำสั่ง else จะดำเนินการ เนื่องจากค่าตัวเลขของนิพจน์ if ถูกทดสอบว่าเป็นศูนย์จึงสามารถใช้ทางลัดบางอย่างได้

ตัวอย่างเช่นสองคำสั่งต่อไปนี้แสดงตรรกะเดียวกัน -

if (expression)

if (expression != 0)เนื่องจากส่วนอื่นของ if-else เป็นทางเลือกอาจมีความสับสนเมื่อส่วนอื่นถูกละไว้จากลำดับ if ที่ซ้อนกัน สิ่งนี้แก้ไขได้โดยการเชื่อมโยงสิ่งอื่นกับสิ่งที่ใกล้เคียงที่สุดก่อนหน้านี้เสมอหากไม่มีสิ่งอื่น

ตัวอย่าง

if (index > 0)

if (rega > regb)

result = rega;

else // else applies to preceding if

result = regb;

If that association is not what you want, use a begin-end block statement

to force the proper association

if (index > 0)

begin

if (rega > regb)

result = rega;

end

else

result = regb;โครงสร้างของ: if- else- if

การก่อสร้างต่อไปนี้เกิดขึ้นบ่อยครั้งมากจนควรมีการอภิปรายแยกกันสั้น ๆ

Example

if (<expression>)

<statement>

else if (<expression>)

<statement>

else if (<expression>)

<statement>

else

<statement>ลำดับของ if นี้ (เรียกว่าโครงสร้าง if-else-if) เป็นวิธีทั่วไปที่สุดในการเขียนการตัดสินใจหลายทาง นิพจน์ได้รับการประเมินตามลำดับ หากนิพจน์ใด ๆ เป็นจริงคำสั่งที่เกี่ยวข้องจะถูกดำเนินการและสิ่งนี้จะยุติห่วงโซ่ทั้งหมด แต่ละคำสั่งเป็นคำสั่งเดียวหรือบล็อกของคำสั่ง

ส่วนอื่นสุดท้ายของโครงสร้าง if-else-if จัดการกับกรณีที่ "ไม่มีข้อใดข้อหนึ่งข้างต้น" หรือกรณีเริ่มต้นโดยที่เงื่อนไขอื่น ๆ ไม่เป็นไปตามเงื่อนไข บางครั้งไม่มีการดำเนินการที่ชัดเจนสำหรับค่าเริ่มต้น ในกรณีนั้นสามารถละเว้นอื่น ๆ ต่อท้ายหรือสามารถใช้สำหรับการตรวจสอบข้อผิดพลาดเพื่อตรวจจับเงื่อนไขที่เป็นไปไม่ได้

คำชี้แจงกรณี

คำชี้แจงกรณีเป็นคำสั่งการตัดสินใจหลายทางแบบพิเศษที่ทดสอบว่านิพจน์ตรงกับนิพจน์อื่น ๆ จำนวนหนึ่งหรือไม่และแตกแขนงออกไปตามนั้น คำสั่ง case มีประโยชน์สำหรับการอธิบายตัวอย่างเช่นการถอดรหัสคำสั่งของไมโครโปรเซสเซอร์ คำสั่ง case มีไวยากรณ์ต่อไปนี้ -

Example

<statement>

::= case ( <expression> ) <case_item>+ endcase

||= casez ( <expression> ) <case_item>+ endcase

||= casex ( <expression> ) <case_item>+ endcase

<case_item>

::= <expression> <,<expression>>* : <statement_or_null>

||= default : <statement_or_null>

||= default <statement_or_null>นิพจน์เคสจะได้รับการประเมินและเปรียบเทียบตามลำดับที่ได้รับ ในระหว่างการค้นหาเชิงเส้นหากหนึ่งในนิพจน์ไอเท็มเคสตรงกับนิพจน์ในวงเล็บคำสั่งที่เกี่ยวข้องกับไอเท็มเคสนั้นจะถูกดำเนินการ หากการเปรียบเทียบทั้งหมดล้มเหลวและกำหนดรายการดีฟอลต์คำสั่งไอเท็มเริ่มต้นจะถูกดำเนินการ หากไม่ได้กำหนดคำสั่งเริ่มต้นและการเปรียบเทียบทั้งหมดล้มเหลวจะไม่มีการดำเนินการคำสั่ง case item ใด ๆ

นอกเหนือจากไวยากรณ์คำสั่ง case แตกต่างจากการสร้าง if-else-if แบบหลายทางในสองวิธีที่สำคัญ -

นิพจน์เงื่อนไขในโครงสร้าง if-else-if มีลักษณะทั่วไปมากกว่าการเปรียบเทียบนิพจน์หนึ่งกับนิพจน์อื่น ๆ เช่นในคำสั่ง case

คำสั่ง case ให้ผลลัพธ์ที่ชัดเจนเมื่อมีค่า x และ z ในนิพจน์

คำสั่งวนซ้ำ

คำสั่งวนซ้ำมีสี่ประเภท พวกเขาให้วิธีการควบคุมการดำเนินการของคำสั่งศูนย์หนึ่งครั้งหรือมากกว่านั้น

ดำเนินการคำสั่งอย่างต่อเนื่องตลอดไป

ทำซ้ำดำเนินการคำสั่งตามจำนวนครั้งที่กำหนด

ในขณะที่รันคำสั่งจนกว่านิพจน์จะกลายเป็นเท็จ ถ้านิพจน์เริ่มต้นเป็นเท็จจะไม่มีการดำเนินการคำสั่งเลย

สำหรับการควบคุมการดำเนินการของคำสั่งที่เกี่ยวข้องโดยกระบวนการสามขั้นตอนดังต่อไปนี้ -

ดำเนินการมอบหมายตามปกติที่ใช้เพื่อเริ่มต้นตัวแปรที่ควบคุมจำนวนลูปที่ดำเนินการ

ประเมินนิพจน์ - ถ้าผลลัพธ์เป็นศูนย์สำหรับลูปจะออกและถ้าไม่ใช่ศูนย์สำหรับลูปจะรันคำสั่งที่เกี่ยวข้องจากนั้นดำเนินการขั้นตอนที่ 3

ดำเนินการมอบหมายตามปกติที่ใช้เพื่อแก้ไขค่าของตัวแปร loopcontrol จากนั้นทำซ้ำขั้นตอนที่ 2

ต่อไปนี้เป็นกฎไวยากรณ์สำหรับคำสั่งวนซ้ำ -

Example

<statement>

::= forever <statement>

||=forever

begin

<statement>+

end

<Statement>

::= repeat ( <expression> ) <statement>

||=repeat ( <expression> )

begin

<statement>+

end

<statement>

::= while ( <expression> ) <statement>

||=while ( <expression> )

begin

<statement>+

end

<statement>

::= for ( <assignment> ; <expression> ; <assignment> )

<statement>

||=for ( <assignment> ; <expression> ; <assignment> )

begin

<statement>+

endการควบคุมความล่าช้า

การควบคุมความล่าช้า

การดำเนินการของคำสั่งขั้นตอนสามารถควบคุมความล่าช้าได้โดยใช้ไวยากรณ์ต่อไปนี้ -

<statement>

::= <delay_control> <statement_or_null>

<delay_control>

::= # <NUMBER>

||= # <identifier>

||= # ( <mintypmax_expression> )ตัวอย่างต่อไปนี้ทำให้การดำเนินการมอบหมายล่าช้าไป 10 หน่วยเวลา -

# 10 rega = regb;

สามตัวอย่างถัดไปแสดงนิพจน์ตามหลังเครื่องหมายตัวเลข (#) การดำเนินการของความล่าช้าในการมอบหมายตามจำนวนเวลาจำลองที่ระบุโดยค่าของนิพจน์

การควบคุมเหตุการณ์

การดำเนินการของคำสั่งขั้นตอนสามารถซิงโครไนซ์กับการเปลี่ยนแปลงค่าบนเน็ตหรือรีจิสเตอร์หรือการเกิดเหตุการณ์ที่ประกาศโดยใช้ไวยากรณ์การควบคุมเหตุการณ์ต่อไปนี้ -

Example

<statement>

::= <event_control> <statement_or_null>

<event_control>

::= @ <identifier>

||= @ ( <event_expression> )

<event_expression>

::= <expression>

||= posedge <SCALAR_EVENT_EXPRESSION>