組み合わせ回路

組み合わせ回路は、エンコーダ、デコーダ、マルチプレクサ、デマルチプレクサなど、回路内のさまざまなゲートを組み合わせた回路です。組み合わせ回路の特徴のいくつかは次のとおりです。

いつでも組み合わせ回路の出力は、入力端子に存在するレベルにのみ依存します。

組み合わせ回路はメモリを使用しません。以前の入力状態は、回路の現在の状態に影響を与えません。

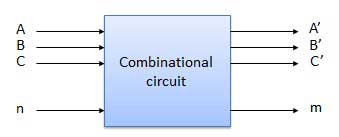

組み合わせ回路は、n個の入力とm個の出力を持つことができます。

ブロック図

以下のように、いくつかの重要な組み合わせ回路を詳しく説明します。

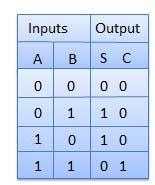

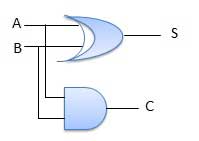

半加算器

半加算器は、2つの入力と2つの出力を備えた組み合わせ論理回路です。半加算回路は、2つのシングルビット2進数AとBを加算するように設計されています。これは、2つを加算するための基本的な構成要素です。singleビット番号。この回路には2つの出力がありますcarry そして sum。

ブロック図

真理値表

回路図

全加算器

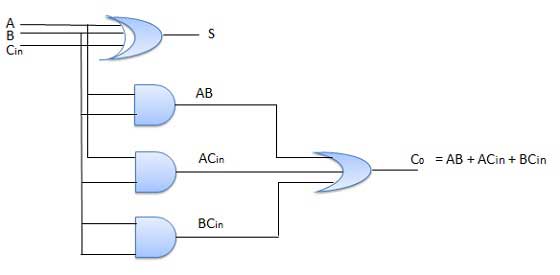

全加算器は、半加算器回路の欠点を克服するために開発されました。2つの1ビット数AとBを加算し、cを運ぶことができます。全加算器は、3入力と2出力の組み合わせ回路です。

ブロック図

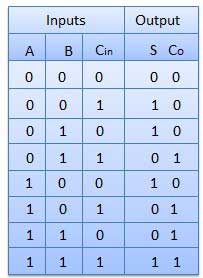

真理値表

回路図

Nビット並列加算器

全加算器は、キャリー入力とともに2つの1桁の2進数のみを加算できます。しかし実際には、1ビットよりはるかに長い2進数を追加する必要があります。2つのnビット2進数を加算するには、nビット並列加算器を使用する必要があります。カスケードで多数の全加算器を使用します。前の全加算器のキャリー出力は、次の全加算器のキャリー入力に接続されます。

4ビット並列加算器

ブロック図において、A 0およびB 0はLSB 4ビットワードAおよびBを表し、したがって全加算器-0が最も低い段階です。したがって、そのC inは永続的に0になります。残りの接続は、nビット並列加算器の接続とまったく同じです。4ビット並列加算器は非常に一般的な論理回路です。

ブロック図

Nビット並列減算器

減算は、減算する数値の1または2の補数を取ることによって実行できます。たとえば、Bの1または2の補数をAに加算することで減算(AB)を実行できます。つまり、2進加算器を使用して2進減算を実行できます。

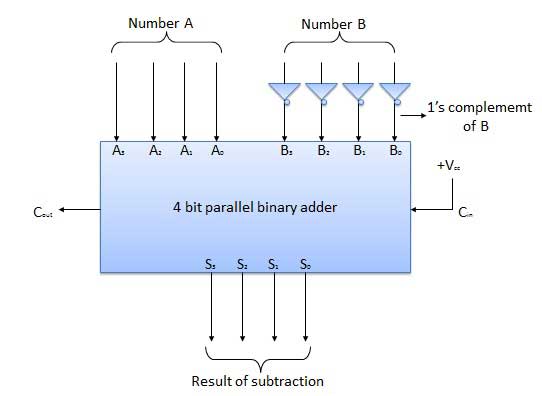

4ビット並列減算器

減算される数(B)は、最初にインバーターを通過して1の補数を取得します。次に、4ビット加算器はAとBの2の補数を加算して、減算を生成します。S 3 S 2 S 1 S 0は、バイナリ減算(AB)及びキャリー出力Cの結果を表しアウト結果の極性を表しています。A> Bの場合、Cout = 0であり、バイナリ形式(AB)の結果である場合、C out = 1であり、結果は2の補数形式になります。

ブロック図

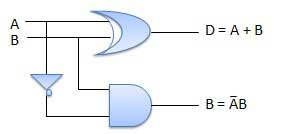

ハーフ減算器

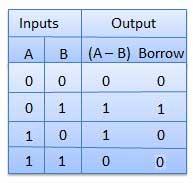

ハーフサブトラクタは、2つの入力と2つの出力(差分と借用)を備えた直並列回路です。入力で2つのバイナリビット間の差を生成し、1が借用されたかどうかを示す出力(借用)も生成します。減算(AB)では、Aは被減数ビットと呼ばれ、Bは減数ビットと呼ばれます。

真理値表

回路図

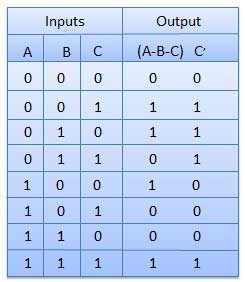

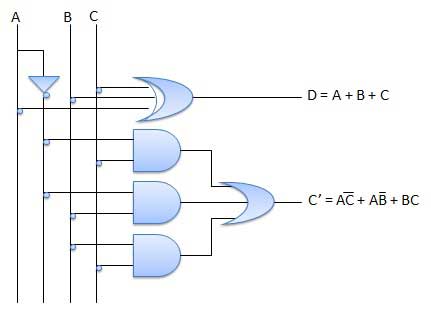

完全な減算器

ハーフサブトラクタの欠点は、フルサブトラクタによって克服されます。フルサブトラクタは、3つの入力A、B、Cと2つの出力DおよびC 'を備えた組み合わせ回路です。Aは「被減数」、Bは「減算」、Cは前のステージで生成された「借用」、Dは差分出力、Cは借用出力です。

真理値表

回路図

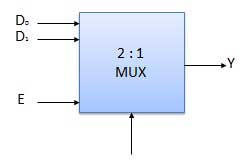

マルチプレクサ

マルチプレクサは、特殊なタイプの組み合わせ回路です。n個のデータ入力、1個の出力、および2m = nのm個の選択入力があります。これは、n個のデータ入力の1つを選択し、それを出力にルーティングするデジタル回路です。n個の入力の1つを選択するには、選択した入力を使用します。選択した入力に適用されるデジタルコードに応じて、n個のデータソースから1つが選択され、単一の出力Yに送信されます。Eはストロボまたはイネーブル入力と呼ばれ、カスケードに役立ちます。これは通常、アクティブロー端子です。つまり、ローのときに必要な操作を実行します。

ブロック図

マルチプレクサには複数のバリエーションがあります

- 2:1マルチプレクサ

- 4:1マルチプレクサ

- 16:1マルチプレクサ

- 32:1マルチプレクサ

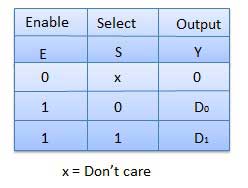

ブロック図

真理値表

デマルチプレクサ

デマルチプレクサは、マルチプレクサの逆の動作を実行します。つまり、1つの入力を受け取り、それを複数の出力に分配します。入力は1つ、出力はn、選択入力はmです。一度に1つの出力ラインのみが選択ラインによって選択され、入力は選択された出力ラインに送信されます。デマルチプレクサは、図1に示すように単極多方向スイッチに相当します。

デマルチプレクサには複数のバリエーションがあります。

- 1:2デマルチプレクサ

- 1:4デマルチプレクサ

- 1:16デマルチプレクサ

- 1:32デマルチプレクサ

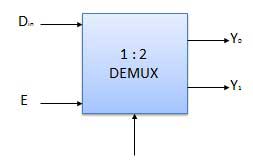

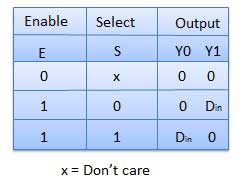

ブロック図

真理値表

デコーダ

デコーダは組み合わせ回路です。入力はn個、出力は最大m = 2nです。デコーダーは、データ入力のないデマルチプレクサーと同じです。エンコーダの操作とは正反対の操作を実行します。

ブロック図

デコーダーの例は次のとおりです。

- コードコンバーター

- BCDから7セグメントデコーダー

- ニキシー管デコーダー

- リレーアクチュエータ

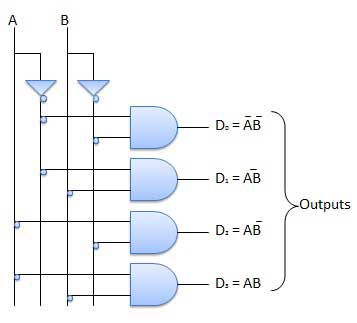

2〜4ラインデコーダー

2〜4ラインデコーダのブロック図を図1に示します。AとBは2つの入力であり、DからDは4つの出力です。真理値表は、デコーダーの動作を説明しています。これは、入力の特定の組み合わせに対してのみ、各出力が1であることを示しています。

ブロック図

真理値表

論理回路

エンコーダー

エンコーダは、デコーダの逆演算を実行するように設計された組み合わせ回路です。エンコーダには、n個の入力ラインとm個の出力ラインがあります。エンコーダは、デジタル入力番号に対応するmビットのバイナリコードを生成します。エンコーダはn入力デジタルワードを受け入れ、それをmビットの別のデジタルワードに変換します。

ブロック図

エンコーダーの例は次のとおりです。

- プライオリティエンコーダ

- 10進数からBCDエンコーダ

- 8進数から2進数のエンコーダ

- 16進数から2進数のエンコーダ

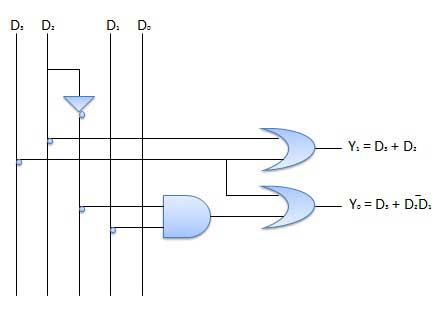

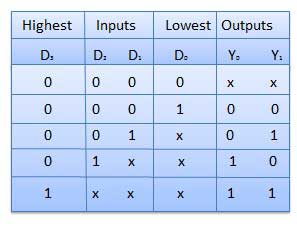

プライオリティエンコーダ

これは特殊なタイプのエンコーダです。入力行が優先されます。2つ以上の入力ラインが同時に1の場合、最も優先度の高い入力ラインが考慮されます。4つの入力Dあり0、D 1、D 2、D 3と2つの出力Y 0、Y 1。4つの入力のうち、D 3が最高の優先度を持ち、D0が最低の優先度を持ちます。つまり、D 3 = 1の場合、他の入力に関係なく、Y 1 Y 1 = 11になります。同様にDもし3 = 0及びD 2 = 1次に、Y 1 Y 0に関わらず、他の入力= 10。

ブロック図

真理値表

論理回路