デジタルレジスタ

フリップフロップは、デジタルデータの保存に使用できる1ビットのメモリセルです。ビット数の観点からストレージ容量を増やすには、フリップフロップのグループを使用する必要があります。このようなフリップフロップのグループは、Register。ザ・n-bit register で構成されます n フリップフロップの数とそれを保存することができます n-bit 語。

レジスタ内のバイナリデータは、レジスタ内で1つのフリップフロップから別のフリップフロップに移動できます。このようなデータ転送を可能にするレジスタは、次のように呼ばれます。shift registers。シフトレジスタの動作には4つのモードがあります。

- シリアル入力シリアル出力

- シリアル入力パラレル出力

- パラレル入力シリアル出力

- パラレル入力パラレル出力

シリアル入力シリアル出力

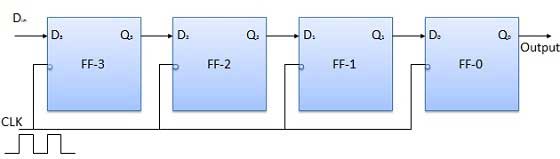

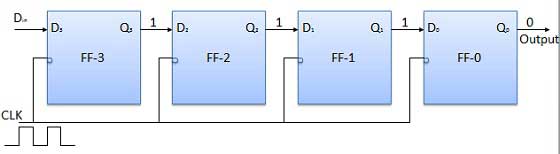

すべてのフリップフロップを最初はリセット状態、つまりQ 3 = Q 2 = Q 1 = Q 0 = 0とします。4ビットの2進数11 1 1をレジスタに入力する場合、この数値は次のようになります。に適用されますDinLSBビットが最初に適用されたビット。FF-3、すなわちDのD入力3は、シリアルデータ入力に接続されています。Din。FF-3、すなわちQの出力3は、すなわちD次のフリップフロップの入力に接続されている2とになります。

ブロック図

操作

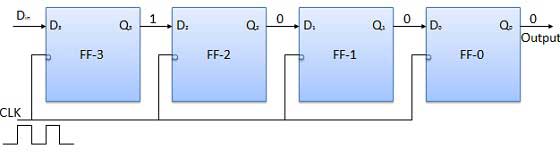

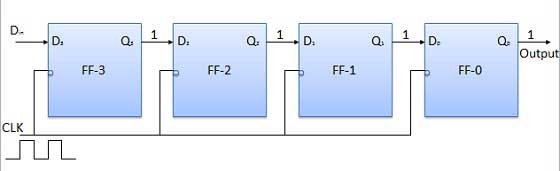

クロック信号を印加する前に、Q 3 Q 2 Q 1 Q 0 = 0000とし、入力する数値のLSBビットをDに印加します。したがって、D in = D 3 = 1です。クロックを適用します。クロックの最初の立ち下がりエッジでFF-3が設定され、レジスタに格納されるワードはQ 3 Q 2 Q 1 Q 0 = 1000です。

次のビットをのDに適用します。したがって、D in = 1です。クロックの次の負のエッジがヒットするとすぐに、FF-2が設定され、格納されているワードがQ 3 Q 2 Q 1 Q 0 = 1100に変更されます。

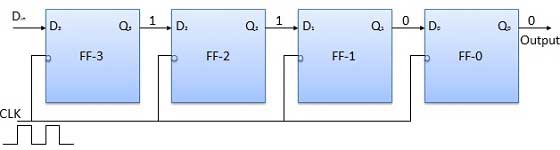

保存する次のビット、つまり1からDを適用します。クロックパルスを適用します。3番目の負のクロックエッジがヒットするとすぐに、FF-1が設定され、出力がQ 3 Q 2 Q 1 Q 0 = 1110に変更されます。

同様に、D in = 1で、4番目の負のクロックエッジが到着すると、レジスタに格納されるワードはQ 3 Q 2 Q 1 Q 0 = 1111です。

真理値表

波形

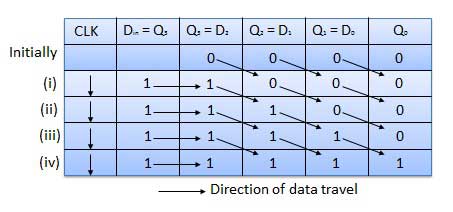

シリアル入力パラレル出力

このようなタイプの操作では、データはシリアルに入力され、並列に取り出されます。

データは少しずつロードされます。データがロードされている限り、出力は無効になります。

データのロードが完了するとすぐに、すべてのフリップフロップに必要なデータが含まれ、出力が有効になり、ロードされたすべてのデータがすべての出力ラインで同時に使用できるようになります。

4ビットワードをロードするには、4クロックサイクルが必要です。したがって、SIPOモードの動作速度はSISOモードの動作速度と同じです。

ブロック図

パラレル入力シリアル出力(PISO)

データビットは並列に入力されます。

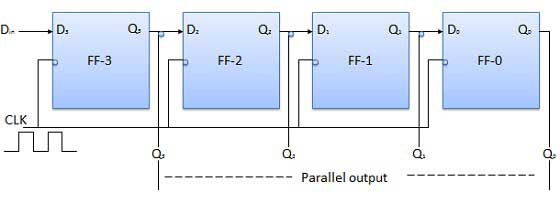

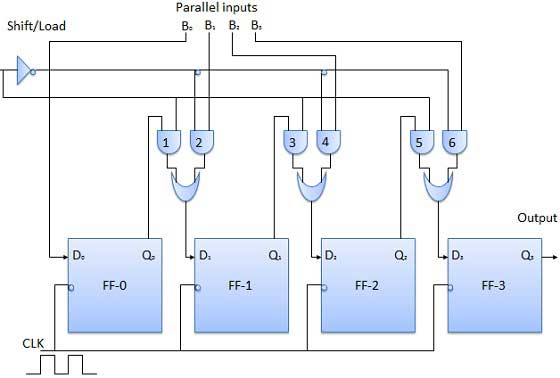

以下に示す回路は、4ビットのパラレル入力シリアル出力レジスタです。

前のフリップフロップの出力は、組み合わせ回路を介して次のフリップフロップの入力に接続されます。

バイナリ入力ワードB0、B 1、B 2、B 3は、同じ組み合わせ回路を介して適用されます。

この回路が機能できるモードには、シフトモードとロードモードの2つがあります。

ロードモード

シフト/ロードバーライン(0)が低い場合には、ANDゲート2、4及びそれらがB通過するアクティブになっ6 1、B 2、B 3ビットには、対応するフリップフロップ。クロックの低い立ち上がりエッジ、バイナリ入力Bに0、B 1、B 2、B 3は対応するにロードされますフリップフロップ。したがって、並列ロードが行われます。

シフトモード

シフト/ロードバーラインが低い場合(1)、ANDゲート2、4、および6は非アクティブになります。したがって、データの並列ロードは不可能になります。ただし、ANDゲート1、3、および5がアクティブになります。したがって、クロックパルスの適用時にデータをビットごとに左から右にシフトします。したがって、パラレルインシリアルアウト操作が行われます。

ブロック図

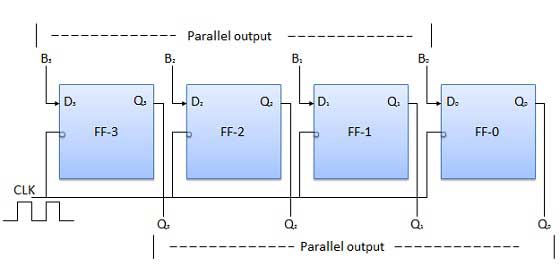

パラレル入力パラレル出力(PIPO)

このモードでは、図4は、バイナリ入力ビットb 0、B 1、B 2はB、3はデータ入力に印加されるD 0、D 1、D 2、D 3はそれぞれ4個のフリップフロップのを。負のクロックエッジが適用されるとすぐに、入力バイナリビットがフリップフロップに同時にロードされます。ロードされたビットは、出力側に同時に表示されます。すべてのビットをロードするには、クロックパルスのみが不可欠です。

ブロック図

双方向シフトレジスタ

2進数を左に1桁シフトすると、元の数値に2を掛けることになります。同様に、2進数を右に1桁シフトすると、元の数値を2で割ることになります。

したがって、シフトレジスタを使用して、指定された2進数を乗算および除算する場合は、データを左方向または右方向に移動できるはずです。

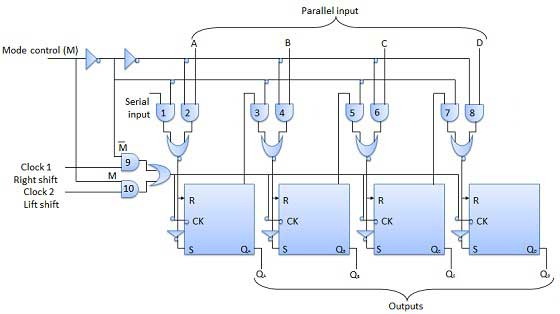

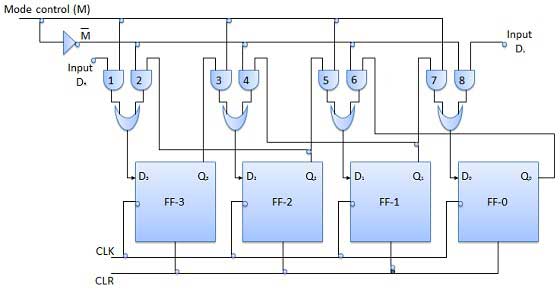

このようなレジスタは双方向レジスタと呼ばれます。4ビットの双方向シフトレジスタを図1に示します。

シリアル右シフトデータ入力DRとシリアル左シフトデータ入力DLの2つのシリアル入力と、モード選択入力(M)があります。

ブロック図

操作

| SN | 状態 | 操作 |

|---|---|---|

| 1 | With M = 1 − Shift right operation | M = 1の場合、ANDゲート1、3、5、および7が有効になり、残りのANDゲート2、4、6、および8は無効になります。 D Rのデータは、クロックパルスの適用時にFF-3からFF-0にビットごとに右にシフトされます。したがって、M = 1の場合、シリアル右シフト演算が得られます。 |

| 2 | With M = 0 − Shift left operation | モード制御Mが0に接続されている場合、ANDゲート2、4、6、および8が有効になり、1、3、5、および7が無効になります。 D Lのデータは、クロックパルスの適用時にFF-0からFF-3にビットごとに左にシフトされます。したがって、M = 0の場合、シリアル右シフト演算が得られます。 |

ユニバーサルシフトレジスタ

データを一方向にのみシフトできるシフトレジスタを単方向シフトレジスタと呼びます。データを両方向にシフトできるシフトレジスタを双方向シフトレジスタと呼びます。同じロジックを適用して、データを両方向にシフトし、並列にロードできるシフトレジスタは、ユニバーサルシフトレジスタと呼ばれます。シフトレジスタは次の操作を実行できます-

- 並列ロード

- 左シフト

- 右シフト

モード制御入力は、パラレルロード操作の場合はロジック1に接続され、シリアルシフトの場合は0に接続されます。モード制御ピンがグランドに接続されている場合、ユニバーサルシフトレジスタは双方向レジスタとして機能します。シリアルレフト操作の場合、入力は、図に示すANDゲート-1に向かうシリアル入力に適用されます。一方、右シフト操作の場合、シリアル入力はD入力に適用されます。

ブロック図