Sirkuit Digital - Pengunci

Ada dua jenis elemen memori berdasarkan jenis pemicuan yang cocok untuk mengoperasikannya.

- Latches

- Flip-flops

Latch beroperasi dengan mengaktifkan sinyal, yaitu level sensitive. Padahal, sandal jepit sensitif terhadap tepi. Kami akan membahas tentang sandal jepit di bab selanjutnya. Nah sekarang mari kita bahas tentang SR Latch & D Latch satu persatu.

SR Latch

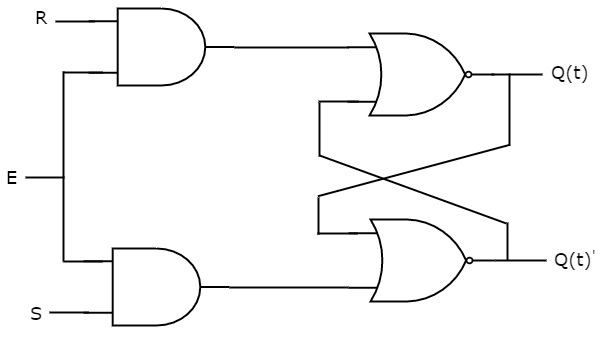

SR Latch juga disebut sebagai Set Reset Latch. Latch ini mempengaruhi output selama pengaktifan, E dipertahankan pada '1'. Itucircuit diagram SR Latch ditunjukkan pada gambar berikut.

Sirkuit ini memiliki dua input S & R dan dua output Q (t) & Q (t) '. Ituupper NOR gate memiliki dua masukan R & melengkapi keadaan sekarang, Q (t) 'dan menghasilkan keadaan berikutnya, Q (t + 1) saat diaktifkan, E adalah' 1 '.

Demikian pula dengan lower NOR gate memiliki dua input S & keadaan sekarang, Q (t) dan menghasilkan komplemen keadaan selanjutnya, Q (t + 1) 'saat diaktifkan, E adalah' 1 '.

Kami tahu bahwa a 2-input NOR gatemenghasilkan keluaran, yang merupakan komplemen dari masukan lain jika salah satu masukannya adalah '0'. Demikian pula, ia menghasilkan keluaran '0', ketika salah satu masukannya adalah '1'.

Jika S = 1, maka status selanjutnya Q (t + 1) akan sama dengan '1' terlepas dari nilai Q (t) saat ini.

Jika R = 1, maka status selanjutnya Q (t + 1) akan sama dengan '0' terlepas dari nilai Q (t) saat ini.

Setiap saat, hanya dari dua masukan itu yang harus '1'. Jika kedua masukan adalah '1', maka nilai Q (t + 1) keadaan selanjutnya tidak terdefinisi.

Tabel berikut menunjukkan state table dari kait SR.

| S | R | Q (t + 1) |

|---|---|---|

| 0 | 0 | Q (t) |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | - |

Oleh karena itu, SR Latch melakukan tiga jenis fungsi seperti Hold, Set & Reset berdasarkan kondisi input.

D Latch

Ada satu kelemahan SR Latch. Artinya, nilai status selanjutnya tidak dapat diprediksi jika kedua input S & R adalah satu. Jadi kita bisa mengatasi kesulitan ini dengan D Latch. Ini juga disebut sebagai Data Latch. Itucircuit diagram dari D Latch ditunjukkan pada gambar berikut.

Sirkuit ini memiliki input D tunggal dan dua output Q (t) & Q (t) '. D Latch didapat dari SR Latch dengan menempatkan inverter antara input S amp; & R dan menghubungkan input D ke S. Artinya kita menghilangkan kombinasi S & R yang nilainya sama.

Jika D = 0 → S = 0 & R = 1, maka status selanjutnya Q (t + 1) akan sama dengan '0' terlepas dari nilai Q (t) saat ini. Ini sesuai dengan baris kedua tabel status SR Latch.

Jika D = 1 → S = 1 & R = 0, maka status selanjutnya Q (t + 1) akan sama dengan '1' terlepas dari nilai-nilai Q (t) saat ini. Ini sesuai dengan baris ketiga tabel status SR Latch.

Tabel berikut menunjukkan state table dari kait D.

| D | Q (t + 1) |

|---|---|

| 0 | 0 |

| 1 | 1 |

Oleh karena itu, D Latch Menyimpan informasi yang tersedia pada masukan data, D. Artinya, keluaran D Latch sensitif terhadap perubahan masukan, D selama pengaktifannya Tinggi.

Dalam bab ini, kami menerapkan berbagai Latch dengan menyediakan kopling silang antara gerbang NOR. Demikian pula, Anda dapat mengimplementasikan Latch ini menggunakan gerbang NAND.