Sirkuit Digital - Panduan Cepat

Jika basis atau radix dari sistem bilangan adalah 'r', maka bilangan yang ada dalam sistem bilangan itu berkisar dari nol hingga r-1. Jumlah total yang ada dalam sistem bilangan itu adalah 'r'. Jadi, kita akan mendapatkan berbagai sistem bilangan, dengan memilih nilai radix lebih besar dari atau sama dengan dua.

Dalam bab ini, mari kita bahas tentang popular number systemsdan bagaimana merepresentasikan angka di sistem angka masing-masing. Sistem angka berikut adalah yang paling umum digunakan.

- Sistem Angka Desimal

- Sistem Bilangan Biner

- Sistem Angka Oktal

- Sistem Bilangan Heksadesimal

Sistem Angka Desimal

Itu base atau radix dari sistem bilangan desimal adalah 10. Jadi, angka mulai dari 0 hingga 9 digunakan dalam sistem angka ini. Bagian bilangan yang terletak di sebelah kiridecimal pointdikenal sebagai bagian integer. Demikian pula, bagian dari bilangan yang terletak di sebelah kanan koma desimal dikenal sebagai bagian pecahan.

Dalam sistem bilangan ini, posisi berturut-turut di sebelah kiri koma desimal berbobot 10 0 , 10 1 , 10 2 , 10 3 dan seterusnya. Demikian pula posisi berurutan di sebelah kanan koma desimal yang memiliki bobot 10 -1 , 10 -2 , 10 -3 dan seterusnya. Artinya, setiap posisi memiliki bobot tertentu, yaitupower of base 10

Contoh

Pertimbangkan decimal number 1358.246. Bagian bilangan bulat dari nomor ini adalah 1358 dan bagian pecahan dari nomor ini adalah 0,246. Angka 8, 5, 3 dan 1 memiliki bobot masing-masing 100, 101, 10 2 dan 10 3 . Demikian pula, angka 2, 4 dan 6 memiliki bobot masing-masing 10 -1 , 10 -2 dan 10 -3 .

Mathematically, kita bisa menulisnya sebagai

1358.246 = (1 × 10 3 ) + (3 × 10 2 ) + (5 × 10 1 ) + (8 × 10 0 ) + (2 × 10 -1 ) +

(4 × 10 -2 ) + (6 × 10 -3 )

Setelah menyederhanakan suku-suku sisi kanan, kita akan mendapatkan angka desimal yang ada di sisi kiri.

Sistem Bilangan Biner

Semua sirkuit dan sistem digital menggunakan sistem bilangan biner ini. Itubase atau radix dari sistem bilangan ini 2. Jadi, angka 0 dan 1 digunakan dalam sistem bilangan ini.

Bagian dari nomor yang terletak di sebelah kiri binary pointdikenal sebagai bagian integer. Demikian pula, bagian dari bilangan yang terletak di sebelah kanan titik biner disebut bagian pecahan.

Dalam sistem bilangan ini, posisi berurutan di sebelah kiri titik biner berbobot 2 0 , 2 1 , 2 2 , 2 3 dan seterusnya. Begitu pula dengan posisi berurutan di sebelah kanan titik biner yang memiliki bobot 2 -1 , 2 -2 , 2 -3 dan seterusnya. Artinya, setiap posisi memiliki bobot tertentu, yaitupower of base 2.

Contoh

Pertimbangkan binary number 1101.011. Bagian bilangan bulat dari nomor ini adalah 1101 dan bagian pecahan dari nomor ini adalah 0,011. Angka 1, 0, 1 dan 1 bagian bilangan bulat memiliki bobot masing-masing 2 0 , 2 1 , 2 2 , 2 3 . Demikian pula, angka 0, 1 dan 1 dari bagian pecahan memiliki bobot masing-masing 2 -1 , 2 -2 , 2 -3 .

Mathematically, kita bisa menulisnya sebagai

1101,011 = (1 × 2 3 ) + (1 × 2 2 ) + (0 × 2 1 ) + (1 × 2 0 ) + (0 × 2 -1 ) +

(1 × 2 -2 ) + (1 × 2 -3 )

Setelah menyederhanakan suku-suku ruas kanan, kita akan mendapatkan angka desimal, yang setara dengan bilangan biner di sisi kiri.

Sistem Angka Oktal

Itu base atau radix dari sistem bilangan oktal adalah 8. Jadi, angka mulai dari 0 hingga 7 digunakan dalam sistem angka ini. Bagian bilangan yang terletak di sebelah kirioctal pointdikenal sebagai bagian integer. Demikian pula, bagian dari bilangan yang terletak di sebelah kanan titik oktal dikenal sebagai bagian pecahan.

Dalam sistem bilangan ini, posisi berurutan di sebelah kiri titik oktal berbobot 8 0 , 8 1 , 8 2 , 8 3 dan seterusnya. Begitu pula dengan posisi berurutan di sebelah kanan titik oktal yang berbobot 8 -1 , 8 -2 , 8 -3 dan seterusnya. Artinya, setiap posisi memiliki bobot tertentu, yaitupower of base 8.

Contoh

Pertimbangkan octal number 1457.236. Bagian bilangan bulat dari nomor ini adalah 1457 dan bagian pecahan dari nomor ini adalah 0,236. Angka 7, 5, 4 dan 1 memiliki bobot masing-masing 8 0 , 8 1 , 8 2 dan 8 3 . Demikian pula, angka 2, 3, dan 6 memiliki bobot masing-masing 8 -1 , 8 -2 , 8 -3 .

Mathematically, kita bisa menulisnya sebagai

1457,236 = (1 × 8 3 ) + (4 × 8 2 ) + (5 × 8 1 ) + (7 × 8 0 ) + (2 × 8 -1 ) +

(3 × 8 -2 ) + (6 × 8 -3 )

Setelah menyederhanakan suku-suku ruas kanan, kita akan mendapatkan angka desimal, yang setara dengan bilangan oktal di sisi kiri.

Sistem Angka Heksadesimal

Itu base atau radix dari sistem bilangan heksa-desimal adalah 16. Jadi, angka mulai dari 0 sampai 9 dan huruf dari A sampai F digunakan dalam sistem bilangan ini. Persamaan desimal dari digit heksa-desimal dari A ke F adalah 10 sampai 15.

Bagian dari nomor yang terletak di sebelah kiri hexadecimal pointdikenal sebagai bagian integer. Demikian pula, bagian dari bilangan yang terletak di sebelah kanan koma desimal Heksa disebut sebagai bagian pecahan.

Dalam sistem bilangan ini, posisi berurutan di sebelah kiri koma desimal Hexa berbobot 16 0 , 16 1 , 16 2 , 16 3 dan seterusnya. Demikian pula, posisi berurutan di sebelah kanan koma desimal heksa memiliki bobot 16 -1 , 16 -2 , 16 -3 dan seterusnya. Artinya, setiap posisi memiliki bobot tertentu, yaitupower of base 16.

Contoh

Pertimbangkan Hexa-decimal number 1A05.2C4. Bagian bilangan bulat dari nomor ini adalah 1A05 dan bagian pecahan dari nomor ini adalah 0.2C4. Angka 5, 0, A dan 1 memiliki bobot masing-masing 16 0 , 16 1 , 16 2 dan 16 3 . Demikian pula, angka 2, C dan 4 memiliki bobot masing-masing 16 -1 , 16 -2 dan 16 -3 .

Mathematically, kita bisa menulisnya sebagai

1A05.2C4 = (1 × 16 3 ) + (10 × 16 2 ) + (0 × 16 1 ) + (5 × 16 0 ) + (2 × 16 -1 ) +

(12 × 16 -2 ) + (4 × 16 -3 )

Setelah menyederhanakan suku-suku sisi kanan, kita akan mendapatkan angka desimal, yang setara dengan angka desimal-heksa di sisi kiri.

Pada bab sebelumnya, kita telah melihat empat sistem bilangan yang menonjol. Dalam bab ini, mari kita ubah bilangan dari satu sistem bilangan ke bilangan lainnya untuk menemukan nilai yang setara.

Konversi Bilangan Desimal ke Basis Lain

Jika bilangan desimal berisi bagian bilangan bulat dan pecahan, maka konversikan kedua bagian bilangan desimal tersebut menjadi basis lain satu per satu. Ikuti langkah-langkah ini untuk mengubah bilangan desimal menjadi bilangan ekivalen dari setiap basis 'r'.

Melakukan division dari bagian bilangan bulat dari bilangan desimal dan successive quotientsdengan basis 'r' dan catat sisanya sampai hasil bagi adalah nol. Pertimbangkan sisa-sisa dalam urutan terbalik untuk mendapatkan bagian bilangan bulat dari jumlah yang setara dari basis 'r'. Artinya, sisa pertama dan terakhir masing-masing menunjukkan digit paling signifikan dan digit paling signifikan.

Melakukan multiplication dari bagian pecahan bilangan desimal dan successive fractionsdengan basis 'r' dan catat carry sampai hasilnya nol atau jumlah digit ekuivalen yang diinginkan diperoleh. Pertimbangkan urutan normal muatan untuk mendapatkan bagian pecahan dari bilangan ekivalen alas 'r'.

Konversi Desimal ke Biner

Dua jenis operasi berikut berlangsung, saat mengonversi bilangan desimal menjadi bilangan biner yang setara.

- Pembagian bagian bilangan bulat dan hasil yang berurutan dengan basis 2.

- Perkalian bagian pecahan dan pecahan berurutan dengan basis 2.

Example

Pertimbangkan decimal number 58.25. Di sini, bagian bilangan bulat adalah 58 dan bagian pecahan adalah 0,25.

Step 1 - Divisi 58 dan hasil yang berurutan dengan basis 2.

| Operasi | Hasil bagi | Sisa |

|---|---|---|

| 58/2 | 29 | 0 (LSB) |

| 29/2 | 14 | 1 |

| 14/2 | 7 | 0 |

| 7/2 | 3 | 1 |

| 3/2 | 1 | 1 |

| 1/2 | 0 | 1(MSB) |

⇒ (58) 10 = (111010) 2

Oleh karena itu, integer part dari bilangan biner yang setara adalah 111010.

Step 2 - Perkalian 0,25 dan pecahan berurutan dengan basis 2.

| Operasi | Hasil | Membawa |

|---|---|---|

| 0,25 x 2 | 0,5 | 0 |

| 0,5 x 2 | 1.0 | 1 |

| - | 0.0 | - |

⇒ (.25) 10 = (.01) 2

Oleh karena itu, fractional part dari bilangan biner yang setara adalah .01

⇒ (58,25) 10 = (111010,01) 2

Oleh karena itu, binary equivalent dari angka desimal 58.25 adalah 111010.01.

Konversi Desimal ke Oktal

Dua jenis operasi berikut berlangsung, saat mengonversi bilangan desimal menjadi bilangan oktal yang setara.

Pembagian bagian bilangan bulat dan hasil perhitungan berurutan dengan basis 8.

Perkalian bagian pecahan dan pecahan berurutan dengan basis 8.

Example

Pertimbangkan decimal number 58.25. Di sini, bagian bilangan bulat adalah 58 dan bagian pecahan adalah 0,25.

Step 1 - Divisi 58 dan hasil akhir yang berurutan dengan basis 8.

| Operasi | Hasil bagi | Sisa |

|---|---|---|

| 58/8 | 7 | 2 |

| 7/8 | 0 | 7 |

⇒ (58) 10 = (72) 8

Oleh karena itu, integer part bilangan oktal yang setara adalah 72.

Step 2 - Perkalian 0,25 dan pecahan berurutan dengan basis 8.

| Operasi | Hasil | Membawa |

|---|---|---|

| 0,25 x 8 | 2.00 | 2 |

| - | 0,00 | - |

⇒ (.25) 10 = (.2) 8

Oleh karena itu, fractional part bilangan oktal ekuivalen adalah .2

⇒ (58.25) 10 = (72.2) 8

Oleh karena itu, octal equivalent dari angka desimal 58.25 adalah 72.2.

Konversi Desimal ke Heksa-Desimal

Dua jenis operasi berikut berlangsung, saat mengonversi bilangan desimal menjadi bilangan heksa-desimal yang setara.

- Pembagian bagian bilangan bulat dan hasil yang berurutan dengan basis 16.

- Perkalian bagian pecahan dan pecahan berurutan dengan basis 16.

Example

Pertimbangkan decimal number 58.25. Di sini, bagian bilangan bulat adalah 58 dan bagian desimal adalah 0,25.

Step 1 - Divisi 58 dan hasil akhir yang berurutan dengan basis 16.

| Operasi | Hasil bagi | Sisa |

|---|---|---|

| 58/16 | 3 | 10 = A |

| 3/16 | 0 | 3 |

⇒ (58) 10 = (3A) 16

Oleh karena itu, integer part dari angka Hexa-desimal yang setara adalah 3A.

Step 2 - Perkalian 0,25 dan pecahan berurutan dengan basis 16.

| Operasi | Hasil | Membawa |

|---|---|---|

| 0,25 x 16 | 4.00 | 4 |

| - | 0,00 | - |

⇒ (.25) 10 = (.4) 16

Oleh karena itu, fractional part dari angka Hexa-desimal yang setara adalah 0,4.

⇒(58.25)10 = (3A.4)16

Oleh karena itu, Hexa-decimal equivalent dari angka desimal 58.25 adalah 3A.4.

Konversi Bilangan Biner ke Basis Lain

Proses mengonversi bilangan dari biner ke desimal berbeda dengan proses pengubahan bilangan biner ke basis lain. Sekarang, mari kita bahas tentang konversi bilangan biner menjadi sistem bilangan desimal, oktal dan heksa-desimal satu per satu.

Konversi Biner ke Desimal

Untuk mengonversi bilangan biner menjadi bilangan desimal ekuivalennya, pertama-tama kalikan bit bilangan biner dengan bobot posisional masing-masing, lalu tambahkan semua produk tersebut.

Example

Pertimbangkan binary number 1101.11.

Mathematically, kita bisa menulisnya sebagai

(1101,11) 2 = (1 × 2 3 ) + (1 × 2 2 ) + (0 × 2 1 ) + (1 × 2 0 ) + (1 × 2 -1 ) +

(1 × 2 -2 )

⇒ (1101,11) 2 = 8 + 4 + 0 + 1 + 0,5 + 0,25 = 13,75

⇒ (1101,11) 2 = (13,75) 10

Oleh karena itu, decimal equivalent dari bilangan biner 1101.11 adalah 13.75.

Konversi Biner ke Oktal

Kita tahu bahwa basis sistem bilangan biner dan oktal masing-masing adalah 2 dan 8. Tiga bit bilangan biner setara dengan satu digit oktal, karena 2 3 = 8.

Ikuti dua langkah ini untuk mengubah bilangan biner menjadi bilangan oktal yang ekuivalen.

Mulai dari titik biner dan buat kelompok 3 bit di kedua sisi titik biner. Jika satu atau dua bit lebih kecil saat membuat grup dari 3 bit, maka masukkan jumlah nol yang diperlukan pada sisi ekstrim.

Tuliskan angka oktal yang sesuai dengan setiap kelompok 3 bit.

Example

Pertimbangkan binary number 101110.01101.

Step 1 - Buat grup 3 bit di kedua sisi titik biner.

101 110.011 01

Di sini, di sisi kanan titik biner, grup terakhir hanya memiliki 2 bit. Jadi, masukkan satu nol di sisi ekstrem untuk menjadikannya sebagai kelompok 3 bit.

⇒ 101 110.011 010

Step 2 - Tulis digit oktal yang sesuai untuk setiap kelompok 3 bit.

⇒ (101110.011 010) 2 = (56.32) 8

Oleh karena itu, octal equivalent dari bilangan biner 101110.01101 adalah 56.32.

Konversi Biner ke Heksa-Desimal

Kita tahu bahwa basis sistem bilangan biner dan heksa-desimal adalah 2 dan 16. Empat bit bilangan biner setara dengan satu digit heksa-desimal, karena 2 4 = 16.

Ikuti dua langkah ini untuk mengonversi bilangan biner menjadi bilangan heksa-desimal yang setara.

Mulai dari titik biner dan buat grup 4 bit di kedua sisi titik biner. Jika beberapa bit lebih kecil saat membuat grup dari 4 bit, maka sertakan jumlah nol yang diperlukan pada sisi yang ekstrim.

Tuliskan digit Heksa-desimal yang sesuai untuk setiap kelompok 4 bit.

Example

Pertimbangkan binary number 101110.01101

Step 1 - Buat kelompok 4 bit di kedua sisi titik biner.

10 1110.0110 1

Di sini, grup pertama hanya memiliki 2 bit. Jadi, sertakan dua angka nol di sisi ekstrim untuk menjadikannya sebagai kelompok 4 bit. Demikian pula, sertakan tiga angka nol pada sisi ekstrim untuk membuat grup terakhir juga sebagai grup 4 bit.

⇒ 0010 1110,0110 1000

Step 2 - Tulis digit heksa-desimal yang sesuai dengan setiap kelompok 4 bit.

⇒ (0010 1110.0110 1000) 2 = (2E.68) 16

Oleh karena itu, Hexa-decimal equivalent dari bilangan biner 101110.01101 adalah (2E.68).

Konversi Bilangan Oktal ke Basis Lain

Proses pengubahan bilangan oktal ke desimal berbeda dengan proses pengubahan bilangan oktal ke basis lain. Sekarang, mari kita bahas tentang konversi bilangan oktal menjadi sistem bilangan desimal, biner dan heksa-desimal satu per satu.

Konversi Oktal ke Desimal

Untuk mengonversi bilangan oktal menjadi bilangan desimal ekuivalennya, pertama-tama kalikan digit bilangan oktal dengan bobot posisional masing-masing, lalu tambahkan semua hasil kali tersebut.

Example

Pertimbangkan octal number 145.23.

Mathematically, kita bisa menulisnya sebagai

(145,23) 8 = (1 × 8 2 ) + (4 × 8 1 ) + (5 × 8 0 ) + (2 × 8 -1 ) + (3 × 8 -2 )

⇒ (145,23) 8 = 64 + 32 + 5 + 0,25 + 0,05 = 101,3

⇒ (145,23) 8 = (101,3) 10

Oleh karena itu, decimal equivalent dari angka oktal 145,23 adalah 101,3.

Konversi Oktal ke Biner

Proses untuk mengubah bilangan oktal menjadi bilangan biner yang setara adalah kebalikan dari proses konversi biner ke oktal. Dengan merepresentasikan setiap digit oktal dengan 3 bit, kita akan mendapatkan bilangan biner yang setara.

Example

Pertimbangkan octal number 145.23.

Mewakili setiap digit oktal dengan 3 bit.

(145.23) 8 = (001 100 101.010 011) 2

Nilai tidak berubah dengan menghilangkan angka nol, yang berada di sisi ekstrim.

⇒ (145.23) 8 = (1100101.010011) 2

Oleh karena itu, binary equivalent dari bilangan oktal 145.23 adalah 1100101.010011.

Konversi Oktal ke Heksa-Desimal

Ikuti dua langkah ini untuk mengubah bilangan oktal menjadi bilangan desimal Hexa yang setara.

- Ubah bilangan oktal menjadi bilangan biner ekivalennya.

- Ubah bilangan biner di atas menjadi bilangan desimal Hexa yang setara.

Example

Pertimbangkan octal number 145.23

Dalam contoh sebelumnya, kita mendapatkan bilangan oktal yang setara biner 145.23 sebagai 1100101.010011.

Dengan mengikuti prosedur konversi biner ke heksa-desimal, kita akan mendapatkan

(1100101.010011) 2 = (65.4C) 16

⇒ (145,23) 8 = (65,4C) 16

Oleh karena itu, Hexa-decimal equivalentdari oktal nomor 145,23 adalah 65,4 C .

Konversi Bilangan Heksa-Desimal ke Basis Lain

Proses mengonversi bilangan dari Heksa-desimal ke desimal berbeda dengan proses pengubahan bilangan heksa-desimal menjadi basis lain. Sekarang mari kita bahas tentang konversi bilangan heksa-desimal menjadi sistem bilangan desimal, biner dan oktal satu per satu.

Konversi Heksa-Desimal ke Desimal

Untuk mengonversi bilangan desimal heksa menjadi bilangan desimal ekuivalennya, pertama-tama kalikan digit bilangan desimal heksa dengan bobot posisi masing-masing, lalu tambahkan semua produk tersebut.

Example

Pertimbangkan Hexa-decimal number 1A5.2

Mathematically, kita bisa menulisnya sebagai

(1A5.2) 16 = (1 × 16 2 ) + (10 × 16 1 ) + (5 × 16 0 ) + (2 × 16 -1 )

⇒ (1A5.2) 16 = 256 + 160 + 5 + 0,125 = 421,125

⇒ (1A5.2) 16 = (421.125) 10

Oleh karena itu, decimal equivalent dari bilangan Hexa-desimal 1A5.2 adalah 421.125.

Konversi Heksa-Desimal ke Biner

Proses mengonversi bilangan heksa-desimal menjadi bilangan biner yang setara adalah kebalikan dari konversi biner ke heksa-desimal. Dengan merepresentasikan setiap digit heksa-desimal dengan 4 bit, kita akan mendapatkan angka biner yang setara.

Example

Pertimbangkan Hexa-decimal number 65.4C

Mewakili setiap digit heksa-desimal dengan 4 bit.

(65.4C) 6 = (0110 0101.0100 1100) 2

Nilai tidak berubah dengan menghilangkan angka nol, yang berada di dua sisi ekstrim.

⇒ (65.4C) 16 = (1100101.010011) 2

Oleh karena itu, binary equivalent dari bilangan Hexa-desimal 65.4C adalah 1100101.010011.

Konversi Heksa-Desimal ke Oktal

Ikuti dua langkah ini untuk mengonversi bilangan desimal heksa menjadi bilangan oktal ekuivalennya.

- Ubah bilangan desimal heksa menjadi bilangan biner ekuivalennya.

- Ubah bilangan biner di atas menjadi bilangan oktal ekuivalennya.

Example

Pertimbangkan Hexa-decimal number 65.4C

Dalam contoh sebelumnya, kita mendapatkan persamaan biner dari bilangan desimal Hexa 65.4C sebagai 1100101.010011.

Dengan mengikuti prosedur konversi biner ke oktal, kita akan mendapatkan

(1100101.010011) 2 = (145.23) 8

⇒ (65,4C) 16 = (145,23)

Oleh karena itu, octal equivalentdari bilangan Hexa-desimal 65,4 C adalah 145,23.

Kita dapat membuat bilangan biner menjadi dua kelompok berikut - Unsigned numbers dan Signed numbers.

Nomor Tak Bertanda Tangan

Nomor tak bertanda tangan hanya berisi besaran angka. Mereka tidak memiliki tanda apapun. Itu berarti semua bilangan biner unsigned adalah positif. Seperti dalam sistem bilangan desimal, penempatan tanda positif di depan bilangan bersifat opsional untuk merepresentasikan bilangan positif. Oleh karena itu, semua bilangan positif termasuk nol dapat dianggap sebagai bilangan unsigned jika tidak ada tanda positif di depan bilangan tersebut.

Nomor yang Ditandatangani

Bilangan bertanda tangan mengandung tanda dan besarnya bilangan tersebut. Umumnya, tanda diletakkan di depan nomor. Jadi, kita harus memperhatikan tanda positif untuk bilangan positif dan tanda negatif untuk bilangan negatif. Oleh karena itu, semua nomor dapat diperlakukan sebagai nomor bertanda jika tanda yang sesuai ditetapkan di depan nomor tersebut.

Jika bit tanda adalah nol, yang menunjukkan bilangan biner positif. Demikian pula jika bit tanda adalah satu, yang menunjukkan bilangan biner negatif.

Representasi Bilangan Biner Tak Bertanda Tangan

Bit yang ada dalam bilangan biner bertanda tangan memegang magnitudedari sebuah angka. Artinya, jika bilangan biner yang tidak bertanda tangan berisi‘N’ bit, lalu semuanya N bit mewakili besarnya angka, karena tidak memiliki bit tanda apa pun.

Example

Pertimbangkan decimal number 108. Persamaan biner dari angka ini adalah1101100. Ini adalah representasi dari bilangan biner unsigned.

(108) 10 = (1101100) 2

Ini memiliki 7 bit. 7 bit ini mewakili besarnya angka 108.

Representasi Bilangan Biner yang Ditandatangani

Bit Paling Signifikan (MSB) dari bilangan biner bertanda digunakan untuk menunjukkan tanda bilangan tersebut. Oleh karena itu, ini juga disebut sebagaisign bit. Tanda positif diwakili dengan menempatkan '0' di bit tanda. Demikian pula, tanda negatif diwakili dengan menempatkan '1' di bit tanda.

Jika bilangan biner bertanda berisi bit 'N', maka (N-1) bit hanya mewakili besaran bilangan tersebut karena satu bit (MSB) dicadangkan untuk mewakili tanda bilangan tersebut.

Ada tiga types of representations untuk bilangan biner bertanda

- Bentuk Sign-Magnitude

- Bentuk pelengkap 1

- Bentuk pelengkap 2

Representasi bilangan positif di semua 3 bentuk ini sama. Namun, hanya representasi bilangan negatif yang akan berbeda di setiap bentuk.

Example

Pertimbangkan positive decimal number +108. Persamaan biner dari besaran bilangan ini adalah 1101100. 7 bit ini mewakili besaran bilangan 108. Karena ini adalah bilangan positif, anggap bit tanda sebagai nol, yang ditempatkan di sisi paling kiri besaran.

(+108) 10 = (01101100) 2

Oleh karena itu, signed binary representationdari angka desimal positif +108 adalah. Jadi, representasi yang sama berlaku dalam bentuk besaran-besaran, bentuk komplemen 1 dan bentuk komplemen 2 untuk bilangan desimal positif +108.

Bentuk Sign-Magnitude

Dalam bentuk sign-magnitude, MSB digunakan untuk merepresentasikan sign dari bilangan tersebut dan bit yang tersisa mewakili magnitudedari nomor tersebut. Jadi, cukup masukkan bit tanda di sisi paling kiri dari bilangan biner unsigned. Representasi ini mirip dengan representasi bilangan desimal bertanda.

Example

Pertimbangkan negative decimal number -108. Besarnya bilangan ini adalah 108. Kita mengetahui representasi biner unsigned dari 108 adalah 1101100. Ini memiliki 7 bit. Semua bit ini mewakili besarnya.

Karena bilangan yang diberikan adalah negatif, anggap bit tanda sebagai satu, yang ditempatkan di sisi paling kiri besarnya.

(−108) 10 = (11101100) 2

Oleh karena itu, representasi besaran -108 tanda adalah 11101100.

Bentuk pelengkap 1

Komplemen angka 1 diperoleh dengan complementing all the bitsdari bilangan biner bertanda. Jadi, pelengkap 1 dari bilangan positif menghasilkan bilangan negatif. Demikian pula, komplemen 1 dari bilangan negatif memberikan bilangan positif.

Artinya, jika Anda melakukan komplemen dua kali 1 dari bilangan biner termasuk bit tanda, maka Anda akan mendapatkan bilangan biner bertanda asli.

Example

Pertimbangkan negative decimal number -108. Besarnya angka ini adalah 108. Kita mengetahui representasi biner bertanda 108 adalah 01101100.

Ini memiliki 8 bit. MSB dari angka ini adalah nol, yang menunjukkan angka positif. Komplemen nol adalah satu dan sebaliknya. Jadi, gantikan nol dengan satu dan satu dengan nol untuk mendapatkan angka negatif.

(−108) 10 = (10010011) 2

Oleh karena itu, 1’s complement of (108)10 adalah (10010011)2.

Bentuk pelengkap 2

Komplemen 2 dari bilangan biner diperoleh dengan adding one to the 1’s complementdari bilangan biner bertanda. Jadi, komplemen 2 dari bilangan positif memberikan bilangan negatif. Demikian pula, pelengkap bilangan negatif 2 memberikan bilangan positif.

Artinya, jika Anda melakukan komplemen dua kali 2 dari bilangan biner termasuk bit tanda, maka Anda akan mendapatkan bilangan biner bertanda asli.

Example

Pertimbangkan negative decimal number -108.

Kami tahu pelengkap 1 dari (108)10 adalah (10010011)2

Pujian 2 dari (108) 10 = 1 dari (108) 10 + 1.

= 10010011 + 1

= 10010100

Oleh karena itu, 2’s complement of (108)10 adalah (10010100)2.

Dalam bab ini, mari kita bahas tentang operasi aritmatika dasar, yang dapat dilakukan pada dua bilangan biner bertanda mana pun menggunakan metode komplemen 2. Itubasic arithmetic operations adalah penjumlahan dan pengurangan.

Penambahan dua Bilangan Biner Bertanda

Pertimbangkan dua bilangan biner bertanda A & B, yang direpresentasikan dalam bentuk komplemen 2. Kami dapat melakukanadditiondari kedua bilangan ini, yang mirip dengan penjumlahan dua bilangan biner unsigned. Namun, jika hasil penjumlahannya berisi perintah dari bit tanda, maka buang (abaikan) untuk mendapatkan nilai yang benar.

Jika hasil penjumlahannya positif, Anda dapat mencari besarnya secara langsung. Tetapi, jika hasil penjumlahannya negatif, maka ambil komplemen 2 untuk mendapatkan besarannya.

Contoh 1

Mari kita lakukan addition dari dua angka desimal +7 and +4 menggunakan metode komplemen 2.

Itu 2’s complement representasi dari +7 dan +4 dengan masing-masing 5 bit ditampilkan di bawah ini.

(+7) 10 = (00111) 2

(+4) 10 = (00100) 2

Penambahan kedua bilangan tersebut adalah

(+7) 10 + (+ 4) 10 = (00111) 2 + (00100) 2

⇒ (+7) 10 + (+ 4) 10 = (01011) 2 .

Jumlah yang dihasilkan berisi 5 bit. Jadi, tidak ada pelaksanaan dari tanda sedikit. Bit tanda '0' menunjukkan bahwa jumlah yang dihasilkan adalahpositive. Jadi, besaran penjumlahannya adalah 11 dalam sistem bilangan desimal. Oleh karena itu, penjumlahan dua bilangan positif akan menghasilkan bilangan positif lainnya.

Contoh 2

Mari kita lakukan addition dari dua angka desimal -7 dan -4 menggunakan metode komplemen 2.

Itu 2’s complement representasi -7 dan -4 dengan masing-masing 5 bit ditampilkan di bawah ini.

(−7) 10 = (11001) 2

(−4) 10 = (11100) 2

Penambahan kedua bilangan tersebut adalah

(−7) 10 + (−4) 10 = (11001) 2 + (11100) 2

⇒ (−7) 10 + (−4) 10 = (110101) 2 .

Jumlah yang dihasilkan berisi 6 bit. Dalam hal ini, carry diperoleh dari bit tanda. Jadi, kita bisa menghapusnya

Jumlah resultan setelah menghilangkan carry adalah (−7) 10 + (−4) 10 =(10101)2.

Tanda bit '1' menunjukkan bahwa jumlah yang dihasilkan adalah negative. Jadi, dengan mengambil komplemen 2 kita akan mendapatkan besaran resultan jumlah 11 dalam sistem bilangan desimal. Oleh karena itu, penambahan dua angka negatif akan menghasilkan angka negatif lainnya.

Pengurangan dua Bilangan Biner Bertanda

Pertimbangkan dua bilangan biner bertanda A & B, yang direpresentasikan dalam bentuk komplemen 2. Kita tahu bahwa komplemen 2 dari bilangan positif menghasilkan bilangan negatif. Jadi, setiap kali kita harus mengurangi bilangan B dari bilangan A, ambil komplemen B 2 dan tambahkan ke A. Jadi,mathematically kita bisa menulisnya sebagai

A - B = A + (2's complement of B)

Demikian pula, jika kita harus mengurangkan bilangan A dari bilangan B, ambil komplemen A 2 dan tambahkan ke B. Jadi, mathematically kita bisa menulisnya sebagai

B - A = B + (2's complement of A)

Jadi pengurangan dua bilangan biner bertanda sama dengan penjumlahan dua bilangan biner bertanda. Tapi, kita harus mengambil komplemen angka 2, yang seharusnya dikurangkan. Ini adalahadvantagedari teknik komplemen 2. Ikuti, aturan yang sama dari penjumlahan dua bilangan biner bertanda.

Contoh 3

Mari kita lakukan subtraction dari dua angka desimal +7 and +4 menggunakan metode komplemen 2.

Pengurangan kedua bilangan ini adalah

(+7) 10 - (+4) 10 = (+7) 10 + (−4) 10 .

Itu 2’s complement representasi dari +7 dan -4 dengan masing-masing 5 bit ditampilkan di bawah ini.

(+7) 10 = (00111) 2

(+4) 10 = (11100) 2

⇒ (+7) 10 + (+4) 10 = (00111) 2 + (11100) 2 = (00011) 2

Di sini, carry didapat dari tanda bit. Jadi, kita bisa menghapusnya. Jumlah yang dihasilkan setelah menghapus carry adalah

(+7) 10 + (+4) 10 =(00011)2

Bit tanda '0' menunjukkan bahwa jumlah yang dihasilkan adalah positive. Jadi, besarnya adalah 3 dalam sistem bilangan desimal. Oleh karena itu, pengurangan dua bilangan desimal +7 dan +4 adalah +3.

Contoh 4

Mari kita lakukan subtraction of dua angka desimal +4 dan +7 menggunakan metode komplemen 2.

Pengurangan kedua bilangan ini adalah

(+4) 10 - (+7) 10 = (+4) 10 + (−7) 10 .

Itu 2’s complement representasi dari +4 dan -7 dengan masing-masing 5 bit ditampilkan di bawah ini.

(+4) 10 = (00100) 2

(-7) 10 = (11001) 2

⇒ (+4) 10 + (-7) 10 = (00100) 2 + (11001) 2 = (11101) 2

Di sini, carry tidak didapat dari bit sign. Tanda bit '1' menunjukkan bahwa jumlah yang dihasilkan adalahnegative. Jadi, dengan mengambil komplemen 2 nya kita akan mendapatkan besaran resultan jumlah 3 dalam sistem bilangan desimal. Oleh karena itu, pengurangan dua bilangan desimal +4 dan +7 adalah -3.

Dalam pengkodean, ketika angka atau huruf diwakili oleh sekelompok simbol tertentu, dikatakan bahwa angka atau huruf itu sedang dikodekan. Kelompok simbol disebut sebagaicode. Data digital direpresentasikan, disimpan dan ditransmisikan sebagai sekelompok bit. Kelompok bit ini juga disebut sebagaibinary code.

Kode biner dapat diklasifikasikan menjadi dua jenis.

- Kode berbobot

- Kode tidak berbobot

Jika kode memiliki bobot posisi, maka dikatakan weighted code. Jika tidak, itu adalah kode tidak berbobot. Kode berbobot lebih lanjut dapat diklasifikasikan sebagai kode berbobot positif dan kode berbobot negatif.

Kode Biner untuk angka Desimal

Tabel berikut menunjukkan berbagai kode biner untuk angka desimal 0 hingga 9.

| Digit Desimal | 8421 Kode | 2421 Kode | 84-2-1 Kode | Kelebihan 3 Kode |

|---|---|---|---|---|

| 0 | 0000 | 0000 | 0000 | 0011 |

| 1 | 0001 | 0001 | 0111 | 01.00 |

| 2 | 0010 | 0010 | 0110 | 0101 |

| 3 | 0011 | 0011 | 0101 | 0110 |

| 4 | 01.00 | 01.00 | 01.00 | 0111 |

| 5 | 0101 | 1011 | 1011 | 1000 |

| 6 | 0110 | 1100 | 1010 | 1001 |

| 7 | 0111 | 1101 | 1001 | 1010 |

| 8 | 1000 | 1110 | 1000 | 1011 |

| 9 | 1001 | 1111 | 1111 | 1100 |

Kami memiliki 10 digit dalam sistem bilangan desimal. Untuk merepresentasikan 10 digit ini dalam biner, kami membutuhkan minimal 4 bit. Tapi, dengan 4 bit akan ada 16 kombinasi unik dari nol dan satu. Karena, kami hanya memiliki 10 digit desimal, 6 kombinasi lain dari nol dan satu tidak diperlukan.

8 4 2 1 kode

Bobot dari kode ini adalah 8, 4, 2 dan 1.

Kode ini memiliki semua bobot positif. Jadi, ini adalah apositively weighted code.

Kode ini juga disebut sebagai natural BCD (Desimal Berkode Biner) code.

Example

Mari kita cari BCD yang setara dengan bilangan desimal 786. Bilangan ini memiliki 3 angka desimal 7, 8 dan 6. Dari tabel tersebut, kita dapat menuliskan kode BCD (8421) dari 7, 8 dan 6 masing-masing adalah 0111, 1000 dan 0110 .

∴ (786)10 = (011110000110)BCD

Ada 12 bit dalam representasi BCD, karena setiap kode BCD digit desimal memiliki 4 bit.

2 4 2 1 kode

Bobot dari kode ini adalah 2, 4, 2 dan 1.

Kode ini memiliki semua bobot positif. Jadi, ini adalah apositively weighted code.

Ini adalah sebuah unnatural BCDkode. Jumlah bobot kode BCD yang tidak wajar sama dengan 9.

Ini adalah sebuah self-complementingkode. Kode pelengkap sendiri menyediakan komplemen 9 dari angka desimal, hanya dengan menukar 1 dan 0 dalam representasi setara 2421.

Example

Mari kita cari 2421 ekuivalen angka desimal 786. Angka ini memiliki 3 angka desimal 7, 8 dan 6. Dari tabel tersebut, kita dapat menuliskan 2421 kode dari 7, 8 dan 6 masing-masing adalah 1101, 1110 dan 1100.

Oleh karena itu, 2421 ekivalen dengan angka desimal 786 adalah 110111101100.

8 4 -2 -1 kode

Bobot dari kode ini adalah 8, 4, -2 dan -1.

Kode ini memiliki bobot negatif bersama dengan bobot positif. Jadi, ini adalah anegatively weighted code.

Ini adalah sebuah unnatural BCD kode.

Ini adalah sebuah self-complementing kode.

Example

Mari kita cari 8 4-2-1 ekuivalen angka desimal 786. Angka ini memiliki 3 angka desimal 7, 8 dan 6. Dari tabel tersebut, kita bisa menuliskan 8 4 -2 -1 kode 7, 8 dan 6 masing-masing adalah 1001, 1000 dan 1010.

Oleh karena itu, 8 4 -2 -1 setara dengan angka desimal 786 adalah 100110001010.

Kelebihan 3 kode

Kode ini tidak memiliki bobot apa pun. Jadi, ini adalahun-weighted code.

Kita akan mendapatkan kode Kelebihan 3 dari angka desimal dengan menambahkan tiga (0011) ke biner yang setara dengan angka desimal itu. Oleh karena itu, ini disebut sebagai kode Kelebihan 3.

Ini adalah sebuah self-complementing kode.

Example

Mari kita cari Kelebihan 3 yang setara dengan angka desimal 786. Angka ini memiliki 3 angka desimal 7, 8 dan 6. Dari tabel tersebut, kita dapat menuliskan kode Kelebihan 3 dari 7, 8 dan 6 masing-masing adalah 1010, 1011 dan 1001.

Oleh karena itu, Kelebihan 3 setara dengan angka desimal 786 adalah 101010111001

Kode Abu-abu

Tabel berikut menunjukkan kode Gray 4-bit yang sesuai dengan setiap kode biner 4-bit.

| Angka desimal | Kode biner | Kode Abu-abu |

|---|---|---|

| 0 | 0000 | 0000 |

| 1 | 0001 | 0001 |

| 2 | 0010 | 0011 |

| 3 | 0011 | 0010 |

| 4 | 01.00 | 0110 |

| 5 | 0101 | 0111 |

| 6 | 0110 | 0101 |

| 7 | 0111 | 01.00 |

| 8 | 1000 | 1100 |

| 9 | 1001 | 1101 |

| 10 | 1010 | 1111 |

| 11 | 1011 | 1110 |

| 12 | 1100 | 1010 |

| 13 | 1101 | 1011 |

| 14 | 1110 | 1001 |

| 15 | 1111 | 1000 |

Kode ini tidak memiliki bobot apa pun. Jadi, ini adalahun-weighted code.

Pada tabel di atas, kode Gray berturut-turut dibedakan dalam satu posisi bit saja. Karenanya, kode ini disebut sebagaiunit distance kode.

Kode biner ke Konversi Kode Gray

Ikuti langkah-langkah ini untuk mengubah kode biner menjadi kode Gray yang setara.

Pertimbangkan kode biner yang diberikan dan letakkan nol di sebelah kiri MSB.

Bandingkan dua bit berturut-turut mulai dari nol. Jika 2 bitnya sama, maka outputnya nol. Jika tidak, keluarannya adalah satu.

Ulangi langkah di atas sampai kode LSB dari Gray diperoleh.

Example

Dari tabel tersebut, kita mengetahui bahwa kode Gray yang sesuai dengan kode biner 1000 adalah 1100. Sekarang, mari kita verifikasi dengan menggunakan prosedur di atas.

Diberikan, kode biner adalah 1000.

Step 1 - Dengan menempatkan nol di sebelah kiri MSB, kode biner akan menjadi 01000.

Step 2 - Dengan membandingkan dua bit kode biner baru yang berurutan, kita akan mendapatkan kode abu-abu sebagai 1100.

Kita tahu bahwa bit 0 dan 1 sesuai dengan dua rentang tegangan analog yang berbeda. Jadi, selama transmisi data biner dari satu sistem ke sistem lainnya, noise juga dapat ditambahkan. Karena ini, mungkin ada kesalahan dalam data yang diterima di sistem lain.

Itu berarti bit 0 bisa berubah menjadi 1 atau bit 1 bisa berubah menjadi 0. Kita tidak bisa menghindari interferensi noise. Tapi, kita bisa mendapatkan kembali data asli terlebih dahulu dengan mendeteksi apakah ada kesalahan dan kemudian mengoreksi kesalahan tersebut. Untuk tujuan ini, kita dapat menggunakan kode-kode berikut.

- Kode deteksi kesalahan

- Kode koreksi kesalahan

Error detection codes- digunakan untuk mendeteksi kesalahan yang ada dalam data yang diterima (aliran bit). Kode-kode ini berisi beberapa bit, yang disertakan (ditambahkan) ke aliran bit asli. Kode-kode ini mendeteksi kesalahan, jika itu terjadi selama transmisi data asli (aliran bit).Example - Kode paritas, kode Hamming.

Error correction codes- digunakan untuk memperbaiki kesalahan yang ada pada data yang diterima (aliran bit) sehingga, kita akan mendapatkan data asli. Kode koreksi kesalahan juga menggunakan strategi serupa dari kode deteksi kesalahan.Example - Kode Hamming.

Oleh karena itu, untuk mendeteksi dan memperbaiki kesalahan, bit tambahan ditambahkan ke bit data pada saat transmisi.

Kode Paritas

Sangat mudah untuk memasukkan (menambahkan) satu bit paritas baik di sebelah kiri MSB atau di sebelah kanan LSB dari aliran bit asli. Ada dua jenis kode paritas yaitu kode paritas genap dan kode paritas ganjil berdasarkan jenis paritas yang dipilih.

Bahkan Kode Paritas

Nilai bit paritas genap harus nol, jika bilangan genap yang ada dalam kode biner. Jika tidak, itu harus menjadi satu. Sehingga, jumlah yang genap ada dieven parity code. Bahkan kode paritas berisi bit data dan bahkan bit paritas.

Tabel berikut menunjukkan even parity codessesuai dengan setiap kode biner 3-bit. Di sini, bit paritas genap disertakan di sebelah kanan LSB kode biner.

| Kode biner | Bahkan paritas sedikit | Bahkan Kode Paritas |

|---|---|---|

| 000 | 0 | 0000 |

| 001 | 1 | 0011 |

| 010 | 1 | 0101 |

| 011 | 0 | 0110 |

| 100 | 1 | 1001 |

| 101 | 0 | 1010 |

| 110 | 0 | 1100 |

| 111 | 1 | 1111 |

Di sini, jumlah bit yang ada dalam kode paritas genap adalah 4. Jadi, kemungkinan bilangan genap yang mungkin ada dalam kode paritas genap ini adalah 0, 2 & 4.

Jika sistem lain menerima salah satu dari kode paritas genap ini, maka tidak ada kesalahan dalam data yang diterima. Bit selain bit paritas genap sama dengan bit kode biner.

If the other system receives other than even parity codes, then there will be an error(s) in the received data. In this case, we can’t predict the original binary code because we don’t know the bit position(s) of error.

Therefore, even parity bit is useful only for detection of error in the received parity code. But, it is not sufficient to correct the error.

Odd Parity Code

The value of odd parity bit should be zero, if odd number of ones present in the binary code. Otherwise, it should be one. So that, odd number of ones present in odd parity code. Odd parity code contains the data bits and odd parity bit.

The following table shows the odd parity codes corresponding to each 3-bit binary code. Here, the odd parity bit is included to the right of LSB of binary code.

| Binary Code | Odd Parity bit | Odd Parity Code |

|---|---|---|

| 000 | 1 | 0001 |

| 001 | 0 | 0010 |

| 010 | 0 | 0100 |

| 011 | 1 | 0111 |

| 100 | 0 | 1000 |

| 101 | 1 | 1011 |

| 110 | 1 | 1101 |

| 111 | 0 | 1110 |

Here, the number of bits present in the odd parity codes is 4. So, the possible odd number of ones in these odd parity codes are 1 & 3.

If the other system receives one of these odd parity codes, then there is no error in the received data. The bits other than odd parity bit are same as that of binary code.

If the other system receives other than odd parity codes, then there is an error(s) in the received data. In this case, we can’t predict the original binary code because we don’t know the bit position(s) of error.

Therefore, odd parity bit is useful only for detection of error in the received parity code. But, it is not sufficient to correct the error.

Hamming Code

Hamming code is useful for both detection and correction of error present in the received data. This code uses multiple parity bits and we have to place these parity bits in the positions of powers of 2.

The minimum value of 'k' for which the following relation is correct (valid) is nothing but the required number of parity bits.

$$2^k\geq n+k+1$$

Where,

‘n’ is the number of bits in the binary code (information)

‘k’ is the number of parity bits

Therefore, the number of bits in the Hamming code is equal to n + k.

Let the Hamming code is $b_{n+k}b_{n+k-1}.....b_{3}b_{2}b_{1}$ & parity bits $p_{k}, p_{k-1}, ....p_{1}$. We can place the ‘k’ parity bits in powers of 2 positions only. In remaining bit positions, we can place the ‘n’ bits of binary code.

Based on requirement, we can use either even parity or odd parity while forming a Hamming code. But, the same parity technique should be used in order to find whether any error present in the received data.

Follow this procedure for finding parity bits.

Find the value of p1, based on the number of ones present in bit positions b3, b5, b7 and so on. All these bit positions (suffixes) in their equivalent binary have ‘1’ in the place value of 20.

Find the value of p2, based on the number of ones present in bit positions b3, b6, b7 and so on. All these bit positions (suffixes) in their equivalent binary have ‘1’ in the place value of 21.

Find the value of p3, based on the number of ones present in bit positions b5, b6, b7 and so on. All these bit positions (suffixes) in their equivalent binary have ‘1’ in the place value of 22.

Similarly, find other values of parity bits.

Follow this procedure for finding check bits.

Find the value of c1, based on the number of ones present in bit positions b1, b3, b5, b7 and so on. All these bit positions (suffixes) in their equivalent binary have ‘1’ in the place value of 20.

Find the value of c2, based on the number of ones present in bit positions b2, b3, b6, b7 and so on. All these bit positions (suffixes) in their equivalent binary have ‘1’ in the place value of 21.

Find the value of c3, based on the number of ones present in bit positions b4, b5, b6, b7 and so on. All these bit positions (suffixes) in their equivalent binary have ‘1’ in the place value of 22.

Similarly, find other values of check bits.

The decimal equivalent of the check bits in the received data gives the value of bit position, where the error is present. Just complement the value present in that bit position. Therefore, we will get the original binary code after removing parity bits.

Example 1

Let us find the Hamming code for binary code, d4d3d2d1 = 1000. Consider even parity bits.

The number of bits in the given binary code is n=4.

We can find the required number of parity bits by using the following mathematical relation.

$$2^k\geq n+k+1$$

Substitute, n=4 in the above mathematical relation.

$$\Rightarrow 2^k\geq 4+k+1$$

$$\Rightarrow 2^k\geq 5+k$$

The minimum value of k that satisfied the above relation is 3. Hence, we require 3 parity bits p1, p2, and p3. Therefore, the number of bits in Hamming code will be 7, since there are 4 bits in binary code and 3 parity bits. We have to place the parity bits and bits of binary code in the Hamming code as shown below.

The 7-bit Hamming code is $b_{7}b_{6}b_{5}b_{4}b_{3}b_{2}b_{1}=d_{4}d_{3}d_{2}p_{3}d_{1}p_{2}bp_{1}$

By substituting the bits of binary code, the Hamming code will be $b_{7}b_{6}b_{5}b_{4}b_{3}b_{2}b_{1} = 100p_{3}Op_{2}p_{1}$. Now, let us find the parity bits.

$$p_{1}=b_{7}\oplus b_{5}\oplus b_{3}=1 \oplus 0 \oplus 0=1$$

$$p_{2}=b_{7}\oplus b_{6}\oplus b_{3}=1 \oplus 0 \oplus 0=1$$

$$p_{3}=b_{7}\oplus b_{6}\oplus b_{5}=1 \oplus 0 \oplus 0=1$$

By substituting these parity bits, the Hamming code will be $b_{7}b_{6}b_{5}b_{4}b_{3}b_{2}b_{1}= 1001011$.

Example 2

In the above example, we got the Hamming code as $b_{7}b_{6}b_{5}b_{4}b_{3}b_{2}b_{1}= 1001011$. Now, let us find the error position when the code received is $b_{7}b_{6}b_{5}b_{4}b_{3}b_{2}b_{1}= 1001111$.

Now, let us find the check bits.

$$c_{1}=b_{7}\oplus b_{5}\oplus b_{3}\oplus b_{1}=1 \oplus 0 \oplus 1 \oplus1 =1$$

$$c_{2}=b_{7}\oplus b_{6}\oplus b_{3}\oplus b_{2}=1 \oplus 0 \oplus 1 \oplus1 =1$$

$$c_{3}=b_{7}\oplus b_{6}\oplus b_{5}\oplus b_{4}=1 \oplus 0 \oplus 0 \oplus1 =0$$

The decimal value of check bits gives the position of error in received Hamming code.

$$c_{3}c_{2}c_{1} = \left ( 011 \right )_{2}=\left ( 3 \right )_{10}$$

Therefore, the error present in third bit (b3) of Hamming code. Just complement the value present in that bit and remove parity bits in order to get the original binary code.

Boolean Algebra is an algebra, which deals with binary numbers & binary variables. Hence, it is also called as Binary Algebra or logical Algebra. A mathematician, named George Boole had developed this algebra in 1854. The variables used in this algebra are also called as Boolean variables.

The range of voltages corresponding to Logic ‘High’ is represented with ‘1’ and the range of voltages corresponding to logic ‘Low’ is represented with ‘0’.

Postulates and Basic Laws of Boolean Algebra

In this section, let us discuss about the Boolean postulates and basic laws that are used in Boolean algebra. These are useful in minimizing Boolean functions.

Boolean Postulates

Consider the binary numbers 0 and 1, Boolean variable (x) and its complement (x’). Either the Boolean variable or complement of it is known as literal. The four possible logical OR operations among these literals and binary numbers are shown below.

x + 0 = x

x + 1 = 1

x + x = x

x + x '= 1

Demikian pula empat kemungkinan logical AND operasi antara literal dan bilangan biner tersebut ditunjukkan di bawah ini.

x.1 = x

x.0 = 0

xx = x

x.x '= 0

Ini adalah postulat Boolean sederhana. Kita dapat memverifikasi dalil ini dengan mudah, dengan mengganti variabel Boolean dengan '0' atau '1'.

Note- Komplemen dari variabel Boolean sama dengan variabel itu sendiri. yaitu, (x ')' = x.

Hukum Dasar Aljabar Boolean

Berikut adalah tiga hukum dasar Aljabar Boolean.

- Hukum komutatif

- Hukum asosiatif

- Hukum distributif

Hukum Komutatif

Jika ada operasi logika dari dua variabel Boolean memberikan hasil yang sama terlepas dari urutan kedua variabel tersebut, maka operasi logis tersebut dikatakan Commutative. Operasi logika OR & logika AND dari dua variabel Boolean x & y ditunjukkan di bawah ini

x + y = y + x

xy = yx

Simbol '+' menunjukkan operasi OR logis. Begitu pula dengan simbol '.' menunjukkan operasi AND yang logis dan opsional untuk diwakili. Hukum komutatif mematuhi untuk operasi logis OR & logis AND.

Hukum Asosiatif

Jika operasi logika dari dua variabel Boolean dilakukan terlebih dahulu dan kemudian operasi yang sama dilakukan dengan variabel yang tersisa memberikan hasil yang sama, maka operasi logis tersebut dikatakan Associative. Operasi logika OR & logika AND dari tiga variabel Boolean x, y & z ditunjukkan di bawah ini.

x + (y + z) = (x + y) + z

x. (yz) = (xy) .z

Hukum asosiatif mematuhi untuk operasi logis OR & logis AND.

Hukum distributif

Jika ada operasi logika yang dapat didistribusikan ke semua istilah yang ada dalam fungsi Boolean, maka operasi logis tersebut dikatakan Distributive. Distribusi operasi logika OR & logika AND dari tiga variabel Boolean x, y & z ditunjukkan di bawah ini.

x. (y + z) = xy + xz

x + (yz) = (x + y). (x + z)

Hukum distributif mematuhi operasi logika OR dan logika AND.

Ini adalah hukum dasar aljabar Boolean. Kita dapat memverifikasi hukum ini dengan mudah, dengan mengganti variabel Boolean dengan '0' atau '1'.

Teorema Aljabar Boolean

Dua teorema berikut digunakan dalam aljabar Boolean.

- Teorema dualitas

- Teorema DeMorgan

Teorema Dualitas

Teorema ini menyatakan bahwa dualdari fungsi Boolean diperoleh dengan menukar operator logika AND dengan operator logika OR dan nol dengan satu. Untuk setiap fungsi Boolean, akan ada fungsi Ganda yang sesuai.

Mari kita buat persamaan (relasi) Boolean yang telah kita bahas di bagian postulat Boolean dan hukum dasar menjadi dua kelompok. Tabel berikut menunjukkan dua kelompok ini.

| Grup 1 | Kelompok2 |

|---|---|

| x + 0 = x | x.1 = x |

| x + 1 = 1 | x.0 = 0 |

| x + x = x | xx = x |

| x + x '= 1 | x.x '= 0 |

| x + y = y + x | xy = yx |

| x + (y + z) = (x + y) + z | x. (yz) = (xy) .z |

| x. (y + z) = xy + xz | x + (yz) = (x + y). (x + z) |

Di setiap baris, ada dua persamaan Boolean dan keduanya rangkap satu sama lain. Kita dapat memverifikasi semua persamaan Boolean dari Grup1 dan Grup2 ini dengan menggunakan teorema dualitas.

Teorema DeMorgan

Teorema ini berguna untuk mencari complement of Boolean function. Ini menyatakan bahwa komplemen logika OR dari setidaknya dua variabel Boolean sama dengan logika AND dari setiap variabel komplemen.

Teorema DeMorgan dengan 2 variabel Boolean x dan y dapat direpresentasikan sebagai

(x + y) '= x'.y'

Rangkap dari fungsi Boolean di atas adalah

(xy) '= x' + y '

Oleh karena itu, komplemen logika AND dari dua variabel Boolean sama dengan logika OR dari setiap variabel komplemen. Demikian pula, kita dapat menerapkan teorema DeMorgan untuk lebih dari 2 variabel Boolean juga.

Penyederhanaan Fungsi Boolean

Sampai saat ini, kita telah membahas postulat, hukum dasar dan teorema aljabar Boolean. Sekarang, mari kita sederhanakan beberapa fungsi Boolean.

Contoh 1

Biarkan kami simplify fungsi Boolean, f = p'qr + pq'r + pqr '+ pqr

Fungsi ini dapat disederhanakan dengan dua metode.

Method 1

Diberikan fungsi Boolean, f = p'qr + pq'r + pqr '+ pqr.

Step 1- Pada suku pertama dan kedua r umum dan pada suku ketiga dan keempat pq umum. Jadi, ambillah istilah umum dengan menggunakanDistributive law.

⇒ f = (p'q + pq ') r + pq (r' + r)

Step 2- Istilah yang ada dalam tanda kurung pertama dapat disederhanakan menjadi operasi Ex-OR. Istilah yang ada dalam tanda kurung kedua dapat disederhanakan menjadi '1' menggunakanBoolean postulate

⇒ f = (p ⊕q) r + pq (1)

Step 3- Istilah pertama tidak dapat disederhanakan lebih lanjut. Namun, suku kedua dapat disederhanakan menjadi pq menggunakanBoolean postulate.

⇒ f = (p ⊕q) r + pq

Oleh karena itu, fungsi Boolean yang disederhanakan adalah f = (p⊕q)r + pq

Method 2

Diberikan fungsi Boolean, f = p'qr + pq'r + pqr '+ pqr.

Step 1 - Gunakan Boolean postulate, x + x = x. Itu berarti, operasi Logical OR dengan variabel Boolean 'n' kali akan sama dengan variabel yang sama. Jadi, kita bisa menulis pqr suku terakhir dua kali lagi.

⇒ f = p'qr + pq'r + pqr '+ pqr + pqr + pqr

Step 2 - Gunakan Distributive lawuntuk 1 st dan 4 th istilah, 2 nd dan 5 th istilah, 3 rd dan 6 th istilah.

⇒ f = qr (p '+ p) + pr (q' + q) + pq (r '+ r)

Step 3 - Gunakan Boolean postulate, x + x '= 1 untuk menyederhanakan suku-suku yang ada di setiap tanda kurung.

⇒ f = qr (1) + pr (1) + pq (1)

Step 4 - Gunakan Boolean postulate, x.1 = x untuk menyederhanakan ketiga suku di atas.

⇒ f = qr + pr + pq

⇒ f = pq + qr + pr

Oleh karena itu, fungsi Boolean yang disederhanakan adalah f = pq + qr + pr.

Jadi, kami mendapatkan dua fungsi Boolean yang berbeda setelah menyederhanakan fungsi Boolean yang diberikan di setiap metode. Secara fungsional, kedua fungsi Boolean itu sama. Jadi, berdasarkan kebutuhan, kita bisa memilih salah satu dari dua fungsi Boolean tersebut.

Contoh 2

Mari kita temukan complement dari fungsi Boolean, f = p'q + pq '.

Komplemen dari fungsi Boolean adalah f '= (p'q + pq') '.

Step 1 - Gunakan teorema DeMorgan, (x + y) '= x'.y'.

⇒ f '= (p'q)'. (Pq ')'

Step 2 - Gunakan teorema DeMorgan, (xy) '= x' + y '

⇒ f '= {(p') '+ q'}. {P '+ (q') '}

Step3 - Gunakan postulat Boolean, (x ')' = x.

⇒ f '= {p + q'}. {P '+ q}

⇒ f '= pp' + pq + p'q '+ qq'

Step 4 - Gunakan postulat Boolean, xx '= 0.

⇒ f = 0 + pq + p'q '+ 0

⇒ f = pq + p'q '

Oleh karena itu, complement dari fungsi Boolean, p'q + pq 'adalah pq + p’q’.

Kita akan mendapatkan empat suku produk Boolean dengan menggabungkan dua variabel x dan y dengan operasi logika AND. Istilah produk Boolean ini disebut sebagaimin terms atau standard product terms. Suku minnya adalah x'y ', x'y, xy' dan xy.

Demikian pula, kita akan mendapatkan empat suku Boolean dengan menggabungkan dua variabel x dan y dengan operasi OR logis. Istilah penjumlahan Boolean ini disebut sebagaiMax terms atau standard sum terms. Suku Max adalah x + y, x + y ', x' + y dan x '+ y'.

Tabel berikut menunjukkan representasi suku min dan suku MAX untuk 2 variabel.

| x | y | Istilah min | Ketentuan maks |

|---|---|---|---|

| 0 | 0 | m 0 = x'y ' | M 0 = x + y |

| 0 | 1 | m 1 = x'y | M 1 = x + y ' |

| 1 | 0 | m 2 = xy ' | M 2 = x '+ y |

| 1 | 1 | m 3 = xy | M 3 = x '+ y' |

Jika variabel biner adalah '0', maka variabel tersebut direpresentasikan sebagai variabel pelengkap dalam istilah min dan sebagai variabel itu sendiri dalam istilah Max. Demikian pula, jika variabel biner adalah '1', maka variabel tersebut direpresentasikan sebagai pelengkap variabel dalam istilah Max dan sebagai variabel itu sendiri dalam istilah min.

Dari tabel di atas, kita dapat dengan mudah melihat bahwa istilah min dan istilah Max saling melengkapi. Jika ada 'n' variabel Boolean, maka akan ada 2 n suku min dan 2 n suku Max.

Bentuk SoP dan PoS kanonis

Tabel kebenaran terdiri dari satu set input dan output. Jika ada variabel input 'n', maka akan ada 2 n kemungkinan kombinasi dengan nol dan satu. Jadi nilai setiap variabel keluaran tergantung dari kombinasi variabel masukan tersebut. Jadi, setiap variabel keluaran akan memiliki '1' untuk beberapa kombinasi variabel masukan dan '0' untuk beberapa kombinasi variabel masukan lainnya.

Oleh karena itu, kita dapat mengekspresikan setiap variabel keluaran dengan dua cara berikut.

- Bentuk SoP Kanonis

- Bentuk PoS kanonis

Bentuk SoP Kanonis

Bentuk SoP Kanonis berarti bentuk Jumlah Produk Kanonis. Dalam bentuk ini, setiap istilah produk mengandung semua literal. Jadi, istilah produk ini tidak lain adalah istilah min. Oleh karena itu, bentuk SoP kanonik juga disebut sebagaisum of min terms bentuk.

Pertama, identifikasi suku-suku min yang variabel keluarannya adalah satu dan kemudian lakukan logika OR suku-suku min tersebut untuk mendapatkan ekspresi Boolean (fungsi) yang sesuai dengan variabel keluaran tersebut. Fungsi Boolean ini akan berupa penjumlahan suku-suku min.

Ikuti prosedur yang sama untuk variabel keluaran lainnya juga, jika ada lebih dari satu variabel keluaran.

Contoh

Simak berikut ini truth table.

| Masukan | Keluaran | ||

|---|---|---|---|

| p | q | r | f |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

Di sini, keluaran (f) adalah '1' untuk empat kombinasi masukan. Istilah min terkait adalah p'qr, pq'r, pqr ', pqr. Dengan melakukan logika OR dari empat suku min ini, kita akan mendapatkan fungsi Boolean dari keluaran (f).

Oleh karena itu, fungsi keluaran Boolean adalah, f = p'qr + pq'r + pqr '+ pqr. Ini adalahcanonical SoP formkeluaran, f. Kami juga dapat mewakili fungsi ini dengan mengikuti dua notasi.

$$f = m_{3}+m_{5}+m_{6}+m_{7}$$

$$f = \sum m\left ( 3,5,6,7 \right )$$

Dalam satu persamaan, kami merepresentasikan fungsi sebagai jumlah dari masing-masing suku min. Dalam persamaan lain, kami menggunakan simbol untuk penjumlahan suku-suku min tersebut.

Bentuk PoS kanonis

Bentuk PoS Kanonis berarti bentuk Produk Kanonis dari Jumlah. Dalam bentuk ini, setiap istilah penjumlahan berisi semua literal. Jadi, istilah penjumlahan ini tidak lain adalah istilah Max. Oleh karena itu, bentuk PoS kanonik juga disebut sebagaiproduct of Max terms bentuk.

Pertama, identifikasi suku-suku Max yang variabel keluarannya nol dan kemudian lakukan logika AND dari suku-suku Max tersebut untuk mendapatkan ekspresi Boolean (fungsi) yang sesuai dengan variabel keluaran tersebut. Fungsi Boolean ini akan berupa perkalian suku Max.

Ikuti prosedur yang sama untuk variabel keluaran lainnya juga, jika ada lebih dari satu variabel keluaran.

Example

Pertimbangkan tabel kebenaran yang sama dari contoh sebelumnya. Di sini, keluaran (f) adalah '0' untuk empat kombinasi masukan. Suku Max yang sesuai adalah p + q + r, p + q + r ', p + q' + r, p '+ q + r. Dengan melakukan logika AND dari keempat suku Max ini, kita akan mendapatkan fungsi Boolean dari keluaran (f).

Oleh karena itu, fungsi keluaran Boolean adalah, f = (p + q + r). (P + q + r ']. (P + q' + r). (P '+ q + r). Ini adalahcanonical PoS formkeluaran, f. Kami juga dapat mewakili fungsi ini dengan mengikuti dua notasi.

$$f=M_{0}.M_{1}.M_{2}.M_{4}$$

$$f=\prod M\left ( 0,1,2,4 \right )$$

Dalam satu persamaan, kami merepresentasikan fungsi sebagai produk dari masing-masing suku Max. Dalam persamaan lain, kami menggunakan simbol untuk perkalian suku-suku Max tersebut.

Fungsi Boolean, f = (p + q + r). (P + q + r '). (P + q' + r). (P '+ q + r) adalah rangkap dari fungsi Boolean, f = p'qr + pq'r + pqr '+ pqr.

Oleh karena itu, bentuk SoP kanonik dan PoS kanonik adalah Dualsatu sama lain. Secara fungsional, kedua bentuk ini sama. Berdasarkan kebutuhan, kita bisa menggunakan salah satu dari dua bentuk ini.

Formulir SoP dan PoS standar

Kami membahas dua bentuk kanonik yang mewakili keluaran Boolean. Demikian pula, ada dua bentuk standar yang mewakili keluaran Boolean. Ini adalah versi bentuk kanonik yang disederhanakan.

- Bentuk SoP standar

- Bentuk PoS standar

Kami akan membahas tentang gerbang Logika di bab selanjutnya. Utamaadvantagebentuk standar adalah bahwa jumlah input yang diterapkan ke gerbang logika dapat diminimalkan. Terkadang, akan ada pengurangan jumlah total gerbang logika yang dibutuhkan.

Bentuk SoP standar

Artinya bentuk SoP standar Standard Sum of Productsbentuk. Dalam bentuk ini, setiap istilah produk tidak harus mengandung semua literal. Jadi, istilah produk mungkin atau mungkin bukan istilah min. Oleh karena itu, formulir SoP Standar adalah bentuk SoP kanonik yang disederhanakan.

Kita akan mendapatkan bentuk variabel keluaran SoP Standar dalam dua langkah.

- Dapatkan bentuk variabel keluaran SoP kanonik

- Sederhanakan fungsi Boolean di atas, yang ada dalam bentuk SoP kanonik.

Ikuti prosedur yang sama untuk variabel keluaran lainnya juga, jika ada lebih dari satu variabel keluaran. Terkadang, formulir SoP kanonik tidak dapat disederhanakan. Dalam hal ini, formulir SoP kanonis dan standar sama.

Example

Ubah fungsi Boolean berikut menjadi bentuk SoP Standar.

f = p'qr + pq'r + pqr '+ pqr

Fungsi Boolean yang diberikan adalah dalam bentuk SoP kanonik. Sekarang, kita harus menyederhanakan fungsi Boolean ini untuk mendapatkan bentuk SoP standar.

Step 1 - Gunakan Boolean postulate, x + x = x. Itu berarti, operasi Logical OR dengan variabel Boolean 'n' kali akan sama dengan variabel yang sama. Jadi, kita bisa menulis pqr suku terakhir dua kali lagi.

⇒ f = p'qr + pq'r + pqr '+ pqr + pqr + pqr

Step 2 - Gunakan Distributive lawuntuk 1 st dan 4 th istilah, 2 nd dan 5 th istilah, 3 rd dan 6 th istilah.

⇒ f = qr (p '+ p) + pr (q' + q) + pq (r '+ r)

Step 3 - Gunakan Boolean postulate, x + x '= 1 untuk menyederhanakan suku-suku yang ada di setiap tanda kurung.

⇒ f = qr (1) + pr (1) + pq (1)

Step 4 - Gunakan Boolean postulate, x.1 = x untuk menyederhanakan tiga suku di atas.

⇒ f = qr + pr + pq

⇒ f = pq + qr + pr

Ini adalah fungsi Boolean yang disederhanakan. Oleh karena itu,standard SoP form sesuai dengan bentuk SoP kanonik yang diberikan f = pq + qr + pr

Bentuk PoS standar

Bentuk standar PoS artinya Standard Product of Sumsbentuk. Dalam bentuk ini, setiap istilah penjumlahan tidak harus mengandung semua literal. Jadi, persyaratan penjumlahan mungkin atau mungkin bukan persyaratan Max. Oleh karena itu, formulir PoS Standar adalah bentuk PoS kanonik yang disederhanakan.

Kita akan mendapatkan bentuk variabel keluaran PoS Standar dalam dua langkah.

- Dapatkan bentuk variabel keluaran PoS kanonik

- Sederhanakan fungsi Boolean di atas, yang ada dalam bentuk PoS kanonis.

Ikuti prosedur yang sama untuk variabel keluaran lainnya juga, jika ada lebih dari satu variabel keluaran. Terkadang, tidak mungkin untuk menyederhanakan formulir PoS kanonik. Dalam hal ini, bentuk PoS kanonik dan standar sama.

Example

Ubah fungsi Boolean berikut menjadi bentuk PoS Standar.

f = (p + q + r). (p + q + r ']. (p + q' + r). (p '+ q + r)

Fungsi Boolean yang diberikan adalah dalam bentuk PoS kanonik. Sekarang, kita harus menyederhanakan fungsi Boolean ini untuk mendapatkan bentuk PoS standar.

Step 1 - Gunakan Boolean postulate, xx = x. Artinya, operasi Logical AND dengan variabel Boolean 'n' kali akan sama dengan variabel yang sama. Jadi, kita bisa menulis suku pertama p + q + r dua kali lagi.

⇒ f = (p + q + r). (P + q + r). (P + q + r). (P + q + r '). (P + q' + r). (P '+ q + r)

Step 2 - Gunakan Distributive law,x + (yz) = (x + y). (x + z) untuk 1 st dan 4 th kurung, 2 nd dan 5 th kurung, 3 rd dan 6 th kurung.

⇒ f = (p + q + rr ']. (P + r + qq']. (Q + r + pp ')

Step 3 - Gunakan Boolean postulate, x.x '= 0 untuk menyederhanakan suku-suku yang ada di setiap tanda kurung.

⇒ f = (p + q + 0). (P + r + 0). (Q + r + 0)

Step 4 - Gunakan Boolean postulate, x + 0 = x untuk menyederhanakan suku-suku yang ada di setiap tanda kurung

⇒ f = (p + q). (P + r). (Q + r)

⇒ f = (p + q). (Q + r). (P + r)

Ini adalah fungsi Boolean yang disederhanakan. Oleh karena itu,standard PoS form sesuai dengan bentuk PoS kanonik yang diberikan f = (p + q).(q + r).(p + r). Ini adalahdual dari fungsi Boolean, f = pq + qr + pr.

Oleh karena itu, baik bentuk SoP Standar dan PoS Standar Ganda satu sama lain.

Pada bab sebelumnya, kita telah menyederhanakan fungsi Boolean menggunakan postulat dan teorema Boolean. Ini adalah proses yang memakan waktu dan kami harus menulis ulang ekspresi yang disederhanakan setelah setiap langkah.

Untuk mengatasi kesulitan ini, Karnaughmemperkenalkan metode penyederhanaan fungsi Boolean dengan cara yang mudah. Metode ini dikenal dengan metode peta Karnaugh atau metode K-map. Ini adalah metode grafis, yang terdiri dari 2 n sel untuk variabel 'n'. Sel yang berdekatan dibedakan hanya dalam posisi bit tunggal.

K-Maps untuk 2 hingga 5 Variabel

Metode K-Map paling cocok untuk meminimalkan fungsi Boolean dari 2 variabel menjadi 5 variabel. Sekarang mari kita bahas tentang K-Maps untuk 2 sampai 5 variabel satu per satu.

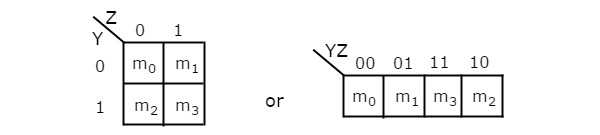

2 Variabel K-Map

Jumlah sel dalam 2 variabel K-map adalah empat, karena jumlah variabel adalah dua. Gambar berikut menunjukkan2 variable K-Map.

Hanya ada satu kemungkinan untuk mengelompokkan 4 suku min yang berdekatan.

Kombinasi yang mungkin dari pengelompokan 2 suku min yang berdekatan adalah {(m 0 , m 1 ), (m 2 , m 3 ), (m 0 , m 2 ) and (m 1 , m 3 )}.

3 Variabel K-Map

Jumlah sel dalam 3 variabel K-map adalah delapan, karena jumlah variabel adalah tiga. Gambar berikut menunjukkan3 variable K-Map.

Hanya ada satu kemungkinan untuk mengelompokkan 8 suku min yang berdekatan.

Kemungkinan kombinasi pengelompokan 4 suku min yang berdekatan adalah {(m 0 , m 1 , m 3 , m 2 ), (m 4 , m 5 , m 7 , m 6 ), (m 0 , m 1 , m 4 , m 5 ), (m 1 , m 3 , m 5 , m 7 ), (m 3 , m 2 , m 7 , m 6 ) and (m 2 , m 0 , m 6 , m 4 )}.

Kemungkinan kombinasi pengelompokan 2 suku min yang berdekatan adalah {(m 0 , m 1 ), (m 1 , m 3 ), (m 3 , m 2 ), (m 2 , m 0 ), (m 4 , m 5 ) , (m 5 , m 7 ), (m 7 , m 6 ), (m 6 , m 4 ), (m 0 , m 4 ), (m 1 , m 5 ), (m 3 , m 7 ) and ( m 2 , m 6 )}.

Jika x = 0, maka 3 variabel K-map menjadi 2 variabel K-map.

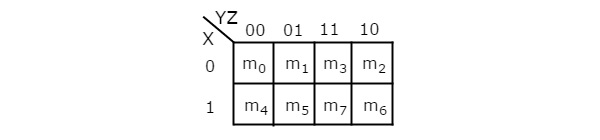

4 Variabel K-Map

Jumlah sel dalam 4 variabel K-map adalah enam belas, karena jumlah variabelnya empat. Gambar berikut menunjukkan4 variable K-Map.

Hanya ada satu kemungkinan untuk mengelompokkan 16 suku min yang berdekatan.

Misal R 1 , R 2 , R 3 dan R 4 masing-masing mewakili suku-suku min dari baris pertama, baris kedua, baris ketiga dan keempat. Demikian pula, C 1 , C 2 , C 3 dan C 4 masing-masing mewakili suku-suku min dari kolom pertama, kolom kedua, kolom ketiga dan kolom keempat. Kombinasi yang mungkin dari pengelompokan 8 suku min yang berdekatan adalah {(R 1 , R 2 ), (R 2 , R 3 ), (R 3 , R 4 ), (R 4 , R 1 ), (C 1 , C 2 ) , (C 2 , C 3 ), (C 3 , C 4 ), (C 4 , C 1 )}.

Jika w = 0, maka 4 variabel K-map menjadi 3 variabel K-map.

5 Variabel K-Map

Jumlah sel dalam 5 variabel K-map adalah tiga puluh dua, karena jumlah variabel adalah 5. Gambar berikut menunjukkan 5 variable K-Map.

Hanya ada satu kemungkinan untuk mengelompokkan 32 suku min yang berdekatan.

Ada dua kemungkinan untuk mengelompokkan 16 suku min yang berdekatan. yaitu, pengelompokan suku-suku min dari m 0 ke m 15 dan m 16 ke m 31 .

Jika v = 0, maka 5 variabel K-map menjadi 4 variabel K-map.

Di atas semua K-maps, kami hanya menggunakan notasi istilah min. Demikian pula, Anda dapat menggunakan notasi istilah Max secara eksklusif.

Meminimalkan Fungsi Boolean menggunakan K-Maps

Jika kita mempertimbangkan kombinasi input yang fungsi Booleannya adalah '1', maka kita akan mendapatkan fungsi Boolean, yaitu di standard sum of products bentuk setelah menyederhanakan K-map.

Demikian pula, jika kita mempertimbangkan kombinasi input yang fungsi Booleannya adalah '0', maka kita akan mendapatkan fungsi Boolean, yaitu di standard product of sums bentuk setelah menyederhanakan K-map.

Ikuti ini rules for simplifying K-maps untuk mendapatkan jumlah standar dari bentuk produk.

Pilih masing-masing K-map berdasarkan jumlah variabel yang ada di fungsi Boolean.

Jika fungsi Boolean diberikan sebagai penjumlahan dari bentuk suku min, letakkan salah satu di sel suku min masing-masing di K-map. Jika fungsi Boolean diberikan sebagai bentuk penjumlahan produk, maka tempatkan satu di semua kemungkinan sel K-map yang istilah produknya valid.

Periksa kemungkinan pengelompokan jumlah maksimum yang berdekatan. Ini harus menjadi kekuatan dua. Mulai dari daya tertinggi dua dan hingga daya terkecil dua. Pangkat tertinggi sama dengan jumlah variabel yang dipertimbangkan dalam K-map dan daya terkecil adalah nol.

Setiap pengelompokan akan menghasilkan istilah produk atau literal. Ini dikenal sebagaiprime implicant. Implikasi utama dikatakanessential prime implicant, jika setidaknya satu '1' tidak tercakup dalam pengelompokan lain tetapi hanya penutup pengelompokan tersebut.

Catat semua implikasi utama dan implikasi utama esensial. Fungsi Boolean yang disederhanakan berisi semua implikasi utama yang penting dan hanya implan utama yang diperlukan.

Note 1 - Jika keluaran tidak ditentukan untuk beberapa kombinasi masukan, maka nilai keluaran tersebut akan diwakili dengan don’t care symbol ‘x’. Artinya, kita dapat menganggapnya sebagai '0' atau '1'.

Note 2- Jika istilah tidak peduli juga ada, maka tempatkan tidak peduli 'x' di sel masing-masing K-map. Pertimbangkan hanya 'x' yang tidak peduli yang berguna untuk mengelompokkan jumlah maksimum yang berdekatan. Dalam kasus tersebut, perlakukan nilai tidak peduli sebagai '1'.

Contoh

Biarkan kami simplify fungsi Boolean berikut, f(W, X, Y, Z)= WX’Y’ + WY + W’YZ’ menggunakan K-map.

Fungsi Boolean yang diberikan adalah dalam bentuk penjumlahan produk. Ini memiliki 4 variabel W, X, Y & Z. Jadi, kami membutuhkan4 variable K-map. Itu4 variable K-map dengan yang sesuai dengan istilah produk yang diberikan ditunjukkan pada gambar berikut.

Di sini, 1s ditempatkan di sel K-map berikut.

Sel-sel yang sama dengan perpotongan Baris 4 dan kolom 1 & 2 berhubungan dengan istilah hasil kali, WX’Y’.

Sel, yang sama dengan perpotongan Baris 3 & 4 dan kolom 3 & 4 sesuai dengan istilah hasil kali, WY.

Sel, yang sama dengan perpotongan Baris 1 & 2 dan kolom 4 sesuai dengan istilah hasil kali, W’YZ’.

Tidak ada kemungkinan pengelompokan baik 16 yang berdekatan atau 8 yang berdekatan. Ada tiga kemungkinan pengelompokan 4 yang berdekatan. Setelah ketiga pengelompokan ini, tidak ada satu pun yang tersisa sebagai tidak dikelompokkan. Jadi, kita tidak perlu memeriksa pengelompokan 2 yang berdekatan. Itu4 variable K-map dengan ketiganya groupings ditunjukkan pada gambar berikut.

Di sini, kami mendapat tiga implan utama WX ', WY & YZ'. Semua implikasi utama iniessential karena alasan berikut.

Dua orang (m8 & m9)Pengelompokan baris keempat tidak tercakup dalam pengelompokan lain. Hanya pengelompokan baris keempat yang mencakup kedua pengelompokan tersebut.

Lajang (m15)pengelompokan bentuk persegi tidak tercakup dalam pengelompokan lain. Hanya pengelompokan bentuk persegi yang mencakup yang satu itu.

Dua orang (m2 & m6)pengelompokan kolom keempat tidak tercakup dalam pengelompokan lain. Hanya pengelompokan kolom keempat yang mencakup kedua kolom tersebut.

Oleh karena itu, simplified Boolean function adalah

f = WX’ + WY + YZ’

Ikuti ini rules for simplifying K-maps untuk mendapatkan produk standar dari bentuk penjumlahan.

Pilih masing-masing K-map berdasarkan jumlah variabel yang ada di fungsi Boolean.

Jika fungsi Boolean diberikan sebagai hasil kali bentuk suku Max, maka letakkan nol di masing-masing sel suku Max di K-map. Jika fungsi Boolean diberikan sebagai hasil perkalian dari bentuk penjumlahan, maka letakkan nol di semua kemungkinan sel K-map yang syarat penjumlahannya valid.

Periksa kemungkinan pengelompokan jumlah maksimum nol yang berdekatan. Ini harus menjadi kekuatan dua. Mulai dari daya tertinggi dua dan hingga daya terkecil dua. Pangkat tertinggi sama dengan jumlah variabel yang dipertimbangkan dalam K-map dan daya terkecil adalah nol.

Setiap pengelompokan akan menghasilkan satu istilah literal atau satu jumlah. Ini dikenal sebagaiprime implicant. Implikasi utama dikatakanessential prime implicant, jika setidaknya satu '0' tidak tercakup dalam pengelompokan lain tetapi hanya penutup pengelompokan tersebut.

Catat semua implikasi utama dan implikasi utama esensial. Fungsi Boolean yang disederhanakan berisi semua implikasi utama yang penting dan hanya implan utama yang diperlukan.

Note- Jika istilah tidak peduli juga ada, maka tempatkan tidak peduli 'x' di sel masing-masing K-map. Pertimbangkan hanya 'x' yang tidak peduli yang berguna untuk mengelompokkan jumlah maksimum nol yang berdekatan. Dalam kasus tersebut, perlakukan nilai tidak peduli sebagai '0'.

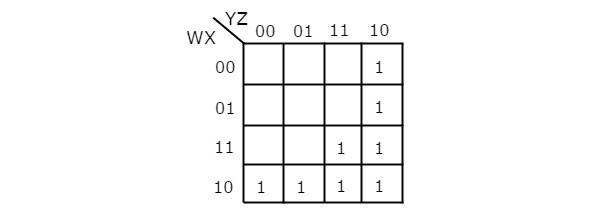

Contoh

Biarkan kami simplify fungsi Boolean berikut, $f\left ( X,Y,Z \right )=\prod M\left ( 0,1,2,4 \right )$ menggunakan K-map.

Fungsi Boolean yang diberikan adalah hasil perkalian dari bentuk istilah Max. Ini memiliki 3 variabel X, Y & Z. Jadi, kita membutuhkan 3 variabel K-map. Suku Max yang diberikan adalah M 0 , M 1 , M 2 & M 4 . 3variable K-map dengan angka nol yang sesuai dengan suku Max yang diberikan ditunjukkan pada gambar berikut.

Tidak ada kemungkinan untuk mengelompokkan 8 angka nol yang berdekatan atau 4 angka nol yang berdekatan. Ada tiga kemungkinan untuk mengelompokkan 2 angka nol yang berdekatan. Setelah ketiga pengelompokan ini, tidak ada satu nol pun yang tersisa sebagai tidak dikelompokkan. Itu3 variable K-map dengan ketiganya groupings ditunjukkan pada gambar berikut.

Di sini, kami mendapat tiga implan utama X + Y, Y + Z & Z + X. Semua implikasi utama ini adalah essential karena satu nol di setiap pengelompokan tidak tercakup oleh pengelompokan lain kecuali dengan pengelompokan individualnya.

Oleh karena itu, simplified Boolean function adalah

f = (X + Y).(Y + Z).(Z + X)

Dengan cara ini, kita dapat dengan mudah menyederhanakan fungsi Boolean hingga 5 variabel menggunakan metode K-map. Untuk lebih dari 5 variabel, sulit untuk menyederhanakan fungsi menggunakan K-Maps. Sebab, banyaknyacells di K-map dapatkan doubled dengan memasukkan variabel baru.

Karena pemeriksaan dan pengelompokan yang berdekatan (istilah min) atau nol yang berdekatan (istilah Max) akan menjadi rumit. Kami akan membahasTabular method pada bab selanjutnya untuk mengatasi kesulitan metode K-map.

Pada bab sebelumnya, kita telah membahas metode K-map, yang merupakan metode yang nyaman untuk meminimalkan fungsi Boolean hingga 5 variabel. Namun, sulit untuk menyederhanakan fungsi Boolean yang memiliki lebih dari 5 variabel dengan menggunakan metode ini.

Metode tabel Quine-McClukey merupakan metode tabel yang didasarkan pada konsep prime implant. Kami tahu ituprime implicant adalah suku produk (atau penjumlahan), yang tidak dapat disederhanakan lagi dengan menggabungkannya dengan suku produk (atau penjumlahan) lainnya dari fungsi Boolean yang diberikan.

Metode tabel ini berguna untuk mendapatkan implikasi utama dengan berulang kali menggunakan identitas Boolean berikut.

xy + xy '= x (y + y') = x.1 = x

Prosedur Metode Tabel Quine-McCluskey

Ikuti langkah-langkah berikut untuk menyederhanakan fungsi Boolean menggunakan metode tabel Quine-McClukey.

Step 1 - Susun suku-suku min yang diberikan dalam sebuah ascending orderdan buat grup berdasarkan jumlah yang ada dalam representasi biner mereka. Jadi, akan adaat most ‘n+1’ groups jika ada 'n' variabel Boolean dalam fungsi Boolean atau bit 'n' dalam ekuivalen biner dari istilah min.

Step 2 - Bandingkan istilah min yang ada di successive groups. Jika hanya ada perubahan dalam posisi satu bit, maka ambil pasangan dari dua suku min tersebut. Letakkan simbol '_' ini pada posisi bit yang berbeda dan pertahankan bit yang tersisa sebagaimana adanya.

Step 3 - Ulangi langkah2 dengan istilah yang baru dibentuk sampai kita mendapatkan semua prime implicants.

Step 4 - Merumuskan prime implicant table. Ini terdiri dari kumpulan baris dan kolom. Implikasi utama dapat ditempatkan dalam baris bijaksana dan istilah min dapat ditempatkan dalam kolom bijaksana. Tempatkan '1' di sel yang sesuai dengan istilah min yang tercakup dalam setiap implik utama.

Step 5- Temukan implan utama yang penting dengan mengamati setiap kolom. Jika suku min hanya dicakup oleh satu implikasi utama, maka suku tersebut adalahessential prime implicant. Implikasi utama esensial tersebut akan menjadi bagian dari fungsi Boolean yang disederhanakan.

Step 6- Kurangi tabel prime implant dengan menghilangkan baris dari setiap prime implant penting dan kolom-kolom yang sesuai dengan istilah min yang tercakup dalam prime implant esensial tersebut. Ulangi langkah 5 untuk tabel Implikasi utama yang dikurangi. Hentikan proses ini ketika semua syarat minimum dari fungsi Boolean yang diberikan sudah berakhir.

Contoh

Biarkan kami simplify fungsi Boolean berikut, $f\left ( W,X,Y,Z \right )=\sum m\left ( 2,6,8,9,10,11,14,15 \right )$ menggunakan metode tabel Quine-McClukey.

Fungsi Boolean yang diberikan ada di sum of min termsbentuk. Ia memiliki 4 variabel W, X, Y & Z. Suku-suku min yang diberikan adalah 2, 6, 8, 9, 10, 11, 14 dan 15. Urutan menaik suku-suku min ini berdasarkan jumlah suku yang ada dalam suku-suku tersebut. ekuivalen biner adalah 2, 8, 6, 9, 10, 11, 14 dan 15. Tabel berikut menunjukkan inimin terms and their equivalent binary representasi.

| Nama grup | Istilah min | W | X | Y | Z |

|---|---|---|---|---|---|

| GA1 | 2 | 0 | 0 | 1 | 0 |

| 8 | 1 | 0 | 0 | 0 | |

| GA2 | 6 | 0 | 1 | 1 | 0 |

| 9 | 1 | 0 | 0 | 1 | |

| 10 | 1 | 0 | 1 | 0 | |

| 11 | 1 | 0 | 1 | 1 | |

| 14 | 1 | 1 | 1 | 0 | |

| GA4 | 15 | 1 | 1 | 1 | 1 |

Suku-suku min yang diberikan disusun menjadi 4 kelompok berdasarkan jumlah suku yang ada dalam persamaan binernya. Tabel berikut menunjukkan kemungkinanmerging of min terms dari kelompok yang berdekatan.

| Nama grup | Istilah min | W | X | Y | Z |

|---|---|---|---|---|---|

| GB1 | 2,6 | 0 | - | 1 | 0 |

| 2,10 | - | 0 | 1 | 0 | |

| 8,9 | 1 | 0 | 0 | - | |

| 8,10 | 1 | 0 | - | 0 | |

| GB2 | 6,14 | - | 1 | 1 | 0 |

| 9,11 | 1 | 0 | - | 1 | |

| 10,11 | 1 | 0 | 1 | - | |

| 10,14 | 1 | - | 1 | 0 | |

| 11,15 | 1 | - | 1 | 1 | |

| 14,15 | 1 | 1 | 1 | - |

Istilah min, yang hanya dibedakan dalam posisi satu-bit dari grup yang berdekatan akan digabungkan. Bit yang berbeda itu diwakili dengan simbol ini, '-'. Dalam kasus ini, ada tiga kelompok dan setiap kelompok berisi kombinasi dua suku min. Tabel berikut menunjukkan kemungkinanmerging of min term pairs dari kelompok yang berdekatan.

| Nama grup | Istilah min | W | X | Y | Z |

|---|---|---|---|---|---|

| GB1 | 2,6,10,14 | - | - | 1 | 0 |

| 2,10,6,14 | - | - | 1 | 0 | |

| 8,9,10,11 | 1 | 0 | - | - | |

| 8,10,9,11 | 1 | 0 | - | - | |

| GB2 | 10,11,14,15 | 1 | - | 1 | - |

| 10,14,11,15 | 1 | - | 1 | - |

Grup pasangan jangka waktu min yang berurutan, yang dibedakan hanya dalam posisi satu bit akan digabungkan. Bit yang berbeda itu diwakili dengan simbol ini, '-'. Dalam kasus ini, ada dua kelompok dan setiap kelompok berisi kombinasi empat suku min. Di sini, kombinasi istilah 4 menit ini tersedia dalam dua baris. Jadi, kami dapat menghapus baris yang berulang. Tabel yang dikurangi setelah menghapus baris yang berlebihan ditampilkan di bawah ini.

| Nama grup | Istilah min | W | X | Y | Z |

|---|---|---|---|---|---|

| GC1 | 2,6,10,14 | - | - | 1 | 0 |

| 8,9,10,11 | 1 | 0 | - | - | |

| GC2 | 10,11,14,15 | 1 | - | 1 | - |

Penggabungan lebih lanjut dari kombinasi suku min dari grup yang berdekatan tidak dimungkinkan, karena mereka berbeda dalam lebih dari satu posisi bit. Ada tiga baris pada tabel di atas. Jadi, setiap baris akan memberikan satu implikasi utama. Oleh karena itu,prime implicants adalah YZ ', WX' & WY.

Itu prime implicant table ditampilkan di bawah.

| Istilah min / Implan Utama | 2 | 6 | 8 | 9 | 10 | 11 | 14 | 15 |

|---|---|---|---|---|---|---|---|---|

| YZ’ | 1 | 1 | 1 | 1 | ||||

| WX’ | 1 | 1 | 1 | 1 | ||||

| WY | 1 | 1 | 1 | 1 |

Implikasi utama ditempatkan dalam baris bijaksana dan istilah min ditempatkan dalam kolom bijaksana. 1s ditempatkan di sel umum baris implikasi utama dan kolom istilah min yang sesuai.

Min suku 2 dan 6 hanya dicakup oleh satu prime implant YZ’. Jadi, ini adalahessential prime implicant. Ini akan menjadi bagian dari fungsi Boolean yang disederhanakan. Sekarang, hapus baris implikasi utama ini dan kolom istilah min yang sesuai. Tabel implikasi utama tereduksi ditampilkan di bawah ini.

| Istilah min / Implan Utama | 8 | 9 | 11 | 15 |

|---|---|---|---|---|

| WX’ | 1 | 1 | 1 | |

| WY | 1 | 1 |

Suku min 8 dan 9 hanya dicakup oleh satu implikasi utama WX’. Jadi, ini adalahessential prime implicant. Ini akan menjadi bagian dari fungsi Boolean yang disederhanakan. Sekarang, hapus baris implikasi utama ini dan kolom istilah min yang sesuai. Tabel implikasi utama tereduksi ditampilkan di bawah ini.

| Istilah min / Implan Utama | 15 |

|---|---|

| WY | 1 |

Min term 15 hanya dicakup oleh satu prime implant WY. Jadi, ini adalahessential prime implicant. Ini akan menjadi bagian dari fungsi Boolean yang disederhanakan.

Dalam contoh soal ini, kami mendapat tiga implikasi utama dan ketiganya penting. Oleh karena itu,simplified Boolean function adalah

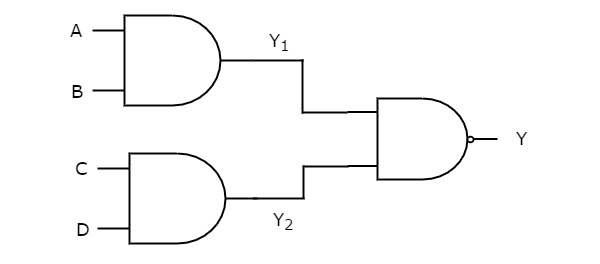

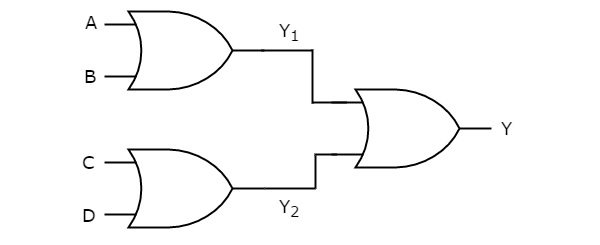

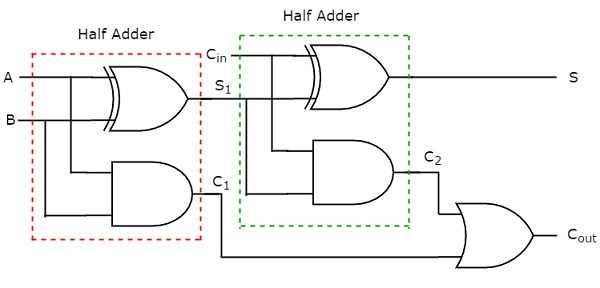

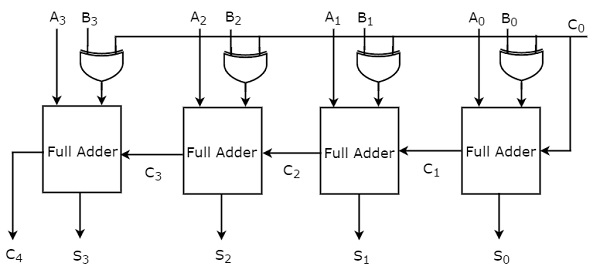

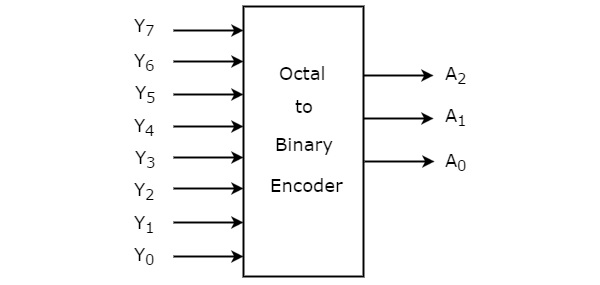

f(W,X,Y,Z) = YZ’ + WX’ + WY.