วงจรดิจิทัล - รีจิสเตอร์ Shift

เราทราบดีว่าฟลิปฟล็อปหนึ่งเครื่องสามารถเก็บข้อมูลหนึ่งบิตได้ ในการจัดเก็บข้อมูลหลายบิตเราต้องใช้รองเท้าแตะหลายอัน กลุ่มของฟลิปฟล็อปซึ่งใช้ในการเก็บ (จัดเก็บ) ข้อมูลไบนารีเรียกว่าregister.

หากรีจิสเตอร์มีความสามารถในการขยับบิตไปทางด้านขวามือหรือทางด้านซ้ายจะเรียกว่า shift register. ทะเบียนกะบิต 'N' มีรองเท้าแตะ 'N' ต่อไปนี้คือการลงทะเบียนกะสี่ประเภทโดยพิจารณาจากการใช้อินพุตและการเข้าถึงเอาต์พุต

- Serial In - Serial Out shift register

- Serial In - Parallel Out shift register

- Parallel In - Serial Out shift register

- Parallel In - Parallel Out shift register

Serial In - Serial Out (SISO) Shift Register

shift register ซึ่งอนุญาตให้ป้อนข้อมูลแบบอนุกรมและสร้างเอาต์พุตแบบอนุกรมเรียกว่า Serial In - Serial Out (SISO)กะลงทะเบียน. block diagram ของ 3-bit SISO shift register แสดงดังรูปต่อไปนี้

แผนภาพบล็อกนี้ประกอบด้วยรองเท้าแตะ D สามแบบซึ่ง ได้แก่ cascaded. นั่นหมายความว่าเอาต์พุตของ D flip-flop หนึ่งตัวเชื่อมต่อเป็นอินพุตของ D flip-flop ถัดไป รองเท้าแตะทั้งหมดนี้ซิงโครไนซ์ซึ่งกันและกันสัญญาณนาฬิกาจะถูกนำไปใช้กับแต่ละอัน

ในการลงทะเบียนกะนี้เราสามารถส่งบิตแบบอนุกรมจากอินพุตของ D flip-flop ทางซ้ายส่วนใหญ่ ดังนั้นอินพุตนี้จึงเรียกอีกอย่างว่าserial input. สำหรับทุกขอบบวกที่ทริกเกอร์สัญญาณนาฬิกาข้อมูลจะเปลี่ยนจากขั้นตอนหนึ่งไปอีกขั้น ดังนั้นเราสามารถรับบิตแบบอนุกรมจากเอาต์พุตของ D flip-flop ทางขวาส่วนใหญ่ ดังนั้นเอาต์พุตนี้จึงเรียกอีกอย่างว่าserial output.

ตัวอย่าง

ให้เราดูการทำงานของ 3-bit SISO shift register โดยการส่งข้อมูลไบนารี “011” จาก LSB เป็น MSB แบบอนุกรมที่อินพุต

สมมติว่าสถานะเริ่มต้นของรองเท้าแตะ D จากซ้ายสุดไปขวาสุดคือ $ Q_ {2} Q_ {1} Q_ {0} = 000 $ เราสามารถเข้าใจไฟล์working of 3-bit SISO shift register จากตารางต่อไปนี้

| ไม่มีขอบด้านบวกของนาฬิกา | อินพุตอนุกรม | คำถาม2 | คำถามที่1 | คำถาม0 |

|---|---|---|---|---|

| 0 | - | 0 | 0 | 0 |

| 1 | 1 (LSB) | 1 | 0 | 0 |

| 2 | 1 | 1 | 1 | 0 |

| 3 | 0 (MSB) | 0 | 1 | 1 (LSB) |

| 4 | - | - | 0 | 1 |

| 5 | - | - | - | 0 (MSB) |

สถานะเริ่มต้นของรองเท้าแตะ D ในกรณีที่ไม่มีสัญญาณนาฬิกาคือ $ Q_ {2} Q_ {1} Q_ {0} = 000 $ ที่นี่เอาต์พุตอนุกรมมาจาก $ Q_ {0} $ ดังนั้น LSB (1) ได้รับ 3 ถขอบในเชิงบวกของนาฬิกาและ MSB (0) จะได้รับ 5 THขอบในเชิงบวกของนาฬิกา

ดังนั้นการลงทะเบียนกะ SISO 3 บิตจึงต้องใช้สัญญาณนาฬิกาห้าครั้งเพื่อให้ได้เอาต์พุตที่ถูกต้อง ในทำนองเดียวกันN-bit SISO shift register ต้องมี 2N-1 สัญญาณนาฬิกาเพื่อเปลี่ยนข้อมูลบิต 'N'

Serial In - Parallel Out (SIPO) Shift Register

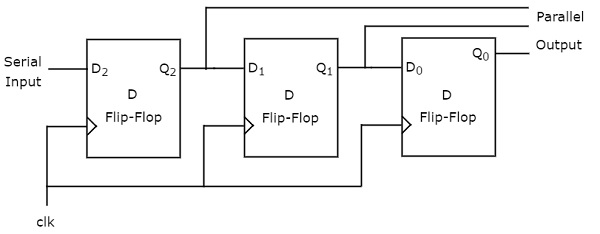

shift register ซึ่งอนุญาตให้ป้อนข้อมูลแบบอนุกรมและสร้างเอาต์พุตแบบขนานเรียกว่า Serial In - Parallel Out (SIPO)กะลงทะเบียน. block diagram ของการลงทะเบียนกะ SIPO 3 บิตจะแสดงในรูปต่อไปนี้

วงจรนี้ประกอบด้วยฟลิปฟล็อป D สามตัวซึ่งเรียงซ้อนกัน นั่นหมายความว่าเอาต์พุตของฟลิปฟล็อป D หนึ่งตัวเชื่อมต่อเป็นอินพุตของ D ฟลิปฟล็อปถัดไป รองเท้าแตะทั้งหมดนี้ซิงโครไนซ์ซึ่งกันและกันสัญญาณนาฬิกาจะถูกนำไปใช้กับแต่ละอัน

ในการลงทะเบียนกะนี้เราสามารถส่งบิตแบบอนุกรมจากอินพุตของ D flip-flop ทางซ้ายส่วนใหญ่ ดังนั้นอินพุตนี้จึงเรียกอีกอย่างว่าserial input. สำหรับทุกขอบบวกที่ทริกเกอร์สัญญาณนาฬิกาข้อมูลจะเปลี่ยนจากขั้นตอนหนึ่งไปอีกขั้น ในกรณีนี้เราสามารถเข้าถึงเอาท์พุตของ D flip-flop แต่ละอันแบบขนานกันได้ ดังนั้นเราจะได้รับparallel outputs จากทะเบียนกะนี้

ตัวอย่าง

ให้เราดูการทำงานของ 3-bit SIPO shift register โดยการส่งข้อมูลไบนารี “011” จาก LSB เป็น MSB แบบอนุกรมที่อินพุต

สมมติว่าสถานะเริ่มต้นของรองเท้าแตะ D จากซ้ายสุดไปขวาสุดคือ $ Q_ {2} Q_ {1} Q_ {0} = 000 $ ที่นี่ $ Q_ {2} $ & $ Q_ {0} $ คือ MSB & LSB ตามลำดับ เราสามารถเข้าใจไฟล์working of 3-bit SIPO shift register จากตารางต่อไปนี้

| ไม่มีขอบด้านบวกของนาฬิกา | อินพุตอนุกรม | คำถาม2 (MSB) | คำถามที่1 | คำถาม0 (LSB) |

|---|---|---|---|---|

| 0 | - | 0 | 0 | 0 |

| 1 | 1 (LSB) | 1 | 0 | 0 |

| 2 | 1 | 1 | 1 | 0 |

| 3 | 0 (MSB) | 0 | 1 | 1 |

สถานะเริ่มต้นของรองเท้าแตะ D ในกรณีที่ไม่มีสัญญาณนาฬิกาคือ $ Q_ {2} Q_ {1} Q_ {0} = 000 $ ข้อมูลไบนารี“011” ได้รับแบบขนานที่เอาต์พุตของ D flip-flop สำหรับขอบนาฬิกาด้านบวกที่สาม

ดังนั้นการลงทะเบียนกะ SIPO 3 บิตจึงต้องใช้สัญญาณนาฬิกาสามครั้งเพื่อสร้างเอาต์พุตที่ถูกต้อง ในทำนองเดียวกันN-bit SIPO shift register ต้องมี N สัญญาณนาฬิกาเพื่อเปลี่ยนข้อมูลบิต 'N'

Parallel In - Serial Out (PISO) Shift Register

shift register ซึ่งอนุญาตให้ป้อนข้อมูลแบบขนานและสร้างเอาต์พุตแบบอนุกรมเรียกว่า Parallel In - Serial Out (PISO)กะลงทะเบียน. block diagram ของ 3-bit PISO shift register แสดงดังรูปต่อไปนี้

วงจรนี้ประกอบด้วยฟลิปฟล็อป D สามตัวซึ่งเรียงซ้อนกัน นั่นหมายความว่าเอาต์พุตของฟลิปฟล็อป D หนึ่งตัวเชื่อมต่อเป็นอินพุตของ D ฟลิปฟล็อปถัดไป รองเท้าแตะทั้งหมดนี้ซิงโครไนซ์ซึ่งกันและกันสัญญาณนาฬิกาจะถูกนำไปใช้กับแต่ละอัน

ในการลงทะเบียนกะนี้เราสามารถใช้ parallel inputsไปยังฟลิปฟล็อป D แต่ละตัวโดยการตั้งค่าล่วงหน้าเปิดใช้งานเป็น 1 สำหรับขอบบวกทุกครั้งที่เรียกสัญญาณนาฬิกาข้อมูลจะเปลี่ยนจากขั้นตอนหนึ่งไปอีกขั้น ดังนั้นเราจะได้รับไฟล์serial output จากทางขวาสุด D flip-flop

ตัวอย่าง

ให้เราดูการทำงานของ 3-bit PISO shift register โดยใช้ข้อมูลไบนารี “011” แบบขนานผ่านอินพุตที่ตั้งไว้ล่วงหน้า

เนื่องจากอินพุตที่ตั้งไว้ล่วงหน้าถูกนำไปใช้ก่อนขอบบวกของนาฬิกาสถานะเริ่มต้นของรองเท้าแตะ D จากซ้ายสุดไปขวาสุดจะเป็น $ Q_ {2} Q_ {1} Q_ {0} = 011 $ เราสามารถเข้าใจไฟล์working of 3-bit PISO shift register จากตารางต่อไปนี้

| ไม่มีขอบด้านบวกของนาฬิกา | คำถาม2 | คำถามที่1 | คำถาม0 |

|---|---|---|---|

| 0 | 0 | 1 | 1 (LSB) |

| 1 | - | 0 | 1 |

| 2 | - | - | 0 (LSB) |

ที่นี่เอาต์พุตอนุกรมมาจาก $ Q_ {0} $ ดังนั้น LSB (1) จะได้รับก่อนที่จะใช้ในเชิงบวกของขอบนาฬิกาและ MSB (0) จะได้รับที่ 2 ครั้งที่ขอบบวกของนาฬิกา

ดังนั้นการลงทะเบียน PISO shift 3 บิตจึงต้องใช้พัลส์นาฬิกาสองครั้งเพื่อสร้างเอาต์พุตที่ถูกต้อง ในทำนองเดียวกันN-bit PISO shift register ต้องมี N-1 สัญญาณนาฬิกาเพื่อเปลี่ยนข้อมูลบิต 'N'

Parallel In - Parallel Out (PIPO) Shift Register

shift register ซึ่งอนุญาตให้ป้อนข้อมูลแบบขนานและสร้างเอาต์พุตแบบขนานเรียกว่า Parallel In - Parallel Out (PIPO)กะลงทะเบียน. block diagram ของ PIPO shift register 3 บิตแสดงดังรูปต่อไปนี้

วงจรนี้ประกอบด้วยฟลิปฟล็อป D สามตัวซึ่งเรียงซ้อนกัน นั่นหมายความว่าเอาต์พุตของฟลิปฟล็อป D หนึ่งตัวเชื่อมต่อเป็นอินพุตของ D ฟลิปฟล็อปถัดไป รองเท้าแตะทั้งหมดนี้ซิงโครไนซ์ซึ่งกันและกันสัญญาณนาฬิกาจะถูกนำไปใช้กับแต่ละอัน

ในการลงทะเบียนกะนี้เราสามารถใช้ parallel inputsกับฟลิปฟล็อป D แต่ละตัวโดยการตั้งค่าล่วงหน้าเปิดใช้งานเป็น 1 เราสามารถใช้อินพุตขนานผ่านค่าที่ตั้งไว้ล่วงหน้าหรือล้าง ทั้งสองเป็นอินพุตแบบอะซิงโครนัส นั่นหมายความว่าฟลิปฟล็อปจะสร้างเอาต์พุตที่สอดคล้องกันโดยพิจารณาจากค่าของอินพุตแบบอะซิงโครนัส ในกรณีนี้ผลของเอาต์พุตจะไม่ขึ้นอยู่กับการเปลี่ยนสัญญาณนาฬิกา ดังนั้นเราจะได้รับไฟล์parallel outputs จากแต่ละ D flip-flop

ตัวอย่าง

ให้เราดูการทำงานของ 3-bit PIPO shift register โดยใช้ข้อมูลไบนารี “011” แบบขนานผ่านอินพุตที่ตั้งไว้ล่วงหน้า

เนื่องจากอินพุตที่ตั้งไว้ล่วงหน้าถูกนำไปใช้ก่อนขอบบวกของนาฬิกาสถานะเริ่มต้นของรองเท้าแตะ D จากซ้ายสุดไปขวาสุดจะเป็น $ Q_ {2} Q_ {1} Q_ {0} = 011 $ ดังนั้นข้อมูลไบนารี“011” ได้รับแบบขนานที่เอาต์พุตของ D flip-flop ก่อนที่จะใช้ขอบนาฬิกาที่เป็นบวก

ดังนั้นการลงทะเบียนกะ PIPO 3 บิตจึงต้องใช้พัลส์นาฬิกาเป็นศูนย์เพื่อสร้างเอาต์พุตที่ถูกต้อง ในทำนองเดียวกันN-bit PIPO shift register ไม่ต้องการพัลส์นาฬิกาใด ๆ เพื่อเปลี่ยนข้อมูลบิต 'N'