Obwody cyfrowe - rejestry przesunięć

Wiemy, że jeden przerzutnik może przechowywać jeden bit informacji. Aby przechowywać wiele bitów informacji, potrzebujemy wielu przerzutników. Grupa przerzutników, które służą do przechowywania (przechowywania) danych binarnych, nazywana jestregister.

Jeśli rejestr jest zdolny do przesuwania bitów albo w prawą stronę, albo w lewą stronę, nazywa się shift register. Rejestr przesuwny z bitem „N” zawiera przerzutniki „N”. Poniżej przedstawiono cztery typy rejestrów przesuwnych oparte na stosowaniu danych wejściowych i uzyskiwaniu dostępu do wyjść.

- Serial In - Rejestr przesuwny szeregowego wyjścia

- Szeregowe wejście - rejestr przesuwny równoległego wyjścia

- Równoległe wejście - rejestr przesuwny szeregowego wyjścia

- Równoległe wejście - rejestr przesuwny równoległego wyjścia

Wejście szeregowe - rejestr przesuwny wyjścia szeregowego (SISO)

Rejestr przesuwny, który umożliwia wejście szeregowe i generuje wyjście szeregowe, jest znany jako Serial In - Serial Out (SISO)rejestr przesuwny. Plikblock diagram 3-bitowego rejestru przesuwnego SISO pokazano na poniższym rysunku.

Ten schemat blokowy składa się z trzech przerzutników typu D. cascaded. Oznacza to, że wyjście jednego przerzutnika D jest dołączane jako wejście następnego przerzutnika D. Wszystkie te przerzutniki są ze sobą synchroniczne, ponieważ do każdego z nich podawany jest ten sam sygnał zegarowy.

W tym rejestrze przesuwnym możemy przesyłać bity szeregowo z wejścia przerzutnika D znajdującego się najbardziej po lewej stronie. Stąd to wejście jest również nazywane jakoserial input. Przy każdym wyzwalaniu zboczem dodatnim sygnału zegarowego dane przesuwają się z jednego stopnia na drugi. Możemy więc otrzymywać bity szeregowo z wyjścia przerzutnika D znajdującego się najbardziej po prawej stronie. Dlatego ten wynik jest również nazywany jakoserial output.

Przykład

Zobaczmy działanie 3-bitowego rejestru przesuwnego SISO, wysyłając informacje binarne “011” z LSB do MSB szeregowo na wejściu.

Załóżmy, że początkowy stan przerzutników D od lewej do prawej to $ Q_ {2} Q_ {1} Q_ {0} = 000 $. Możemy zrozumiećworking of 3-bit SISO shift register z poniższej tabeli.

| Brak dodatniej krawędzi zegara | Wejście szeregowe | Pytanie 2 | Pytanie 1 | Pytanie 0 |

|---|---|---|---|---|

| 0 | - | 0 | 0 | 0 |

| 1 | 1 (LSB) | 1 | 0 | 0 |

| 2 | 1 | 1 | 1 | 0 |

| 3 | 0 (MSB) | 0 | 1 | 1 (LSB) |

| 4 | - | - | 0 | 1 |

| 5 | - | - | - | 0 (MSB) |

Początkowy stan przerzutników D przy braku sygnału zegarowego to $ Q_ {2} Q_ {1} Q_ {0} = 000 $. Tutaj wyjście szeregowe pochodzi z $ Q_ {0} $. Tak więc, LSB (1) jest odbierany w 3 -cim dodatniego zbocza zegara i MSB (0) jest odbierany w 5 th dodatniego zbocza zegara.

Dlatego 3-bitowy rejestr przesuwny SISO wymaga pięciu impulsów zegarowych, aby wytworzyć prawidłowe wyjście. PodobnieN-bit SISO shift register wymaga 2N-1 impulsy zegara w celu przesunięcia informacji o bitach „N”.

Szeregowe wejście - wyjście równoległe (SIPO) Rejestr przesuwny

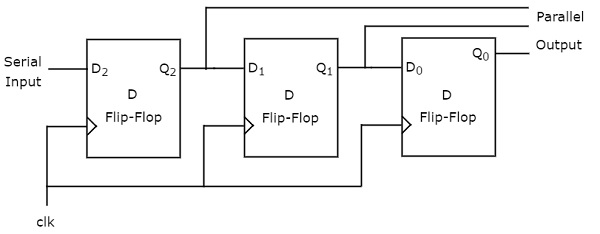

Rejestr przesuwny, który umożliwia wejście szeregowe i wytwarza wyjście równoległe, jest znany jako szeregowe wejście - wyjście równoległe (SIPO)rejestr przesuwny. Plikblock diagram 3-bitowego rejestru przesuwnego SIPO pokazano na poniższym rysunku.

Ten obwód składa się z trzech przerzutników typu D, które są połączone kaskadowo. Oznacza to, że wyjście jednego przerzutnika D jest dołączane jako wejście następnego przerzutnika D. Wszystkie te przerzutniki są ze sobą synchroniczne, ponieważ do każdego z nich podawany jest ten sam sygnał zegarowy.

W tym rejestrze przesuwnym możemy przesyłać bity szeregowo z wejścia przerzutnika D znajdującego się najbardziej po lewej stronie. Stąd to wejście jest również nazywane jakoserial input. Przy każdym wyzwalaniu zboczem dodatnim sygnału zegarowego dane przesuwają się z jednego stopnia na drugi. W takim przypadku możemy uzyskać dostęp do wyjść każdego przerzutnika D równolegle. Więc dostaniemyparallel outputs z tego rejestru przesuwnego.

Przykład

Zobaczmy działanie 3-bitowego rejestru przesuwnego SIPO, wysyłając informacje binarne “011” z LSB do MSB szeregowo na wejściu.

Załóżmy, że początkowy stan przerzutników D od lewej do prawej to $ Q_ {2} Q_ {1} Q_ {0} = 000 $. Tutaj $ Q_ {2} $ i $ Q_ {0} $ to odpowiednio MSB i LSB. Możemy zrozumiećworking of 3-bit SIPO shift register z poniższej tabeli.

| Brak dodatniej krawędzi zegara | Wejście szeregowe | Q 2 (MSB) | Pytanie 1 | Q 0 (LSB) |

|---|---|---|---|---|

| 0 | - | 0 | 0 | 0 |

| 1 | 1 (LSB) | 1 | 0 | 0 |

| 2 | 1 | 1 | 1 | 0 |

| 3 | 0 (MSB) | 0 | 1 | 1 |

Początkowy stan przerzutników D przy braku sygnału zegarowego to $ Q_ {2} Q_ {1} Q_ {0} = 000 $. Informacje binarne“011” jest uzyskiwany równolegle na wyjściach przerzutników D dla trzeciego dodatniego zbocza zegara.

Tak więc 3-bitowy rejestr przesuwny SIPO wymaga trzech impulsów zegarowych, aby wygenerować prawidłowe wyjście. PodobnieN-bit SIPO shift register wymaga N impulsy zegara w celu przesunięcia informacji o bitach „N”.

Rejestr przesuwny równoległego wejścia - wyjścia szeregowego (PISO)

Rejestr przesuwny, który umożliwia równoległe wejście i generuje wyjście szeregowe, jest znany jako Parallel In - Serial Out (PISO)rejestr przesuwny. Plikblock diagram 3-bitowego rejestru przesuwnego PISO pokazano na poniższym rysunku.

Ten obwód składa się z trzech przerzutników typu D, które są połączone kaskadowo. Oznacza to, że wyjście jednego przerzutnika D jest dołączane jako wejście następnego przerzutnika D. Wszystkie te przerzutniki są ze sobą synchroniczne, ponieważ do każdego z nich podawany jest ten sam sygnał zegarowy.

W tym rejestrze przesuwnym możemy zastosować rozszerzenie parallel inputsdo każdego przerzutnika D, ustawiając Preset Enable na 1. Dla każdego wyzwolenia zbocza dodatniego sygnału zegarowego, dane przesuwają się z jednego stopnia do drugiego. Więc otrzymamyserial output od prawej strony przerzutnik D.

Przykład

Zobaczmy działanie 3-bitowego rejestru przesuwnego PISO poprzez zastosowanie informacji binarnych “011” równolegle przez wstępnie ustawione wejścia.

Ponieważ wstępnie ustawione wejścia są stosowane przed dodatnim zboczem zegara, początkowy stan przerzutników D od lewej do prawej będzie wynosił $ Q_ {2} Q_ {1} Q_ {0} = 011 $. Możemy zrozumiećworking of 3-bit PISO shift register z poniższej tabeli.

| Brak dodatniej krawędzi zegara | Pytanie 2 | Pytanie 1 | Pytanie 0 |

|---|---|---|---|

| 0 | 0 | 1 | 1 (LSB) |

| 1 | - | 0 | 1 |

| 2 | - | - | 0 (LSB) |

Tutaj wyjście szeregowe pochodzi z $ Q_ {0} $. Tak więc, LSB (1) jest odbierany przed zastosowaniem dodatniego zbocza zegara i MSB (0) jest otrzymana na 2 nd zbocze zegara.

Dlatego 3-bitowy rejestr przesuwny PISO wymaga dwóch impulsów zegarowych, aby wygenerować prawidłowe wyjście. PodobnieN-bit PISO shift register wymaga N-1 impulsy zegara w celu przesunięcia informacji o bitach „N”.

Rejestr przesuwny równoległego wejścia - wyjścia równoległego (PIPO)

Rejestr przesuwny, który umożliwia równoległe wejście i generuje równoległe wyjście, jest znany jako Parallel In - Parallel Out (PIPO)rejestr przesuwny. Plikblock diagram 3-bitowego rejestru przesuwnego PIPO pokazano na poniższym rysunku.

Ten obwód składa się z trzech przerzutników typu D, które są połączone kaskadowo. Oznacza to, że wyjście jednego przerzutnika D jest dołączane jako wejście następnego przerzutnika D. Wszystkie te przerzutniki są ze sobą synchroniczne, ponieważ do każdego z nich podawany jest ten sam sygnał zegarowy.

W tym rejestrze przesuwnym możemy zastosować rozszerzenie parallel inputsdo każdego przerzutnika D, ustawiając Preset Enable na 1. Możemy zastosować równoległe wejścia poprzez preset lub wyczyść. Te dwa są wejściami asynchronicznymi. Oznacza to, że przerzutniki generują odpowiednie wyjścia w oparciu o wartości wejść asynchronicznych. W tym przypadku efekt wyjść jest niezależny od przejścia zegara. Więc otrzymamyparallel outputs z każdego przerzutnika D.

Przykład

Zobaczmy działanie 3-bitowego rejestru przesuwnego PIPO, stosując informacje binarne “011” równolegle przez wstępnie ustawione wejścia.

Ponieważ wstępnie ustawione wejścia są stosowane przed dodatnim zboczem zegara, początkowy stan przerzutników D od lewej do prawej będzie wynosił $ Q_ {2} Q_ {1} Q_ {0} = 011 $. A więc informacje binarne“011” uzyskuje się równolegle na wyjściach przerzutników D przed zastosowaniem dodatniego zbocza zegara.

Dlatego 3-bitowy rejestr przesuwny PIPO wymaga zerowych impulsów zegarowych w celu wytworzenia prawidłowego wyjścia. PodobnieN-bit PIPO shift registernie wymaga żadnego impulsu zegarowego w celu przesunięcia informacji „N” bitowej.