Digitale Schaltungen - Latches

Es gibt zwei Arten von Speicherelementen, die auf der Art der Auslösung basieren, die für den Betrieb geeignet ist.

- Latches

- Flip-flops

Latches arbeiten mit dem Freigabesignal level sensitive. Während Flip-Flops kantenempfindlich sind. Wir werden im nächsten Kapitel über Flip-Flops diskutieren. Lassen Sie uns nun nacheinander über SR Latch & D Latch diskutieren.

SR Latch

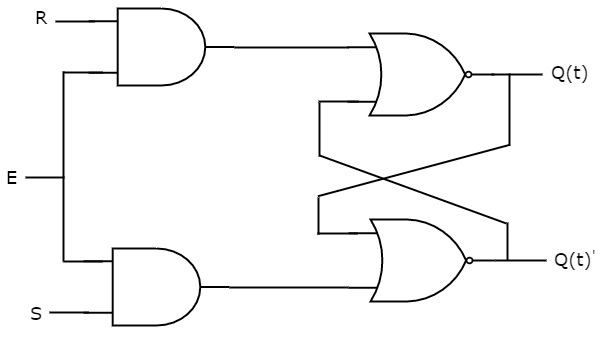

SR Latch wird auch als bezeichnet Set Reset Latch. Dieser Latch wirkt sich auf die Ausgänge aus, solange die Freigabe E auf '1' gehalten wird. Dascircuit diagram von SR Latch ist in der folgenden Abbildung dargestellt.

Diese Schaltung hat zwei Eingänge S & R und zwei Ausgänge Q (t) & Q (t) '. Dasupper NOR gate hat zwei Eingänge R & Komplement des gegenwärtigen Zustands Q (t) 'und erzeugt den nächsten Zustand Q (t + 1), wenn die Aktivierung E' 1 'ist.

Ebenso die lower NOR gate hat zwei Eingänge S & gegenwärtigen Zustand, Q (t) und erzeugt ein Komplement des nächsten Zustands, Q (t + 1) ', wenn aktiviert, ist E' 1 '.

Wir wissen, dass a 2-input NOR gateerzeugt eine Ausgabe, die das Komplement einer anderen Eingabe ist, wenn eine der Eingaben '0' ist. In ähnlicher Weise wird eine '0'-Ausgabe erzeugt, wenn eine der Eingaben' 1 'ist.

Wenn S = 1 ist, ist der nächste Zustand Q (t + 1) unabhängig vom gegenwärtigen Zustand Q (t) gleich '1'.

Wenn R = 1 ist, ist der nächste Zustand Q (t + 1) unabhängig vom gegenwärtigen Zustand Q (t) gleich '0'.

Zu jedem Zeitpunkt sollte nur einer dieser beiden Eingänge '1' sein. Wenn beide Eingänge '1' sind, ist der nächste Q-Wert (t + 1) undefiniert.

Die folgende Tabelle zeigt die state table von SR Latch.

| S. | R. | Q (t + 1) |

|---|---|---|

| 0 | 0 | Q (t) |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | - - |

Daher führt SR Latch drei Arten von Funktionen aus, z. B. Halten, Setzen und Zurücksetzen, basierend auf den Eingabebedingungen.

D Verriegelung

Es gibt einen Nachteil von SR Latch. Dies ist der nächste Zustandswert, der nicht vorhergesagt werden kann, wenn beide Eingänge S & R eins sind. Wir können diese Schwierigkeit also durch D Latch überwinden. Es wird auch als Data Latch bezeichnet. Dascircuit diagram von D Latch ist in der folgenden Abbildung dargestellt.

Diese Schaltung hat einen einzelnen Eingang D und zwei Ausgänge Q (t) & Q (t) '. D Latch wird von SR Latch erhalten, indem ein Wechselrichter zwischen S & R-Eingängen platziert und D-Eingang mit S verbunden wird. Das heißt, wir haben die Kombinationen von S & R eliminiert, die denselben Wert haben.

Wenn D = 0 → S = 0 & R = 1 ist, ist der nächste Zustand Q (t + 1) unabhängig vom gegenwärtigen Zustand Q (t) gleich '0'. Dies entspricht der zweiten Zeile der SR Latch-Statustabelle.

Wenn D = 1 → S = 1 & R = 0 ist, ist der nächste Zustand Q (t + 1) unabhängig vom gegenwärtigen Zustand Q (t) gleich '1'. Dies entspricht der dritten Zeile der SR Latch-Statustabelle.

Die folgende Tabelle zeigt die state table von D Latch.

| D. | Q (t + 1) |

|---|---|

| 0 | 0 |

| 1 | 1 |

Daher hält D Latch die Informationen bereit, die für die Dateneingabe D verfügbar sind. Dies bedeutet, dass der Ausgang von D Latch empfindlich auf Änderungen am Eingang D reagiert, solange die Freigabe hoch ist.

In diesem Kapitel haben wir verschiedene Latches implementiert, indem wir die Kreuzkopplung zwischen NOR-Gattern bereitgestellt haben. Ebenso können Sie diese Latches mithilfe von NAND-Gattern implementieren.