Dijital Devreler - Kaydırma Kayıtlarının Uygulanması

Önceki bölümde, dört tür vardiya kaydı tartıştık. Gereksinime bağlı olarak, bu vardiya kayıtlarından birini kullanabiliriz. Aşağıda vardiya kayıtlarının uygulamaları bulunmaktadır.

Vardiya kaydı, Parallel to serial converter, paralel verileri seri verilere dönüştürür. Analogdan Dijitale Dönüştürücü (ADC) bloğundan sonra verici bölümünde kullanılır.

Vardiya kaydı, Serial to parallel converter, seri verileri paralel verilere dönüştürür. Alıcı bölümünde Digital to Analog Converter (DAC) bloğundan önce kullanılır.

Kaydırma kaydı bazı ek kapı (lar) ile birlikte sıfırlar ve birler dizisini oluşturur. Bu nedenle, olarak kullanılırsequence generator.

Vardiya kayıtları ayrıca counters. Sağdaki çıktı tipine bağlı olarak iki tür sayaç vardır, çoğu D flip-flopu seri girişe bağlıdır. Bunlar Ring sayacı ve Johnson Ring sayacı.

Bu bölümde bu iki sayacı tek tek tartışalım.

Yüzük Sayacı

Önceki bölümde Seri Giriş - Paralel Çıkış'ın çalışmasını tartışmıştık. (SIPO)vardiya yazmacı. Verileri dışarıdan seri biçimde kabul eder ve 'N' bit verisini kaydırmak için 'N' saat darbelerine ihtiyaç duyar.

Benzer şekilde, ‘N’ bit Ring counterbenzer işlemi gerçekleştirir. Ancak, tek fark, en sağdaki D flip-flopunun çıktısının, dışarıdan veri uygulamak yerine en soldaki D flip-flopunun girdisi olarak verilmesidir. Bu nedenle, Halka sayacı bir durum dizisi üretir (sıfırlar ve birler düzeni) ve her biri için tekrar eder.‘N’ clock cycles.

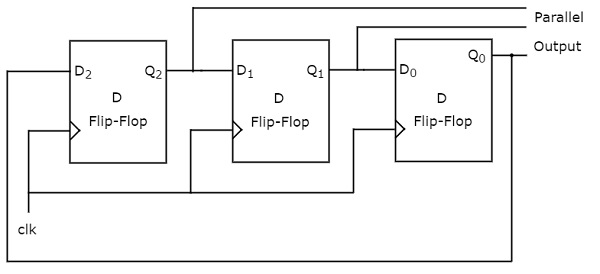

block diagram 3-bitlik Halka sayacı aşağıdaki şekilde gösterilmiştir.

3 bitlik Halka sayacı yalnızca 3 bitlik bir SIPO kaydıran yazmacı içerir. En sağdaki D flip-flopunun çıkışı, soldaki çoğu D flip-flopunun seri girişine bağlanır.

D flip-floplarının en soldan en sağa başlangıç durumunun $ Q_ {2} Q_ {1} Q_ {0} = 001 $ olduğunu varsayalım. Burada, $ Q_ {2} $ ve $ Q_ {0} $ sırasıyla MSB ve LSB'dir. Anlayabilirizworking of Ring counter aşağıdaki tablodan.

| Saatin pozitif kenarı yok | Seri Giriş = Q 0 | Q 2 (MSB) | Q 1 | Q 0 (LSB) |

|---|---|---|---|---|

| 0 | - | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 | 0 |

| 2 | 0 | 0 | 1 | 0 |

| 3 | 0 | 0 | 0 | 1 |

Saat sinyali olmadığında D flip-floplarının başlangıç durumu $ Q_ {2} Q_ {1} Q_ {0} = 001 $ şeklindedir. Bu durum, saat sinyalinin her üç pozitif kenar geçişi için tekrar eder.

Bu nedenle, aşağıdaki operations saat sinyalinin her pozitif kenarı için yer alır.

İlk D flip-flopun seri girişi, üçüncü flip-flopun önceki çıkışını alır. Dolayısıyla, ilk D flip-flopunun mevcut çıktısı, üçüncü flip-flopun önceki çıktısına eşittir.

Birinci ve ikinci D flip-flopların önceki çıktıları bir bit sağa kaydırılır. Bu, ikinci ve üçüncü D flip-flopların mevcut çıktılarının, birinci ve ikinci D flip-flopların önceki çıktılarına eşit olduğu anlamına gelir.

Johnson Yüzük Sayacı

Operasyonu Johnson Ring counterRing sayacına benzer. Ancak, tek fark, en sağdaki D flip-flopunun tamamlanmış çıktısının normal çıktı yerine en soldaki D flip-flopunun girdisi olarak verilmesidir. Bu nedenle, 'N' bit Johnson Ring sayacı bir dizi durum üretir (sıfırlar ve birler düzeni) ve her biri için tekrar eder.‘2N’ clock cycles.

Johnson Ring sayacı aynı zamanda Twisted Ring counterve kuyruk halkası sayacını değiştirin. block diagram 3 bitlik Johnson Ring sayacı aşağıdaki şekilde gösterilmektedir.

3 bitlik Johnson Ring sayacı ayrıca yalnızca 3 bitlik bir SIPO kaydırma yazmacı içerir. En sağdaki D flip-flopun tamamlanmış çıkışı, en soldaki D flip-flopunun seri girişine bağlanır.

Varsayalım, başlangıçta tüm D flip-flopları temizlendi. Yani, $ Q_ {2} Q_ {1} Q_ {0} = 000 $. Burada, $ Q_ {2} $ ve $ Q_ {0} $ sırasıyla MSB ve LSB'dir. Anlayabilirizworking Johnson Ring sayacı aşağıdaki tablodan.

| Saatin pozitif kenarı yok | Seri Giriş = Q 0 | Q 2 (MSB) | Q 1 | Q 0 (LSB) |

|---|---|---|---|---|

| 0 | - | 0 | 0 | 0 |

| 1 | 1 | 1 | 0 | 0 |

| 2 | 1 | 1 | 1 | 0 |

| 3 | 1 | 1 | 1 | 1 |

| 4 | 0 | 0 | 1 | 1 |

| 5 | 0 | 0 | 0 | 1 |

| 6 | 0 | 0 | 0 | 0 |

Saat sinyali olmadığında D flip-floplarının başlangıç durumu $ Q_ {2} Q_ {1} Q_ {0} = 000 $ şeklindedir. Bu durum, saat sinyalinin her altı pozitif kenar geçişi için tekrar eder.

Bu nedenle, aşağıdaki operations saat sinyalinin her pozitif kenarı için yer alır.

İlk D flip-flopun seri girişi, üçüncü flip-flopun önceki tamamlanmış çıktısını alır. Dolayısıyla, ilk D flip-flopun mevcut çıktısı, üçüncü flip-flopun önceki tamamlanmış çıktısına eşittir.

Birinci ve ikinci D flip-flopların önceki çıktıları bir bit sağa kaydırılır. Bu, ikinci ve üçüncü D flip-flopların mevcut çıktılarının, birinci ve ikinci D flip-flopların önceki çıktılarına eşit olduğu anlamına gelir.