Dijital Devreler - Mandallar

Çalıştırmak için uygun olan tetikleme türüne bağlı olarak iki tür bellek öğesi vardır.

- Latches

- Flip-flops

Mandallar, etkinleştirme sinyali ile çalışır. level sensitive. Oysa parmak arası terlikler kenara duyarlıdır. Bir sonraki bölümde parmak arası terlikler hakkında tartışacağız. Şimdi SR Latch & D Latch'i tek tek tartışalım.

SR Mandalı

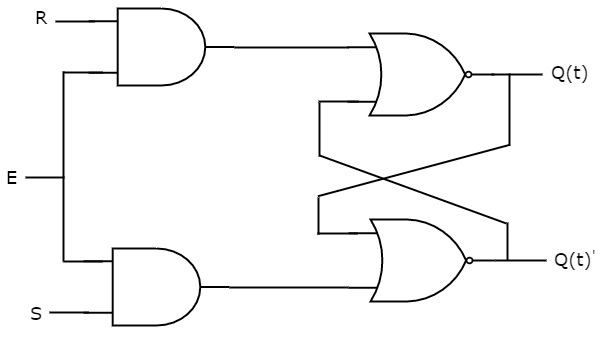

SR Mandalı aynı zamanda Set Reset Latch. Bu mandal, etkinleştirme, E "1" de tutulduğu sürece çıktıları etkiler. circuit diagram SR Mandalı aşağıdaki şekilde gösterilmektedir.

Bu devrede iki S & R girişi ve iki Q (t) ve Q (t) 'çıkışı vardır. upper NOR gate mevcut durumun R & tamamlayıcısı olan iki girişe sahiptir, Q (t) 've bir sonraki durumu, etkinleştirildiğinde Q (t + 1) üretir, E' 1'dir.

Benzer şekilde, lower NOR gate S ve mevcut durum olmak üzere iki girişe sahiptir, Q (t) ve bir sonraki durumun tamamlayıcısı olan Q (t + 1) 'etkinleştirildiğinde, E' 1 'dir.

Biliyoruz ki 2-input NOR gategirdilerden biri '0' olduğunda başka bir girdinin tamamlayıcısı olan bir çıktı üretir. Benzer şekilde, girdilerden biri '1' olduğunda '0' çıktı üretir.

S = 1 ise, sonraki durum Q (t + 1), mevcut durum, Q (t) değerlerine bakılmaksızın '1'e eşit olacaktır.

R = 1 ise, sonraki durum Q (t + 1), mevcut durum, Q (t) değerlerine bakılmaksızın '0'a eşit olacaktır.

Herhangi bir zamanda, yalnızca bu iki girişten '1' olmalıdır. Her iki giriş de '1' ise, sonraki durum Q (t + 1) değeri tanımsızdır.

Aşağıdaki tablo, state table SR mandalı.

| S | R | Q (t + 1) |

|---|---|---|

| 0 | 0 | Q (t) |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | - |

Bu nedenle, SR Mandalı, giriş koşullarına göre Beklet, Ayarla ve Sıfırla gibi üç tür işlevi gerçekleştirir.

D Mandal

SR Mandalının bir dezavantajı vardır. Bu, S ve R girişlerinin her ikisi de bir olduğunda bir sonraki durum değeri tahmin edilemez. D Latch ile bu zorluğun üstesinden gelebiliriz. Veri Mandalı olarak da adlandırılır. circuit diagram D Mandalı aşağıdaki şekilde gösterilmektedir.

Bu devrenin tek girişi D ve iki çıkışı vardır Q (t) & Q (t) '. D Latch, SR Latch'den S amp; & R girişleri arasına bir inverter yerleştirilerek ve D girişini S'ye bağlayarak elde edilir. Yani S & R'nin aynı değerde kombinasyonlarını ortadan kaldırdık.

D = 0 → S = 0 & R = 1 ise, sonraki durum Q (t + 1), mevcut durum, Q (t) değerlerine bakılmaksızın '0'a eşit olacaktır. Bu, SR Kilitleme durum tablosunun ikinci satırına karşılık gelir.

D = 1 → S = 1 & R = 0 ise, sonraki durum Q (t + 1), mevcut durum, Q (t) değerlerinden bağımsız olarak '1'e eşit olacaktır. Bu, SR Kilitleme durum tablosunun üçüncü satırına karşılık gelir.

Aşağıdaki tablo, state table D mandalı.

| D | Q (t + 1) |

|---|---|

| 0 | 0 |

| 1 | 1 |

Bu nedenle, D Mandalı veri girişi D'de mevcut olan bilgileri tutun. Bu, etkinleştirme Yüksek olduğu sürece D Mandalının çıktısının girişteki değişikliklere duyarlı olduğu anlamına gelir.

Bu bölümde, NOR kapıları arasında çapraz bağlantı sağlayarak çeşitli Mandallar uyguladık. Benzer şekilde, bu Mandalları NAND geçitlerini kullanarak uygulayabilirsiniz.