デジタル回路-エンコーダ

アン Encoderデコーダの逆動作を行う組み合わせ回路です。最大2n個の入力ラインと「n」個の出力ラインがあります。これは、アクティブなHighである入力と同等のバイナリコードを生成します。したがって、エンコーダは2n個の入力ラインを「n」ビットでエンコードします。エンコーダでイネーブル信号を表すことはオプションです。

4対2エンコーダ

ましょ4 Y 2のエンコーダは、4つの入力を有する3、Y 2、Y 1およびY 0と2つの出力A 1&A 0。ザ・block diagram 次の図に、4〜2個のエンコーダを示します。

いつでも、出力でそれぞれのバイナリコードを取得するために、これら4つの入力のうち1つだけを「1」にすることができます。ザ・Truth table 4対2のエンコーダーを以下に示します。

| 入力 | 出力 | ||||

|---|---|---|---|---|---|

| Y3 | Y2 | Y1 | Y0 | A1 | A0 |

| 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 | 1 |

真理値表から、 Boolean functions 各出力に対して

$$ A_ {1} = Y_ {3} + Y_ {2} $$

$$ A_ {0} = Y_ {3} + Y_ {1} $$

2つの入力ORゲートを使用して、上記の2つのブール関数を実装できます。ザ・circuit diagram 次の図に、4〜2個のエンコーダを示します。

上記の回路図には、2つのORゲートが含まれています。これらのORゲートは、4つの入力を2ビットでエンコードします

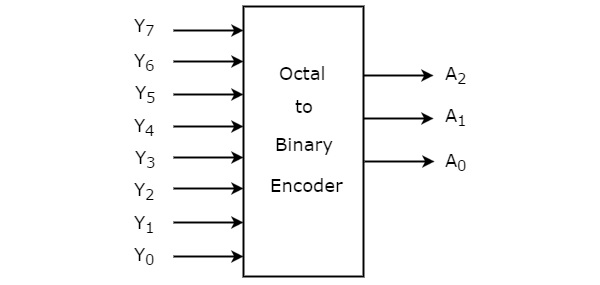

8進数から2進数のエンコーダ

バイナリエンコーダにオクタルは8つの入力、Y有する7をYに0と3つの出力A 2、A 1&A 0。オクタルからバイナリへのエンコーダは、8から3のエンコーダに他なりません。ザ・block diagram 次の図に、8進数から2進数へのエンコーダの変換を示します。

いつでも、それぞれのバイナリコードを取得するために、これらの8つの入力のうち1つだけを「1」にすることができます。ザ・Truth table 8進数から2進数へのエンコーダの比較を以下に示します。

| 入力 | 出力 | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| Y7 | Y6 | Y5 | Y4 | Y3 | Y2 | Y1 | Y0 | A2 | A1 | A0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 |

真理値表から、 Boolean functions 各出力に対して

$$ A_ {2} = Y_ {7} + Y_ {6} + Y_ {5} + Y_ {4} $$

$$ A_ {1} = Y_ {7} + Y_ {6} + Y_ {3} + Y_ {2} $$

$$ A_ {0} = Y_ {7} + Y_ {5} + Y_ {3} + Y_ {1} $$

4つの入力ORゲートを使用して、上記のブール関数を実装できます。ザ・circuit diagram 次の図に、8進数から2進数へのエンコーダの変換を示します。

上記の回路図には、3つの4入力ORゲートが含まれています。これらのORゲートは、8つの入力を3ビットでエンコードします。

エンコーダの欠点

通常のエンコーダの欠点は次のとおりです。

エンコーダのすべての出力がゼロに等しい場合、あいまいさがあります。なぜなら、最下位の入力のみが1の場合、またはすべての入力が0の場合、入力に対応するコードである可能性があるためです。

複数の入力がアクティブHighの場合、エンコーダーは出力を生成しますが、これは正しいコードではない可能性があります。ためにexample、Y両方の場合3およびY 6が「1」であることは、次に符号化器は、出力で111を生成します。これは、Yに対応するも同等のコードである3が「1」にもYに対応する同等のコードであり、6が「1」です、。

したがって、これらの問題を克服するには、エンコーダの各入力に優先順位を割り当てる必要があります。その場合、エンコーダーの出力は、優先度の高いアクティブなHigh入力に対応する(バイナリ)コードになります。このエンコーダーはpriority encoder。

プライオリティエンコーダ

4〜2プライオリティエンコーダには、4つの入力Y 3、Y 2、Y 1&Y 0、および2つの出力A 1&A0があります。ここで、入力は、Y 3は、入力に対し、最も高い優先度を有し、Y 0は最も低い優先度を有しています。この場合、複数の入力が同時に「1」であっても、出力は入力に対応する(バイナリ)コードになります。higher priority。

もう1つ検討しました output, V 出力で利用可能なコードが有効かどうかを知るために。

エンコーダーの少なくとも1つの入力が「1」の場合、出力で使用可能なコードは有効なコードです。この場合、出力Vは1に等しくなります。

エンコーダのすべての入力が「0」の場合、出力で使用可能なコードは有効なコードではありません。この場合、出力Vは0に等しくなります。

ザ・ Truth table 4〜2のプライオリティエンコーダの例を以下に示します。

| 入力 | 出力 | |||||

|---|---|---|---|---|---|---|

| Y3 | Y2 | Y1 | Y0 | A1 | A0 | V |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 0 | 1 | バツ | 0 | 1 | 1 |

| 0 | 1 | バツ | バツ | 1 | 0 | 1 |

| 1 | バツ | バツ | バツ | 1 | 1 | 1 |

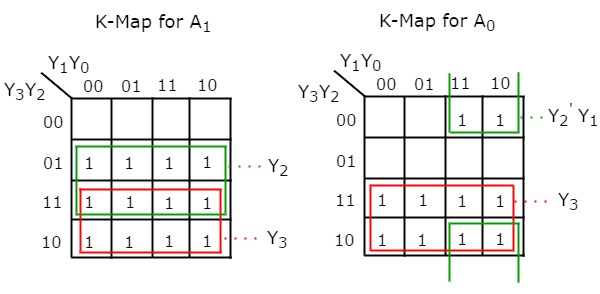

使用する 4 variable K-maps 各出力の簡略化された式を取得するため。

簡略化 Boolean functions です

$$ A_ {1} = Y_ {3} + Y_ {2} $$

$ A_ {0} = Y_ {3} + {Y_ {2}} 'Y_ {1} $

同様に、出力のブール関数Vを次のように取得します。

$$ V = Y_ {3} + Y_ {2} + Y_ {1} + Y_ {0} $$

論理ゲートを使用して、上記のブール関数を実装できます。ザ・circuit diagram 次の図に、4〜2のプライオリティエンコーダを示します。

上記の回路図には、2つの2入力ORゲート、1つの4入力ORゲート、1つの2入力ANDゲート、およびインバータが含まれています。ここで、ANDゲートとインバータの組み合わせは、複数の入力が同時に「1」に等しい場合でも、出力で有効なコードを生成するために使用されます。したがって、この回路は4つの入力を2ビットでエンコードします。priority 各入力に割り当てられます。