プログラマブルロジックデバイス

プログラマブルロジックデバイス (PLDs)集積回路です。これらには、ANDゲートの配列とORゲートの別の配列が含まれています。アレイのタイプに基づいて3種類のPLDがあり、プログラム可能な機能を備えています。

- プログラム可能な読み取り専用メモリ

- プログラマブルアレイロジック

- プログラマブルロジックアレイ

これらのデバイスに情報を入力するプロセスは、 programming。基本的に、ユーザーはこれらのデバイスまたはICを電気的にプログラムして、要件に基づいてブール関数を実装できます。ここで、プログラミングという用語はハードウェアプログラミングを指しますが、ソフトウェアプログラミングは指しません。

プログラム可能な読み取り専用メモリ(PROM)

読み取り専用メモリ(ROM)は、バイナリ情報を永続的に保存するメモリデバイスです。つまり、保存されている情報を後で変更することはできません。ROMにプログラム可能な機能がある場合、それは次のように呼ばれます。Programmable ROM (PROM)。ユーザーは、PROMプログラマーを使用してバイナリ情報を一度電気的にプログラムする柔軟性を持っています。

PROMは、固定ANDアレイとプログラマブルORアレイを備えたプログラマブルロジックデバイスです。ザ・block diagram PROMの概要を次の図に示します。

ここで、ANDゲートの入力はプログラム可能なタイプではありません。したがって、それぞれn個の入力を持つ2 n個のANDゲートを使用して、2n個の積項を生成する必要があります。nx2 nデコーダーを使用して、これらの製品用語を実装できます。したがって、このデコーダーは「n」を生成しますmin terms。

ここで、ORゲートの入力はプログラム可能です。つまり、ANDゲートのすべての出力が各ORゲートへの入力として適用されるため、必要な積項をいくつでもプログラムできます。したがって、PROMの出力は次の形式になります。sum of min terms。

例

以下を実装しましょう Boolean functions PROMを使用します。

$$ A(X、Y、Z)= \ sum m \ left(5,6,7 \ right)$$

$$ B(X、Y、Z)= \ sum m \ left(3,5,6,7 \ right)$$

与えられた2つの関数は最小項形式の合計であり、各関数には3つの変数X、Y、Zがあります。したがって、これら2つの関数を生成するには、3〜8個のデコーダーと2つのプログラム可能なORゲートが必要です。対応しますPROM 次の図に示します。

ここで、3〜8デコーダーは8分の項を生成します。2つのプログラム可能なORゲートは、これらすべての最小項にアクセスできます。ただし、各ORゲートによってそれぞれのブール関数を生成するために、必要な最小項のみがプログラムされます。記号「X」は、プログラム可能な接続に使用されます。

プログラマブルアレイロジック(PAL)

PALは、プログラマブルANDアレイと固定ORアレイを備えたプログラマブルロジックデバイスです。PALの利点は、プログラム可能なANDゲートを使用してすべての最小項を生成する代わりに、ブール関数の必要な積項のみを生成できることです。ザ・block diagram PALの値を次の図に示します。

ここで、ANDゲートの入力はプログラム可能です。つまり、各ANDゲートには、変数の通常の入力と補完された入力の両方があります。したがって、要件に基づいて、これらの入力のいずれかをプログラムできます。したがって、必要なものだけを生成できますproduct terms これらのANDゲートを使用します。

ここで、ORゲートの入力はプログラム可能なタイプではありません。したがって、各ORゲートへの入力数は固定タイプになります。したがって、これらの必要な積項を入力として各ORゲートに適用します。したがって、PALの出力は次の形式になります。sum of products form。

例

以下を実装しましょう Boolean functions PALを使用します。

$$ A = XY + X {Z} '$$

$$ A = X {Y} '+ Y {Z}' $$

与えられた2つの関数は、製品形式の合計です。各ブール関数には2つの積項があります。したがって、これら2つの関数を生成するには、4つのプログラム可能なANDゲートと2つの固定ORゲートが必要です。対応しますPAL 次の図に示します。

ザ・ programmable AND gates変数の通常の入力と補完された入力の両方にアクセスできます。上の図では、入力X、$ {X} '$、Y、$ {Y}' $、Z、および$ {Z} '$は、各ANDゲートの入力で使用できます。したがって、各ANDゲートで1つの積項を生成するために、必要なリテラルのみをプログラムします。記号「X」は、プログラム可能な接続に使用されます。

ここで、ORゲートの入力は固定タイプです。したがって、必要な製品用語は、それぞれの入力に接続されていますOR gate。そのため、ORゲートはそれぞれのブール関数を生成します。象徴 '。' 固定接続に使用されます。

プログラマブルロジックアレイ(PLA)

PLAは、プログラマブルANDアレイとプログラマブルORアレイの両方を備えたプログラマブルロジックデバイスです。したがって、これは最も柔軟なPLDです。ザ・block diagram PLAの概要を次の図に示します。

ここで、ANDゲートの入力はプログラム可能です。つまり、各ANDゲートには、変数の通常の入力と補完された入力の両方があります。したがって、要件に基づいて、これらの入力のいずれかをプログラムできます。したがって、必要なものだけを生成できますproduct terms これらのANDゲートを使用します。

ここでは、ORゲートの入力もプログラム可能です。したがって、ANDゲートのすべての出力が各ORゲートへの入力として適用されるため、必要な積項をいくつでもプログラムできます。したがって、PALの出力は次の形式になります。sum of products form。

例

以下を実装しましょう Boolean functions PLAを使用します。

$$ A = XY + X {Z} '$$

$$ B = X {Y} '+ YZ + X {Z}' $$

与えられた2つの関数は、製品形式の合計です。与えられたブール関数AとBに存在する積項の数は、それぞれ2と3です。1つの積項、$ {Z} 'X $は各関数で共通です。

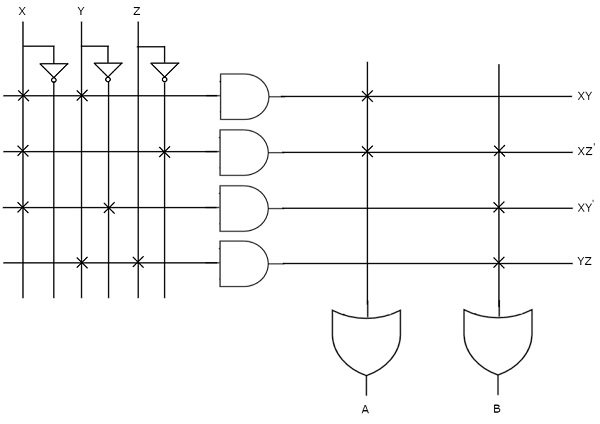

したがって、これら2つの関数を生成するには、4つのプログラム可能なANDゲートと2つのプログラム可能なORゲートが必要です。対応しますPLA 次の図に示します。

ザ・ programmable AND gates変数の通常の入力と補完された入力の両方にアクセスできます。上の図では、入力X、$ {X} '$、Y、$ {Y}' $、Z、および$ {Z} '$は、各ANDゲートの入力で使用できます。したがって、各ANDゲートで1つの積項を生成するために、必要なリテラルのみをプログラムします。

これらの製品用語はすべて、それぞれの入力で入手できます。 programmable OR gate。ただし、各ORゲートでそれぞれのブール関数を生成するには、必要な積項のみをプログラムしてください。記号「X」は、プログラム可能な接続に使用されます。