デジタル回路-クイックガイド

記数法の基数または基数が「r」の場合、その記数法に存在する数は0からr-1の範囲です。その記数法に存在する総数は「r」です。したがって、基数の値を2以上に選択することにより、さまざまな数値システムを取得します。

この章では、 popular number systemsそして、それぞれの記数法で数を表す方法。以下の番号体系が最も一般的に使用されています。

- 10進法

- 2進数システム

- 8進数システム

- 16進数システム

10進法

ザ・ base または10進法の基数は 10。したがって、この記数法では0から9の範囲の番号が使用されます。の左側にある番号の部分decimal point整数部分として知られています。同様に、小数点の右側にある数値の部分は、小数部分と呼ばれます。

この数システムにおける、10の重みを有する小数点の左側に連続する位置0、10 1、10 2、10 3等。同様に、連続的な10の重みを有する小数点の右側に位置-1、10 -2、10 -3など。つまり、各位置には特定の重みがあります。power of base 10

例

考えます decimal number 1358.246。この数の整数部分は1358であり、この数の小数部分は0.246です。数字8、5、3及び1 100、101、10の重み有する2及び10 3それぞれ。同様に、数字2,4および6が10の重み有する-1、10 -2、10 -3それぞれ。

Mathematically、次のように書くことができます

1358.246 =(1×10 3)+(3×10 2)+(5×10 1)+(8×10 0)+(2×10 -1)+

(4×10 -2)+(6×10 -3)

右側の項を単純化した後、左側にある10進数を取得します。

2進数システム

すべてのデジタル回路とシステムは、この2進数システムを使用しています。ザ・base またはこの記数法の基数は 2。したがって、この記数法では0と1の数字が使用されます。

の左側にある番号の部分 binary point整数部分として知られています。同様に、2進小数点の右側にある数値の部分は、小数部分と呼ばれます。

この番号システムにおいて、2の重量を有する二進小数点の左側に連続する位置0、2 1、2 2、2 3とでそうします。同様に、連続する2の重量を有する二進小数点の右に位置-1、2 -2、2 -3など。つまり、各位置には特定の重みがあります。power of base 2。

例

考えます binary number 1101.011。この数の整数部分は1101であり、この数の小数部分は0.011です。整数部の桁1、0、1、1 2の重み有する0、2 1、2 2、2 3それぞれ。同様に、小数部の桁0、1、1 2の重み有する-1 2、-2、2 -3それぞれ。

Mathematically、次のように書くことができます

1101.011 =(1×2 3)+(1×2 2)+(0×2 1)+(1×2 0)+(0×2 -1)+

(1×2 -2)+(1×2 -3)

右側の項を単純化すると、左側の2進数に相当する10進数が得られます。

8進数システム

ザ・ base または8進数システムの基数は 8。したがって、この記数法では0から7の範囲の番号が使用されます。の左側にある番号の部分octal point整数部分として知られています。同様に、8進数のポイントの右側にある数の部分は、小数部分として知られています。

この番号システムでは、8の重みを有する進ポイントの左に連続する位置0、8 1、8 2、8 3とでそうします。同様に、8の重みを有する進小数点の右に連続する位置-1、8 -2、8 -3などを。つまり、各位置には特定の重みがあります。power of base 8。

例

考えます octal number 1457.236。この数の整数部分は1457であり、この数の小数部分は0.236です。数字7、5、4、および1 8の重みを有する0、8 1、8 2及び8 3それぞれ。同様に、数字2,3および6は、8の重みを有する-1、8 -2、8 -3それぞれ。

Mathematically、次のように書くことができます

1457.236 =(1×8 3)+(4×8 2)+(5×8 1)+(7×8 0)+(2×8 -1)+

(3×8 -2)+(6×8 -3)

右側の項を単純化すると、左側の8進数に相当する10進数が得られます。

16進数システム

ザ・ base または16進数の基数-10進法は 16。したがって、この記数法では、0から9までの数字とAからFまでの文字が使用されます。AからFまでの16進数に相当する10進数は10から15です。

の左側にある番号の部分 hexadecimal point整数部分として知られています。同様に、16進小数点の右側にある数値の部分は、小数部分と呼ばれます。

この数システムにおける、16の量を有するヘキサ小数点の左側に連続する位置0、16 1、16 2、16 3等。同様に、16の量を有するヘキサ小数点の右側に連続する位置-1、16 -2、16 -3などを。つまり、各位置には特定の重みがあります。power of base 16。

例

考えます Hexa-decimal number 1A05.2C4。この数値の整数部分は1A05であり、この数値の小数部分は0.2C4です。数字5、0、A 1は、16の重み有する0、16 1、16 2及び16 3をそれぞれ。同様に、桁2、C及び4は、16の重み有する-1、16 -2および16 -3それぞれ。

Mathematically、次のように書くことができます

1A05.2C4 =(1×16 3)+(10×16 2)+(0×16 1)+(5×16 0)+(2×16 -1)+

(12×16 -2)+(4×16 -3)

右側の項を単純化すると、左側の16進数に相当する10進数が得られます。

前の章では、4つの著名な数体系を見てきました。この章では、同等の値を見つけるために、ある記数法から別の記数法に数値を変換してみましょう。

10進数から他の基数への変換

10進数に整数部分と小数部分の両方が含まれている場合は、10進数の両方の部分を個別に他の底に変換します。10進数を任意の基数「r」の同等の数に変換するには、次の手順に従います。

行う division 10進数の整数部分と successive quotients底が「r」で、商がゼロになるまで余りを書き留めます。剰余を逆の順序で検討して、同等の数のベース 'r'の整数部分を取得します。つまり、最初と最後の余りは、それぞれ最下位桁と最上位桁を示します。

行う multiplication 10進数の小数部分の successive fractionsベース「r」を使用して、結果がゼロになるか、必要な数の同等の桁が得られるまで、キャリーを書き留めます。同等の数の塩基「r」の小数部分を取得するために、通常のキャリーシーケンスを検討してください。

10進数から2進数への変換

10進数を同等の2進数に変換しながら、次の2種類の演算が実行されます。

- 2を底とする整数部分と連続する商の除算。

- 小数部と連続する小数の基数2による乗算。

Example

考えます decimal number 58.25。ここで、整数部分は58で、小数部分は0.25です。

Step 1 −58の除算と基数2の連続する商。

| 操作 | 商 | 残り |

|---|---|---|

| 58/2 | 29 | 0 (LSB) |

| 29/2 | 14 | 1 |

| 14/2 | 7 | 0 |

| 7/2 | 3 | 1 |

| 3/2 | 1 | 1 |

| 1/2 | 0 | 1(MSB) |

⇒(58)10 =(111010)2

したがって、 integer part 同等の2進数の 111010。

Step 2 −基数2による0.25および連続する分数の乗算。

| 操作 | 結果 | 運ぶ |

|---|---|---|

| 0.25 x 2 | 0.5 | 0 |

| 0.5 x 2 | 1.0 | 1 |

| - | 0.0 | - |

⇒(.25)10 =(。01)2

したがって、 fractional part 同等の2進数の .01

⇒(58.25)10 =(111010.01)2

したがって、 binary equivalent 10進数58.25のは111010.01です。

10進数から8進数への変換

10進数を同等の8進数に変換しながら、次の2種類の演算が実行されます。

整数部分と基数8の連続する商の除算。

小数部とそれに続く小数の基数8による乗算。

Example

考えます decimal number 58.25。ここで、整数部分は58で、小数部分は0.25です。

Step 1 −58の除算と基数8の連続する商。

| 操作 | 商 | 残り |

|---|---|---|

| 58/8 | 7 | 2 |

| 7/8 | 0 | 7 |

⇒(58)10 =(72)8

したがって、 integer part 同等の8進数の 72。

Step 2 −基数8による0.25および連続する分数の乗算。

| 操作 | 結果 | 運ぶ |

|---|---|---|

| 0.25 x 8 | 2.00 | 2 |

| - | 0.00 | - |

⇒(.25)10 =(。2)8

したがって、 fractional part 同等の8進数の.2

⇒(58.25)10 =(72.2)8

したがって、 octal equivalent 10進数の58.25は72.2です。

10進数から16進数への変換-10進数の変換

10進数を同等の16進数に変換しながら、次の2種類の演算が実行されます。

- 整数部分と16を底とする連続する商の除算。

- 小数部とそれに続く16進数の分数の乗算。

Example

考えます decimal number 58.25。ここで、整数部分は58、小数部分は0.25です。

Step 1 −58の除算と基数16の連続する商。

| 操作 | 商 | 残り |

|---|---|---|

| 58/16 | 3 | 10 = A |

| 3/16 | 0 | 3 |

⇒(58)10 =(3A)16

したがって、 integer part 同等の16進数の10進数は3Aです。

Step 2 −基数16による0.25および連続する分数の乗算。

| 操作 | 結果 | 運ぶ |

|---|---|---|

| 0.25 x 16 | 4.00 | 4 |

| - | 0.00 | - |

⇒(.25)10 =(。4)16

したがって、 fractional part 同等の16進数の10進数は.4です。

⇒(58.25)10 = (3A.4)16

したがって、 Hexa-decimal equivalent 10進数58.25のは3A.4です。

2進数から他の基数への変換

数値を2進数から10進数に変換するプロセスは、2進数を他の基数に変換するプロセスとは異なります。ここで、2進数から10進数、8進数、16進数への変換について1つずつ説明します。

2進化から10進への変換

2進数を同等の10進数に変換するには、最初に2進数のビットにそれぞれの位置の重みを掛けてから、それらすべての積を加算します。

Example

考えます binary number 1101.11。

Mathematically、次のように書くことができます

(1101.11)2 =(1×2 3)+(1×2 2)+(0×2 1)+(1×2 0)+(1×2 -1)+

(1×2 -2)

⇒(1101.11)2 = 8 + 4 + 0 + 1 + 0.5 + 0.25 = 13.75

⇒(1101.11)2 =(13.75)10

したがって、 decimal equivalent 2進数1101.11のは13.75です。

2進数から8進数への変換

2進数と8進数のシステムの底はそれぞれ2と8であることがわかっています。2 3 = 8であるため、3ビットの2進数は1つの8進数に相当します。

2進数を同等の8進数に変換するには、次の2つの手順に従います。

バイナリポイントから開始し、バイナリポイントの両側に3ビットのグループを作成します。3ビットのグループを作成するときに1ビットまたは2ビットが少ない場合は、極端な側に必要な数のゼロを含めます。

3ビットの各グループに対応する8進数を書き込みます。

Example

考えます binary number 101110.01101。

Step 1 −バイナリポイントの両側に3ビットのグループを作成します。

101 110.011 01

ここで、バイナリポイントの右側では、最後のグループは2ビットしかありません。したがって、3ビットのグループにするために、極端な側に1つのゼロを含めます。

⇒101110.011010

Step 2 −3ビットの各グループに対応する8進数を書き込みます。

⇒(101 110.011 010)2 =(56.32)8

したがって、 octal equivalent 2進数の101110.01101は56.32です。

2進数から16進数への変換-10進数の変換

2進数と16進数のシステムの基数はそれぞれ2と16であることがわかっています。2 4 = 16であるため、4ビットの2進数は1つの16進数に相当します。

2進数を同等の16進数に変換するには、次の2つの手順に従います。

バイナリポイントから開始し、バイナリポイントの両側に4ビットのグループを作成します。4ビットのグループを作成しているときに一部のビットが少ない場合は、極端な側に必要な数のゼロを含めます。

4ビットの各グループに対応する16進数を書き込みます。

Example

考えます binary number 101110.01101

Step 1 −バイナリポイントの両側に4ビットのグループを作成します。

10 1110.0110 1

ここで、最初のグループは2ビットしかありません。したがって、4ビットのグループにするために、極端な側に2つのゼロを含めます。同様に、最後のグループも4ビットのグループにするために、極端な側に3つのゼロを含めます。

⇒00101110.01101000

Step 2 −4ビットの各グループに対応する16進数を書き込みます。

⇒(0010 1110.0110 1000)2 =(2E.68)16

したがって、 Hexa-decimal equivalent 2進数の101110.01101は(2E.68)です。

8進数から他の基数への変換

数値を8進数から10進数に変換するプロセスは、8進数を他の基数に変換するプロセスとは異なります。ここで、8進数から10進数、2進数、16進数への変換について1つずつ説明します。

8進数から10進数への変換

8進数を同等の10進数に変換するには、最初に8進数の桁にそれぞれの位置の重みを掛けてから、それらすべての積を加算します。

Example

考えます octal number 145.23。

Mathematically、次のように書くことができます

(145.23)8 =(1×8 2)+(4×8 1)+(5×8 0)+(2×8 -1)+(3×8 -2)

⇒(145.23)8 = 64 + 32 + 5 + 0.25 + 0.05 = 101.3

⇒(145.23)8 =(101.3)10

したがって、 decimal equivalent 8進数の145.23は101.3です。

8進数から2進数への変換

8進数を同等の2進数に変換するプロセスは、2進数から8進数に変換するプロセスとは正反対です。各8進数を3ビットで表すことにより、同等の2進数が得られます。

Example

考えます octal number 145.23。

各8進数を3ビットで表します。

(145.23)8 =(001 100 101.010 011)2

極端な側にあるゼロを削除しても、値は変化しません。

⇒(145.23)8 =(1100101.010011)2

したがって、 binary equivalent 8進数145.23のは1100101.010011です。

8進数から16進数への変換-10進数の変換

8進数を同等の16進数に変換するには、次の2つの手順に従います。

- 8進数を同等の2進数に変換します。

- 上記の2進数を同等の16進数に変換します。

Example

考えます octal number 145.23

前の例では、8進数145.23に相当する2進数を1100101.010011として取得しました。

2進数から16進数への変換の手順に従うことにより、次のようになります。

(1100101.010011)2 =(65.4C)16

⇒(145.23)8 =(65.4C)16

したがって、 Hexa-decimal equivalent進数145.23の65.4であるC。

16進数-10進数から他の基数への変換

数値を16進数から10進数に変換するプロセスは、16進数を他の基数に変換するプロセスとは異なります。ここで、16進数から10進数、2進数、8進数への変換について1つずつ説明します。

16進数から10進数への変換

16進数を同等の10進数に変換するには、最初に16進数の桁にそれぞれの位置の重みを掛けてから、それらすべての積を加算します。

Example

考えます Hexa-decimal number 1A5.2

Mathematically、次のように書くことができます

(1A5.2)16 =(1×16 2)+(10×16 1)+(5×16 0)+(2×16 -1)

⇒(1A5.2)16 = 256 + 160 + 5 + 0.125 = 421.125

⇒(1A5.2)16 =(421.125)10

したがって、 decimal equivalent 16進数の10進数1A5.2は421.125です。

16進数から2進数への変換

16進数を同等の2進数に変換するプロセスは、2進数から16進数に変換するプロセスとは正反対です。各16進数を4ビットで表すことにより、同等の2進数が得られます。

Example

考えます Hexa-decimal number 65.4C

各16進数を4ビットで表します。

(65.4C)6 =(0110 0101.0100 1100)2

2つの極端な側にあるゼロを削除しても、値は変化しません。

⇒(65.4C)16 =(1100101.010011)2

したがって、 binary equivalent 16進数の10進数65.4Cは1100101.010011です。

16進数から10進数への変換

16進数を同等の8進数に変換するには、次の2つの手順に従います。

- 16進数を同等の2進数に変換します。

- 上記の2進数を同等の8進数に変換します。

Example

考えます Hexa-decimal number 65.4C

前の例では、16進数の65.4Cに相当する2進数を1100101.010011として取得しました。

2進数から8進数への変換の手順に従うことにより、次のようになります。

(1100101.010011)2 =(145.23)8

⇒(65.4C)16 =(145.23)

したがって、 octal equivalentヘキサ進数65.4 Cは145.23です。

2進数は次の2つのグループに分類できます- Unsigned numbers そして Signed numbers。

符号なし番号

符号なしの数値には、数値の大きさのみが含まれます。彼らには何の兆候もありません。これは、すべての符号なし2進数が正であることを意味します。10進数システムと同様に、数値の前に正の符号を配置することは、正の数値を表すためにオプションです。したがって、数値の前に正の符号が割り当てられていない場合、ゼロを含むすべての正の数値は符号なし数値として扱うことができます。

符号付き数値

符号付き数値には、数値の符号と大きさの両方が含まれます。通常、記号は数字の前に配置されます。したがって、正の数の場合は正の符号、負の数の場合は負の符号を考慮する必要があります。したがって、対応する符号が番号の前に割り当てられている場合、すべての番号を符号付き数値として扱うことができます。

符号ビットがゼロの場合、2進数が正であることを示します。同様に、符号ビットが1の場合、2進数が負であることを示します。

符号なし2進数の表現

符号なし2進数に存在するビットは、 magnitude数の。つまり、符号なし2進数にが含まれている場合‘N’ ビット、それからすべて N 符号ビットがないため、ビットは数値の大きさを表します。

Example

考えます decimal number 108。この数に相当する2進数は1101100。これは、符号なし2進数の表現です。

(108)10 =(1101100)2

それは7ビットを持っています。これらの7ビットは、数値108の大きさを表します。

符号付き2進数の表現

符号付き2進数の最上位ビット(MSB)は、数値の符号を示すために使用されます。したがって、それはまた呼ばれますsign bit。正の符号は、符号ビットに「0」を入れることで表されます。同様に、負の符号は、符号ビットに「1」を入れることによって表されます。

符号付き2進数に「N」ビットが含まれている場合、1ビット(MSB)は数値の符号を表すために予約されているため、(N-1)ビットは数値の大きさのみを表します。

3つあります types of representations 符号付き2進数の場合

- サイン-マグニチュードフォーム

- 1の補数形式

- 2の補数形式

これら3つの形式すべてでの正の数の表現は同じです。ただし、各形式で異なるのは負の数の表現のみです。

Example

考えます positive decimal number +108。この数の大きさに相当する2進数は1101100です。これらの7ビットは数108の大きさを表します。正の数であるため、大きさの左端に配置される符号ビットをゼロと見なします。

(+108)10 =(01101100)2

したがって、 signed binary representation正の10進数の+108はです。したがって、同じ表現は、符号の大きさの形式、1の補数形式、および正の10進数+108の2の補数形式で有効です。

サイン-マグニチュードフォーム

符号の大きさの形式では、MSBは表現に使用されます sign 数の残りのビットは magnitude数の。したがって、符号なし2進数の左端に符号ビットを含めるだけです。この表現は、符号付き10進数の表現に似ています。

Example

考えます negative decimal number -108。この数の大きさは108です。108の符号なし2進表現は1101100であることがわかっています。7ビットです。これらのビットはすべて大きさを表します。

与えられた数は負であるため、符号ビットを1と見なします。これは、大きさの左端に配置されます。

(−108)10 =(11101100)2

したがって、-108の符号と大きさの表現は次のようになります。 11101100。

1の補数形式

数値の1の補数は、次の式で得られます。 complementing all the bits符号付き2進数の。したがって、正の数の1の補数は、負の数になります。同様に、負の数の1の補数は正の数を与えます。

つまり、符号ビットを含む2進数の1の補数を2回実行すると、元の符号付き2進数が得られます。

Example

考えます negative decimal number -108。この数の大きさは108です。108の符号付き2進表現は01101100であることがわかっています。

それは8ビットを持っています。この数のMSBはゼロであり、正の数を示します。ゼロの補数は1であり、その逆も同様です。したがって、負の数を取得するには、0を1に、1を0に置き換えます。

(−108)10 =(10010011)2

したがって、 1’s complement of (108)10 です (10010011)2。

2の補数形式

2進数の2の補数は、次の式で得られます。 adding one to the 1’s complement符号付き2進数の。したがって、正の数の2の補数は、負の数になります。同様に、負の数の2の補数は正の数を与えます。

つまり、符号ビットを含む2の2の補数を2回実行すると、元の符号付き2進数が得られます。

Example

考えます negative decimal number -108。

(の1の補数を知っています108)10 は(10010011)2

(108)10の2の補数=(108)10 +1の1の補数。

= 10010011 + 1

= 10010100

したがって、 2’s complement of (108)10 です (10010100)2。

この章では、2の補数法を使用して任意の2つの符号付き2進数に対して実行できる基本的な算術演算について説明します。ザ・basic arithmetic operations 足し算と引き算です。

2つの符号付き2進数の追加

2の補数形式で表される2つの符号付き2進数AおよびBについて考えてみます。実行できますadditionこれらの2つの数値のうち、2つの符号なし2進数の加算に似ています。ただし、結果の合計に符号ビットからの実行が含まれている場合は、正しい値を取得するためにそれを破棄(無視)します。

結果の合計が正の場合、その大きさを直接見つけることができます。ただし、結果の合計が負の場合は、大きさを取得するために2の補数を取ります。

例1

実行しましょう addition 2つの10進数の +7 and +4 2の補数法を使用します。

ザ・ 2’s complement それぞれ5ビットの+7と+4の表現を以下に示します。

(+7)10 =(00111)2

(+4)10 =(00100)2

これらの2つの数字の加算は

(+7)10 +(+ 4)10 =(00111)2 +(00100)2

⇒(+7)10 +(+ 4)10 =(01011)2。

結果の合計には5ビットが含まれます。したがって、符号ビットからの実行はありません。符号ビット「0」は、結果の合計がpositive。したがって、合計の大きさは10進数で11です。したがって、2つの正の数を加算すると、別の正の数が得られます。

例2

実行しましょう addition 2つの10進数の -7 そして -4 2の補数法を使用します。

ザ・ 2’s complement それぞれ5ビットの-7と-4の表現を以下に示します。

(−7)10 =(11001)2

(−4)10 =(11100)2

これらの2つの数字の加算は

(−7)10 +(− 4)10 =(11001)2 +(11100)2

⇒(−7)10 +(− 4)10 =(110101)2。

結果の合計には6ビットが含まれます。この場合、キャリーは符号ビットから取得されます。だから、私たちはそれを取り除くことができます

キャリーを削除した後の結果の合計は(-7)10 +(-4)10 =(10101)2。

符号ビット「1」は、結果の合計が negative。したがって、2の補数を取ることにより、結果の合計の大きさを10進数システムで11として取得します。したがって、2つの負の数を加算すると、別の負の数が得られます。

2つの符号付き2進数の減算

2の補数形式で表される2つの符号付き2進数AおよびBについて考えてみます。正の数の2の補数が負の数になることはわかっています。したがって、数Aから数Bを引く必要があるときはいつでも、Bの2の補数を取り、それをAに加算します。mathematically 私たちはそれを次のように書くことができます

A - B = A + (2's complement of B)

同様に、数Bから数Aを引く必要がある場合は、Aの2の補数を取り、それをBに加算します。 mathematically 私たちはそれを次のように書くことができます

B - A = B + (2's complement of A)

したがって、2つの符号付き2進数の減算は、2つの符号付き2進数の加算に似ています。ただし、減算されるはずの数の2の補数を取る必要があります。これはadvantage2の補数手法の。2つの符号付き2進数を加算する同じ規則に従います。

例3

実行しましょう subtraction 2つの10進数の +7 and +4 2の補数法を使用します。

これらの2つの数値の減算は

(+7)10 −(+ 4)10 =(+ 7)10 +(− 4)10。

ザ・ 2’s complement +7と-4をそれぞれ5ビットで表したものを以下に示します。

(+7)10 =(00111)2

(+4)10 =(11100)2

⇒(+7)10 +(+ 4)10 =(00111)2 +(11100)2 =(00011)2

ここでは、符号ビットから得られるキャリー。だから、私たちはそれを取り除くことができます。キャリーを削除した後の結果の合計は

(+7)10 +(+ 4)10 =(00011)2

符号ビット「0」は、結果の合計が positive。したがって、その大きさは10進数で3です。したがって、2つの10進数+7と+4を引くと+3になります。

例4

実行しましょう subtraction of 2つの10進数 +4 そして +7 2の補数法を使用します。

これらの2つの数値の減算は

(+4)10 −(+ 7)10 =(+ 4)10 +(− 7)10。

ザ・ 2’s complement +4と-7をそれぞれ5ビットで表したものを以下に示します。

(+4)10 =(00100)2

(-7)10 =(11001)2

⇒(+4)10 +(-7)10 =(00100)2 +(11001)2 =(11101)2

ここで、キャリーは符号ビットから取得されません。符号ビット「1」は、結果の合計がnegative。したがって、2の補数を取ることにより、結果の合計の大きさを10進数システムで3として取得します。したがって、2つの10進数+4と+7を引くと-3になります。

コーディングにおいて、数字または文字が特定の記号のグループによって表される場合、その数字または文字がエンコードされていると言われます。シンボルのグループは、code。デジタルデータは、ビットのグループとして表され、保存され、送信されます。このビットのグループは、binary code。

バイナリコードは2つのタイプに分類できます。

- 加重コード

- 重み付けされていないコード

コードに位置の重みがある場合、次のようになります。 weighted code。それ以外の場合は、重み付けされていないコードです。加重コードは、正の加重コードと負の加重コードにさらに分類できます。

10進数のバイナリコード

次の表に、10進数の0から9までのさまざまなバイナリコードを示します。

| 10進数 | 8421コード | 2421コード | 84-2-1コード | 過剰3コード |

|---|---|---|---|---|

| 0 | 0000 | 0000 | 0000 | 0011 |

| 1 | 0001 | 0001 | 0111 | 0100 |

| 2 | 0010 | 0010 | 0110 | 0101 |

| 3 | 0011 | 0011 | 0101 | 0110 |

| 4 | 0100 | 0100 | 0100 | 0111 |

| 5 | 0101 | 1011 | 1011 | 1000 |

| 6 | 0110 | 1100 | 1010 | 1001 |

| 7 | 0111 | 1101 | 1001 | 1010 |

| 8 | 1000 | 1110 | 1000 | 1011 |

| 9 | 1001 | 1111 | 1111 | 1100 |

10進数で10桁あります。これらの10桁をバイナリで表すには、最低4ビットが必要です。ただし、4ビットでは、0と1の16の一意の組み合わせがあります。10進数は10桁しかないため、他の6つの0と1の組み合わせは必要ありません。

8 4 21コード

このコードの重みは8、4、2、および1です。

このコードにはすべて正の重みがあります。だから、それはpositively weighted code。

このコードは、 natural BCD (2進化10進数) code。

Example

10進数786に相当するBCDを見つけましょう。この数値には10進数の3桁の7、8、6があります。表から、7、8、6のBCD(8421)コードはそれぞれ0111、1000、0110と書くことができます。 。

∴ (786)10 = (011110000110)BCD

10進数の各BCDコードは4ビットであるため、BCD表現には12ビットがあります。

2 4 21コード

このコードの重みは2、4、2、1です。

このコードにはすべて正の重みがあります。だから、それはpositively weighted code。

それは unnatural BCDコード。不自然なBCDコードの重みの合計は9に等しい。

それは self-complementingコード。自己補完コードは、同等の2421表現で1と0を交換するだけで、10進数の9の補数を提供します。

Example

10進数786に相当する2421を見つけましょう。この数値には10進数の3桁の7、8、6があります。表から、7、8、6の2421コードはそれぞれ1101、1110、1100と書くことができます。

したがって、10進数786に相当する2421は次のようになります。 110111101100。

8 4 -2-1コード

このコードの重みは8、4、-2、および-1です。

このコードには、正の重みとともに負の重みがあります。だから、それはnegatively weighted code。

それは unnatural BCD コード。

それは self-complementing コード。

Example

10進数786に相当する84-2-1を見つけましょう。この数値には10進数の3桁の7、8、6があります。表から、7、8、6の8 4 -2-1コードを記述できます。それぞれ1001、1000、1010です。

したがって、10進数786に相当する8 4 -2-1は次のようになります。 100110001010。

過剰な3コード

このコードには重みがありません。だから、それはun-weighted code。

10進数に相当する2進数に3(0011)を加算することにより、10進数のExcess3コードを取得します。したがって、これはExcess3コードと呼ばれます。

それは self-complementing コード。

Example

10進数786に相当するExcess3を見つけましょう。この番号には10進数の3桁の7、8、6があります。表から、7、8、6のExcess 3コードはそれぞれ1010、1011、1001と書くことができます。

したがって、10進数786に相当するExcess3は次のようになります。 101010111001

グレイコード

次の表に、各4ビットバイナリコードに対応する4ビットグレイコードを示します。

| 10進数 | バイナリコード | グレイコード |

|---|---|---|

| 0 | 0000 | 0000 |

| 1 | 0001 | 0001 |

| 2 | 0010 | 0011 |

| 3 | 0011 | 0010 |

| 4 | 0100 | 0110 |

| 5 | 0101 | 0111 |

| 6 | 0110 | 0101 |

| 7 | 0111 | 0100 |

| 8 | 1000 | 1100 |

| 9 | 1001 | 1101 |

| 10 | 1010 | 1111 |

| 11 | 1011 | 1110 |

| 12 | 1100 | 1010 |

| 13 | 1101 | 1011 |

| 14 | 1110 | 1001 |

| 15 | 1111 | 1000 |

このコードには重みがありません。だから、それはun-weighted code。

上記の表では、連続するグレイコードは1ビット位置のみが異なります。したがって、このコードは次のように呼ばれます。unit distance コード。

バイナリコードからグレイコードへの変換

バイナリコードを同等のグレイコードに変換するには、次の手順に従います。

与えられたバイナリコードを検討し、MSBの左側にゼロを配置します。

ゼロから始まる連続する2ビットを比較します。2ビットが同じ場合、出力はゼロです。それ以外の場合、出力は1です。

グレイコードのLSBが取得されるまで、上記の手順を繰り返します。

Example

表から、バイナリコード1000に対応するグレイコードは1100であることがわかります。ここで、上記の手順を使用して検証します。

与えられたバイナリコードは1000です。

Step 1 − MSBの左側にゼロを配置すると、バイナリコードは01000になります。

Step 2 −新しいバイナリコードの連続する2ビットを比較することにより、グレイコードは次のようになります。 1100。

ビット0と1は、2つの異なる範囲のアナログ電圧に対応していることがわかっています。したがって、あるシステムから別のシステムへのバイナリデータの送信中に、ノイズも追加される可能性があります。このため、他のシステムで受信したデータにエラーがある可能性があります。

つまり、ビット0が1に変わるか、ビット1が0に変わる可能性があります。ノイズの干渉を回避することはできません。ただし、エラーが存在するかどうかを検出してからそれらのエラーを修正することにより、最初に元のデータを取得できます。この目的のために、次のコードを使用できます。

- エラー検出コード

- エラー訂正コード

Error detection codes−受信データ(ビットストリーム)に存在するエラーを検出するために使用されます。これらのコードには、元のビットストリームに含まれる(追加される)いくつかのビットが含まれています。これらのコードは、元のデータ(ビットストリーム)の送信中にエラーが発生した場合にエラーを検出します。Example −パリティコード、ハミングコード。

Error correction codes−は、受信データ(ビットストリーム)に存在するエラーを修正するために使用され、元のデータを取得します。エラー訂正コードも、エラー検出コードと同様の戦略を使用します。Example −ハミングコード。

したがって、エラーを検出して修正するために、送信時にデータビットに追加のビットが追加されます。

パリティコード

元のビットストリームのMSBの左側またはLSBの右側に1つのパリティビットを含める(追加する)のは簡単です。パリティコードには、選択したパリティのタイプに基づいて、偶数パリティコードと奇数パリティコードの2種類があります。

パリティコードでさえ

バイナリコードに偶数の1が存在する場合、偶数パリティビットの値はゼロである必要があります。それ以外の場合は、1つにする必要があります。そのため、偶数のeven parity code。偶数パリティコードには、データビットと偶数パリティビットが含まれます。

次の表は、 even parity codes各3ビットバイナリコードに対応します。ここでは、バイナリコードのLSBの右側に偶数パリティビットが含まれています。

| バイナリコード | Even Parity bit | Even Parity Code |

|---|---|---|

| 000 | 0 | 0000 |

| 001 | 1 | 0011 |

| 010 | 1 | 0101 |

| 011 | 0 | 0110 |

| 100 | 1 | 1001 |

| 101 | 0 | 1010 |

| 110 | 0 | 1100 |

| 111 | 1 | 1111 |

Here, the number of bits present in the even parity codes is 4. So, the possible even number of ones in these even parity codes are 0, 2 & 4.

If the other system receives one of these even parity codes, then there is no error in the received data. The bits other than even parity bit are same as that of binary code.

If the other system receives other than even parity codes, then there will be an error(s) in the received data. In this case, we can’t predict the original binary code because we don’t know the bit position(s) of error.

Therefore, even parity bit is useful only for detection of error in the received parity code. But, it is not sufficient to correct the error.

Odd Parity Code

The value of odd parity bit should be zero, if odd number of ones present in the binary code. Otherwise, it should be one. So that, odd number of ones present in odd parity code. Odd parity code contains the data bits and odd parity bit.

The following table shows the odd parity codes corresponding to each 3-bit binary code. Here, the odd parity bit is included to the right of LSB of binary code.

| Binary Code | Odd Parity bit | Odd Parity Code |

|---|---|---|

| 000 | 1 | 0001 |

| 001 | 0 | 0010 |

| 010 | 0 | 0100 |

| 011 | 1 | 0111 |

| 100 | 0 | 1000 |

| 101 | 1 | 1011 |

| 110 | 1 | 1101 |

| 111 | 0 | 1110 |

Here, the number of bits present in the odd parity codes is 4. So, the possible odd number of ones in these odd parity codes are 1 & 3.

If the other system receives one of these odd parity codes, then there is no error in the received data. The bits other than odd parity bit are same as that of binary code.

If the other system receives other than odd parity codes, then there is an error(s) in the received data. In this case, we can’t predict the original binary code because we don’t know the bit position(s) of error.

Therefore, odd parity bit is useful only for detection of error in the received parity code. But, it is not sufficient to correct the error.

Hamming Code

Hamming code is useful for both detection and correction of error present in the received data. This code uses multiple parity bits and we have to place these parity bits in the positions of powers of 2.

The minimum value of 'k' for which the following relation is correct (valid) is nothing but the required number of parity bits.

$$2^k\geq n+k+1$$

Where,

‘n’ is the number of bits in the binary code (information)

‘k’ is the number of parity bits

Therefore, the number of bits in the Hamming code is equal to n + k.

Let the Hamming code is $b_{n+k}b_{n+k-1}.....b_{3}b_{2}b_{1}$ & parity bits $p_{k}, p_{k-1}, ....p_{1}$. We can place the ‘k’ parity bits in powers of 2 positions only. In remaining bit positions, we can place the ‘n’ bits of binary code.

Based on requirement, we can use either even parity or odd parity while forming a Hamming code. But, the same parity technique should be used in order to find whether any error present in the received data.

Follow this procedure for finding parity bits.

Find the value of p1, based on the number of ones present in bit positions b3, b5, b7 and so on. All these bit positions (suffixes) in their equivalent binary have ‘1’ in the place value of 20.

Find the value of p2, based on the number of ones present in bit positions b3, b6, b7 and so on. All these bit positions (suffixes) in their equivalent binary have ‘1’ in the place value of 21.

Find the value of p3, based on the number of ones present in bit positions b5, b6, b7 and so on. All these bit positions (suffixes) in their equivalent binary have ‘1’ in the place value of 22.

Similarly, find other values of parity bits.

Follow this procedure for finding check bits.

Find the value of c1, based on the number of ones present in bit positions b1, b3, b5, b7 and so on. All these bit positions (suffixes) in their equivalent binary have ‘1’ in the place value of 20.

Find the value of c2, based on the number of ones present in bit positions b2, b3, b6, b7 and so on. All these bit positions (suffixes) in their equivalent binary have ‘1’ in the place value of 21.

Find the value of c3, based on the number of ones present in bit positions b4, b5, b6, b7 and so on. All these bit positions (suffixes) in their equivalent binary have ‘1’ in the place value of 22.

Similarly, find other values of check bits.

The decimal equivalent of the check bits in the received data gives the value of bit position, where the error is present. Just complement the value present in that bit position. Therefore, we will get the original binary code after removing parity bits.

Example 1

Let us find the Hamming code for binary code, d4d3d2d1 = 1000. Consider even parity bits.

The number of bits in the given binary code is n=4.

We can find the required number of parity bits by using the following mathematical relation.

$$2^k\geq n+k+1$$

Substitute, n=4 in the above mathematical relation.

$$\Rightarrow 2^k\geq 4+k+1$$

$$\Rightarrow 2^k\geq 5+k$$

The minimum value of k that satisfied the above relation is 3. Hence, we require 3 parity bits p1, p2, and p3. Therefore, the number of bits in Hamming code will be 7, since there are 4 bits in binary code and 3 parity bits. We have to place the parity bits and bits of binary code in the Hamming code as shown below.

The 7-bit Hamming code is $b_{7}b_{6}b_{5}b_{4}b_{3}b_{2}b_{1}=d_{4}d_{3}d_{2}p_{3}d_{1}p_{2}bp_{1}$

By substituting the bits of binary code, the Hamming code will be $b_{7}b_{6}b_{5}b_{4}b_{3}b_{2}b_{1} = 100p_{3}Op_{2}p_{1}$. Now, let us find the parity bits.

$$p_{1}=b_{7}\oplus b_{5}\oplus b_{3}=1 \oplus 0 \oplus 0=1$$

$$p_{2}=b_{7}\oplus b_{6}\oplus b_{3}=1 \oplus 0 \oplus 0=1$$

$$p_{3}=b_{7}\oplus b_{6}\oplus b_{5}=1 \oplus 0 \oplus 0=1$$

By substituting these parity bits, the Hamming code will be $b_{7}b_{6}b_{5}b_{4}b_{3}b_{2}b_{1}= 1001011$.

Example 2

In the above example, we got the Hamming code as $b_{7}b_{6}b_{5}b_{4}b_{3}b_{2}b_{1}= 1001011$. Now, let us find the error position when the code received is $b_{7}b_{6}b_{5}b_{4}b_{3}b_{2}b_{1}= 1001111$.

Now, let us find the check bits.

$$c_{1}=b_{7}\oplus b_{5}\oplus b_{3}\oplus b_{1}=1 \oplus 0 \oplus 1 \oplus1 =1$$

$$c_{2}=b_{7}\oplus b_{6}\oplus b_{3}\oplus b_{2}=1 \oplus 0 \oplus 1 \oplus1 =1$$

$$c_{3}=b_{7}\oplus b_{6}\oplus b_{5}\oplus b_{4}=1 \oplus 0 \oplus 0 \oplus1 =0$$

The decimal value of check bits gives the position of error in received Hamming code.

$$c_{3}c_{2}c_{1} = \left ( 011 \right )_{2}=\left ( 3 \right )_{10}$$

Therefore, the error present in third bit (b3) of Hamming code. Just complement the value present in that bit and remove parity bits in order to get the original binary code.

Boolean Algebra is an algebra, which deals with binary numbers & binary variables. Hence, it is also called as Binary Algebra or logical Algebra. A mathematician, named George Boole had developed this algebra in 1854. The variables used in this algebra are also called as Boolean variables.

The range of voltages corresponding to Logic ‘High’ is represented with ‘1’ and the range of voltages corresponding to logic ‘Low’ is represented with ‘0’.

Postulates and Basic Laws of Boolean Algebra

In this section, let us discuss about the Boolean postulates and basic laws that are used in Boolean algebra. These are useful in minimizing Boolean functions.

Boolean Postulates

Consider the binary numbers 0 and 1, Boolean variable (x) and its complement (x’). Either the Boolean variable or complement of it is known as literal. The four possible logical OR operations among these literals and binary numbers are shown below.

x + 0 = x

x + 1 = 1

x + x = x

x + x '= 1

同様に、4つの可能な logical AND これらのリテラルと2進数の演算を以下に示します。

x.1 = x

x.0 = 0

xx = x

x.x '= 0

これらは単純なブール仮説です。ブール変数を「0」または「1」に置き換えることで、これらの仮定を簡単に検証できます。

Note−ブール変数の補集合は、変数自体と同じです。つまり、(x ')' = xです。

ブール代数の基本法則

以下は、ブール代数の3つの基本法則です。

- 可換法則

- 結合法則

- 分配法則

可換法則

2つのブール変数の論理演算が、それらの2つの変数の順序に関係なく同じ結果をもたらす場合、その論理演算は次のようになります。 Commutative。2つのブール変数xおよびyの論理ORおよび論理AND演算を以下に示します。

x + y = y + x

xy = yx

記号「+」は論理OR演算を示します。同様に、記号「。」論理AND演算を示し、表現するのはオプションです。可換法則は、論理ORおよび論理AND演算に従います。

結合法則

任意の2つのブール変数の論理演算が最初に実行され、次に同じ演算が残りの変数で実行されて同じ結果が得られる場合、その論理演算は次のようになります。 Associative。3つのブール変数x、y、zの論理ORおよび論理AND演算を以下に示します。

x +(y + z)=(x + y)+ z

x。(yz)=(xy).z

結合法則は、論理ORおよび論理AND演算に従います。

分配法則

ブール関数に存在するすべての用語に論理演算を分散できる場合、その論理演算は次のようになります。 Distributive。3つのブール変数x、y、zの論理ORおよび論理AND演算の分布を以下に示します。

x。(y + z)= xy + xz

x +(yz)=(x + y)。(x + z)

分配法則は、論理ORおよび論理AND演算に従います。

これらはブール代数の基本法則です。ブール変数を「0」または「1」に置き換えることで、これらの法則を簡単に検証できます。

ブール代数の定理

次の2つの定理は、ブール代数で使用されます。

- 双対定理

- ド・モルガンの定理

双対定理

この定理は、 dualブール関数の値は、論理AND演算子を論理OR演算子に、0を1に交換することによって取得されます。すべてのブール関数に対して、対応するデュアル関数があります。

ブール仮説と基本法則のセクションで説明したブール方程式(関係)を2つのグループに分けてみましょう。次の表に、これら2つのグループを示します。

| グループ1 | グループ2 |

|---|---|

| x + 0 = x | x.1 = x |

| x + 1 = 1 | x.0 = 0 |

| x + x = x | xx = x |

| x + x '= 1 | x.x '= 0 |

| x + y = y + x | xy = yx |

| x +(y + z)=(x + y)+ z | x。(yz)=(xy).z |

| x。(y + z)= xy + xz | x +(yz)=(x + y)。(x + z) |

各行には2つのブール方程式があり、それらは互いに二重です。双対定理を使用して、Group1とGroup2のこれらすべてのブール方程式を検証できます。

ド・モルガンの定理

この定理は、 complement of Boolean function。これは、少なくとも2つのブール変数の論理ORの補数が、各補数変数の論理ANDに等しいことを示しています。

2つのブール変数xとyを持つドモルガンの定理は次のように表すことができます。

(x + y) '= x'.y'

上記のブール関数の双対は

(xy) '= x' + y '

したがって、2つのブール変数の論理ANDの補数は、各補数変数の論理ORに等しくなります。同様に、2つ以上のブール変数にもドモルガンの定理を適用できます。

ブール関数の簡略化

これまで、ブール代数の仮説、基本法則、定理について説明してきました。ここで、いくつかのブール関数を単純化してみましょう。

例1

私たちにさせて simplify ブール関数、f = p'qr + pq'r + pqr '+ pqr

この関数は2つの方法で簡略化できます。

Method 1

与えられたブール関数、f = p'qr + pq'r + pqr '+ pqr。

Step 1−第1項と第2項では、rが一般的であり、第3項と第4項ではpqが共通です。だから、を使用して一般的な用語を取るDistributive law。

⇒f=(p'q + pq ')r + pq(r' + r)

Step 2−最初の括弧内にある用語は、Ex-OR演算に簡略化できます。2番目の括弧内にある用語は、次を使用して「1」に簡略化できます。Boolean postulate

⇒f=(p⊕q)r + pq(1)

Step 3−最初の用語をこれ以上単純化することはできません。ただし、第2項は、を使用してpqに簡略化できます。Boolean postulate。

⇒f=(p⊕q)r + pq

したがって、簡略化されたブール関数は次のようになります。 f = (p⊕q)r + pq

Method 2

与えられたブール関数、f = p'qr + pq'r + pqr '+ pqr。

Step 1 −を使用する Boolean postulate、x + x = x。つまり、ブール変数 'n'回の論理OR演算は、同じ変数と等しくなります。したがって、最後の項pqrをさらに2回書くことができます。

⇒f= p'qr + pq'r + pqr '+ pqr + pqr + pqr

Step 2 −使用 Distributive law1番目と4番目の用語は、2番目と5番目の用語は、3番目と6番目の用語。

⇒f= qr(p '+ p)+ pr(q' + q)+ pq(r '+ r)

Step 3 −使用 Boolean postulate、x + x '= 1は、各括弧内に存在する用語を単純化するためのものです。

⇒f= qr(1)+ pr(1)+ pq(1)

Step 4 −使用 Boolean postulate、x.1 = xは、上記の3つの用語を簡略化するためのものです。

⇒f= qr + pr + pq

⇒f= pq + qr + pr

したがって、簡略化されたブール関数は次のようになります。 f = pq + qr + pr。

したがって、各メソッドで指定されたブール関数を単純化した後、2つの異なるブール関数を取得しました。機能的には、これら2つのブール関数は同じです。したがって、要件に基づいて、これら2つのブール関数のいずれかを選択できます。

例2

見つけましょう complement ブール関数のf = p'q + pq '。

ブール関数の補集合はf '=(p'q + pq') 'です。

Step 1 −ドモルガンの定理(x + y) '= x'.y'を使用します。

⇒f '=(p'q)'。(pq ')'

Step 2 −ド・モルガンの定理(xy) '= x' + y 'を使用する

⇒f '= {(p') '+ q'}。{p '+(q') '}

Step3 −ブール仮説(x ')' = xを使用します。

⇒f '= {p + q'}。{p '+ q}

⇒f '= pp' + pq + p'q '+ qq'

Step 4 −ブール仮説xx '= 0を使用します。

⇒f= 0 + pq + p'q '+ 0

⇒f= pq + p'q '

したがって、 complement ブール関数の場合、p'q + pq 'は pq + p’q’。

2つの変数xとyを論理AND演算と組み合わせることにより、4つのブール積項を取得します。これらのブール積の用語は、min terms または standard product terms。最小項は、x'y '、x'y、xy'、およびxyです。

同様に、2つの変数xとyを論理OR演算と組み合わせることにより、4つのブール和項を取得します。これらのブール和項は、Max terms または standard sum terms。最大項は、x + y、x + y '、x' + y、およびx '+ y'です。

次の表は、2つの変数の最小項と最大項の表現を示しています。

| バツ | y | 最小条件 | 最大条件 |

|---|---|---|---|

| 0 | 0 | m 0 = x'y ' | M 0 = x + y |

| 0 | 1 | m 1 = x'y | M 1 = x + y ' |

| 1 | 0 | m 2 = xy ' | M 2 = x '+ y |

| 1 | 1 | m 3 = xy | M 3 = x '+ y' |

バイナリ変数が「0」の場合、最小項では変数の補数として、最大項では変数自体として表されます。同様に、バイナリ変数が「1」の場合、最大項では変数の補数として、最小項では変数自体として表されます。

上記の表から、最小項と最大項が互いに補完し合っていることが簡単にわかります。'n'ブール変数がある場合、2n最小項と2n最大項があります。

標準的なSoPおよびPoSフォーム

真理値表は、入力と出力のセットで構成されています。'n'個の入力変数がある場合、0と1の2n個の可能な組み合わせがあります。したがって、各出力変数の値は、入力変数の組み合わせによって異なります。したがって、各出力変数は、入力変数のいくつかの組み合わせに対して「1」を持ち、入力変数の他のいくつかの組み合わせに対して「0」を持ちます。

したがって、各出力変数は次の2つの方法で表現できます。

- CanonicalSoPフォーム

- CanonicalPoSフォーム

CanonicalSoPフォーム

Canonical SoPフォームは、Canonical Sum ofProductsフォームを意味します。この形式では、各製品用語にすべてのリテラルが含まれています。したがって、これらの製品用語は最小用語に他なりません。したがって、正規のSoP形式は次のようにも呼ばれます。sum of min terms 形。

まず、出力変数が1である最小項を特定し、次にそれらの最小項の論理ORを実行して、その出力変数に対応するブール式(関数)を取得します。このブール関数は、最小項の合計の形式になります。

複数の出力変数がある場合は、他の出力変数についても同じ手順に従います。

例

次のことを考慮してください truth table。

| 入力 | 出力 | ||

|---|---|---|---|

| p | q | r | f |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

ここで、出力(f)は、入力の4つの組み合わせに対して「1」です。対応する最小項は、p'qr、pq'r、pqr '、pqrです。これらの4分間の項の論理ORを実行することにより、出力(f)のブール関数を取得します。

したがって、出力のブール関数は、f = p'qr + pq'r + pqr '+ pqrです。これはcanonical SoP form出力のf。この関数は、次の2つの表記法で表すこともできます。

$$f = m_{3}+m_{5}+m_{6}+m_{7}$$

$$f = \sum m\left ( 3,5,6,7 \right )$$

1つの方程式では、関数をそれぞれの最小項の合計として表しました。他の方程式では、これらの最小項の合計に記号を使用しました。

CanonicalPoSフォーム

Canonical PoSフォームは、Canonical Product ofSumsフォームを意味します。この形式では、各合計項にすべてのリテラルが含まれます。したがって、これらの合計項は最大項に他なりません。したがって、正規のPoS形式は次のようにも呼ばれます。product of Max terms 形。

まず、出力変数がゼロである最大項を特定し、次にそれらの最大項の論理ANDを実行して、その出力変数に対応するブール式(関数)を取得します。このブール関数は、最大項の積の形式になります。

複数の出力変数がある場合は、他の出力変数についても同じ手順に従います。

Example

前の例と同じ真理値表を考えてみましょう。ここで、出力(f)は、入力の4つの組み合わせに対して「0」です。対応する最大項は、p + q + r、p + q + r '、p + q' + r、p '+ q + rです。これらの4つのMax項の論理ANDを実行することにより、出力(f)のブール関数を取得します。

したがって、出力のブール関数は、f =(p + q + r)。(p + q + r ')。(p + q' + r)。(p '+ q + r)です。これはcanonical PoS form出力のf。この関数は、次の2つの表記法で表すこともできます。

$$f=M_{0}.M_{1}.M_{2}.M_{4}$$

$$f=\prod M\left ( 0,1,2,4 \right )$$

1つの方程式では、関数をそれぞれの最大項の積として表しました。他の方程式では、これらの最大項の乗算に記号を使用しました。

ブール関数f =(p + q + r)。(p + q + r ')。(p + q' + r)。(p '+ q + r)は、ブール関数f =の双対です。 p'qr + pq'r + pqr '+ pqr。

したがって、正規のSoP形式と正規のPoS形式の両方が Dualお互いに。機能的には、これら2つの形式は同じです。要件に基づいて、これら2つの形式のいずれかを使用できます。

標準のSoPおよびPoSフォーム

ブール出力を表す2つの標準的な形式について説明しました。同様に、ブール出力を表す2つの標準形式があります。これらは、正規形式の簡略化されたバージョンです。

- 標準のSoPフォーム

- 標準のPoSフォーム

論理ゲートについては、後の章で説明します。メインadvantage標準形式の特徴は、論理ゲートに適用される入力の数を最小限に抑えることができることです。場合によっては、必要な論理ゲートの総数が減ることがあります。

標準のSoPフォーム

標準のSoPフォームは Standard Sum of Products形。この形式では、各製品用語にすべてのリテラルを含める必要はありません。したがって、製品条件は最小条件である場合とそうでない場合があります。したがって、標準SoP形式は、正規のSoP形式の簡略化された形式です。

2つのステップで出力変数の標準SoP形式を取得します。

- 出力変数の正規のSoP形式を取得します

- 正規のSoP形式である上記のブール関数を単純化します。

複数の出力変数がある場合は、他の出力変数についても同じ手順に従います。場合によっては、正規のSoP形式を単純化できないことがあります。その場合、正規のSoP形式と標準のSoP形式の両方が同じです。

Example

次のブール関数を標準のSoP形式に変換します。

f = p'qr + pq'r + pqr '+ pqr

指定されたブール関数は、正規のSoP形式です。ここで、標準のSoP形式を取得するために、このブール関数を単純化する必要があります。

Step 1 −を使用する Boolean postulate、x + x = x。つまり、ブール変数 'n'回の論理OR演算は、同じ変数と等しくなります。したがって、最後の項pqrをさらに2回書くことができます。

⇒f= p'qr + pq'r + pqr '+ pqr + pqr + pqr

Step 2 −使用 Distributive law1番目と4番目の用語は、2番目と5番目の用語は、3番目と6番目の用語。

⇒f= qr(p '+ p)+ pr(q' + q)+ pq(r '+ r)

Step 3 −使用 Boolean postulate、x + x '= 1は、各括弧内に存在する用語を単純化するためのものです。

⇒f= qr(1)+ pr(1)+ pq(1)

Step 4 −使用 Boolean postulate、x.1 = xは、上記の3つの項を単純化するためのものです。

⇒f= qr + pr + pq

⇒f= pq + qr + pr

これは単純化されたブール関数です。したがって、standard SoP form 与えられた標準的なSoP形式に対応するのは f = pq + qr + pr

標準のPoSフォーム

標準のPoSフォームは Standard Product of Sums形。この形式では、各合計項にすべてのリテラルが含まれている必要はありません。したがって、合計項は最大項である場合とそうでない場合があります。したがって、標準PoSフォームは、正規PoSフォームの簡略化されたフォームです。

2つのステップで出力変数の標準PoS形式を取得します。

- 正規のPoS形式の出力変数を取得します

- 正規のPoS形式である上記のブール関数を単純化します。

複数の出力変数がある場合は、他の出力変数についても同じ手順に従います。場合によっては、正規のPoSフォームを単純化できないことがあります。その場合、正規のPoS形式と標準のPoS形式の両方が同じです。

Example

次のブール関数を標準のPoS形式に変換します。

f =(p + q + r)。(p + q + r ')。(p + q' + r)。(p '+ q + r)

指定されたブール関数は、正規のPoS形式です。ここで、標準のPoS形式を取得するために、このブール関数を単純化する必要があります。

Step 1 −を使用する Boolean postulate、xx = x。つまり、ブール変数 'n'回の論理AND演算は、同じ変数と等しくなります。したがって、最初の項p + q + rをさらに2回書くことができます。

⇒f=(p + q + r)。(p + q + r)。(p + q + r)。(p + q + r ')。(p + q' + r)。(p '+ q + r)

Step 2 −使用 Distributive law,X +(Y-Z)=(X + Y)(X + Z)1番目と4番目の括弧、2番目及び5番目の括弧、3番目と6番目の括弧。

⇒f=(p + q + rr ')。(p + r + qq')。(q + r + pp ')

Step 3 −使用 Boolean postulate、x.x '= 0は、各括弧内に存在する用語を単純化するためのものです。

⇒f=(p + q + 0)。(p + r + 0)。(q + r + 0)

Step 4 −使用 Boolean postulate、x + 0 = x(各括弧内に存在する用語を簡略化するため)

⇒f=(p + q)。(p + r)。(q + r)

⇒f=(p + q)。(q + r)。(p + r)

これは単純化されたブール関数です。したがって、standard PoS form 与えられた正規のPoSフォームに対応するのは f = (p + q).(q + r).(p + r)。これはdual ブール関数のf = pq + qr + pr。

したがって、標準SoPフォームと標準PoSフォームはどちらも互いにデュアルです。

前の章では、ブール仮説と定理を使用してブール関数を簡略化しました。これは時間のかかるプロセスであり、各ステップの後に簡略化された式を書き直す必要があります。

この困難を克服するために、 Karnaughブール関数を簡単に簡略化する方法を導入しました。この方法は、カルノー図法またはKマップ法として知られています。これはグラフィカルな方法であり、「n」変数の2n個のセルで構成されます。隣接するセルは、シングルビット位置のみが異なります。

2〜5変数のKマップ

K-Map法は、2変数のブール関数を5変数に最小化するのに最適です。ここで、2〜5個の変数のKマップについて1つずつ説明します。

2変数Kマップ

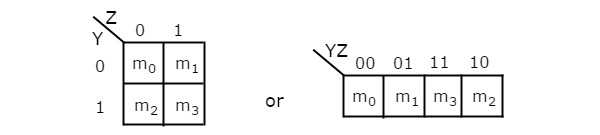

変数の数が2であるため、2つの変数K-mapのセルの数は4です。次の図は2 variable K-Map。

4つの隣接する最小項をグループ化する可能性は1つだけです。

2つの隣接する最小項をグループ化する可能な組み合わせは{(m 0、m 1)、(m 2、m 3)、(m 0、m 2)および(m 1、m 3)}です。

3変数Kマップ

変数の数が3であるため、3つの変数K-mapのセルの数は8です。次の図は3 variable K-Map。

隣接する8つの最小項をグループ化する可能性は1つだけです。

4つの隣接する最小項をグループ化する可能な組み合わせは{(m 0、m 1、m 3、m 2)、(m 4、m 5、m 7、m 6)、(m 0、m 1、m 4、m 5)、(m 1、m 3、m 5、m 7)、(m 3、m 2、m 7、m 6)および(m 2、m 0、m 6、m 4)}。

2つの隣接する最小項をグループ化する可能な組み合わせは、{(m 0、m 1)、(m 1、m 3)、(m 3、m 2)、(m 2、m 0)、(m 4、m 5)です。 、(m 5、m 7)、(m 7、m 6)、(m 6、m 4)、(m 0、m 4)、(m 1、m 5)、(m 3、m 7)および( m 2、m 6)}。

x = 0の場合、3変数Kマップは2変数Kマップになります。

4変数Kマップ

変数の数が4であるため、4つの変数K-mapのセルの数は16です。次の図は4 variable K-Map。

16個の隣接する最小項をグループ化する可能性は1つだけです。

R 1、R 2、R 3、およびR 4が、それぞれ1行目、2行目、3行目、および4行目の最小項を表すとします。同様に、C 1、C 2、C 3、およびC 4は、それぞれ第1列、第2列、第3列、および第4列の最小項を表します。8つの隣接する最小項をグループ化する可能な組み合わせは、{(R 1、R 2)、(R 2、R 3)、(R 3、R 4)、(R 4、R 1)、(C 1、C 2)です。 、(C 2、C 3)、(C 3、C 4)、(C 4、C 1)}。

w = 0の場合、4変数Kマップは3変数Kマップになります。

5変数Kマップ

変数の数が5であるため、5つの変数K-mapのセルの数は32です。次の図は次の図を示しています。 5 variable K-Map。

32個の隣接する最小項をグループ化する可能性は1つだけです。

16個の隣接する最小項をグループ化する2つの可能性があります。すなわち、Mから分用語のグループ0 mまで15及びm 16 mまで31。

v = 0の場合、5変数Kマップは4変数Kマップになります。

上記のすべてのKマップでは、最小用語表記のみを使用しました。同様に、Max用語表記のみを使用できます。

Kマップを使用したブール関数の最小化

ブール関数が「1」である入力の組み合わせを検討すると、ブール関数が得られます。 standard sum of products Kマップを単純化した後のフォーム。

同様に、ブール関数が「0」である入力の組み合わせを検討すると、ブール関数が得られます。 standard product of sums Kマップを単純化した後のフォーム。

これらに従ってください rules for simplifying K-maps 製品の標準的な合計フォームを取得するため。

ブール関数に存在する変数の数に基づいて、それぞれのKマップを選択します。

ブール関数が最小項の合計形式で指定されている場合は、Kマップのそれぞれの最小項セルに配置します。ブール関数が積の合計形式として指定されている場合は、指定された積項が有効であるK-mapのすべての可能なセルにそれらを配置します。

隣接するものの最大数をグループ化する可能性を確認してください。それは2の累乗でなければなりません。最高の2の累乗から始めて、最低の2の累乗まで。最大電力はKマップで考慮される変数の数に等しく、最小電力はゼロです。

各グループは、文字通りまたは1つの製品用語を提供します。それはとして知られていますprime implicant。主な関係者はessential prime implicant、少なくとも単一の「1」が他のグループでカバーされておらず、そのグループのみがカバーされている場合。

すべての主要な含意者と本質的な主要な含意者を書き留めます。簡略化されたブール関数には、すべての必須のプライム含意と、必要なプライム含意のみが含まれます。

Note 1 −入力の組み合わせに対して出力が定義されていない場合、それらの出力値は次のように表されます。 don’t care symbol ‘x’。つまり、「0」または「1」のいずれかと見なすことができます。

Note 2−ドントケア用語も存在する場合は、Kマップのそれぞれのセルにドントケア 'x'を配置します。隣接するものの最大数をグループ化するのに役立つドントケア 'x'のみを考慮してください。そのような場合は、ドントケア値を「1」として扱います。

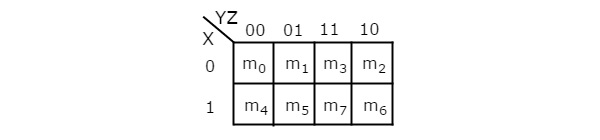

例

私たちにさせて simplify 次のブール関数、 f(W, X, Y, Z)= WX’Y’ + WY + W’YZ’ Kマップを使用します。

指定されたブール関数は、積の合計形式です。W、X、Y、Zの4つの変数があります。したがって、4 variable K-map。ザ・4 variable K-map 与えられた製品用語に対応するものを次の図に示します。

ここでは、K-mapの次のセルに1が配置されています。

行4と列1および2の共通部分に共通するセルは、積項に対応します。 WX’Y’。

行3と4と列3と4の共通部分に共通するセルは、積項に対応します。 WY。

行1と2と列4の共通部分に共通するセルは、積項に対応します。 W’YZ’。

隣接する16個または隣接する8個をグループ化する可能性はありません。4つの隣接するものをグループ化する3つの可能性があります。これらの3つのグループ化の後、グループ化されていないものが1つも残っていません。したがって、隣接する2つのグループをチェックする必要はありません。ザ・4 variable K-map これらの3つで groupings 次の図に示します。

ここでは、3つの主要な関係者WX '、WY&YZ'を取得しました。これらすべての主要な関係者はessential 以下の理由によります。

2つ (m8 & m9)4行目のグループ化は、他のグループ化の対象にはなりません。4行目のグループ化のみがこれら2つの行をカバーします。

シングルワン (m15)正方形のグループ化は、他のグループ化ではカバーされません。正方形のグループだけがそれをカバーします。

2つ (m2 & m6)4番目の列のグループ化は、他のグループ化の対象にはなりません。4番目の列のグループ化のみがこれら2つの列をカバーします。

したがって、 simplified Boolean function です

f = WX’ + WY + YZ’

これらに従ってください rules for simplifying K-maps 合計形式の標準積を取得するため。

ブール関数に存在する変数の数に基づいて、それぞれのKマップを選択します。

ブール関数が最大項形式の積として指定されている場合は、Kマップのそれぞれの最大項セルにゼロを配置します。ブール関数が合計形式の積として指定されている場合は、指定された合計項が有効であるKマップのすべての可能なセルにゼロを配置します。

隣接するゼロの最大数をグループ化する可能性を確認します。それは2の累乗でなければなりません。最高の2の累乗から始めて、最低の2の累乗まで。最大電力はKマップで考慮される変数の数に等しく、最小電力はゼロです。

各グループは、リテラルまたは1つの合計項のいずれかを提供します。それはとして知られていますprime implicant。主な関係者はessential prime implicant、少なくとも単一の「0」が他のグループでカバーされておらず、そのグループのみがカバーされている場合。

すべての主要な含意者と本質的な主要な含意者を書き留めます。簡略化されたブール関数には、すべての必須のプライム含意と、必要なプライム含意のみが含まれます。

Note−ドントケア用語も存在する場合は、Kマップのそれぞれのセルにドントケア 'x'を配置します。隣接するゼロの最大数をグループ化するのに役立つドントケア 'x'のみを考慮してください。そのような場合は、ドントケア値を「0」として扱います。

例

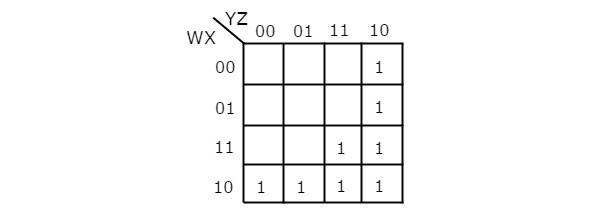

私たちにさせて simplify 次のブール関数、 $f\left ( X,Y,Z \right )=\prod M\left ( 0,1,2,4 \right )$ Kマップを使用します。

指定されたブール関数は、最大項形式の積です。X、Y、Zの3つの変数があります。したがって、3つの変数K-mapが必要です。所与の最大用語はMである0、M 1、M 2およびM 4。3variable K-map 次の図に、指定された最大項に対応するゼロを示します。

8つの隣接するゼロまたは4つの隣接するゼロをグループ化する可能性はありません。2つの隣接するゼロをグループ化する可能性は3つあります。これらの3つのグループ化の後、グループ化されていないものとして残っている単一のゼロはありません。ザ・3 variable K-map これらの3つで groupings 次の図に示します。

ここでは、3つの主要な含意X + Y、Y + Z&Z + Xを取得しました。これらの主要な含意はすべて essential 各グループの1つのゼロは、個々のグループを除いて、他のグループではカバーされないためです。

したがって、 simplified Boolean function です

f = (X + Y).(Y + Z).(Z + X)

このように、K-map法を使用して、最大5変数のブール関数を簡単に簡略化できます。5つを超える変数の場合、Kマップを使用して関数を単純化することは困難です。なぜなら、cells K-mapで取得 doubled 新しい変数を含めることによって。

このため、隣接するもの(最小項)または隣接するゼロ(最大項)のチェックとグループ化は複雑になります。私たちは議論する予定ですTabular method 次の章では、Kマップ法の難しさを克服します。

前の章では、5変数までのブール関数を最小化するための便利な方法であるK-map法について説明しました。ただし、この方法を使用して、5つを超える変数を持つブール関数を単純化することは困難です。

Quine-McClukeyの表形式の方法は、主要な含意の概念に基づく表形式の方法です。私達はことを知っていますprime implicant は積(または合計)項であり、指定されたブール関数の他の積(または合計)項と組み合わせてさらに減らすことはできません。

この表形式の方法は、次のブール単位元を繰り返し使用して、主要な含意を取得するのに役立ちます。

xy + xy '= x(y + y')= x.1 = x

クワイン・マクラスキー表形式法の手順

Quine-McClukey表形式メソッドを使用してブール関数を単純化するには、次の手順に従います。

Step 1 −指定された最小項を ascending orderバイナリ表現に存在するものの数に基づいてグループを作成します。だから、at most ‘n+1’ groups ブール関数に「n」ブール変数がある場合、または最小項に相当するバイナリに「n」ビットがある場合。

Step 2 −に存在する最小項を比較します successive groups。1ビットの位置のみに変化がある場合は、それらの2つの最小項のペアを取ります。この記号「_」を異なるビット位置に配置し、残りのビットをそのままにします。

Step 3 −すべてが得られるまで、新しく形成された用語でステップ2を繰り返します。 prime implicants。

Step 4 −を策定する prime implicant table。これは、行と列のセットで構成されています。主な含意は行ごとに配置でき、最小の用語は列ごとに配置できます。各プライム含意でカバーされている最小項に対応するセルに「1」を配置します。

Step 5−各列を観察して、本質的な主要な関係者を見つけます。最小項が1つの主要な含意者によってのみカバーされている場合、それはessential prime implicant。これらの重要な主要な含意は、単純化されたブール関数の一部になります。

Step 6−各必須プライム含意の行と、そのエッセンシャルプライム含意でカバーされている最小項に対応する列を削除して、プライム含意テーブルを減らします。縮小プライム含意テーブルに対して手順5を繰り返します。指定されたブール関数のすべての最小項が終了したら、このプロセスを停止します。

例

私たちにさせて simplify 次のブール関数、 $f\left ( W,X,Y,Z \right )=\sum m\left ( 2,6,8,9,10,11,14,15 \right )$ Quine-McClukey表形式メソッドを使用します。

与えられたブール関数は sum of min terms形。それは4つの変数W、X、Y、Zを持っています。与えられた最小項は2、6、8、9、10、11、14、15です。これらの最小項の昇順は、同等のバイナリは2、8、6、9、10、11、14、および15です。次の表にこれらを示します。min terms and their equivalent binary 表現。

| グループ名 | 最小条件 | W | バツ | Y | Z |

|---|---|---|---|---|---|

| GA1 | 2 | 0 | 0 | 1 | 0 |

| 8 | 1 | 0 | 0 | 0 | |

| GA2 | 6 | 0 | 1 | 1 | 0 |

| 9 | 1 | 0 | 0 | 1 | |

| 10 | 1 | 0 | 1 | 0 | |

| 11 | 1 | 0 | 1 | 1 | |

| 14 | 1 | 1 | 1 | 0 | |

| GA4 | 15 | 1 | 1 | 1 | 1 |

与えられた最小項は、同等のバイナリに存在するものの数に基づいて4つのグループに配置されます。次の表は、可能なことを示していますmerging of min terms 隣接するグループから。

| グループ名 | 最小条件 | W | バツ | Y | Z |

|---|---|---|---|---|---|

| GB1 | 2,6 | 0 | - | 1 | 0 |

| 2,10 | - | 0 | 1 | 0 | |

| 8,9 | 1 | 0 | 0 | - | |

| 8,10 | 1 | 0 | - | 0 | |

| GB2 | 6,14 | - | 1 | 1 | 0 |

| 9,11 | 1 | 0 | - | 1 | |

| 10,11 | 1 | 0 | 1 | - | |

| 10,14 | 1 | - | 1 | 0 | |

| 11,15 | 1 | - | 1 | 1 | |

| 14,15 | 1 | 1 | 1 | - |

隣接するグループと1ビットの位置だけが異なる最小項がマージされます。その異なるビットは、この記号「-」で表されます。この場合、3つのグループがあり、各グループには2つの最小項の組み合わせが含まれています。次の表は、可能なことを示していますmerging of min term pairs 隣接するグループから。

| グループ名 | 最小条件 | W | バツ | Y | Z |

|---|---|---|---|---|---|

| GB1 | 2,6,10,14 | - | - | 1 | 0 |

| 2,10,6,14 | - | - | 1 | 0 | |

| 8,9,10,11 | 1 | 0 | - | - | |

| 8,10,9,11 | 1 | 0 | - | - | |

| GB2 | 10,11,14,15 | 1 | - | 1 | - |

| 10,14,11,15 | 1 | - | 1 | - |

1ビットの位置のみが異なる最小項ペアの連続するグループがマージされます。その異なるビットは、この記号「-」で表されます。この場合、2つのグループがあり、各グループには4つの最小項の組み合わせが含まれています。ここでは、これらの4分の用語の組み合わせが2行で利用できます。したがって、繰り返される行を削除できます。冗長行を削除した後の縮小テーブルを以下に示します。

| グループ名 | 最小条件 | W | バツ | Y | Z |

|---|---|---|---|---|---|

| GC1 | 2,6,10,14 | - | - | 1 | 0 |

| 8,9,10,11 | 1 | 0 | - | - | |

| GC2 | 10,11,14,15 | 1 | - | 1 | - |

隣接するグループの最小項の組み合わせは、1ビット以上の位置で異なるため、さらにマージすることはできません。上記の表には3つの行があります。したがって、各行は1つの主要な含意を与えます。したがって、prime implicants YZ '、WX'、WYです。

ザ・ prime implicant table 以下に示します。

| 最小条件/プライム含意 | 2 | 6 | 8 | 9 | 10 | 11 | 14 | 15 |

|---|---|---|---|---|---|---|---|---|

| YZ’ | 1 | 1 | 1 | 1 | ||||

| WX’ | 1 | 1 | 1 | 1 | ||||

| WY | 1 | 1 | 1 | 1 |

主な含意は行ごとに配置され、最小の用語は列ごとに配置されます。1は、プライム含意行と対応する最小項列の共通セルに配置されます。

最小項2および6は、1つの主要な関係者によってのみカバーされます YZ’。だから、それはessential prime implicant。これは、簡略化されたブール関数の一部になります。ここで、この主要な含意行と対応する最小項列を削除します。縮小されたプライム含意表を以下に示します。

| 最小条件/プライム含意 | 8 | 9 | 11 | 15 |

|---|---|---|---|---|

| WX’ | 1 | 1 | 1 | |

| WY | 1 | 1 |

最小項8および9は、1つの主要な関係者によってのみカバーされます WX’。だから、それはessential prime implicant。これは、簡略化されたブール関数の一部になります。ここで、この主要な含意行と対応する最小項列を削除します。縮小されたプライム含意表を以下に示します。

| 最小条件/プライム含意 | 15 |

|---|---|

| WY | 1 |

最小項15は、1人の主要な関係者によってのみカバーされます WY。だから、それはessential prime implicant。これは、簡略化されたブール関数の一部になります。

この問題の例では、3つの主要な関係者がいて、3つすべてが不可欠です。したがって、simplified Boolean function です

f(W,X,Y,Z) = YZ’ + WX’ + WY.

デジタル電子回路は、 two logic levelsつまり、ロジックローとロジックハイです。ロジックローに対応する電圧範囲は「0」で表されます。同様に、LogicHighに対応する電圧の範囲は「1」で表されます。

The basic digital electronic circuit that has one or more inputs and single output is known as Logic gate. Hence, the Logic gates are the building blocks of any digital system. We can classify these Logic gates into the following three categories.

- Basic gates

- Universal gates

- Special gates

Now, let us discuss about the Logic gates come under each category one by one.

Basic Gates

In earlier chapters, we learnt that the Boolean functions can be represented either in sum of products form or in product of sums form based on the requirement. So, we can implement these Boolean functions by using basic gates. The basic gates are AND, OR & NOT gates.

AND gate

An AND gate is a digital circuit that has two or more inputs and produces an output, which is the logical AND of all those inputs. It is optional to represent the Logical AND with the symbol ‘.’.

The following table shows the truth table of 2-input AND gate.

| A | B | Y = A.B |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Here A, B are the inputs and Y is the output of two input AND gate. If both inputs are ‘1’, then only the output, Y is ‘1’. For remaining combinations of inputs, the output, Y is ‘0’.

The following figure shows the symbol of an AND gate, which is having two inputs A, B and one output, Y.

This AND gate produces an output (Y), which is the logical AND of two inputs A, B. Similarly, if there are ‘n’ inputs, then the AND gate produces an output, which is the logical AND of all those inputs. That means, the output of AND gate will be ‘1’, when all the inputs are ‘1’.

OR gate

An OR gate is a digital circuit that has two or more inputs and produces an output, which is the logical OR of all those inputs. This logical OR is represented with the symbol ‘+’.

The following table shows the truth table of 2-input OR gate.

| A | B | Y = A + B |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Here A, B are the inputs and Y is the output of two input OR gate. If both inputs are ‘0’, then only the output, Y is ‘0’. For remaining combinations of inputs, the output, Y is ‘1’.

The following figure shows the symbol of an OR gate, which is having two inputs A, B and one output, Y.

This OR gate produces an output (Y), which is the logical OR of two inputs A, B. Similarly, if there are ‘n’ inputs, then the OR gate produces an output, which is the logical OR of all those inputs. That means, the output of an OR gate will be ‘1’, when at least one of those inputs is ‘1’.

NOT gate

A NOT gate is a digital circuit that has single input and single output. The output of NOT gate is the logical inversion of input. Hence, the NOT gate is also called as inverter.

The following table shows the truth table of NOT gate.

| A | Y = A’ |

|---|---|

| 0 | 1 |

| 1 | 0 |

Here A and Y are the input and output of NOT gate respectively. If the input, A is ‘0’, then the output, Y is ‘1’. Similarly, if the input, A is ‘1’, then the output, Y is ‘0’.

The following figure shows the symbol of NOT gate, which is having one input, A and one output, Y.

This NOT gate produces an output (Y), which is the complement of input, A.

Universal gates

NAND & NOR gates are called as universal gates. Because we can implement any Boolean function, which is in sum of products form by using NAND gates alone. Similarly, we can implement any Boolean function, which is in product of sums form by using NOR gates alone.

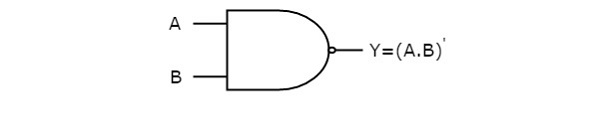

NAND gate

NAND gate is a digital circuit that has two or more inputs and produces an output, which is the inversion of logical AND of all those inputs.

The following table shows the truth table of 2-input NAND gate.

| A | B | Y = (A.B)’ |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Here A, B are the inputs and Y is the output of two input NAND gate. When both inputs are ‘1’, the output, Y is ‘0’. If at least one of the input is zero, then the output, Y is ‘1’. This is just opposite to that of two input AND gate operation.

The following image shows the symbol of NAND gate, which is having two inputs A, B and one output, Y.

NAND gate operation is same as that of AND gate followed by an inverter. That’s why the NAND gate symbol is represented like that.

NOR gate

NOR gate is a digital circuit that has two or more inputs and produces an output, which is the inversion of logical OR of all those inputs.

The following table shows the truth table of 2-input NOR gate

| A | B | Y = (A+B)’ |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

Here A, B are the inputs and Y is the output. If both inputs are ‘0’, then the output, Y is ‘1’. If at least one of the input is ‘1’, then the output, Y is ‘0’. This is just opposite to that of two input OR gate operation.

The following figure shows the symbol of NOR gate, which is having two inputs A, B and one output, Y.

NOR gate operation is same as that of OR gate followed by an inverter. That’s why the NOR gate symbol is represented like that.

Special Gates

Ex-OR & Ex-NOR gates are called as special gates. Because, these two gates are special cases of OR & NOR gates.

Ex-OR gate

The full form of Ex-OR gate is Exclusive-OR gate. Its function is same as that of OR gate except for some cases, when the inputs having even number of ones.

The following table shows the truth table of 2-input Ex-OR gate.

| A | B | Y = A⊕B |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Here A, B are the inputs and Y is the output of two input Ex-OR gate. The truth table of Ex-OR gate is same as that of OR gate for first three rows. The only modification is in the fourth row. That means, the output (Y) is zero instead of one, when both the inputs are one, since the inputs having even number of ones.

Therefore, the output of Ex-OR gate is ‘1’, when only one of the two inputs is ‘1’. And it is zero, when both inputs are same.

Below figure shows the symbol of Ex-OR gate, which is having two inputs A, B and one output, Y.

Ex-OR gate operation is similar to that of OR gate, except for few combination(s) of inputs. That’s why the Ex-OR gate symbol is represented like that. The output of Ex-OR gate is ‘1’, when odd number of ones present at the inputs. Hence, the output of Ex-OR gate is also called as an odd function.

Ex-NOR gate

The full form of Ex-NOR gate is Exclusive-NOR gate. Its function is same as that of NOR gate except for some cases, when the inputs having even number of ones.

The following table shows the truth table of 2-input Ex-NOR gate.

| A | B | Y = A⊙B |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Here A, B are the inputs and Y is the output. The truth table of Ex-NOR gate is same as that of NOR gate for first three rows. The only modification is in the fourth row. That means, the output is one instead of zero, when both the inputs are one.

Therefore, the output of Ex-NOR gate is ‘1’, when both inputs are same. And it is zero, when both the inputs are different.

The following figure shows the symbol of Ex-NOR gate, which is having two inputs A, B and one output, Y.

Ex-NOR gate operation is similar to that of NOR gate, except for few combination(s) of inputs. That’s why the Ex-NOR gate symbol is represented like that. The output of Ex-NOR gate is ‘1’, when even number of ones present at the inputs. Hence, the output of Ex-NOR gate is also called as an even function.

From the above truth tables of Ex-OR & Ex-NOR logic gates, we can easily notice that the Ex-NOR operation is just the logical inversion of Ex-OR operation.

The maximum number of levels that are present between inputs and output is two in two level logic. That means, irrespective of total number of logic gates, the maximum number of Logic gates that are present (cascaded) between any input and output is two in two level logic. Here, the outputs of first level Logic gates are connected as inputs of second level Logic gate(s).

Consider the four Logic gates AND, OR, NAND & NOR. Since, there are 4 Logic gates, we will get 16 possible ways of realizing two level logic. Those are AND-AND, AND-OR, ANDNAND, AND-NOR, OR-AND, OR-OR, OR-NAND, OR-NOR, NAND-AND, NAND-OR, NANDNAND, NAND-NOR, NOR-AND, NOR-OR, NOR-NAND, NOR-NOR.

These two level logic realizations can be classified into the following two categories.

- Degenerative form

- Non-degenerative form

Degenerative Form

If the output of two level logic realization can be obtained by using single Logic gate, then it is called as degenerative form. Obviously, the number of inputs of single Logic gate increases. Due to this, the fan-in of Logic gate increases. This is an advantage of degenerative form.

Only 6 combinations of two level logic realizations out of 16 combinations come under degenerative form. Those are AND-AND, AND-NAND, OR-OR, OR-NOR, NAND-NOR, NORNAND.

In this section, let us discuss some realizations. Assume, A, B, C & D are the inputs and Y is the output in each logic realization.

AND-AND Logic

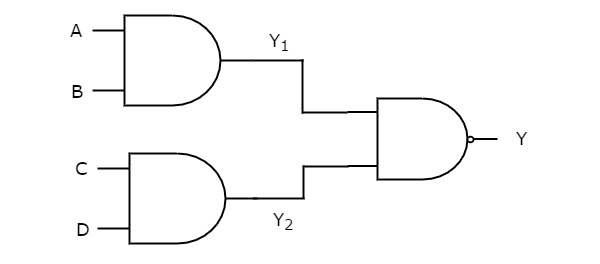

In this logic realization, AND gates are present in both levels. Below figure shows an example for AND-AND logic realization.

We will get the outputs of first level logic gates as $Y_{1}=AB$ and $Y_{2}=CD$

These outputs, $Y_{1}$ and $Y_{2}$ are applied as inputs of AND gate that is present in second level. So, the output of this AND gate is

$$Y=Y_{1}Y_{2}$$

Substitute $Y_{1}$ and $Y_{2}$ values in the above equation.

$$Y=\left ( AB \right )\left ( CD \right )$$

$\Rightarrow Y=ABCD$

Therefore, the output of this AND-AND logic realization is ABCD. This Boolean function can be implemented by using a 4 input AND gate. Hence, it is degenerative form.

AND-NAND Logic

In this logic realization, AND gates are present in first level and NAND gate(s) are present in second level. The following figure shows an example for AND-NAND logic realization.

以前は、第1レベルの論理ゲートの出力を次のように取得しました。 $Y_{1} = AB$ そして $Y_{2} = CD$

これらの出力、$Y_{1}$ そして $Y_{2}$2番目のレベルに存在するNANDゲートの入力として適用されます。したがって、このNANDゲートの出力は次のようになります。

$$Y={\left ( Y_{1}Y_{2} \right )}'$$

代替 $Y_{1}$ そして $Y_{2}$ 上記の式の値。

$$Y={\left ( \left ( AB \right ) \left ( CD \right )\right )}'$$

$\Rightarrow Y={\left ( ABCD \right )}'$

したがって、このAND-NANDロジック実現の出力は次のようになります。 ${\left ( ABCD \right )}'$。このブール関数は、4入力NANDゲートを使用して実装できます。したがって、それはdegenerative form。

OR-ORロジック

この論理の実現では、ORゲートは両方のレベルに存在します。次の図は、OR-OR logic 実現。

第1レベルの論理ゲートの出力を次のように取得します。 $Y_{1}=A+B$ そして $Y_{2}=C+D$。

これらの出力、 $Y_{1}$ そして $Y_{2}$2番目のレベルに存在するORゲートの入力として適用されます。したがって、このORゲートの出力は次のようになります。

$$Y=Y_{1}+Y_{2}$$

代替 $Y_{1}$ そして $Y_{2}$ 上記の式の値。

$$Y=\left ( A+B \right )+\left ( C+D \right )$$

$\Rightarrow Y=A+B+C+D$

したがって、このOR-ORロジック実現の出力は次のようになります。 A+B+C+D。このブール関数は、4入力ORゲートを使用して実装できます。したがって、それはdegenerative form。

同様に、残りの実現がこのカテゴリに属しているかどうかを確認できます。

非変性型

単一の論理ゲートを使用して2レベルの論理実現の出力を取得できない場合、それは次のように呼び出されます。 non-degenerative form。

残り 10 combinations2つのレベルの論理実現のうち、非縮退形式になります。それらは、AND-OR、AND-NOR、OR-AND、OR-NAND、NAND-AND、NANDOR、NAND-NAND、NOR-AND、NOR-OR、NOR-NORです。

それでは、いくつかの実現について説明しましょう。各論理実現において、A、B、C、およびDが入力であり、Yが出力であると想定します。

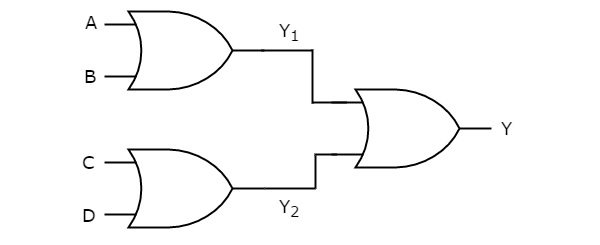

AND-ORロジック

この論理実現では、ANDゲートは第1レベルに存在し、ORゲートは第2レベルに存在します。下の図は、AND-OR logic 実現。

以前は、第1レベルの論理ゲートの出力を次のように取得しました。 $Y_{1} = AB$ そして $Y_{2} = CD$。

これらの出力Y1とY2は、2番目のレベルに存在するORゲートの入力として適用されます。したがって、このORゲートの出力は次のようになります。

$$Y=Y_{1}+Y_{2}$$

代替 $Y_{1}$ そして $Y_{2}$ 上記の式の値

$$Y=AB+CD$$

したがって、このAND-OR論理実現の出力は次のようになります。 AB+CD。このブール関数はSum of Products形。単一の論理ゲートを使用して実装することはできないため、このAND-OR論理の実現はnon-degenerative form。

AND-NORロジック

この論理実現では、ANDゲートは第1レベルに存在し、NORゲートは第2レベルに存在します。次の図は、AND-NOR logic 実現。

第1レベルの論理ゲートの出力は次のようにわかっています。 $Y_{1} = AB$ そして $Y_{2} = CD$

これらの出力Y1とY2は、2番目のレベルに存在するNORゲートの入力として適用されます。したがって、このNORゲートの出力は次のようになります。

$$Y={\left ( Y_{1}+Y_{2} \right )}'$$

代替 $Y_{1}$ そして $Y_{2}$ 上記の式の値。

$$Y={\left ( AB+CD \right )}'$$

したがって、このAND-NORロジック実現の出力は次のようになります。 ${\left ( AB+CD \right )}'$。このブール関数はAND-OR-Invert形。単一の論理ゲートを使用して実装することはできないため、このAND-NOR論理の実現はnon-degenerative form

OR-ANDロジック

この論理実現では、ORゲートは第1レベルに存在し、ANDゲートは第2レベルに存在します。次の図は、OR-AND logic 実現。

以前は、第1レベルの論理ゲートの出力を次のように取得しました。 $Y_{1}=A+B$ そして $Y_{2}=C+D$。

これらの出力、 $Y_{1}$ そして $Y_{2}$2番目のレベルに存在するANDゲートの入力として適用されます。したがって、このANDゲートの出力は次のようになります。

$$Y=Y_{1}Y_{2}$$

代替 $Y_{1}$ そして $Y_{2}$ 上記の式の値。

$$Y = \left ( A+B \right )\left ( C+D \right )$$

したがって、このOR-AND論理実現の出力は次のようになります。 (A + B) (C + D)。このブール関数はProduct of Sums形。単一の論理ゲートを使用して実装することはできないため、このOR-AND論理の実現はnon-degenerative form。

同様に、残りの実現がこのカテゴリに属しているかどうかを確認できます。

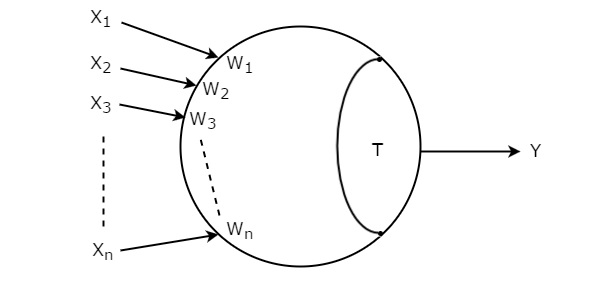

Combinational circuits論理ゲートで構成されています。これらの回路は2進値で動作します。組み合わせ回路の出力は、現在の入力の組み合わせに依存します。次の図は、block diagram 組み合わせ回路の。

この組み合わせ回路には、「n」個の入力変数と「m」個の出力があります。入力変数の各組み合わせは、出力に影響を与えます。

組み合わせ回路の設計手順

与えられた仕様から必要な数の入力変数と出力を見つけます。

を策定する Truth table。'n'個の入力変数がある場合、2n個の可能な組み合わせがあります。入力の組み合わせごとに、出力値を見つけます。

を見つける Boolean expressions出力ごとに。必要に応じて、これらの式を簡略化します。

を使用して、各出力に対応する上記のブール式を実装します。 Logic gates。

コードコンバーター

codeという名前の章でさまざまなコードについて説明しました。あるコードを別のコードに変換するコンバーターは、次のように呼ばれます。code converters。これらのコードコンバータは基本的に論理ゲートで構成されています。

例

バイナリコードからグレイコードへのコンバーター

4ビットのバイナリコードWXYZを同等のグレイコードABCDに変換するコンバーターを実装しましょう。

次の表は、 Truth table 4ビットのバイナリコードからグレイコードへのコンバーター。

| バイナリコードWXYZ | WXYZグレイコードABCD |

|---|---|

| 0000 | 0000 |

| 0001 | 0001 |

| 0010 | 0011 |

| 0011 | 0010 |

| 0100 | 0110 |

| 0101 | 0111 |

| 0110 | 0101 |

| 0111 | 0100 |

| 1000 | 1100 |

| 1001 | 1101 |

| 1010 | 1111 |

| 1011 | 1110 |

| 1100 | 1010 |

| 1101 | 1011 |

| 1110 | 1001 |

| 1111 | 1000 |

真理値表から、 Boolean functions 以下のようにグレイコードの各出力ビットに対して。

$$A=\sum m\left (8,9,10,11,12,13,14,15 \right )$$

$$B=\sum m\left (4,5,6,7,8,9,10,11 \right )$$

$$C=\sum m\left (2,3,4,5,10,11,12,13 \right )$$

$$D=\sum m\left (1,2,5,6,9,10,13,14 \right )$$

4つの変数K-Mapを使用して、上記の関数を単純化してみましょう。

次の図は、 4 variable K-Map 簡素化するため Boolean function, A。

隣接する8つをグループ化することで、 $A=W$。

次の図は、 4 variable K-Map 簡素化するため Boolean function, B。

4つの隣接するグループの2つのグループがあります。グループ化した後、Bを次のように取得します

$$B={W}'X+W{X}'=W\oplus X $$

同様に、単純化した後、CとDに対して次のブール関数を取得します。

$$C={X}'Y+X{Y}'=X \oplus Y$$

$$D={Y}'Z+Y{Z}'=Y \oplus Z$$

次の図は、 circuit diagram 4ビットバイナリコードからグレイコードへのコンバーター。

出力は現在の入力のみに依存するため、この4ビットのバイナリコードからグレイコードへのコンバータは組み合わせ回路です。同様に、他のコードコンバーターを実装できます。

パリティビットジェネレータ

生成されるパリティビットのタイプに基づいて、2つのタイプのパリティビットジェネレータがあります。 Even parity generator偶数パリティビットを生成します。同様に、odd parity generator 奇数のパリティビットを生成します。

パリティジェネレータでさえ

ここで、3ビットのバイナリ入力WXY用の偶数パリティジェネレータを実装しましょう。偶数パリティビットPを生成します。入力に奇数の1が存在する場合、偶数パリティビットPは「1」であり、結果のワードに偶数の1が含まれるようにする必要があります。入力の他の組み合わせの場合、パリティビットであっても、Pは「0」である必要があります。次の表は、Truth table 偶数パリティジェネレータの。

| バイナリ入力WXY | パリティビットPでも |

|---|---|

| 000 | 0 |

| 001 | 1 |

| 010 | 1 |

| 011 | 0 |

| 100 | 1 |

| 101 | 0 |

| 110 | 0 |

| 111 | 1 |

上記の真理値表から、次のように書くことができます。 Boolean function 偶数パリティビットの場合

$$P={W}'{X}'Y+{W}'X{Y}'+W{X}'{Y}'+WXY$$

$\Rightarrow P={W}'\left ( {X}'Y+X{Y}' \right )+W\left ({X}'{Y}'+XY \right )$

$\Rightarrow P={W}'\left ( X \oplus Y \right )+W{\left (X \oplus Y \right )}'=W \oplus X \oplus Y$

次の図は、 circuit diagram 偶数パリティジェネレータの。

この回路は2つで構成されています Exclusive-OR gatesそれぞれ2つの入力があります。2つの入力WとXを持ち、出力W⊕Xを生成する最初の排他的論理和ゲート。この出力は、2番目の排他的論理和ゲートの1つの入力として与えられます。この2番目の排他的論理和ゲートのもう1つの入力はYであり、W⊕X⊕Yの出力を生成します。

奇数パリティジェネレータ

入力に偶数の1が存在する場合、奇数のパリティビットPは「1」である必要があります。これにより、結果のワードに奇数の1が含まれます。入力のその他の組み合わせ、奇数パリティビットの場合、Pは「0」である必要があります。

奇数パリティジェネレータを実装するには、偶数パリティジェネレータと同じ手順に従います。ザ・circuit diagram 奇数パリティジェネレータの例を次の図に示します。

上記の回路図は、第1レベルのEx-ORゲートと第2レベルのEx-NORゲートで構成されています。奇数パリティは偶数パリティとは正反対なので、偶数パリティジェネレータの出力にインバータを配置できます。その場合、第1レベルと第2レベルには各レベルにExORゲートが含まれ、第3レベルにはインバーターが含まれます。

パリティチェッカー

チェックする必要のあるパリティのタイプに基づいて、2つのタイプのパリティチェッカーがあります。 Even parity checker送信されたデータのエラーをチェックします。これには、偶数パリティとともにメッセージビットが含まれます。同様に、odd parity checker 奇数パリティとともにメッセージビットを含む送信データのエラーをチェックします。

パリティチェッカーでも

ここで、偶数パリティチェッカー回路を実装しましょう。3ビットのバイナリ入力を想定すると、WXYは偶数パリティビットPとともに送信されます。したがって、結果のワード(データ)には4ビットが含まれ、偶数パリティチェッカーの入力として受信されます。

それは生成します even parity check bit, E。受信データに偶数の1が含まれている場合、このビットはゼロになります。つまり、受信したデータにエラーはありません。受信データに奇数の1が含まれている場合、この偶数パリティチェックビットは1になります。つまり、受信したデータにエラーがあります。

次の表は、 Truth table 偶数パリティチェッカーの。

| 4ビット受信データWXYP | パリティチェックビットEでも |

|---|---|

| 0000 | 0 |

| 0001 | 1 |

| 0010 | 1 |

| 0011 | 0 |

| 0100 | 1 |

| 0101 | 0 |

| 0110 | 0 |

| 0111 | 1 |

| 1000 | 1 |

| 1001 | 0 |

| 1010 | 0 |

| 1011 | 1 |

| 1100 | 0 |

| 1101 | 1 |

| 1110 | 1 |

| 1111 | 0 |

上記の真理値表から、受信データに奇数の1が存在する場合、偶数パリティチェックビット値が「1」であることがわかります。つまり、偶数パリティチェックビットのブール関数はodd function。排他的論理和関数はこの条件を満たす。したがって、直接書くことができますBoolean function 偶数パリティチェックビットの

$$E=W \oplus X \oplus Y \oplus P$$

次の図は、 circuit diagram 偶数パリティチェッカーの。

この回路は3つで構成されています Exclusive-OR gatesそれぞれ2つの入力があります。第1レベルのゲートは、$W \oplus X$ & $Y \oplus P$。2番目のレベルにある排他的論理和ゲートは、次の出力を生成します。$W \oplus X \oplus Y \oplus P$

奇数パリティチェッカー

3ビットのバイナリ入力を想定すると、WXYは奇数パリティビットPとともに送信されます。したがって、結果のワード(データ)には4ビットが含まれ、奇数パリティチェッカーの入力として受信されます。

それは生成します odd parity check bit, E。受信データに奇数の1が含まれている場合、このビットはゼロになります。つまり、受信したデータにエラーはありません。受信データに偶数の1が含まれている場合、この奇数パリティチェックビットは1になります。つまり、受信したデータにエラーがあります。

奇数パリティチェッカーを実装するには、偶数パリティチェッカーと同じ手順に従います。ザ・circuit diagram 奇数パリティチェッカーの例を次の図に示します。

上記の回路図は、第1レベルのEx-ORゲートと第2レベルのEx-NORゲートで構成されています。奇数パリティは偶数パリティとは正反対なので、偶数パリティチェッカーの出力にインバータを配置できます。その場合、第1、第2、第3レベルには、それぞれ2つのEx-ORゲート、1つのEx-ORゲート、1つのインバーターが含まれます。

バイナリ加算器

最も基本的な算術演算は加算です。2つの2進数の加算を実行する回路は、Binary adder。まず、2ビットの加算を実行する加算器を実装しましょう。

半加算器

半加算器は、2つの2進数AとBの加算を実行する組み合わせ回路です。 single bit。2つの出力合計SとキャリーCを生成します。

ザ・ Truth table 半加算器の概要を以下に示します。

| 入力 | 出力 | ||

|---|---|---|---|

| A | B | C | S |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

2ビットの加算を行うと、結果の合計は10進数で0から2の範囲の値を持つことができます。10進数の0と1は、2進数の1ビットで表すことができます。ただし、10進数の2を2進数の1ビットで表すことはできません。したがって、バイナリで表すには2ビットが必要です。

合計すると、Sは最下位ビットであり、キャリー、Cは結果の合計の最上位ビットです。入力の最初の3つの組み合わせ、キャリーの場合、Cはゼロであり、Sの値はゼロまたは1に基づいて1になります。number of ones入力に存在します。ただし、入力の最後の組み合わせであるキャリーの場合、結果の合計は2であるため、Cは1で合計、Sはゼロです。

真理値表から、直接書くことができます Boolean functions 各出力に対して

$$S=A \oplus B$$

$C=AB$

上記の機能は、2入力Ex-ORゲートと2入力ANDゲートで実装できます。ザ・circuit diagram 次の図に半加算器のを示します。

上記の回路では、2入力Ex-ORゲートと2入力ANDゲートがそれぞれ合計SとキャリーCを生成します。したがって、半加算器は2ビットの加算を実行します。

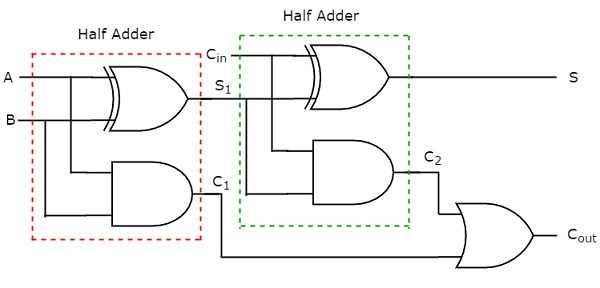

全加算器

全加算器は、を実行する組み合わせ回路です。 addition of three bitsA、B及びCにおける。ここで、AとBは2つの並列有効ビットであり、Cinは前のステージから生成されたキャリービットです。この全加算器は、2つの出力の和、S&キャリー、C生成アウト半加算器と同様です。

ザ・ Truth table 全加算器の概要を以下に示します。

| 入力 | 出力 | |||

|---|---|---|---|---|

| A | B | Cin | Cout | S |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

3ビットの加算を行うと、結果の合計は10進数で0から3の範囲の値を持つことができます。10進数の0と1は、2進数の1ビットで表すことができます。ただし、10進数の2と3を2進数の1ビットで表すことはできません。したがって、これらの2桁の10進数を2進数で表すには2ビットが必要です。

Sは最下位ビットとキャリーでみよう、合計は、Cのうちは、加算結果の最上位ビットです。真理値表の入力のすべての組み合わせの出力の値を入力するのは簡単です。数えるだけnumber of ones入力に存在し、出力に同等の2進数を書き込みます。C inがゼロに等しい場合、全加算器の真理値表は半加算器の真理値表と同じです。

以下を取得します Boolean functions 簡略化後の出力ごとに。

$$S=A \oplus B \oplus C_{in}$$

$c_{out} = AB + \left ( A \oplus B \right )c_{in}$

入力に奇数の1が存在する場合、合計Sは1に等しくなります。Ex-ORゲートが出力を生成することはわかっていますが、これは奇妙な関数です。したがって、合計Sを生成するために2つの2入力Ex-ORゲートまたは1つの3入力Ex-ORゲートのいずれかを使用できます。2つの2入力ANDゲートと1つのORゲートを使用してキャリーC出力を実装できます。ザ・circuit diagram 次の図に全加算器のを示します。

この加算器は次のように呼ばれます Full adder1つの全加算器を実装するには、2つの半加算器と1つのORゲートが必要になるためです。C inがゼロの場合、全加算器は半加算器になります。上記の回路図または全加算器の出力のブール関数から簡単に確認できます。

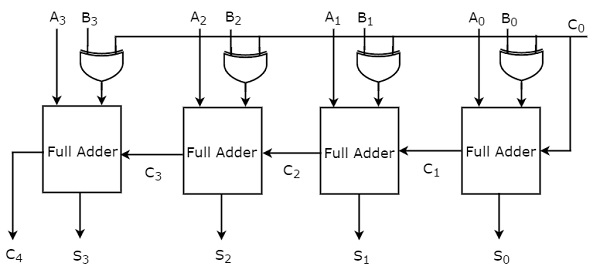

4ビットバイナリ加算器

4ビットバイナリ加算器は addition of two 4-bit numbers。4ビットの2進数、$A=A_{3}A_{2}A_{1}A_{0}$ そして $B= B_{3}B_{2}B_{1}B_{0}$。次の2つの方法のいずれかで4ビットバイナリ加算器を実装できます。

2つの最下位ビットの加算を行うには1つの半加算器を使用し、3つの上位ビットの加算を行うには3つの全加算器を使用します。

均一性のために4つの全加算器を使用します。初期キャリC、ためにはゼロであり、最下位ビットを付加するために使用される全加算器は、半加算器となります。

とりあえず、2番目のアプローチを検討しました。ザ・block diagram 次の図に、4ビットバイナリ加算器の概要を示します。

ここでは、4つの全加算器がカスケード接続されています。各全加算器は、2つの並列入力AおよびBのそれぞれのビットを取得しています。1つの全加算器のキャリー出力は、後続の高次全加算器のキャリー入力になります。この4ビットの2進加算器は、最大5ビットの合計を生成します。したがって、最終段階から実行します。全加算器がMSBになります。

このようにして、必要な数の全加算器をカスケード接続するだけで、高次のバイナリ加算器を実装できます。このバイナリ加算器は、ripple carry (binary) adder キャリーが1つのステージから次のステージに伝播(波紋)するためです。

バイナリ減算器

2つの2進数の減算を実行する回路は、 Binary subtractor。次の2つの方法でバイナリ減算器を実装できます。

- カスケードフルサブトラクタ

- 2の補数法

最初の方法では、「n」フル減算器をカスケード接続することにより、nビットのバイナリ減算器を取得します。したがって、最初に、半加算器と全加算器と同様に、半減算器と全減算器を実装できます。次に、「n」フル減算器をカスケードすることにより、nビットのバイナリ減算器を実装できます。したがって、2つの2進数の2進数の加算と減算のための2つの別々の回路があります。

2番目の方法では、2番目の入力でいくつかの変更を行うだけで、同じ2進加算器を使用して2つの2進数を減算できます。したがって、内部的に2進加算演算が実行されますが、出力は結果の減算です。

2つの2進数AとBの減算は、次のように記述できることがわかっています。

$$A-B = A+\left ( {2}'s \: compliment \: of \: B \right )$$

$\Rightarrow A-B = A+\left ( {1}'s \: compliment \: of \: B \right )+1$

4ビットバイナリ減算器

4ビットのバイナリ減算器は、 subtraction of two 4-bit numbers。4ビットの2進数、$A=A_{3}A_{2}A_{1}A_{0}$ そして $B= B_{3}B_{2}B_{1}B_{0}$。内部的には、4ビットのバイナリ減算器の動作は4ビットのバイナリ加算器の動作と似ています。2進数Aの通常ビット、2進数Bの補完ビット、および初期キャリー(借用)、C inが4ビットの2進数加算器に適用されると、4ビットの2進数減算器になります。ザ・block diagram 次の図に、4ビットのバイナリ減算器を示します。

この4ビットのバイナリ減算器は、最大5ビットの出力を生成します。2進数Aが2進数Bより大きい場合、出力のMSBはゼロであり、残りのビットはABの大きさを保持します。2進数Aが2進数Bより小さい場合、出力のMSBは1です。したがって、ABの大きさを取得するには、出力の2の補数を取ります。

このようにして、必要な数の全加算器を必要な変更を加えてカスケードするだけで、高次のバイナリ減算器を実装できます。

バイナリ加算器/減算器

2つの2進数の加算または減算をいつでも実行するために使用できる回路は、次のように知られています。 Binary Adder / subtractor。バイナリ加算器とバイナリ減算器の両方に、カスケード接続された全加算器のセットが含まれています。2進数Aの入力ビットは、2進加算器と2進減算器の両方に直接適用されます。

バイナリ加算器とバイナリ減算器に存在する全加算器の入力には2つの違いがあります。

2進数Bの入力ビットは、2進数加算器の全加算器に直接適用されますが、2進数Bの補完ビットは、2進数減算器の全加算器に適用されます。

初期キャリーC0 = 0は4ビット2進加算器で適用されますが、初期キャリー(借用)C 0 = 1は4ビット2進減算器で適用されます。

私たちはそれを知っています 2-input Ex-OR gate他の入力がゼロの場合の最初の入力と同じ出力を生成します。同様に、他の入力が1つの場合、最初の入力を補完する出力を生成します。

したがって、2進数Bの入力ビットを2入力Ex-ORゲートに適用できます。これらすべてのEx-ORゲートへの他の入力はC0です。したがって、C 0の値に基づいて、Ex-ORゲートは2進数Bの通常ビットまたは補完ビットのいずれかを生成します。

4ビットバイナリ加算器/減算器

4ビットの2進加算器/減算器は、最初のキャリーまたはボローの値0に基づいて、2つの4ビット数の加算または減算を生成します。4ビットの2進数、$A=A_{3}A_{2}A_{1}A_{0}$ そして $B= B_{3}B_{2}B_{1}B_{0}$。4ビットの2進加算器/減算器の動作は、4ビットの2進加算器および4ビットの2進減算器の操作と同様です。

2進数AおよびBの通常ビットと初期キャリーまたはボローC0を外部から4ビット2進加算器に適用します。ザ・block diagram 4ビットの2進加算器/減算器の概要を次の図に示します。

初期キャリー0がゼロの場合、各全加算器は2進数AおよびBの通常のビットを取得します。したがって、4ビットの2進加算器/減算器は出力を生成します。addition of two binary numbers A&B。

最初の借用、0が1の場合、各全加算器は2進数Aの通常ビットと2進数Bの補完ビットを取得します。したがって、4ビットの2進加算器/減算器は出力を生成します。subtraction of two binary numbers A&B。

したがって、追加のEx-ORゲートを使用すると、2つの2進数の加算と減算の両方に同じ回路を使用できます。

Decoderは、「n」個の入力ラインと最大2n個の出力ラインを持つ組み合わせ回路です。デコーダーが有効になっている場合、これらの出力の1つは、存在する入力の組み合わせに基づいてアクティブHighになります。これは、デコーダーが特定のコードを検出することを意味します。デコーダーの出力は、min terms 有効な場合は、「n」個の入力変数(行)。

2〜4デコーダー

ましょうデコーダは、2つの入力を有する2〜4 A 1&A 0 4つの出力Y 3、Y 2、Y 1およびY 0。ザ・block diagram 次の図に、2〜4個のデコーダーを示します。

これらの4つの出力の1つは、有効にすると入力の組み合わせごとに「1」になり、Eは「1」になります。ザ・Truth table 2〜4個のデコーダーを以下に示します。

| 有効にする | 入力 | 出力 | ||||

|---|---|---|---|---|---|---|

| E | A1 | A0 | Y3 | Y2 | Y1 | Y0 |

| 0 | バツ | バツ | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 | 0 | 0 |

真理値表から、 Boolean functions 各出力に対して

$$Y_{3}=E.A_{1}.A_{0}$$

$$ Y_{2}=E.A_{1}.{A_{0}}'$$

$$ Y_{1}=E.{A_{1}}'.A_{0}$$

$$ Y_{0}=E.{A_{1}}'.{A_{0}}'$$

各出力には1つの積項があります。したがって、合計4つの製品用語があります。それぞれ3つの入力と2つのインバーターを持つ4つのANDゲートを使用することにより、これらの4つの積項を実装できます。ザ・circuit diagram 次の図に、2〜4個のデコーダーを示します。

したがって、2〜4デコーダーの出力は min terms二つの入力変数Aを1&A 0、有効にすると、Eは1に等しいです。イネーブルの場合、Eはゼロになり、デコーダーのすべての出力はゼロに等しくなります。

同様に、3〜8デコーダーは3つの入力変数A 2、A 1&A 0の8分の項を生成し、4〜16デコーダーは4つの入力変数A 3、A 2、A 1&A0の16分の項を生成します。

高次デコーダーの実装

ここで、低次デコーダーを使用して、次の2つの高次デコーダーを実装しましょう。

- 3〜8デコーダー

- 4〜16デコーダー

3〜8デコーダー

このセクションでは、実装しましょう 3 to 8 decoder using 2 to 4 decoders。我々が知っているデコーダは、2つの入力を有する2〜4、A 1およびA 0 4つの出力、Y 3 Yに0。3 A 8、デコーダは、3つの入力を有し、一方2、A 1およびA 0と8つの出力、Y 7 Yに0。

次の式を使用して、高次デコーダを実装するために必要な低次デコーダの数を見つけることができます。

$$Required \: number \: of \: lower \: order \: decoders=\frac{m_{2}}{m_{1}}$$

どこ、

$m_{1}$ は低次デコーダの出力数です。

$m_{2}$ 高次デコーダーの出力数です。

ここに、 $m_{1}$ = 4および $m_{2}$ = 8.代入すると、上記の式のこれら2つの値になります。

$$Required \: number \: of \: 2 \: to \: 4 \: decoders=\frac{8}{4}=2$$

したがって、1つの3〜8デコーダーを実装するには、2つの2〜4デコーダーが必要です。ザ・block diagram 次の図に、2〜4個のデコーダーを使用した3〜8個のデコーダーの例を示します。

パラレル入力A 1およびA 0は、それぞれ2〜4のデコーダに適用されます。入力Aの補数2はY、出力を取得するために、4デコーダ2下のE可能に接続されている3 Yに0。これらはlower four min terms。入力、A 2は直接、Y出力を得るために、上位2デコーダ4へのE可能に接続されている7をYに4。これらはhigher four min terms。

4〜16デコーダー

このセクションでは、実装しましょう 4 to 16 decoder using 3 to 8 decoders。我々が知っているデコーダは三つの入力Aは3〜8 2、A 1およびA 0と8つの出力、Y 7 Yに0。一方、4デコーダ16には、4つの入力を有する3、A 2、A 1およびA 0と16の出力、Y 15 Yに0

必要な低次デコーダーの数を見つけるための次の式がわかっています。

$$Required \: number \: of \: lower \: order \: decoders=\frac{m_{2}}{m_{1}}$$

代替、 $m_{1}$ = 8および $m_{2}$ =上記の式では16。

$$Required \: number \: of \: 3 \: to \: 8 decoders=\frac{16}{8}=2$$

したがって、1つの4〜16デコーダーを実装するには、2つの3〜8デコーダーが必要です。ザ・block diagram 次の図に、3〜8個のデコーダーを使用した4〜16個のデコーダーの例を示します。

A入力パラレル2は、A 1およびA 0は、それぞれ3~8デコーダに適用されます。入力の補数は、A3は、Y出力を得るために、より低い3~8デコーダのE可能に接続されている7をYに0。これらはlower eight min terms。入力、A 3は、直接、Y出力を得るために、上位3デコーダ8へのE可能に接続されている15をYに8。これらはhigher eight min terms。

アン Encoderデコーダの逆動作を行う組み合わせ回路です。最大2n個の入力ラインと「n」個の出力ラインがあります。これは、アクティブなHighである入力と同等のバイナリコードを生成します。したがって、エンコーダは2n個の入力ラインを「n」ビットでエンコードします。エンコーダでイネーブル信号を表すことはオプションです。

4対2エンコーダ

ましょ4 Y 2のエンコーダは、4つの入力を有する3、Y 2、Y 1およびY 0と2つの出力A 1&A 0。ザ・block diagram 次の図に、4〜2個のエンコーダを示します。

いつでも、出力でそれぞれのバイナリコードを取得するために、これら4つの入力のうち1つだけを「1」にすることができます。ザ・Truth table 4対2のエンコーダーを以下に示します。

| 入力 | 出力 | ||||

|---|---|---|---|---|---|

| Y3 | Y2 | Y1 | Y0 | A1 | A0 |

| 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 | 1 |

真理値表から、 Boolean functions 各出力に対して

$$A_{1}=Y_{3}+Y_{2}$$

$$A_{0}=Y_{3}+Y_{1}$$

2つの入力ORゲートを使用して、上記の2つのブール関数を実装できます。ザ・circuit diagram 次の図に、4〜2個のエンコーダを示します。

上記の回路図には、2つのORゲートが含まれています。これらのORゲートは、4つの入力を2ビットでエンコードします

8進数から2進数のエンコーダ

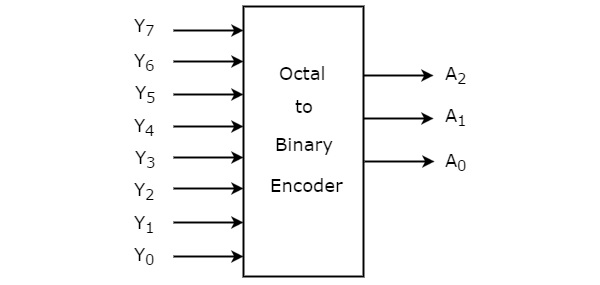

バイナリエンコーダにオクタルは8つの入力、Y有する7をYに0と3つの出力A 2、A 1&A 0。オクタルからバイナリへのエンコーダは、8から3のエンコーダに他なりません。ザ・block diagram 次の図に、8進数から2進数へのエンコーダの変換を示します。

いつでも、それぞれのバイナリコードを取得するために、これらの8つの入力のうち1つだけを「1」にすることができます。ザ・Truth table 8進数から2進数へのエンコーダの比較を以下に示します。

| 入力 | 出力 | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| Y7 | Y6 | Y5 | Y4 | Y3 | Y2 | Y1 | Y0 | A2 | A1 | A0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 |

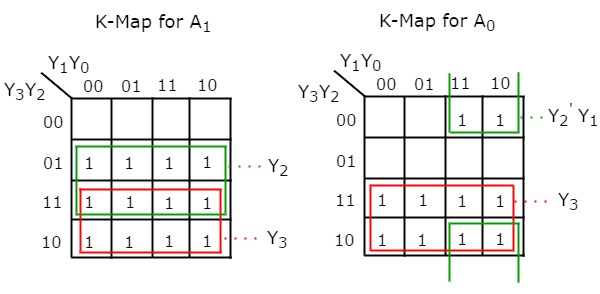

真理値表から、 Boolean functions 各出力に対して

$$A_{2}=Y_{7}+Y_{6}+Y_{5}+Y_{4}$$

$$A_{1}=Y_{7}+Y_{6}+Y_{3}+Y_{2}$$

$$A_{0}=Y_{7}+Y_{5}+Y_{3}+Y_{1}$$

4つの入力ORゲートを使用して、上記のブール関数を実装できます。ザ・circuit diagram 次の図に、8進数から2進数へのエンコーダの変換を示します。

上記の回路図には、3つの4入力ORゲートが含まれています。これらのORゲートは、8つの入力を3ビットでエンコードします。

エンコーダの欠点

通常のエンコーダの欠点は次のとおりです。

エンコーダのすべての出力がゼロに等しい場合、あいまいさがあります。なぜなら、最下位の入力のみが1の場合、またはすべての入力が0の場合、入力に対応するコードである可能性があるためです。

複数の入力がアクティブHighの場合、エンコーダーは出力を生成しますが、これは正しいコードではない可能性があります。にとってexample、Y両方の場合3およびY 6が「1」であることは、次に符号化器は、出力で111を生成します。これは、Yに対応するも同等のコードである3が「1」にもYに対応する同等のコードであり、6が「1」です、。

したがって、これらの問題を克服するには、エンコーダの各入力に優先順位を割り当てる必要があります。次に、エンコーダーの出力は、優先度の高いアクティブなHigh入力に対応する(バイナリ)コードになります。このエンコーダーはpriority encoder。

プライオリティエンコーダ

4〜2プライオリティエンコーダには、4つの入力Y 3、Y 2、Y 1&Y 0、および2つの出力A 1&A0があります。ここで、入力は、Y 3は、入力に対し、最も高い優先度を有し、Y 0は最も低い優先度を有しています。この場合、複数の入力が同時に「1」であっても、出力は入力に対応する(バイナリ)コードになります。higher priority。

もう1つ検討しました output, V 出力で利用可能なコードが有効かどうかを知るために。

エンコーダーの少なくとも1つの入力が「1」の場合、出力で使用可能なコードは有効なコードです。この場合、出力Vは1に等しくなります。

エンコーダのすべての入力が「0」の場合、出力で使用可能なコードは有効なコードではありません。この場合、出力Vは0に等しくなります。

ザ・ Truth table 4〜2のプライオリティエンコーダの例を以下に示します。

| 入力 | 出力 | |||||

|---|---|---|---|---|---|---|

| Y3 | Y2 | Y1 | Y0 | A1 | A0 | V |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 0 | 1 | バツ | 0 | 1 | 1 |

| 0 | 1 | バツ | バツ | 1 | 0 | 1 |

| 1 | バツ | バツ | バツ | 1 | 1 | 1 |

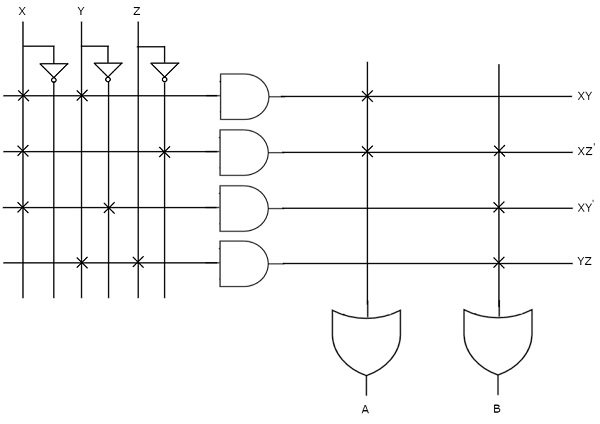

使用する 4 variable K-maps 各出力の簡略化された式を取得するため。

簡略化 Boolean functions です

$$A_{1}=Y_{3}+Y_{2}$$

$A_{0}=Y_{3}+{Y_{2}}'Y_{1}$

同様に、出力のブール関数Vを次のように取得します。

$$V=Y_{3}+Y_{2}+Y_{1}+Y_{0}$$

論理ゲートを使用して、上記のブール関数を実装できます。ザ・circuit diagram 次の図に、4〜2のプライオリティエンコーダを示します。

上記の回路図には、2つの2入力ORゲート、1つの4入力ORゲート、1つの2入力ANDゲート、およびインバータが含まれています。ここで、ANDゲートとインバータの組み合わせは、複数の入力が同時に「1」に等しい場合でも、出力で有効なコードを生成するために使用されます。したがって、この回路は4つの入力を2ビットでエンコードします。priority 各入力に割り当てられます。

Multiplexerは、最大2 n個のデータ入力、「n」個の選択ライン、および単一の出力ラインを備えた組み合わせ回路です。これらのデータ入力の1つは、選択ラインの値に基づいて出力に接続されます。

'n'の選択行があるため、0と1の可能な組み合わせは2nになります。したがって、各組み合わせは1つのデータ入力のみを選択します。マルチプレクサは、Mux。

4x1マルチプレクサ

4x1マルチプレクサには、4つのデータ入力I 3、I 2、I 1&I 0、2つの選択ラインs 1&s 0、および1つの出力Yがあります。block diagram 次の図に、4x1マルチプレクサの概要を示します。

これらの4つの入力の1つは、これら2つの選択ラインに存在する入力の組み合わせに基づいて出力に接続されます。 Truth table 4x1マルチプレクサの概要を以下に示します。

| 選択ライン | 出力 | |

|---|---|---|

| S1 | S0 | Y |

| 0 | 0 | I 0 |

| 0 | 1 | I 1 |

| 1 | 0 | I 2 |

| 1 | 1 | I 3 |

真理値表から、直接書くことができます Boolean function 出力の場合、Y as

$$Y={S_{1}}'{S_{0}}'I_{0}+{S_{1}}'S_{0}I_{1}+S_{1}{S_{0}}'I_{2}+S_{1}S_{0}I_{3}$$

このブール関数は、インバーター、ANDゲートおよびORゲートを使用して実装できます。ザ・circuit diagram 4x1マルチプレクサの例を次の図に示します。

上記の回路の動作は簡単に理解できます。同様に、同じ手順に従って、8x1マルチプレクサと16x1マルチプレクサを実装できます。

高次マルチプレクサの実装。

ここで、低次マルチプレクサを使用して、次の2つの高次マルチプレクサを実装しましょう。

- 8x1マルチプレクサ

- 16x1マルチプレクサ

8x1マルチプレクサ

このセクションでは、4x1マルチプレクサと2x1マルチプレクサを使用して8x1マルチプレクサを実装しましょう。4x1マルチプレクサには、4つのデータ入力、2つの選択ライン、および1つの出力があることがわかっています。一方、8x1マルチプレクサには、8つのデータ入力、3つの選択ライン、および1つの出力があります。

したがって、2つ必要です 4x1 Multiplexers8つのデータ入力を取得するための最初の段階で。各4x1マルチプレクサは1つの出力を生成するため、2x1 Multiplexer 第1段階の出力を入力と見なし、最終出力を生成することにより、第2段階で。

ましょ8×1マルチプレクサは、8つのデータ入力を有するI 7 Iに0、3つの選択ラインS 2はS 1およびS 0と1つの出力Y.ザTruth table 8x1マルチプレクサの例を以下に示します。

| 選択入力 | 出力 | ||

|---|---|---|---|

| S2 | S1 | S0 | Y |

| 0 | 0 | 0 | I 0 |

| 0 | 0 | 1 | I 1 |

| 0 | 1 | 0 | I 2 |

| 0 | 1 | 1 | I 3 |

| 1 | 0 | 0 | I 4 |

| 1 | 0 | 1 | I 5 |

| 1 | 1 | 0 | I 6 |

| 1 | 1 | 1 | I7 |

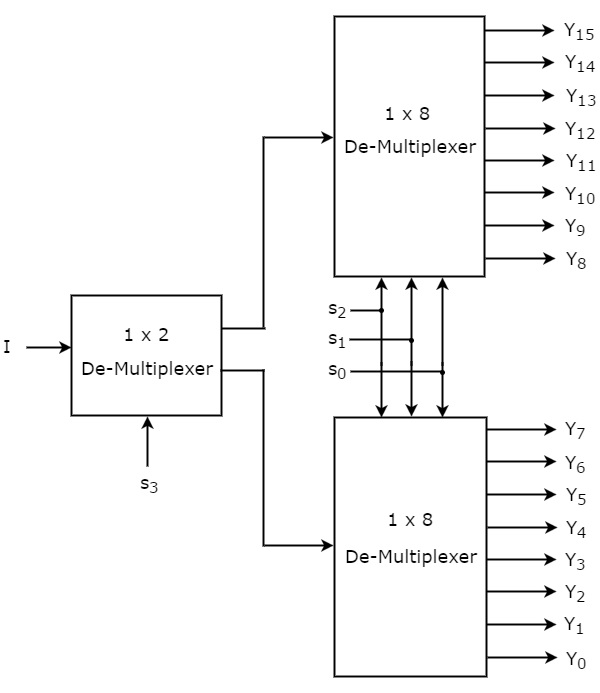

We can implement 8x1 Multiplexer using lower order Multiplexers easily by considering the above Truth table. The block diagram of 8x1 Multiplexer is shown in the following figure.

The same selection lines, s1 & s0 are applied to both 4x1 Multiplexers. The data inputs of upper 4x1 Multiplexer are I7 to I4 and the data inputs of lower 4x1 Multiplexer are I3 to I0. Therefore, each 4x1 Multiplexer produces an output based on the values of selection lines, s1 & s0.

The outputs of first stage 4x1 Multiplexers are applied as inputs of 2x1 Multiplexer that is present in second stage. The other selection line, s2 is applied to 2x1 Multiplexer.

If s2 is zero, then the output of 2x1 Multiplexer will be one of the 4 inputs I3 to I0 based on the values of selection lines s1 & s0.

If s2 is one, then the output of 2x1 Multiplexer will be one of the 4 inputs I7 to I4 based on the values of selection lines s1 & s0.