デジタル回路-ラッチ

それを操作するのに適したトリガーのタイプに基づいて、2つのタイプのメモリー要素があります。

- Latches

- Flip-flops

ラッチは、イネーブル信号で動作します。 level sensitive。一方、フリップフロップはエッジに敏感です。フリップフロップについては、次の章で説明します。それでは、SRラッチとDラッチについて1つずつ説明しましょう。

SRラッチ

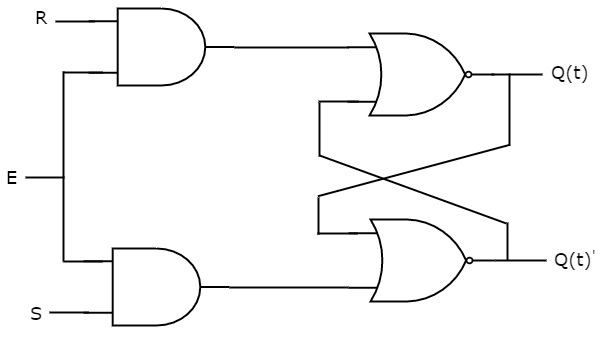

SRラッチは別名 Set Reset Latch。このラッチは、イネーブルEが「1」に維持されている限り出力に影響します。ザ・circuit diagram SRラッチの概要を次の図に示します。

この回路には、2つの入力SとRと2つの出力Q(t)とQ(t) 'があります。ザ・upper NOR gate 2つの入力Rと現在の状態の補数Q(t) 'があり、有効にすると次の状態Q(t + 1)が生成されます。Eは「1」です。

同様に、 lower NOR gate 2つの入力Sと現在の状態Q(t)があり、有効にすると次の状態Q(t + 1) 'の補数を生成します。Eは' 1 'です。

私たちはそれを知っています 2-input NOR gate入力の1つが「0」の場合、別の入力の補数である出力を生成します。同様に、入力の1つが「1」の場合、「0」出力を生成します。

S = 1の場合、次の状態Q(t + 1)は、現在の状態Q(t)の値に関係なく、「1」に等しくなります。

R = 1の場合、次の状態Q(t + 1)は、現在の状態Q(t)の値に関係なく、「0」に等しくなります。

いつでも、これら2つの入力のうち「1」のみにする必要があります。両方の入力が「1」の場合、次の状態Q(t + 1)値は未定義です。

次の表は、 state table SRラッチの。

| S | R | Q(t + 1) |

|---|---|---|

| 0 | 0 | Q(t) |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | - |

そのため、SRラッチは、入力条件に基づいて、ホールド、セット、リセットの3種類の機能を実行します。

Dラッチ

SRラッチには1つの欠点があります。つまり、入力SとRの両方が1の場合、次の状態値は予測できません。したがって、Dラッチによってこの困難を克服することができます。データラッチとも呼ばれます。ザ・circuit diagram Dラッチの概要を次の図に示します。

この回路には、単一の入力Dと2つの出力Q(t)およびQ(t) 'があります。Dラッチは、S amp;&R入力の間にインバーターを配置し、D入力をSに接続することにより、SRラッチから取得されます。つまり、SとRの組み合わせが同じ値になることを排除しました。

D = 0→S = 0&R = 1の場合、次の状態Q(t + 1)は、現在の状態Q(t)の値に関係なく、「0」に等しくなります。これは、SRラッチ状態テーブルの2行目に対応します。

D = 1→S = 1&R = 0の場合、次の状態Q(t + 1)は、現在の状態Q(t)の値に関係なく、「1」に等しくなります。これは、SRラッチ状態テーブルの3行目に対応します。

次の表は、 state table Dラッチの。

| D | Q(t + 1) |

|---|---|

| 0 | 0 |

| 1 | 1 |

したがって、Dラッチはデータ入力Dで利用可能な情報を保持します。つまり、イネーブルがHighである限り、Dラッチの出力は入力Dの変化に敏感です。

この章では、NORゲート間のクロスカップリングを提供することにより、さまざまなラッチを実装しました。同様に、NANDゲートを使用してこれらのラッチを実装できます。