デジタル回路-シフトレジスタ

1つのフリップフロップで1ビットの情報を格納できることはわかっています。複数ビットの情報を格納するには、複数のフリップフロップが必要です。バイナリデータを保持(保存)するために使用されるフリップフロップのグループは、次のように知られています。register。

レジスタがビットを右側または左側にシフトできる場合は、次のように知られています。 shift register。「N」ビットシフトレジスタには「N」フリップフロップが含まれています。以下は、入力の適用と出力へのアクセスに基づく4種類のシフトレジスタです。

- シリアル入力-シリアル出力シフトレジスタ

- シリアル入力-パラレル出力シフトレジスタ

- パラレル入力-シリアル出力シフトレジスタ

- パラレル入力-パラレル出力シフトレジスタ

シリアル入力-シリアル出力(SISO)シフトレジスタ

シリアル入力を可能にし、シリアル出力を生成するシフトレジスタは、シリアル入力–シリアル出力として知られています。 (SISO)シフトレジスタ。ザ・block diagram 次の図に、3ビットSISOシフトレジスタの概要を示します。

このブロック図は、3つのDフリップフロップで構成されています。 cascaded。つまり、1つのDフリップフロップの出力が次のDフリップフロップの入力として接続されます。同じクロック信号がそれぞれに適用されるため、これらのフリップフロップはすべて互いに同期しています。

このシフトレジスタでは、左端のDフリップフロップの入力からビットをシリアルに送信できます。したがって、この入力は次のようにも呼ばれます。serial input。クロック信号のポジティブエッジトリガーごとに、データは1つのステージから次のステージにシフトします。したがって、右端のDフリップフロップの出力からビットをシリアルに受信できます。したがって、この出力は次のようにも呼ばれます。serial output。

例

バイナリ情報を送信して、3ビットSISOシフトレジスタの動作を見てみましょう。 “011” 入力でLSBからMSBにシリアルに。

左端から右端へのDフリップフロップの初期ステータスが$ Q_ {2} Q_ {1} Q_ {0} = 000 $であると仮定します。私たちは理解することができますworking of 3-bit SISO shift register 次の表から。

| クロックの立ち上がりエッジがありません | シリアル入力 | Q 2 | Q 1 | Q 0 |

|---|---|---|---|---|

| 0 | - | 0 | 0 | 0 |

| 1 | 1(LSB) | 1 | 0 | 0 |

| 2 | 1 | 1 | 1 | 0 |

| 3 | 0(MSB) | 0 | 1 | 1(LSB) |

| 4 | - | - | 0 | 1 |

| 5 | - | - | - | 0(MSB) |

クロック信号がない場合のDフリップフロップの初期ステータスは$ Q_ {2} Q_ {1} Q_ {0} = 000 $です。ここでは、シリアル出力は$ Q_ {0} $から来ています。したがって、LSB(1)はクロックの3番目の立ち上がりエッジで受信され、MSB(0)はクロックの5番目の立ち上がりエッジで受信されます。

したがって、3ビットSISOシフトレジスタは、有効な出力を生成するために5つのクロックパルスを必要とします。同様に、N-bit SISO shift register が必要 2N-1 'N'ビット情報をシフトするためのクロックパルス。

シリアル入力-パラレル出力(SIPO)シフトレジスタ

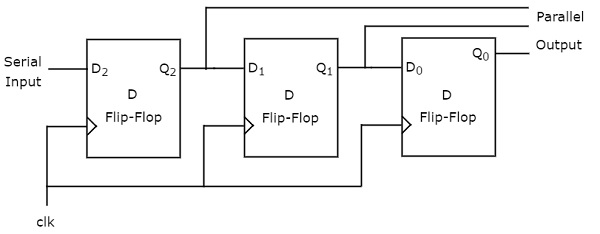

シリアル入力を可能にし、パラレル出力を生成するシフトレジスタは、シリアル入力–パラレル出力として知られています。 (SIPO)シフトレジスタ。ザ・block diagram 次の図に、3ビットSIPOシフトレジスタの概要を示します。

この回路は、カスケード接続された3つのDフリップフロップで構成されています。つまり、1つのDフリップフロップの出力が次のDフリップフロップの入力として接続されます。同じクロック信号がそれぞれに適用されるため、これらのフリップフロップはすべて互いに同期しています。

このシフトレジスタでは、左端のDフリップフロップの入力からビットをシリアルに送信できます。したがって、この入力は次のようにも呼ばれます。serial input。クロック信号のポジティブエッジトリガーごとに、データは1つのステージから次のステージにシフトします。この場合、各Dフリップフロップの出力に並列にアクセスできます。だから、私たちは得るでしょうparallel outputs このシフトレジスタから。

例

バイナリ情報を送信して、3ビットSIPOシフトレジスタの動作を見てみましょう。 “011” 入力でLSBからMSBにシリアルに。

左端から右端へのDフリップフロップの初期ステータスが$ Q_ {2} Q_ {1} Q_ {0} = 000 $であると仮定します。ここで、$ Q_ {2} $と$ Q_ {0} $はそれぞれMSBとLSBです。私たちは理解することができますworking of 3-bit SIPO shift register 次の表から。

| クロックの立ち上がりエッジがありません | シリアル入力 | Q 2(MSB) | Q 1 | Q 0(LSB) |

|---|---|---|---|---|

| 0 | - | 0 | 0 | 0 |

| 1 | 1(LSB) | 1 | 0 | 0 |

| 2 | 1 | 1 | 1 | 0 |

| 3 | 0(MSB) | 0 | 1 | 1 |

クロック信号がない場合のDフリップフロップの初期ステータスは$ Q_ {2} Q_ {1} Q_ {0} = 000 $です。バイナリ情報“011” は、クロックの3番目の立ち上がりエッジのDフリップフロップの出力で並列に取得されます。

したがって、3ビットSIPOシフトレジスタは、有効な出力を生成するために3つのクロックパルスを必要とします。同様に、N-bit SIPO shift register が必要 N 'N'ビット情報をシフトするためのクロックパルス。

パラレル入力-シリアル出力(PISO)シフトレジスタ

パラレル入力を可能にし、シリアル出力を生成するシフトレジスタは、パラレル入力-シリアル出力として知られています。 (PISO)シフトレジスタ。ザ・block diagram 次の図に、3ビットPISOシフトレジスタの概要を示します。

この回路は、カスケード接続された3つのDフリップフロップで構成されています。つまり、1つのDフリップフロップの出力が次のDフリップフロップの入力として接続されます。同じクロック信号がそれぞれに適用されるため、これらのフリップフロップはすべて互いに同期しています。

このシフトレジスタでは、 parallel inputsプリセットイネーブルを1に設定して、各Dフリップフロップに接続します。クロック信号のポジティブエッジトリガーごとに、データは1つのステージから次のステージにシフトします。だから、私たちはserial output 右端のDフリップフロップから。

例

バイナリ情報を適用して、3ビットPISOシフトレジスタの動作を見てみましょう。 “011” プリセット入力を介して並列に。

プリセット入力はクロックの立ち上がりエッジの前に適用されるため、左端から右端へのDフリップフロップの初期ステータスは$ Q_ {2} Q_ {1} Q_ {0} = 011 $になります。私たちは理解することができますworking of 3-bit PISO shift register 次の表から。

| クロックの立ち上がりエッジがありません | Q 2 | Q 1 | Q 0 |

|---|---|---|---|

| 0 | 0 | 1 | 1(LSB) |

| 1 | - | 0 | 1 |

| 2 | - | - | 0(LSB) |

ここでは、シリアル出力は$ Q_ {0} $から来ています。したがって、LSB(1)はクロックの立ち上がりエッジを適用する前に受信され、MSB(0)はクロックの2番目の立ち上がりエッジで受信されます。

したがって、3ビットのPISOシフトレジスタは、有効な出力を生成するために2つのクロックパルスを必要とします。同様に、N-bit PISO shift register が必要 N-1 'N'ビット情報をシフトするためのクロックパルス。

パラレル入力-パラレル出力(PIPO)シフトレジスタ

パラレル入力を可能にし、パラレル出力を生成するシフトレジスタは、Parallel In − ParallelOutとして知られています。 (PIPO)シフトレジスタ。ザ・block diagram 次の図に、3ビットPIPOシフトレジスタの概要を示します。

この回路は、カスケード接続された3つのDフリップフロップで構成されています。つまり、1つのDフリップフロップの出力が次のDフリップフロップの入力として接続されます。同じクロック信号がそれぞれに適用されるため、これらのフリップフロップはすべて互いに同期しています。

このシフトレジスタでは、 parallel inputsプリセットイネーブルを1にすると、各Dフリップフロップに並列入力を適用できます。プリセットまたはクリアを使用して並列入力を適用できます。これら2つは非同期入力です。つまり、フリップフロップは、非同期入力の値に基づいて、対応する出力を生成します。この場合、出力の影響はクロック遷移とは無関係です。だから、私たちはparallel outputs 各Dフリップフロップから。

例

バイナリ情報を適用して、3ビットPIPOシフトレジスタの動作を見てみましょう。 “011” プリセット入力を介して並列に。

プリセット入力はクロックの立ち上がりエッジの前に適用されるため、左端から右端へのDフリップフロップの初期ステータスは$ Q_ {2} Q_ {1} Q_ {0} = 011 $になります。だから、バイナリ情報“011” クロックの立ち上がりエッジを適用する前に、Dフリップフロップの出力で並列に取得されます。

したがって、3ビットPIPOシフトレジスタは、有効な出力を生成するためにゼロクロックパルスを必要とします。同様に、N-bit PIPO shift register 'N'ビット情報をシフトするためにクロックパルスを必要としません。