Цифровые схемы - Краткое руководство

Если основание или основание системы счисления - 'r', тогда числа, присутствующие в этой системе счисления, находятся в диапазоне от нуля до r-1. Общее количество чисел в этой системе счисления - "r". Итак, мы получим различные системы счисления, выбирая значения системы счисления больше или равные двум.

В этой главе давайте обсудим popular number systemsи как представить число в соответствующей системе счисления. Наиболее часто используются следующие системы счисления.

- Десятичная система счисления

- Двоичная система счисления

- Восьмеричная система счисления

- Шестнадцатеричная система счисления

Десятичная система счисления

В base или основание десятичной системы счисления 10. Итак, в этой системе счисления используются числа от 0 до 9. Часть числа, лежащая слева отdecimal pointназывается целой частью. Точно так же часть числа, которая находится справа от десятичной точки, называется дробной частью.

В этой системе счисления последовательные позиции слева от десятичной точки имеют веса 10 0 , 10 1 , 10 2 , 10 3 и так далее. Точно так же последовательные позиции справа от десятичной точки имеют веса 10 -1 , 10 -2 , 10 -3 и так далее. Это означает, что каждая позиция имеет определенный вес, которыйpower of base 10

пример

Рассмотрим decimal number 1358.246. Целая часть этого числа - 1358, дробная часть - 0,246. Цифры 8, 5, 3 и 1 имеют веса 100, 101, 10 2 и 10 3 соответственно. Точно так же цифры 2, 4 и 6 имеют веса 10 -1 , 10 -2 и 10 -3 соответственно.

Mathematically, мы можем записать это как

1358,246 = (1 × 10 3 ) + (3 × 10 2 ) + (5 × 10 1 ) + (8 × 10 0 ) + (2 × 10 -1 ) +

(4 × 10 -2 ) + (6 × 10 -3 )

После упрощения членов с правой стороны мы получим десятичное число, которое находится слева.

Двоичная система счисления

Все цифровые схемы и системы используют эту двоичную систему счисления. Вbase или основание этой системы счисления 2. Итак, в этой системе счисления используются числа 0 и 1.

Часть числа, лежащая слева от binary pointназывается целой частью. Точно так же часть числа, которая находится справа от двоичной точки, называется дробной частью.

В этой системе счисления последовательные позиции слева от двоичной точки имеют веса 2 0 , 2 1 , 2 2 , 2 3 и так далее. Точно так же последовательные позиции справа от двоичной точки имеют веса 2-1 , 2-2 , 2-3 и так далее. Это означает, что каждая позиция имеет определенный вес, которыйpower of base 2.

пример

Рассмотрим binary number 1101.011. Целая часть этого числа - 1101, а дробная часть - 0,011. Цифры 1, 0, 1 и 1 целой части имеют веса 2 0 , 2 1 , 2 2 , 2 3 соответственно. Точно так же цифры 0, 1 и 1 дробной части имеют веса 2–1 , 2–2 , 2–3 соответственно.

Mathematically, мы можем записать это как

1101.011 = (1 × 2 3 ) + (1 × 2 2 ) + (0 × 2 1 ) + (1 × 2 0 ) + (0 × 2 -1 ) +

(1 × 2 -2 ) + (1 × 2 -3 )

После упрощения членов правой части мы получим десятичное число, которое является эквивалентом двоичного числа в левой части.

Восьмеричная система счисления

В base или основание восьмеричной системы счисления 8. Итак, в этой системе счисления используются числа от 0 до 7. Часть числа, лежащая слева отoctal pointназывается целой частью. Точно так же часть числа, которая находится справа от восьмеричной точки, называется дробной частью.

В этой системе счисления последовательные позиции слева от восьмеричной точки имеют веса 8 0 , 8 1 , 8 2 , 8 3 и так далее. Точно так же последовательные позиции справа от восьмеричной точки имеют веса 8 -1 , 8 -2 , 8 -3 и так далее. Это означает, что каждая позиция имеет определенный вес, которыйpower of base 8.

пример

Рассмотрим octal number 1457.236. Целая часть этого числа равна 1457, а дробная часть - 0,236. Цифры 7, 5, 4 и 1 имеют веса 8 0 , 8 1 , 8 2 и 8 3 соответственно. Точно так же цифры 2, 3 и 6 имеют веса 8-1 , 8-2 , 8-3 соответственно.

Mathematically, мы можем записать это как

1457,236 = (1 × 8 3 ) + (4 × 8 2 ) + (5 × 8 1 ) + (7 × 8 0 ) + (2 × 8 -1 ) +

(3 × 8 -2 ) + (6 × 8 -3 )

После упрощения членов правой части мы получим десятичное число, которое является эквивалентом восьмеричного числа в левой части.

Шестнадцатеричная система счисления

В base или основание шестнадцатеричной системы счисления 16. Итак, в этой системе счисления используются числа от 0 до 9 и буквы от A до F. Десятичный эквивалент шестнадцатеричных цифр от A до F - от 10 до 15.

Часть числа, лежащая слева от hexadecimal pointназывается целой частью. Точно так же часть числа, которая находится справа от десятичной шестнадцатеричной точки, называется дробной частью.

В этой системе счисления последовательные позиции слева от десятичной шестнадцатеричной точки имеют веса 16 0 , 16 1 , 16 2 , 16 3 и так далее. Аналогичным образом, последовательные позиции справа от десятичной шестнадцатеричной точки имеют веса 16 -1 , 16 -2 , 16 -3 и так далее. Это означает, что каждая позиция имеет определенный вес, которыйpower of base 16.

пример

Рассмотрим Hexa-decimal number 1A05.2C4. Целая часть этого числа - 1A05, а дробная часть - 0,2C4. Цифры 5, 0, A и 1 имеют веса 16 0 , 16 1 , 16 2 и 16 3 соответственно. Точно так же цифры 2, C и 4 имеют веса 16-1 , 16-2 и 16-3 соответственно.

Mathematically, мы можем записать это как

1A05.2C4 = (1 × 16 3 ) + (10 × 16 2 ) + (0 × 16 1 ) + (5 × 16 0 ) + (2 × 16 -1 ) +

(12 × 16 -2 ) + (4 × 16 -3 )

После упрощения членов правой части мы получим десятичное число, которое эквивалентно шестнадцатеричному десятичному числу слева.

В предыдущей главе мы рассмотрели четыре известные системы счисления. В этой главе давайте переведем числа из одной системы счисления в другую, чтобы найти эквивалентное значение.

Преобразование десятичного числа в другое основание

Если десятичное число содержит как целую, так и дробную часть, тогда конвертируйте обе части десятичного числа в другую основу по отдельности. Выполните следующие действия для преобразования десятичного числа в эквивалентное ему число с основанием "r".

Делать division целой части десятичного числа и successive quotientsс основанием 'r' и запишите остаток, пока частное не станет равным нулю. Рассмотрим остатки в обратном порядке, чтобы получить целую часть эквивалентного числа по основанию 'r'. Это означает, что первый и последний остатки обозначают наименее значащую цифру и наиболее значительную цифру соответственно.

Делать multiplication дробной части десятичного числа и successive fractionsс основанием 'r' и записывайте перенос, пока результат не станет нулевым или не будет получено желаемое количество эквивалентных цифр. Рассмотрим обычную последовательность переноса, чтобы получить дробную часть эквивалентного числа по основанию 'r'.

Преобразование десятичного числа в двоичное

При преобразовании десятичного числа в его эквивалентное двоичное число выполняются следующие два типа операций.

- Деление целой части и последовательных частных с основанием 2.

- Умножение дробной части и последовательных дробей с основанием 2.

Example

Рассмотрим decimal number 58.25. Здесь целая часть равна 58, а дробная часть - 0,25.

Step 1 - Деление 58 и последовательные частные с основанием 2.

| Операция | Частное | Остаток |

|---|---|---|

| 58/2 | 29 | 0 (LSB) |

| 29/2 | 14 | 1 |

| 14/2 | 7 | 0 |

| 7/2 | 3 | 1 |

| 3/2 | 1 | 1 |

| 1/2 | 0 | 1(MSB) |

⇒ (58) 10 = (111010) 2

Следовательно integer part эквивалентного двоичного числа 111010.

Step 2 - Умножение 0,25 и последовательных дробей с основанием 2.

| Операция | Результат | Нести |

|---|---|---|

| 0,25 х 2 | 0,5 | 0 |

| 0,5 х 2 | 1.0 | 1 |

| - | 0,0 | - |

⇒ (0,25) 10 = (0,01) 2

Следовательно fractional part эквивалентного двоичного числа .01

⇒ (58,25) 10 = (111010,01) 2

Следовательно binary equivalent десятичного числа 58,25 равно 111010,01.

Преобразование десятичных чисел в восьмеричные

При преобразовании десятичного числа в его эквивалентное восьмеричное число выполняются следующие два типа операций.

Деление целой части и последовательных частных с основанием 8.

Умножение дробной части и последовательных дробей с основанием 8.

Example

Рассмотрим decimal number 58.25. Здесь целая часть равна 58, а дробная часть - 0,25.

Step 1 - Деление 58 и последовательные частные с основанием 8.

| Операция | Частное | Остаток |

|---|---|---|

| 58/8 | 7 | 2 |

| 7/8 | 0 | 7 |

⇒ (58) 10 = (72) 8

Следовательно integer part эквивалентного восьмеричного числа 72.

Step 2 - Умножение 0,25 и последовательных дробей с основанием 8.

| Операция | Результат | Нести |

|---|---|---|

| 0,25 х 8 | 2,00 | 2 |

| - | 0,00 | - |

⇒ (0,25) 10 = (0,2) 8

Следовательно fractional part эквивалентного восьмеричного числа .2

⇒ (58,25) 10 = (72,2) 8

Следовательно octal equivalent десятичного числа 58,25 равно 72,2.

Преобразование десятичного числа в шестнадцатеричное

При преобразовании десятичного числа в его эквивалентное шестнадцатеричное число имеют место следующие два типа операций.

- Деление целой части и последовательных частных с основанием 16.

- Умножение дробной части и последовательных дробей с основанием 16.

Example

Рассмотрим decimal number 58.25. Здесь целая часть равна 58, а десятичная часть - 0,25.

Step 1 - Деление 58 и последовательные частные с основанием 16.

| Операция | Частное | Остаток |

|---|---|---|

| 58/16 | 3 | 10 = А |

| 3/16 | 0 | 3 |

⇒ (58) 10 = (3A) 16

Следовательно integer part эквивалентного шестнадцатеричного числа - 3А.

Step 2 - Умножение 0,25 и последовательных дробей с основанием 16.

| Операция | Результат | Нести |

|---|---|---|

| 0,25 х 16 | 4.00 | 4 |

| - | 0,00 | - |

⇒ (0,25) 10 = (0,4) 16

Следовательно fractional part эквивалентного шестнадцатеричного числа .4.

⇒(58.25)10 = (3A.4)16

Следовательно Hexa-decimal equivalent десятичного числа 58,25 равно 3A.4.

Преобразование двоичного числа в другие базы

Процесс преобразования числа из двоичного в десятичное отличается от процесса преобразования двоичного числа в другие основания. Теперь давайте обсудим преобразование двоичного числа в десятичную, восьмеричную и шестнадцатеричную системы счисления по очереди.

Преобразование двоичного числа в десятичное

Для преобразования двоичного числа в его эквивалентное десятичное число сначала умножьте биты двоичного числа на соответствующие позиционные веса, а затем сложите все эти произведения.

Example

Рассмотрим binary number 1101.11.

Mathematically, мы можем записать это как

(1101.11) 2 = (1 × 2 3 ) + (1 × 2 2 ) + (0 × 2 1 ) + (1 × 2 0 ) + (1 × 2 -1 ) +

(1 × 2 -2 )

⇒ (1101,11) 2 = 8 + 4 + 0 + 1 + 0,5 + 0,25 = 13,75

⇒ (1101,11) 2 = (13,75) 10

Следовательно decimal equivalent двоичного числа 1101,11 равно 13,75.

Двоичное преобразование в восьмеричное

Мы знаем, что основания двоичной и восьмеричной систем счисления равны 2 и 8 соответственно. Три бита двоичного числа эквивалентны одной восьмеричной цифре, поскольку 2 3 = 8.

Выполните эти два шага для преобразования двоичного числа в его эквивалентное восьмеричное число.

Начните с двоичной точки и сделайте группы по 3 бита по обе стороны от двоичной точки. Если при формировании группы из 3-х битов на один или два бита меньше, то необходимо включить необходимое количество нулей на крайних сторонах.

Запишите восьмеричные цифры, соответствующие каждой группе из 3 бит.

Example

Рассмотрим binary number 101110.01101.

Step 1 - Сделайте группы по 3 бита с обеих сторон двоичной точки.

101 110.011 01

Здесь, справа от двоичной точки, последняя группа имеет только 2 бита. Итак, добавьте один ноль на крайнюю сторону, чтобы сделать его группой из 3 бит.

⇒ 101 110.011 010

Step 2 - Запишите восьмеричные цифры, соответствующие каждой группе из 3 бит.

⇒ (101 110,011 010) 2 = (56,32) 8

Следовательно octal equivalent двоичного числа 101110.01101 равно 56.32.

Преобразование двоичного числа в шестнадцатеричное

Мы знаем, что основания двоичной и шестнадцатеричной систем счисления равны 2 и 16 соответственно. Четыре бита двоичного числа эквивалентны одной десятичной шестнадцатеричной цифре, поскольку 2 4 = 16.

Выполните эти два шага для преобразования двоичного числа в его эквивалентное шестнадцатеричное десятичное число.

Начните с двоичной точки и сделайте группы по 4 бита по обе стороны от двоичной точки. Если при образовании группы из 4-х битов несколько бит меньше, то по крайним сторонам нужно добавить необходимое количество нулей.

Запишите шестнадцатеричные цифры, соответствующие каждой группе из 4 бит.

Example

Рассмотрим binary number 101110.01101

Step 1 - Составляйте группы по 4 бита с обеих сторон двоичной точки.

10 1110.0110 1

Здесь первая группа имеет только 2 бита. Итак, добавьте два нуля на крайнюю сторону, чтобы получилась группа из 4 бит. Точно так же добавьте три нуля на крайнюю сторону, чтобы последняя группа также была группой из 4 бит.

⇒ 0010 1110.0110 1000

Step 2 - Запишите шестнадцатеричные десятичные цифры, соответствующие каждой группе из 4 бит.

⇒ (0010 1110.0110 1000) 2 = (2E.68) 16

Следовательно Hexa-decimal equivalent двоичного числа 101110.01101 равно (2E.68).

Преобразование восьмеричного числа в другое основание

Процесс преобразования восьмеричного числа в десятичное отличается от процесса преобразования восьмеричного числа в другие основания. Теперь давайте обсудим преобразование восьмеричного числа в десятичную, двоичную и шестнадцатеричную системы счисления по очереди.

Восьмеричное преобразование в десятичное

Для преобразования восьмеричного числа в его эквивалентное десятичное число сначала умножьте цифры восьмеричного числа на соответствующие позиционные веса, а затем сложите все эти произведения.

Example

Рассмотрим octal number 145.23.

Mathematically, мы можем записать это как

(145,23) 8 = (1 × 8 2 ) + (4 × 8 1 ) + (5 × 8 0 ) + (2 × 8 -1 ) + (3 × 8 -2 )

⇒ (145,23) 8 = 64 + 32 + 5 + 0,25 + 0,05 = 101,3

⇒ (145,23) 8 = (101,3) 10

Следовательно decimal equivalent восьмеричного числа 145,23 равно 101,3.

Восьмеричное преобразование в двоичное

Процесс преобразования восьмеричного числа в эквивалентное двоичное число прямо противоположен процессу преобразования двоичного числа в восьмеричное. Представляя каждую восьмеричную цифру 3 битами, мы получим эквивалентное двоичное число.

Example

Рассмотрим octal number 145.23.

Представьте каждую восьмеричную цифру 3 битами.

(145,23) 8 = (001 100 101,010 011) 2

Значение не меняется при удалении нулей, которые находятся на крайнем крае.

⇒ (145,23) 8 = (1100101.010011) 2

Следовательно binary equivalent восьмеричного числа 145.23 равно 1100101.010011.

Восьмеричное преобразование в шестнадцатеричное

Выполните эти два шага для преобразования восьмеричного числа в его эквивалентное шестнадцатеричное десятичное число.

- Преобразуйте восьмеричное число в его эквивалентное двоичное число.

- Преобразуйте указанное выше двоичное число в его эквивалентное шестнадцатеричное десятичное число.

Example

Рассмотрим octal number 145.23

В предыдущем примере мы получили двоичный эквивалент восьмеричного числа 145,23 как 1100101.010011.

Следуя процедуре преобразования двоичного кода в шестнадцатеричный, мы получим

(1100101.010011) 2 = (65,4 ° C) 16

⇒ (145,23) 8 = (65,4C) 16

Следовательно Hexa-decimal equivalentвосьмеричного числа 145.23 является 65.4 С .

Преобразование шестнадцатеричных чисел в другие основания

Процесс преобразования шестнадцатеричного числа в десятичное отличается от процесса преобразования шестнадцатеричного числа в другое основание. Теперь давайте обсудим преобразование шестнадцатеричного числа в десятичную, двоичную и восьмеричную системы счисления по очереди.

Преобразование шестнадцатеричного числа в десятичное

Для преобразования шестнадцатеричного числа в его эквивалентное десятичное число сначала умножьте цифры шестнадцатеричного числа на соответствующие позиционные веса, а затем сложите все эти произведения.

Example

Рассмотрим Hexa-decimal number 1A5.2

Mathematically, мы можем записать это как

(1A5.2) 16 = (1 × 16 2 ) + (10 × 16 1 ) + (5 × 16 0 ) + (2 × 16 -1 )

⇒ (1A5.2) 16 = 256 + 160 + 5 + 0,125 = 421,125

⇒ (1A5.2) 16 = (421,125) 10

Следовательно decimal equivalent шестнадцатеричного числа 1A5.2 равно 421,125.

Шестнадцатеричное преобразование в двоичное

Процесс преобразования шестнадцатеричного числа в его эквивалентное двоичное число прямо противоположен процессу преобразования двоичного числа в шестнадцатеричное. Представляя каждую шестнадцатеричную цифру 4 битами, мы получим эквивалентное двоичное число.

Example

Рассмотрим Hexa-decimal number 65.4C

Представьте каждую шестнадцатеричную цифру 4 битами.

(65.4C) 6 = (0110 0101.0100 1100) 2

Значение не меняется при удалении нулей, которые находятся на двух крайних сторонах.

⇒ (65,4C) 16 = (1100101.010011) 2

Следовательно binary equivalent шестнадцатеричного числа 65.4C равно 1100101.010011.

Преобразование шестнадцатеричного числа в восьмеричное

Выполните эти два шага для преобразования шестнадцатеричного числа в его эквивалентное восьмеричное число.

- Преобразуйте десятичное шестнадцатеричное число в его эквивалентное двоичное число.

- Преобразуйте указанное выше двоичное число в его эквивалентное восьмеричное число.

Example

Рассмотрим Hexa-decimal number 65.4C

В предыдущем примере мы получили двоичный эквивалент шестнадцатеричного числа 65.4C как 1100101.010011.

Следуя процедуре преобразования двоичного числа в восьмеричное, мы получим

(1100101.010011) 2 = (145,23) 8

⇒ (65,4C) 16 = (145,23)

Следовательно octal equivalentшестнадцатеричного числа 65,4 C равно 145,23.

Мы можем разделить двоичные числа на следующие две группы: Unsigned numbers и Signed numbers.

Беззнаковые числа

Беззнаковые числа содержат только величину числа. У них нет никаких знаков. Это означает, что все двоичные числа без знака положительны. Как и в десятичной системе счисления, размещение положительного знака перед числом необязательно для представления положительных чисел. Следовательно, все положительные числа, включая ноль, можно рассматривать как числа без знака, если перед числом не установлен положительный знак.

Подписанные номера

Числа со знаком содержат знак и величину числа. Как правило, знак ставится перед числом. Итак, мы должны учитывать положительный знак для положительных чисел и отрицательный знак для отрицательных чисел. Следовательно, все числа можно рассматривать как числа со знаком, если перед числом поставлен соответствующий знак.

Если бит знака равен нулю, это означает, что двоичное число положительно. Аналогично, если бит знака равен единице, это означает, что двоичное число отрицательно.

Представление двоичных чисел без знака

Биты, присутствующие в двоичном числе без знака, содержат magnitudeчисла. Это означает, что если двоичное число без знака содержит‘N’ биты, то все N биты представляют величину числа, поскольку у него нет знакового бита.

Example

Рассмотрим decimal number 108. Двоичный эквивалент этого числа:1101100. Это представление двоичного числа без знака.

(108) 10 = (1101100) 2

Он имеет 7 бит. Эти 7 битов представляют величину числа 108.

Представление двоичных чисел со знаком

Старший значащий бит (MSB) двоичных чисел со знаком используется для обозначения знака чисел. Следовательно, его также называютsign bit. Положительный знак представлен помещением «0» в знаковый бит. Точно так же отрицательный знак представлен помещением «1» в знаковый бит.

Если двоичное число со знаком содержит N битов, тогда (N-1) биты представляют только величину числа, поскольку один бит (MSB) зарезервирован для представления знака числа.

Есть три types of representations для двоичных чисел со знаком

- Форма "Знак-величина"

- Форма дополнения 1

- Форма дополнения 2

Представление положительного числа во всех этих трех формах одинаково. Но в каждой форме будет отличаться только представление отрицательного числа.

Example

Рассмотрим positive decimal number +108. Двоичный эквивалент величины этого числа - 1101100. Эти 7 битов представляют величину числа 108. Поскольку это положительное число, считайте знаковый бит равным нулю, который помещается в крайнюю левую часть величины.

(+108) 10 = (01101100) 2

Следовательно signed binary representationположительного десятичного числа +108. Таким образом, одно и то же представление действительно в форме знак-величина, в форме дополнения до единицы и в форме дополнения до двух для положительного десятичного числа +108.

Форма "Знак-величина"

В форме знака-величины MSB используется для представления sign числа, а остальные биты представляют magnitudeчисла. Итак, просто включите знаковый бит в крайнюю левую часть двоичного числа без знака. Это представление похоже на представление десятичных чисел со знаком.

Example

Рассмотрим negative decimal number -108. Величина этого числа 108. Мы знаем, что двоичное представление 108 без знака - это 1101100. Оно имеет 7 бит. Все эти биты представляют величину.

Поскольку данное число отрицательное, считайте знаковый бит равным единице, который находится в крайней левой части величины.

(-108) 10 = (11101100) 2

Следовательно, знак-величина -108 представляет собой 11101100.

Форма дополнения 1

Дополнение числа до 1 получается следующим образом: complementing all the bitsзнакового двоичного числа. Таким образом, дополнение положительного числа до единицы дает отрицательное число. Точно так же дополнение отрицательного числа до единицы дает положительное число.

Это означает, что если вы выполните два раза дополнение двоичного числа до единицы, включая знаковый бит, то вы получите исходное двоичное число со знаком.

Example

Рассмотрим negative decimal number -108. Величина этого числа 108. Мы знаем, что двоичное представление числа 108 со знаком - 01101100.

Он имеет 8 бит. Старший бит этого числа равен нулю, что указывает на положительное число. Дополнение к нулю равно единице, и наоборот. Итак, заменим нули на единицы, а единицы на нули, чтобы получить отрицательное число.

(-108) 10 = (10010011) 2

Следовательно 1’s complement of (108)10 является (10010011)2.

Форма дополнения 2

Дополнение до 2 двоичного числа получается следующим образом: adding one to the 1’s complementзнакового двоичного числа. Итак, дополнение до 2 положительного числа дает отрицательное число. Точно так же дополнение отрицательного числа до 2 дает положительное число.

Это означает, что если вы выполните двойное дополнение двоичного числа, включая знаковый бит, то вы получите исходное двоичное число со знаком.

Example

Рассмотрим negative decimal number -108.

Мы знаем, что до единицы (108)10 является (10010011)2

Дополнение 2 к (108) 10 = 1 дополнение (108) 10 + 1.

= 10010011 + 1

= 10010100

Следовательно 2’s complement of (108)10 является (10010100)2.

В этой главе давайте обсудим основные арифметические операции, которые могут быть выполнены с любыми двумя двоичными числами со знаком, используя метод дополнения до 2. Вbasic arithmetic operations сложение и вычитание.

Сложение двух двоичных чисел со знаком

Рассмотрим два двоичных числа со знаком A и B, которые представлены в виде дополнения до 2. Мы можем выполнитьadditionэтих двух чисел, что аналогично сложению двух двоичных чисел без знака. Но, если результирующая сумма содержит бит переноса из знака, то отбросьте (игнорируйте) его, чтобы получить правильное значение.

Если результирующая сумма положительна, вы можете определить ее величину напрямую. Но, если результирующая сумма отрицательна, то возьмите ее дополнение до 2, чтобы получить величину.

Пример 1

Давайте выполним addition двух десятичных чисел +7 and +4 используя метод дополнения до 2.

В 2’s complement представления +7 и +4 с 5 битами каждое показаны ниже.

(+7) 10 = (00111) 2

(+4) 10 = (00100) 2

Сложение этих двух чисел есть

(+7) 10 + (+ 4) 10 = (00111) 2 + (00100) 2

⇒ (+7) 10 + (+ 4) 10 = (01011) 2 .

Результирующая сумма содержит 5 бит. Таким образом, нет никакого переноса из знакового бита. Знаковый бит '0' указывает, что результирующая сумма равнаpositive. Итак, величина суммы равна 11 в десятичной системе счисления. Следовательно, сложение двух положительных чисел даст еще одно положительное число.

Пример 2

Давайте выполним addition двух десятичных чисел -7 и -4 используя метод дополнения до 2.

В 2’s complement Представление -7 и -4 с 5 битами каждое показано ниже.

(−7) 10 = (11001) 2

(−4) 10 = (11100) 2

Сложение этих двух чисел есть

(−7) 10 + (−4) 10 = (11001) 2 + (11100) 2

⇒ (−7) 10 + (−4) 10 = (110101) 2 .

Результирующая сумма содержит 6 бит. В этом случае перенос получается из знакового бита. Итак, мы можем удалить это

Итоговая сумма после удаления переноса составляет (−7) 10 + (−4) 10 =(10101)2.

Знаковый бит '1' указывает, что результирующая сумма равна negative. Итак, взяв двойное дополнение к нему, мы получим величину результирующей суммы как 11 в десятичной системе счисления. Следовательно, сложение двух отрицательных чисел даст еще одно отрицательное число.

Вычитание двух двоичных чисел со знаком

Рассмотрим два двоичных числа со знаком A и B, которые представлены в виде дополнения до 2. Мы знаем, что дополнение до 2 положительного числа дает отрицательное число. Итак, всякий раз, когда нам нужно вычесть число B из числа A, возьмите дополнение B до 2 и добавьте его к A. Итак,mathematically мы можем записать это как

A - B = A + (2's complement of B)

Точно так же, если нам нужно вычесть число A из числа B, возьмем дополнение A до 2 и прибавим его к B. Итак, mathematically мы можем записать это как

B - A = B + (2's complement of A)

Итак, вычитание двух двоичных чисел со знаком аналогично сложению двух двоичных чисел со знаком. Но мы должны взять 2-кратное дополнение числа, которое предполагается вычесть. Этоadvantage2-х комплементарной техники. Следуйте тем же правилам сложения двух двоичных чисел со знаком.

Пример 3

Давайте выполним subtraction двух десятичных чисел +7 and +4 используя метод дополнения до 2.

Вычитание этих двух чисел равно

(+7) 10 - (+4) 10 = (+7) 10 + (−4) 10 .

В 2’s complement Представление +7 и -4 с 5 битами каждое показано ниже.

(+7) 10 = (00111) 2

(+4) 10 = (11100) 2

⇒ (+7) 10 + (+4) 10 = (00111) 2 + (11100) 2 = (00011) 2

Здесь перенос, полученный из знакового бита. Итак, мы можем удалить это. Итоговая сумма после удаления переноса равна

(+7) 10 + (+4) 10 =(00011)2

Знаковый бит '0' указывает, что результирующая сумма равна positive. Итак, его величина в десятичной системе счисления равна 3. Следовательно, вычитание двух десятичных чисел +7 и +4 равно +3.

Пример 4

Давайте выполним subtraction of два десятичных числа +4 и +7 используя метод дополнения до 2.

Вычитание этих двух чисел равно

(+4) 10 - (+7) 10 = (+4) 10 + (−7) 10 .

В 2’s complement Представление +4 и -7 с 5 битами каждое показано ниже.

(+4) 10 = (00100) 2

(-7) 10 = (11001) 2

⇒ (+4) 10 + (-7) 10 = (00100) 2 + (11001) 2 = (11101) 2

Здесь перенос не получается из знакового бита. Знаковый бит '1' указывает, что результирующая сумма равнаnegative. Итак, взяв двойное дополнение к нему, мы получим величину итоговой суммы как 3 в десятичной системе счисления. Следовательно, вычитание двух десятичных чисел +4 и +7 равно -3.

При кодировании, когда числа или буквы представлены определенной группой символов, говорят, что это число или буква кодируются. Группа символов называетсяcode. Цифровые данные представляются, хранятся и передаются как группа битов. Эта группа бит также называетсяbinary code.

Двоичные коды можно разделить на два типа.

- Взвешенные коды

- Невзвешенные коды

Если в коде есть позиционные веса, то он называется weighted code. В противном случае это невзвешенный код. Взвешенные коды могут быть дополнительно классифицированы как коды с положительным весом и коды с отрицательным весом.

Двоичные коды для десятичных цифр

В следующей таблице показаны различные двоичные коды десятичных цифр от 0 до 9.

| Десятичная цифра | Код 8421 | Код 2421 | 84-2-1 Код | Код превышения 3 |

|---|---|---|---|---|

| 0 | 0000 | 0000 | 0000 | 0011 |

| 1 | 0001 | 0001 | 0111 | 0100 |

| 2 | 0010 | 0010 | 0110 | 0101 |

| 3 | 0011 | 0011 | 0101 | 0110 |

| 4 | 0100 | 0100 | 0100 | 0111 |

| 5 | 0101 | 1011 | 1011 | 1000 |

| 6 | 0110 | 1100 | 1010 | 1001 |

| 7 | 0111 | 1101 | 1001 | 1010 |

| 8 | 1000 | 1110 | 1000 | 1011 |

| 9 | 1001 | 1111 | 1111 | 1100 |

У нас есть 10 цифр в десятичной системе счисления. Чтобы представить эти 10 цифр в двоичном формате, нам требуется минимум 4 бита. Но с 4 битами будет 16 уникальных комбинаций нулей и единиц. Поскольку у нас всего 10 десятичных цифр, остальные 6 комбинаций нулей и единиц не требуются.

8 4 2 1 код

Веса этого кода 8, 4, 2 и 1.

В этом коде все положительные веса. Итак, этоpositively weighted code.

Этот код также называется natural BCD (Десятичное число с двоичным кодом) code.

Example

Давайте найдем двоично-десятичный эквивалент десятичного числа 786. Это число состоит из трех десятичных цифр 7, 8 и 6. Из таблицы мы можем записать двоично-десятичные (8421) коды 7, 8 и 6: 0111, 1000 и 0110 соответственно. .

∴ (786)10 = (011110000110)BCD

В представлении BCD 12 бит, поскольку каждый десятичный код BCD имеет 4 бита.

2 4 2 1 код

Веса этого кода - 2, 4, 2 и 1.

В этом коде все положительные веса. Итак, этоpositively weighted code.

Это unnatural BCDкод. Сумма весов неестественных кодов BCD равна 9.

Это self-complementingкод. Самостоятельные коды обеспечивают дополнение до 9 десятичного числа, просто меняя местами 1 и 0 в его эквивалентном представлении 2421.

Example

Давайте найдем 2421 эквивалент десятичного числа 786. Это число состоит из 3 десятичных цифр 7, 8 и 6. Из таблицы мы можем записать коды 2421 из 7, 8 и 6: 1101, 1110 и 1100 соответственно.

Следовательно, 2421 эквивалент десятичного числа 786 равен 110111101100.

8 4-2-1 код

Веса этого кода - 8, 4, -2 и -1.

Этот код имеет отрицательные веса наряду с положительными. Итак, этоnegatively weighted code.

Это unnatural BCD код.

Это self-complementing код.

Example

Давайте найдем эквивалент 8 4-2-1 десятичного числа 786. Это число состоит из 3 десятичных цифр 7, 8 и 6. Из таблицы мы можем записать коды 8 4-2-1 чисел 7, 8 и 6. равны 1001, 1000 и 1010 соответственно.

Следовательно, эквивалент 8 4 -2 -1 десятичного числа 786 равен 100110001010.

Код превышения 3

Этот код не имеет весов. Итак, этоun-weighted code.

Мы получим код Превышения 3 десятичного числа, добавив три (0011) к двоичному эквиваленту этого десятичного числа. Следовательно, он называется кодом превышения 3.

Это self-complementing код.

Example

Давайте найдем эквивалент Превышения 3 десятичного числа 786. Это число состоит из 3 десятичных цифр 7, 8 и 6. Из таблицы мы можем записать коды Превышения 3 из 7, 8 и 6: 1010, 1011 и 1001 соответственно.

Следовательно, эквивалент десятичного числа 786 в избытке 3 равен 101010111001

Код Грея

В следующей таблице показаны 4-битные коды Грея, соответствующие каждому 4-битному двоичному коду.

| Десятичное число | Бинарный код | Код Грея |

|---|---|---|

| 0 | 0000 | 0000 |

| 1 | 0001 | 0001 |

| 2 | 0010 | 0011 |

| 3 | 0011 | 0010 |

| 4 | 0100 | 0110 |

| 5 | 0101 | 0111 |

| 6 | 0110 | 0101 |

| 7 | 0111 | 0100 |

| 8 | 1000 | 1100 |

| 9 | 1001 | 1101 |

| 10 | 1010 | 1111 |

| 11 | 1011 | 1110 |

| 12 | 1100 | 1010 |

| 13 | 1101 | 1011 |

| 14 | 1110 | 1001 |

| 15 | 1111 | 1000 |

Этот код не имеет весов. Итак, этоun-weighted code.

В приведенной выше таблице последовательные коды Грея различаются только одной битовой позицией. Следовательно, этот код называетсяunit distance код.

Преобразование двоичного кода в код Грея

Выполните следующие действия для преобразования двоичного кода в эквивалентный ему код Грея.

Рассмотрим данный двоичный код и поставим ноль слева от MSB.

Сравните следующие два бита, начиная с нуля. Если 2 бита одинаковы, то выход равен нулю. В противном случае на выходе будет один.

Повторяйте вышеуказанный шаг, пока не получите младший бит кода Грея.

Example

Из таблицы мы знаем, что код Грея, соответствующий двоичному коду 1000, равен 1100. Теперь давайте проверим его, используя описанную выше процедуру.

Учитывая, что двоичный код равен 1000.

Step 1 - Если поставить ноль слева от MSB, двоичный код будет 01000.

Step 2 - Сравнивая два последовательных бита нового двоичного кода, мы получим код Грея как 1100.

Мы знаем, что биты 0 и 1 соответствуют двум разным диапазонам аналоговых напряжений. Таким образом, во время передачи двоичных данных из одной системы в другую также может добавляться шум. Из-за этого могут быть ошибки в полученных данных в другой системе.

Это означает, что бит 0 может измениться на 1 или бит 1 может измениться на 0. Мы не можем избежать помех от шума. Но мы можем сначала вернуть исходные данные, определив наличие каких-либо ошибок, а затем исправив эти ошибки. Для этого мы можем использовать следующие коды.

- Коды обнаружения ошибок

- Коды исправления ошибок

Error detection codes- используются для обнаружения ошибок, присутствующих в полученных данных (битовый поток). Эти коды содержат некоторые биты, которые включаются (добавляются) к исходному потоку битов. Эти коды обнаруживают ошибку, если она возникла при передаче исходных данных (битовый поток).Example - Код четности, код Хэмминга.

Error correction codes- используются для исправления ошибок, присутствующих в полученных данных (битовом потоке), чтобы мы получили исходные данные. Коды исправления ошибок также используют аналогичную стратегию кодов обнаружения ошибок.Example - Код Хэмминга.

Поэтому для обнаружения и исправления ошибок к битам данных во время передачи добавляются дополнительные биты.

Код четности

Легко включить (добавить) один бит четности либо слева от MSB, либо справа от LSB исходного потока битов. Существует два типа кодов четности, а именно код четности и код нечетности, в зависимости от выбранного типа четности.

Код четности

Значение бита четности должно быть равно нулю, если в двоичном коде присутствует четное количество единиц. В противном случае он должен быть одним. Так что, четное количество единиц присутствует вeven parity code. Код четности содержит биты данных и бит четности.

В следующей таблице показаны even parity codesсоответствует каждому 3-битному двоичному коду. Здесь бит четности включен справа от младшего разряда двоичного кода.

| Бинарный код | Бит четности | Код четности |

|---|---|---|

| 000 | 0 | 0000 |

| 001 | 1 | 0011 |

| 010 | 1 | 0101 |

| 011 | 0 | 0110 |

| 100 | 1 | 1001 |

| 101 | 0 | 1010 |

| 110 | 0 | 1100 |

| 111 | 1 | 1111 |

Here, the number of bits present in the even parity codes is 4. So, the possible even number of ones in these even parity codes are 0, 2 & 4.

If the other system receives one of these even parity codes, then there is no error in the received data. The bits other than even parity bit are same as that of binary code.

If the other system receives other than even parity codes, then there will be an error(s) in the received data. In this case, we can’t predict the original binary code because we don’t know the bit position(s) of error.

Therefore, even parity bit is useful only for detection of error in the received parity code. But, it is not sufficient to correct the error.

Odd Parity Code

The value of odd parity bit should be zero, if odd number of ones present in the binary code. Otherwise, it should be one. So that, odd number of ones present in odd parity code. Odd parity code contains the data bits and odd parity bit.

The following table shows the odd parity codes corresponding to each 3-bit binary code. Here, the odd parity bit is included to the right of LSB of binary code.

| Binary Code | Odd Parity bit | Odd Parity Code |

|---|---|---|

| 000 | 1 | 0001 |

| 001 | 0 | 0010 |

| 010 | 0 | 0100 |

| 011 | 1 | 0111 |

| 100 | 0 | 1000 |

| 101 | 1 | 1011 |

| 110 | 1 | 1101 |

| 111 | 0 | 1110 |

Here, the number of bits present in the odd parity codes is 4. So, the possible odd number of ones in these odd parity codes are 1 & 3.

If the other system receives one of these odd parity codes, then there is no error in the received data. The bits other than odd parity bit are same as that of binary code.

If the other system receives other than odd parity codes, then there is an error(s) in the received data. In this case, we can’t predict the original binary code because we don’t know the bit position(s) of error.

Therefore, odd parity bit is useful only for detection of error in the received parity code. But, it is not sufficient to correct the error.

Hamming Code

Hamming code is useful for both detection and correction of error present in the received data. This code uses multiple parity bits and we have to place these parity bits in the positions of powers of 2.

The minimum value of 'k' for which the following relation is correct (valid) is nothing but the required number of parity bits.

$$2^k\geq n+k+1$$

Where,

‘n’ is the number of bits in the binary code (information)

‘k’ is the number of parity bits

Therefore, the number of bits in the Hamming code is equal to n + k.

Let the Hamming code is $b_{n+k}b_{n+k-1}.....b_{3}b_{2}b_{1}$ & parity bits $p_{k}, p_{k-1}, ....p_{1}$. We can place the ‘k’ parity bits in powers of 2 positions only. In remaining bit positions, we can place the ‘n’ bits of binary code.

Based on requirement, we can use either even parity or odd parity while forming a Hamming code. But, the same parity technique should be used in order to find whether any error present in the received data.

Follow this procedure for finding parity bits.

Find the value of p1, based on the number of ones present in bit positions b3, b5, b7 and so on. All these bit positions (suffixes) in their equivalent binary have ‘1’ in the place value of 20.

Find the value of p2, based on the number of ones present in bit positions b3, b6, b7 and so on. All these bit positions (suffixes) in their equivalent binary have ‘1’ in the place value of 21.

Find the value of p3, based on the number of ones present in bit positions b5, b6, b7 and so on. All these bit positions (suffixes) in their equivalent binary have ‘1’ in the place value of 22.

Similarly, find other values of parity bits.

Follow this procedure for finding check bits.

Find the value of c1, based on the number of ones present in bit positions b1, b3, b5, b7 and so on. All these bit positions (suffixes) in their equivalent binary have ‘1’ in the place value of 20.

Find the value of c2, based on the number of ones present in bit positions b2, b3, b6, b7 and so on. All these bit positions (suffixes) in their equivalent binary have ‘1’ in the place value of 21.

Find the value of c3, based on the number of ones present in bit positions b4, b5, b6, b7 and so on. All these bit positions (suffixes) in their equivalent binary have ‘1’ in the place value of 22.

Similarly, find other values of check bits.

The decimal equivalent of the check bits in the received data gives the value of bit position, where the error is present. Just complement the value present in that bit position. Therefore, we will get the original binary code after removing parity bits.

Example 1

Let us find the Hamming code for binary code, d4d3d2d1 = 1000. Consider even parity bits.

The number of bits in the given binary code is n=4.

We can find the required number of parity bits by using the following mathematical relation.

$$2^k\geq n+k+1$$

Substitute, n=4 in the above mathematical relation.

$$\Rightarrow 2^k\geq 4+k+1$$

$$\Rightarrow 2^k\geq 5+k$$

The minimum value of k that satisfied the above relation is 3. Hence, we require 3 parity bits p1, p2, and p3. Therefore, the number of bits in Hamming code will be 7, since there are 4 bits in binary code and 3 parity bits. We have to place the parity bits and bits of binary code in the Hamming code as shown below.

The 7-bit Hamming code is $b_{7}b_{6}b_{5}b_{4}b_{3}b_{2}b_{1}=d_{4}d_{3}d_{2}p_{3}d_{1}p_{2}bp_{1}$

By substituting the bits of binary code, the Hamming code will be $b_{7}b_{6}b_{5}b_{4}b_{3}b_{2}b_{1} = 100p_{3}Op_{2}p_{1}$. Now, let us find the parity bits.

$$p_{1}=b_{7}\oplus b_{5}\oplus b_{3}=1 \oplus 0 \oplus 0=1$$

$$p_{2}=b_{7}\oplus b_{6}\oplus b_{3}=1 \oplus 0 \oplus 0=1$$

$$p_{3}=b_{7}\oplus b_{6}\oplus b_{5}=1 \oplus 0 \oplus 0=1$$

By substituting these parity bits, the Hamming code will be $b_{7}b_{6}b_{5}b_{4}b_{3}b_{2}b_{1}= 1001011$.

Example 2

In the above example, we got the Hamming code as $b_{7}b_{6}b_{5}b_{4}b_{3}b_{2}b_{1}= 1001011$. Now, let us find the error position when the code received is $b_{7}b_{6}b_{5}b_{4}b_{3}b_{2}b_{1}= 1001111$.

Now, let us find the check bits.

$$c_{1}=b_{7}\oplus b_{5}\oplus b_{3}\oplus b_{1}=1 \oplus 0 \oplus 1 \oplus1 =1$$

$$c_{2}=b_{7}\oplus b_{6}\oplus b_{3}\oplus b_{2}=1 \oplus 0 \oplus 1 \oplus1 =1$$

$$c_{3}=b_{7}\oplus b_{6}\oplus b_{5}\oplus b_{4}=1 \oplus 0 \oplus 0 \oplus1 =0$$

The decimal value of check bits gives the position of error in received Hamming code.

$$c_{3}c_{2}c_{1} = \left ( 011 \right )_{2}=\left ( 3 \right )_{10}$$

Therefore, the error present in third bit (b3) of Hamming code. Just complement the value present in that bit and remove parity bits in order to get the original binary code.

Boolean Algebra is an algebra, which deals with binary numbers & binary variables. Hence, it is also called as Binary Algebra or logical Algebra. A mathematician, named George Boole had developed this algebra in 1854. The variables used in this algebra are also called as Boolean variables.

The range of voltages corresponding to Logic ‘High’ is represented with ‘1’ and the range of voltages corresponding to logic ‘Low’ is represented with ‘0’.

Postulates and Basic Laws of Boolean Algebra

In this section, let us discuss about the Boolean postulates and basic laws that are used in Boolean algebra. These are useful in minimizing Boolean functions.

Boolean Postulates

Consider the binary numbers 0 and 1, Boolean variable (x) and its complement (x’). Either the Boolean variable or complement of it is known as literal. The four possible logical OR operations among these literals and binary numbers are shown below.

x + 0 = x

x + 1 = 1

х + х = х

х + х '= 1

Точно так же четыре возможных logical AND операции между этими литералами и двоичными числами показаны ниже.

х.1 = х

х.0 = 0

хх = х

x.x '= 0

Это простые булевы постулаты. Мы можем легко проверить эти постулаты, заменив логическую переменную на «0» или «1».

Note- Дополнение к любой логической переменной равно самой переменной. т.е. (x ')' = x.

Основные законы булевой алгебры

Ниже приведены три основных закона булевой алгебры.

- Коммутативный закон

- Ассоциативный закон

- Распределительное право

Коммутативный закон

Если любая логическая операция с двумя логическими переменными дает один и тот же результат независимо от порядка этих двух переменных, то эта логическая операция называется Commutative. Операции логического ИЛИ и логического И для двух логических переменных x и y показаны ниже.

х + у = у + х

xy = yx

Символ «+» обозначает операцию логического ИЛИ. Точно так же символ '.' обозначает логическую операцию И и необязательно представлять. Коммутативный закон подчиняется операциям логического ИЛИ и логического И.

Ассоциативный закон

Если сначала выполняется логическая операция с любыми двумя логическими переменными, а затем такая же операция с оставшейся переменной дает тот же результат, то эта логическая операция называется Associative. Ниже показаны операции логического ИЛИ и логического И для трех логических переменных x, y и z.

х + (у + г) = (х + у) + г

х. (yz) = (ху) .z

Ассоциативный закон подчиняется операциям логического ИЛИ и логического И.

Распределительное право

Если какая-либо логическая операция может быть распределена на все термины, присутствующие в булевой функции, то эта логическая операция называется Distributive. Распределение операций логического ИЛИ и логического И трех логических переменных x, y и z показано ниже.

х. (у + г) = ху + хz

х + (уz) = (х + у). (х + z)

Распределительный закон подчиняется логическим операциям ИЛИ и логическим операциям И.

Это основные законы булевой алгебры. Мы можем легко проверить эти законы, заменив булевы переменные на «0» или «1».

Теоремы булевой алгебры

Следующие две теоремы используются в булевой алгебре.

- Теорема двойственности

- Теорема ДеМоргана

Теорема двойственности

Эта теорема утверждает, что dualлогической функции получается заменой логического оператора И оператором логического ИЛИ и нулей на единицы. Для каждой логической функции будет соответствующая функция Dual.

Разделим булевы уравнения (отношения), которые мы обсуждали в разделе «Булевы постулаты и основные законы», на две группы. В следующей таблице показаны эти две группы.

| Группа 1 | Группа 2 |

|---|---|

| х + 0 = х | х.1 = х |

| х + 1 = 1 | х.0 = 0 |

| х + х = х | хх = х |

| х + х '= 1 | x.x '= 0 |

| х + у = у + х | xy = yx |

| х + (у + г) = (х + у) + г | х. (yz) = (ху) .z |

| х. (у + г) = ху + хz | х + (уz) = (х + у). (х + z) |

В каждой строке есть два булевых уравнения, двойственных друг другу. Мы можем проверить все эти булевы уравнения Группы 1 и Группы 2, используя теорему двойственности.

Теорема ДеМоргана

Эта теорема полезна при нахождении complement of Boolean function. Он утверждает, что дополнение логического ИЛИ по крайней мере двух логических переменных равно логическому И каждой дополненной переменной.

Теорема ДеМоргана с двумя булевыми переменными x и y может быть представлена как

(х + у) '= х'.у'

Двойственная к вышеуказанной булевой функции есть

(ху) '= х' + у '

Следовательно, дополнение логического И двух логических переменных равно логическому ИЛИ каждой дополняемой переменной. Точно так же мы можем применить теорему ДеМоргана для более чем двух булевых переменных.

Упрощение булевых функций.

До сих пор мы обсуждали постулаты, основные законы и теоремы булевой алгебры. Теперь давайте упростим некоторые булевы функции.

Пример 1

Разрешите нам simplify булева функция, f = p'qr + pq'r + pqr '+ pqr

Мы можем упростить эту функцию двумя способами.

Method 1

Для данной булевой функции f = p'qr + pq'r + pqr '+ pqr.

Step 1- В первом и втором членах r является общим, а в третьем и четвертом членах pq является общим. Итак, возьмите общие термины, используяDistributive law.

⇒ f = (p'q + pq ') r + pq (r' + r).

Step 2- Термины, указанные в первых скобках, могут быть упрощены до операции Ex-OR. Термины, представленные во вторых скобках, можно упростить до «1», используяBoolean postulate

⇒ f = (p ⊕q) r + pq (1)

Step 3- Первый термин не подлежит дальнейшему упрощению. Но второй член можно упростить до pq, используяBoolean postulate.

⇒ f = (p ⊕q) r + pq

Следовательно, упрощенная логическая функция f = (p⊕q)r + pq

Method 2

Для данной булевой функции f = p'qr + pq'r + pqr '+ pqr.

Step 1 - Используйте Boolean postulate, х + х = х. Это означает, что операция логического ИЛИ с любой логической переменной n раз будет равна той же переменной. Итак, мы можем написать последний член pqr еще два раза.

⇒ f = p'qr + pq'r + pqr '+ pqr + pqr + pqr

Step 2 - Использование Distributive lawдля 1- го и 4- го , 2- го и 5- го , 3- го и 6- го триместров.

⇒ f = qr (p '+ p) + pr (q' + q) + pq (r '+ r).

Step 3 - Использование Boolean postulate, x + x '= 1 для упрощения терминов, содержащихся в каждой скобке.

⇒ f = qr (1) + pr (1) + pq (1)

Step 4 - Использование Boolean postulate, x.1 = x для упрощения трех приведенных выше терминов.

⇒ f = qr + pr + pq

⇒ f = pq + qr + pr

Следовательно, упрощенная логическая функция f = pq + qr + pr.

Итак, после упрощения данной логической функции в каждом методе мы получили две разные логические функции. Функционально эти две булевы функции одинаковы. Итак, исходя из требований, мы можем выбрать одну из этих двух логических функций.

Пример 2

Давайте найдем complement булевой функции f = p'q + pq '.

Дополнением к булевой функции является f '= (p'q + pq') '.

Step 1 - Используйте теорему ДеМоргана, (x + y) '= x'.y'.

⇒ f '= (p'q)'. (Pq ')'

Step 2 - Используйте теорему ДеМоргана, (xy) '= x' + y '

⇒ f '= {(p') '+ q'}. {P '+ (q') '}.

Step3 - Используйте булев постулат, (x ')' = x.

⇒ f '= {p + q'}. {P '+ q}.

⇒ f '= pp' + pq + p'q '+ qq'

Step 4 - Используйте булев постулат, xx '= 0.

⇒ f = 0 + pq + p'q '+ 0

⇒ f = pq + p'q '

Следовательно complement булевой функции p'q + pq 'равно pq + p’q’.

Мы получим четыре логических термина продукта, объединив две переменные x и y с помощью логической операции И. Эти логические термины продукта называютсяmin terms или же standard product terms. Минимальные члены - это x'y ', x'y, xy' и xy.

Точно так же мы получим четыре члена логической суммы, объединив две переменные x и y с помощью операции логического ИЛИ. Эти логические суммы называютсяMax terms или же standard sum terms. Термины Max: x + y, x + y ', x' + y и x '+ y'.

В следующей таблице показано представление минимальных и максимальных значений для 2 переменных.

| Икс | y | Минимальные сроки | Максимальные сроки |

|---|---|---|---|

| 0 | 0 | m 0 = x'y ' | М 0 = х + у |

| 0 | 1 | m 1 = x'y | М 1 = х + у ' |

| 1 | 0 | м 2 = ху ' | М 2 = х '+ у |

| 1 | 1 | м 3 = ху | М 3 = х '+ у' |

Если двоичная переменная равна «0», то она представляется как дополнение переменной в минимальном термине и как сама переменная в максимальном термине. Точно так же, если двоичная переменная равна «1», то она представлена как дополнение переменной в Max term и как сама переменная в min term.

Из приведенной выше таблицы мы можем легко заметить, что минимальные и максимальные термины дополняют друг друга. Если имеется n логических переменных, то будет 2 n минимальных и 2 n максимальных терминов.

Канонические формы SoP и PoS

Таблица истинности состоит из набора входов и выходов. Если есть n входных переменных, то будет 2 n возможных комбинаций с нулями и единицами. Таким образом, значение каждой выходной переменной зависит от комбинации входных переменных. Таким образом, каждая выходная переменная будет иметь «1» для некоторой комбинации входных переменных и «0» для некоторой другой комбинации входных переменных.

Следовательно, мы можем выразить каждую выходную переменную двумя способами.

- Каноническая форма SoP

- Каноническая форма PoS

Каноническая форма SoP

Каноническая форма SoP означает форму канонической суммы произведений. В этой форме каждый термин продукта содержит все литералы. Итак, эти условия продукта - не что иное, как минимальные условия. Следовательно, каноническая форма SoP также называетсяsum of min terms форма.

Сначала определите минимальные термины, для которых выходная переменная равна единице, а затем выполните логическое ИЛИ этих минимальных терминов, чтобы получить логическое выражение (функцию), соответствующее этой выходной переменной. Эта логическая функция будет иметь форму суммы минимальных членов.

Выполните ту же процедуру и для других выходных переменных, если существует более одной выходной переменной.

пример

Рассмотрим следующие truth table.

| Входы | Вывод | ||

|---|---|---|---|

| p | q | r | f |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

Здесь выход (f) равен «1» для четырех комбинаций входов. Соответствующие минимальные члены - это p'qr, pq'r, pqr ', pqr. Выполнив логическое ИЛИ для этих четырех минимальных членов, мы получим логическую функцию вывода (f).

Следовательно, логическая функция вывода: f = p'qr + pq'r + pqr '+ pqr. Этоcanonical SoP formвыработки, ф. Мы также можем представить эту функцию в следующих двух обозначениях.

$$f = m_{3}+m_{5}+m_{6}+m_{7}$$

$$f = \sum m\left ( 3,5,6,7 \right )$$

В одном уравнении мы представили функцию как сумму соответствующих минимальных членов. В другом уравнении мы использовали символ для суммирования этих минимальных членов.

Каноническая форма PoS

Каноническая форма PoS означает форму канонического произведения сумм. В этой форме каждый член суммы содержит все литералы. Итак, эти суммы являются не чем иным, как максимальными условиями. Следовательно, каноническая форма PoS также называетсяproduct of Max terms форма.

Сначала определите условия Max, для которых выходная переменная равна нулю, а затем выполните логическое И этих терминов Max, чтобы получить логическое выражение (функцию), соответствующее этой выходной переменной. Эта логическая функция будет представлена в виде произведения максимальных членов.

Выполните ту же процедуру и для других выходных переменных, если существует более одной выходной переменной.

Example

Рассмотрим ту же таблицу истинности из предыдущего примера. Здесь выход (f) равен «0» для четырех комбинаций входов. Соответствующие члены Max: p + q + r, p + q + r ', p + q' + r, p '+ q + r. Выполнив логическое И для этих четырех максимальных членов, мы получим булеву функцию вывода (f).

Следовательно, логическая функция вывода: f = (p + q + r). (P + q + r '). (P + q' + r). (P '+ q + r). Этоcanonical PoS formвыработки, ф. Мы также можем представить эту функцию в следующих двух обозначениях.

$$f=M_{0}.M_{1}.M_{2}.M_{4}$$

$$f=\prod M\left ( 0,1,2,4 \right )$$

В одном уравнении мы представили функцию как произведение соответствующих членов Max. В другом уравнении мы использовали символ для умножения этих максимальных членов.

Булева функция, f = (p + q + r). (P + q + r '). (P + q' + r). (P '+ q + r), является двойником булевой функции, f = p'qr + pq'r + pqr '+ pqr.

Следовательно, и каноническая форма SoP, и каноническая форма PoS являются Dualдруг другу. Функционально эти две формы одинаковы. Исходя из требований, мы можем использовать одну из этих двух форм.

Стандартные формы SoP и PoS

Мы обсудили две канонические формы представления логического вывода (ов). Точно так же есть две стандартные формы представления логического вывода (ов). Это упрощенная версия канонических форм.

- Стандартная форма SoP

- Стандартная форма PoS

Мы обсудим логические вентили в следующих главах. Главныйadvantageстандартных форм состоит в том, что количество входов, применяемых к логическим элементам, может быть минимизировано. Иногда общее количество требуемых логических вентилей сокращается.

Стандартная форма SoP

Стандартная форма SoP означает Standard Sum of Productsформа. В этой форме каждый термин продукта не обязательно должен содержать все литералы. Таким образом, условия продукта могут быть минимальными, а могут и не быть. Следовательно, стандартная форма SoP - это упрощенная форма канонической формы SoP.

Мы получим стандартную форму выходной переменной SoP за два шага.

- Получите каноническую форму выходной переменной SoP

- Упростите приведенную выше логическую функцию, которая находится в канонической форме SoP.

Выполните ту же процедуру и для других выходных переменных, если существует более одной выходной переменной. Иногда невозможно упростить каноническую форму SoP. В этом случае и каноническая, и стандартная форма SoP одинаковы.

Example

Преобразуйте следующую логическую функцию в стандартную форму SoP.

f = p'qr + pq'r + pqr '+ pqr

Данная булева функция находится в канонической форме SoP. Теперь нам нужно упростить эту логическую функцию, чтобы получить стандартную форму SoP.

Step 1 - Используйте Boolean postulate, х + х = х. Это означает, что операция логического ИЛИ с любой логической переменной n раз будет равна той же переменной. Итак, мы можем написать последний член pqr еще два раза.

⇒ f = p'qr + pq'r + pqr '+ pqr + pqr + pqr

Step 2 - Использование Distributive lawдля 1- го и 4- го , 2- го и 5- го , 3- го и 6- го триместров.

⇒ f = qr (p '+ p) + pr (q' + q) + pq (r '+ r).

Step 3 - Использование Boolean postulate, x + x '= 1 для упрощения терминов, содержащихся в каждой скобке.

⇒ f = qr (1) + pr (1) + pq (1)

Step 4 - Использование Boolean postulate, x.1 = x для упрощения вышеуказанных трех членов.

⇒ f = qr + pr + pq

⇒ f = pq + qr + pr

Это упрощенная логическая функция. Следовательноstandard SoP form соответствующая данной канонической форме SoP f = pq + qr + pr

Стандартная форма PoS

Стандартная форма PoS означает Standard Product of Sumsформа. В этой форме каждый член суммы не обязательно должен содержать все литералы. Таким образом, условия суммы могут быть или не быть максимальными условиями. Таким образом, Стандартная форма PoS - это упрощенная форма канонической формы PoS.

Мы получим стандартную форму выходной переменной PoS за два шага.

- Получите каноническую форму выходной переменной PoS

- Упростите приведенную выше логическую функцию, которая находится в канонической форме PoS.

Выполните ту же процедуру и для других выходных переменных, если существует более одной выходной переменной. Иногда невозможно упростить каноническую форму PoS. В этом случае и каноническая, и стандартная форма PoS одинаковы.

Example

Преобразуйте следующую логическую функцию в стандартную форму PoS.

f = (p + q + r). (p + q + r '). (p + q' + r). (p '+ q + r).

Данная логическая функция находится в канонической форме PoS. Теперь нам нужно упростить эту логическую функцию, чтобы получить стандартную форму PoS.

Step 1 - Используйте Boolean postulate, хх = х. Это означает, что операция логического И с любой логической переменной n раз будет равна той же переменной. Итак, мы можем написать первый член p + q + r еще два раза.

⇒ f = (p + q + r). (P + q + r). (P + q + r). (P + q + r '). (P + q' + r). (P '+ q). + г)

Step 2 - Использование Distributive law,x + (yz) = (x + y). (x + z) для 1- й и 4- й скобок, 2- й и 5- й скобок, 3- й и 6- й скобок.

⇒ f = (p + q + rr '). (P + r + qq'). (Q + r + pp ').

Step 3 - Использование Boolean postulate, x.x '= 0 для упрощения терминов, содержащихся в каждой скобке.

⇒ f = (p + q + 0). (P + r + 0). (Q + r + 0).

Step 4 - Использование Boolean postulate, x + 0 = x для упрощения терминов в каждой скобке

⇒ f = (p + q). (P + r). (Q + r).

⇒ f = (p + q). (Q + r). (P + r).

Это упрощенная логическая функция. Следовательноstandard PoS form соответствующая данной канонической форме PoS, является f = (p + q).(q + r).(p + r). Этоdual булевой функции f = pq + qr + pr.

Следовательно, и стандартные формы SoP, и стандартные формы PoS являются двойными друг другу.

В предыдущих главах мы упростили булевы функции, используя булевы постулаты и теоремы. Это трудоемкий процесс, и мы должны переписывать упрощенные выражения после каждого шага.

Чтобы преодолеть эту трудность, Karnaughпредставил метод упрощения булевых функций простым способом. Этот метод известен как метод карты Карно или метод K-карты. Это графический метод, который состоит из 2 n ячеек для n переменных. Соседние ячейки различаются только позицией одного бита.

K-карты для 2-5 переменных

Метод K-Map лучше всего подходит для минимизации булевых функций от 2 переменных до 5 переменных. Теперь давайте обсудим K-Maps для 2–5 переменных по очереди.

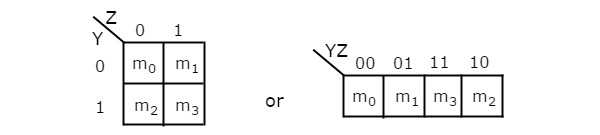

2 переменная K-карта

Количество ячеек в К-карте 2 переменных равно четырем, так как количество переменных равно двум. На следующем рисунке показано2 variable K-Map.

Есть только одна возможность сгруппировать 4 соседних минимальных термина.

Возможные комбинации группировки 2 соседних min термов: {(m 0 , m 1 ), (m 2 , m 3 ), (m 0 , m 2 ) и (m 1 , m 3 )}.

3 переменная K-карта

Количество ячеек в К-карте с 3 переменными равно восьми, так как количество переменных равно трем. На следующем рисунке показано3 variable K-Map.

Есть только одна возможность сгруппировать 8 соседних мин. Терминов.

Возможные комбинации группировки 4 соседних min терминов: {(m 0 , m 1 , m 3 , m 2 ), (m 4 , m 5 , m 7 , m 6 ), (m 0 , m 1 , m 4 , m 5 ), (m 1 , m 3 , m 5 , m 7 ), (m 3 , m 2 , m 7 , m 6 ) и (m 2 , m 0 , m 6 , m 4 )}.

Возможные комбинации группировки 2 соседних min термов: {(m 0 , m 1 ), (m 1 , m 3 ), (m 3 , m 2 ), (m 2 , m 0 ), (m 4 , m 5 ) , (m 5 , m 7 ), (m 7 , m 6 ), (m 6 , m 4 ), (m 0 , m 4 ), (m 1 , m 5 ), (m 3 , m 7 ) и ( м 2 , м 6 )}.

Если x = 0, то K-карта с 3 переменными становится K-картой с 2 переменными.

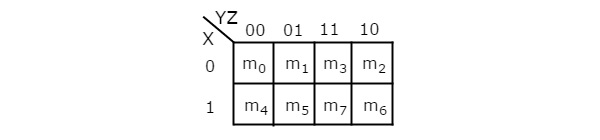

4 переменных K-Map

Количество ячеек в K-карте с 4 переменными равно шестнадцати, поскольку количество переменных равно четырем. На следующем рисунке показано4 variable K-Map.

Есть только одна возможность сгруппировать 16 соседних минутных терминов.

Пусть R 1 , R 2 , R 3 и R 4 представляют минимальные члены первой строки, второй строки, третьей строки и четвертой строки соответственно. Точно так же C 1 , C 2 , C 3 и C 4 представляют минимальные члены первого столбца, второго столбца, третьего столбца и четвертого столбца соответственно. Возможные комбинации группировки 8 соседних минимальных терминов: {(R 1 , R 2 ), (R 2 , R 3 ), (R 3 , R 4 ), (R 4 , R 1 ), (C 1 , C 2 ) , (С 2 , С 3 ), (С 3 , С 4 ), (С 4 , С 1 )}.

Если w = 0, то K-карта с 4 переменными становится K-картой с 3 переменными.

5 переменных K-Map

Количество ячеек в K-карте с 5 переменными равно 32, так как количество переменных равно 5. На следующем рисунке показано 5 variable K-Map.

Есть только одна возможность сгруппировать 32 соседних минимальных термина.

Есть две возможности сгруппировать 16 соседних мин. Терминов. т. е. группировка минимальных терминов от m 0 до m 15 и m 16 до m 31 .

Если v = 0, то K-карта с 5 переменными становится K-картой с 4 переменными.

Во всех вышеупомянутых K-картах мы использовали исключительно обозначение минимальных терминов. Точно так же вы можете использовать исключительно обозначение терминов Max.

Минимизация булевых функций с помощью K-Maps

Если мы рассмотрим комбинацию входов, для которых логическая функция равна '1', то мы получим логическую функцию, которая находится в standard sum of products форма после упрощения K-карты.

Точно так же, если мы рассмотрим комбинацию входов, для которых логическая функция равна '0', мы получим логическую функцию, которая находится в standard product of sums форма после упрощения K-карты.

Следуйте этим rules for simplifying K-maps чтобы получить стандартную форму суммы продуктов.

Выберите соответствующую K-карту на основе количества переменных, присутствующих в булевой функции.

Если логическая функция задана как сумма минимальных терминов, то поместите их в соответствующие ячейки минимальных терминов на K-карте. Если булева функция задана как сумма продуктов, поместите их во все возможные ячейки K-карты, для которых действительны заданные условия продукта.

Проверьте возможности группировки максимального количества соседних. Это должно быть степень двойки. Начните с наибольшей степени двойки и до наименьшей степени двойки. Наивысшая степень равна количеству переменных, рассматриваемых в K-карте, а наименьшая степень равна нулю.

Каждая группа дает буквальный или один термин продукта. Он известен какprime implicant. Главный импликант называетсяessential prime implicant, если хотя бы одна '1' не покрывается никакими другими группами, а покрывается только этой группой.

Запишите все основные импликанты и основные импликанты. Упрощенная логическая функция содержит все основные простые импликанты и только необходимые простые импликанты.

Note 1 - Если выходы не определены для некоторой комбинации входов, то эти выходные значения будут представлены как don’t care symbol ‘x’. Это означает, что мы можем рассматривать их как «0» или «1».

Note 2- Если также присутствуют термины «безразлично», поместите «х» в соответствующие ячейки K-карты. Учитывайте только безразличные 'x', которые помогают сгруппировать максимальное количество соседних. В таких случаях считайте значение безразличия "1".

пример

Разрешите нам simplify следующая логическая функция, f(W, X, Y, Z)= WX’Y’ + WY + W’YZ’ используя K-карту.

Данная логическая функция находится в форме суммы произведений. Он имеет 4 переменные W, X, Y и Z. Итак, нам требуется4 variable K-map. В4 variable K-map с теми, которые соответствуют данным условиям продукта, показано на следующем рисунке.

Здесь единицы помещаются в следующие ячейки K-карты.

Ячейки, которые являются общими для пересечения строки 4 и столбцов 1 и 2, соответствуют термину продукта, WX’Y’.

Ячейки, которые являются общими для пересечения строк 3 и 4 и столбцов 3 и 4, соответствуют термину продукта, WY.

Ячейки, которые являются общими для пересечения строк 1 и 2 и столбца 4, соответствуют термину продукта, W’YZ’.

Нет возможности группировать ни 16 соседних, ни 8 соседних. Есть три возможности сгруппировать 4 соседних. После этих трех группировок не остается ни одной разгруппированной. Таким образом, нам не нужно проверять группировку 2-х соседних. В4 variable K-map с этими тремя groupings показано на следующем рисунке.

Здесь мы получили три основных импликанта WX ', WY и YZ'. Все эти основные импликантыessential по следующим причинам.

Два (m8 & m9)группы четвертой строки не попадают ни в какие другие группы. Только четвертая группа строк охватывает эти две строки.

Один (m15)группировки квадратной формы не покрываются никакими другими группировками. Только квадратная группа покрывает это.

Два (m2 & m6)группы четвертого столбца не попадают ни в какие другие группы. Только четвертая группа столбцов охватывает эти две.

Следовательно simplified Boolean function является

f = WX’ + WY + YZ’

Следуйте этим rules for simplifying K-maps для получения стандартного продукта суммовой формы.

Выберите соответствующую K-карту на основе количества переменных, присутствующих в булевой функции.

Если логическая функция задана как произведение максимальной формы термов, тогда поместите нули в соответствующие ячейки максимума термов на K-карте. Если логическая функция задана как произведение суммы сумм, то поместите нули во все возможные ячейки K-карты, для которых действительны заданные члены суммы.

Проверьте возможности группировки максимального количества соседних нулей. Это должно быть степень двойки. Начните с наибольшей степени двойки и до наименьшей степени двойки. Наивысшая степень равна количеству переменных, рассматриваемых в K-карте, а наименьшая степень равна нулю.

Каждая группировка даст буквальный или один суммарный член. Он известен какprime implicant. Главный импликант называетсяessential prime implicant, если хотя бы один '0' не покрывается никакими другими группами, а покрывается только эта группа.

Запишите все основные импликанты и основные импликанты. Упрощенная логическая функция содержит все основные простые импликанты и только необходимые простые импликанты.

Note- Если также присутствуют термины «безразлично», поместите «х» в соответствующие ячейки K-карты. Рассмотрим только безразличный 'x', который помогает сгруппировать максимальное количество соседних нулей. В таких случаях значение безразличия следует рассматривать как «0».

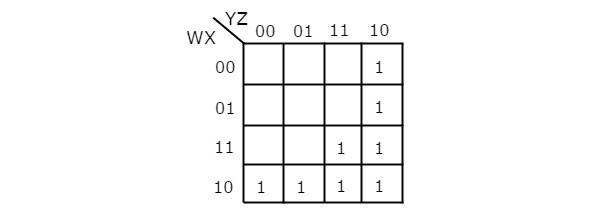

пример

Разрешите нам simplify следующая логическая функция, $f\left ( X,Y,Z \right )=\prod M\left ( 0,1,2,4 \right )$ используя K-карту.

Данная логическая функция является продуктом формы максимума термов. Он имеет 3 переменные X, Y и Z. Итак, нам требуется 3 переменных K-map. Указанные условия Max: M 0 , M 1 , M 2 и M 4 . 3variable K-map с нулями, соответствующими заданным параметрам Max, показано на следующем рисунке.

Нет возможности сгруппировать 8 соседних нулей или 4 соседних нуля. Есть три возможности сгруппировать 2 соседних нуля. После этих трех группировок не остается ни одного нуля в разгруппированном виде. В3 variable K-map с этими тремя groupings показано на следующем рисунке.

Здесь мы получили три простые импликанты X + Y, Y + Z и Z + X. Все эти простые импликанты суть essential потому что один ноль в каждой группе не покрывается никакими другими группами, кроме их индивидуальных группировок.

Следовательно simplified Boolean function является

f = (X + Y).(Y + Z).(Z + X)

Таким образом, мы можем легко упростить логические функции до 5 переменных, используя метод K-map. Для более чем 5 переменных сложно упростить функции с помощью K-Maps. Потому что количествоcells в K-карте получает doubled включив новую переменную.

Из-за этого проверка и группировка соседних единиц (минимальные члены) или соседних нулей (максимальные члены) будут усложнены. Мы обсудимTabular method в следующей главе, чтобы преодолеть трудности метода K-map.

В предыдущей главе мы обсудили метод K-map, который является удобным методом минимизации булевых функций до 5 переменных. Но с помощью этого метода сложно упростить логические функции, имеющие более 5 переменных.

Табличный метод Куайна-Макклюки - это табличный метод, основанный на концепции простых импликантов. Мы знаем этоprime implicant - это член произведения (или суммы), который не может быть дополнительно уменьшен путем объединения с любыми другими членами произведения (или суммы) данной булевой функции.

Этот табличный метод полезен для получения основных импликантов путем многократного использования следующего логического идентификатора.

ху + ху '= х (у + у') = х.1 = х

Процедура табличного метода Куайна-Маккласки

Выполните следующие шаги для упрощения логических функций с использованием табличного метода Куайна-Макклюки.

Step 1 - Упорядочить указанные минимальные сроки в ascending orderи сделайте группы на основе количества единиц, присутствующих в их двоичных представлениях. Итак, будетat most ‘n+1’ groups если есть n логических переменных в булевой функции или n битов в двоичном эквиваленте минимальных условий.

Step 2 - Сравните минимальные термины, представленные в successive groups. Если есть изменение только в одной битовой позиции, тогда возьмите пару этих двух минимальных членов. Поместите этот символ '_' в другую битовую позицию и оставьте оставшиеся биты как есть.

Step 3 - Повторите шаг 2 с вновь сформированными терминами, пока мы не получим все prime implicants.

Step 4 - Сформулируйте prime implicant table. Он состоит из набора строк и столбцов. Простые импликанты можно размещать по строкам, а минимальные термины - по столбцам. Поместите «1» в ячейки, соответствующие минимальным терминам, которые включены в каждый простой импликант.

Step 5- Найдите основные основные импликанты, наблюдая за каждым столбцом. Если минимальный член покрывается только одним простым импликантом, то онessential prime implicant. Эти важные простые импликанты будут частью упрощенной логической функции.

Step 6- Уменьшите таблицу простых импликантов, удалив строку каждого существенного простого импликанта и столбцы, соответствующие минимальным членам, которые покрываются этим существенным простым импликантом. Повторите шаг 5 для уменьшенной простой импликантной таблицы. Остановите этот процесс, когда все минимальные члены данной булевой функции закончились.

пример

Разрешите нам simplify следующая логическая функция, $f\left ( W,X,Y,Z \right )=\sum m\left ( 2,6,8,9,10,11,14,15 \right )$ с использованием табличного метода Куайна-Макклюки.

Данная логическая функция находится в sum of min termsформа. Он имеет 4 переменные W, X, Y и Z. Заданные минимальные члены - это 2, 6, 8, 9, 10, 11, 14 и 15. Порядок возрастания этих минимальных членов основан на количестве единиц, присутствующих в их двоичный эквивалент - 2, 8, 6, 9, 10, 11, 14 и 15. В следующей таблице показаны этиmin terms and their equivalent binary представления.

| Имя группы | Минимальные сроки | W | Икс | Y | Z |

|---|---|---|---|---|---|

| GA1 | 2 | 0 | 0 | 1 | 0 |

| 8 | 1 | 0 | 0 | 0 | |

| GA2 | 6 | 0 | 1 | 1 | 0 |

| 9 | 1 | 0 | 0 | 1 | |

| 10 | 1 | 0 | 1 | 0 | |

| 11 | 1 | 0 | 1 | 1 | |

| 14 | 1 | 1 | 1 | 0 | |

| GA4 | 15 | 1 | 1 | 1 | 1 |

Указанные минимальные термины разбиты на 4 группы в зависимости от количества единиц, присутствующих в их двоичных эквивалентах. В следующей таблице показаны возможныеmerging of min terms из соседних групп.

| Имя группы | Минимальные сроки | W | Икс | Y | Z |

|---|---|---|---|---|---|

| GB1 | 2,6 | 0 | - | 1 | 0 |

| 2,10 | - | 0 | 1 | 0 | |

| 8,9 | 1 | 0 | 0 | - | |

| 8,10 | 1 | 0 | - | 0 | |

| GB2 | 6,14 | - | 1 | 1 | 0 |

| 9,11 | 1 | 0 | - | 1 | |

| 10,11 | 1 | 0 | 1 | - | |

| 10,14 | 1 | - | 1 | 0 | |

| 11,15 | 1 | - | 1 | 1 | |

| 14,15 | 1 | 1 | 1 | - |

Минимальные члены, которые отличаются только одной битовой позицией от соседних групп, объединяются. Этот отличающийся бит представлен этим символом '-'. В этом случае есть три группы, и каждая группа содержит комбинации из двух минимальных терминов. В следующей таблице показаны возможныеmerging of min term pairs из соседних групп.

| Имя группы | Минимальные сроки | W | Икс | Y | Z |

|---|---|---|---|---|---|

| GB1 | 2,6,10,14 | - | - | 1 | 0 |

| 2,10,6,14 | - | - | 1 | 0 | |

| 8,9,10,11 | 1 | 0 | - | - | |

| 8,10,9,11 | 1 | 0 | - | - | |

| GB2 | 10,11,14,15 | 1 | - | 1 | - |

| 10,14,11,15 | 1 | - | 1 | - |

Последовательные группы минимальных пар терминов, которые отличаются только одной битовой позицией, объединяются. Этот отличающийся бит представлен этим символом '-'. В этом случае есть две группы, и каждая группа содержит комбинации из четырех минимальных терминов. Здесь эти комбинации 4-минутных терминов доступны в двух рядах. Итак, мы можем удалить повторяющиеся строки. Уменьшенная таблица после удаления избыточных строк показана ниже.

| Имя группы | Минимальные сроки | W | Икс | Y | Z |

|---|---|---|---|---|---|

| GC1 | 2,6,10,14 | - | - | 1 | 0 |

| 8,9,10,11 | 1 | 0 | - | - | |

| GC2 | 10,11,14,15 | 1 | - | 1 | - |

Дальнейшее объединение комбинаций минимальных термов из соседних групп невозможно, так как они различаются более чем в одной битовой позиции. В приведенной выше таблице есть три строки. Итак, каждая строка дает одну простую импликанту. Следовательноprime implicants являются YZ ', WX' и WY.

В prime implicant table показано ниже.

| Минимальные сроки / основные импликанты | 2 | 6 | 8 | 9 | 10 | 11 | 14 | 15 |

|---|---|---|---|---|---|---|---|---|

| YZ’ | 1 | 1 | 1 | 1 | ||||

| WX’ | 1 | 1 | 1 | 1 | ||||

| WY | 1 | 1 | 1 | 1 |

Первичные импликанты располагаются по строкам, а минимальные термины - по столбцам. Единицы помещаются в общие ячейки простых импликантных строк и соответствующих столбцов с минимальным термином.

Минимальные члены 2 и 6 покрываются только одним простым импликантом YZ’. Итак, этоessential prime implicant. Это будет частью упрощенной логической функции. Теперь удалите эту простую импликантную строку и соответствующие столбцы с минимальным термином. Сокращенная таблица импликантов простых чисел показана ниже.

| Минимальные сроки / основные импликанты | 8 | 9 | 11 | 15 |

|---|---|---|---|---|

| WX’ | 1 | 1 | 1 | |

| WY | 1 | 1 |

Минимальные члены 8 и 9 покрываются только одним простым импликантом WX’. Итак, этоessential prime implicant. Это будет частью упрощенной логической функции. Теперь удалите эту простую импликантную строку и соответствующие столбцы с минимальным термином. Сокращенная таблица импликантов простых чисел показана ниже.

| Минимальные сроки / основные импликанты | 15 |

|---|---|

| WY | 1 |

Минимальный член 15 покрывается только одним простым импликантом WY. Итак, этоessential prime implicant. Это будет частью упрощенной логической функции.

В этом примере задачи у нас есть три основных импликанты, и все они существенны. Следовательноsimplified Boolean function является

f(W,X,Y,Z) = YZ’ + WX’ + WY.

Цифровые электронные схемы работают с напряжениями two logic levelsа именно Logic Low и Logic High. Диапазон напряжений, соответствующий нижнему логическому уровню, представлен «0». Точно так же диапазон напряжений, соответствующий High Logic, представлен цифрой «1».

Базовая цифровая электронная схема, имеющая один или несколько входов и один выход, известна как Logic gate. Следовательно, логические ворота являются строительными блоками любой цифровой системы. Мы можем разделить эти логические ворота на следующие три категории.

- Основные ворота

- Универсальные ворота

- Специальные ворота

Теперь давайте поговорим о логических воротах, подпадающих под каждую категорию один за другим.

Основные ворота

В предыдущих главах мы узнали, что булевы функции могут быть представлены либо в форме суммы произведений, либо в форме произведения сумм в зависимости от требований. Итак, мы можем реализовать эти логические функции с помощью базовых вентилей. Основные ворота - это ворота И, ИЛИ И НЕ.

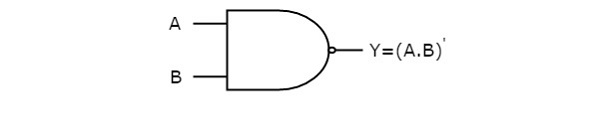

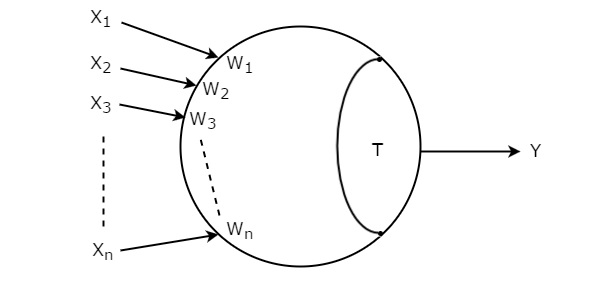

И ворота